数字电路讲义与 系统设计

数电讲义--2章

1.0

VOL(max)0.5

输入标 准低电

平

0.4V

VNL

D VNH

E

V V 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

SL VOFF VON

SH

Vi (V)

输入标准

高电平

2. 输入特性

+VCC

1) 输入伏安特性

iI

R1 3kΩ

1

-1.6 mA

<50 uA vI A

31

B

T1

1.4 V

和边沿,T4放大。 VO随iOH变化不大。 当由i于Oi以OHH受↑:线时功性,R耗变4上的化压限。降制增,大i0,H过T大3 、会T4烧饱毁和T,4管V,O随所

功耗 1mW IOH 400 A

输出高电平时的扇出系数 3.6V

R2 750Ω 2T3 Vc2 1 3 R4

VO

+VCC

R 4 +5V 100Ω

抗干扰能力越强。 高电平噪声容限

VNH= VSH ¯ VON 。

VNH越大,输入为1态下

抗干扰能力越强。

Vo (V)

4.0 A B

3.5

3.0

VOH(min)2.5 2.4V

C

2.0

1.5

A(0V, 3. 6V) B(0.6V, 3.6V) C(1.3V, 2.48V) D(1.4V, 0.3V) E(3.6V, 0.3V)

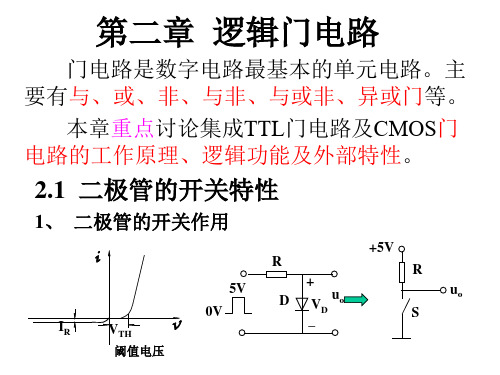

• 导通(VD>VTH) • 2、二极管的开关时间

截止5V(VDR<VT+H)

0V

D VD

uo

_

VF Vi

二极管开关状态的转换需要时间:

t1 t2

《数字电路》实验讲义

一、实验目的

1.掌握寄存器的工作原理、逻辑功能及应用;

2.掌握异步计数器的工作原理及输出波形;

3.掌握中规模集成电路计数器接成任意进制计数器的方法

二、实验设备及器件

1.SAC-DS数字逻辑实验箱一台;

⑶用一片74LS153和一片74LS00接成一位全加器

⑷设计一个有A、B、C三位代码输入的密码锁(假设密码是011),当输入密码正确时,锁被打开(Y1=1),如果密码不符,电路发出报警信号(Y2=1)。

以上四个小设计任做一个,多做不限。

实验三触发器及触发器之间的转换

一、实验目的

1.掌握D触发器和JK触发器的逻辑功能及触发方式;

输入

输出

A

B

C

D

Y

0

0

0

0

1

0

0

0

1

1

0

0

1

1

1

0

1

1

1

1

1

1

1

1

0

4.异或门逻辑功能的测试

⑴按图1-4接好电路。

⑵按表1-4的要求测试,将结果填入表1-4中。

输入

输出

A

B

Y

0

0

0

0

1

1

1

0

1

1

1

0

5.设计实验

⑴用一片74LS00实现Y = A+B的逻辑功能;

⑵用一片74LS86设计一个四位奇偶校验电路;

以上两个小设计必做一个,多做不限。

四、思考题

1.与非门一个输入端接连续脉冲,其余端是何状态时允许脉冲通过,是何状态时禁止脉冲通过?

2.为什么异或门又称为可控反相门?

数字电路讲义 第三章

是构成数字电路的基本单元之一

CMOS 集成门电路 用互补对称 MOS 管构成的逻辑门电路。

TTL 集成门电路 输入端和输出端都用 三极管的逻辑门电路。

CMOS Complementary Metal-Oxide-Semiconductor TTL 即即 Transistor-Transistor Logic 按功能特点不同分 普通门 输出 三态门 CMOS (推拉式输出) 开路门 传输门 EXIT

E

B UBE(sat) iB ≥ IB(sat) E C

三极管 截止状态 等效电路

UCE(sat)

三极管 饱和状态 等效电路

EXIT

逻辑门电路

开关工作的条件

截止条件 uBE < Uth 可靠截止条件为 uBE ≤ 0

VCC U CE(sat) RC VCC RC

饱和条件

iB > IB(Sat)

逻辑门电路

[例] 下图中,已知 ROFF 800 ,RON 3 k,试对应 输入波形定性画出TTL与非门的输出波形。

A 3.6 V 0.3 V

逻辑0 (a)

逻辑1

O Ya t

(b)

解:图(a)中,RI = 300 < ROFF 800 相应输入端相当于输入低电平, O 也即相当于输入逻辑 0 。 Yb 不同因此 TTLY 系列, R R 不同。 ON、 OFF UOH 。 a 输出恒为高电平 图(b)中,RI = 5.1 k > RON 3 k 相应输入端相当于输入高电平, O 也即相当于输入逻辑 1 。 Yb A 1 A 因此,可画出波形如图所示。

0. 3 O

t

EXIT

逻辑门电路

二、三极管的动态开关特性

数字电子技术讲义杨志忠版

第1章绪论1.1概述学习目标:了解数字电路的特点、应用概况;熟悉逻辑电平、数字信号的概念;了解数字电路的优点;了解脉冲波形的主要参数。

教学重点:区分数字信号和模拟信号的区别课时分配:2学时教学过程:信号分为两类:模拟信号、数字信号模拟信号:指在时间上和数值上都是连续变化的信号。

如电视图像和伴音信号。

数字信号:指在时间上和数值上都是断续变化的离散信号。

如生产中自动记录零件个数的计数信号。

模拟电路:对模拟信号进行传输和处理的电路数字电路:对数字信号进行传输和处理的电路1.1.2数字电路的分类(1)按集成度分类:数字电路可分为小规模(SSI,每片数十器件)、中规模(MSI,每片数百器件)、大规模(LSI,每片数千器件)和超大规模(VLSI,每片器件数目大于1万)数字集成电路。

集成电路从应用的角度又可分为通用型和专用型两大类型。

(2)按所用器件制作工艺的不同:数字电路可分为双极型(TTL型)和单极型(MOS 型)两类。

(3)按照电路的结构和工作原理的不同:数字电路可分为组合逻辑电路和时序逻辑电路两类。

组合逻辑电路没有记忆功能,其输出信号只与当时的输入信号有关,而与电路以前的状态无关。

时序逻辑电路具有记忆功能,其输出信号不仅和当时的输入信号有关,而且与电路以前的状态有关。

数字电路的产生和发展是电子技术发展最重要的基础。

由于数字电路相对于模拟电路有一系列的优点,使它在通信、电子计算机、电视雷达、自动控制、电子测量仪器等科学领域得到广泛的应用,对现代科学、工业、农业、医学、社会和人类的文明产生着越来越深刻地影响。

1.1.3数字电路的优点和特点特点:(1)工作信号是二进制的数字信号,在时间上和数值上是离散的(不连续),反映在电路上就是低电平和高电平两种状态(即0和1两个逻辑值)。

(2)在数字电路中,研究的主要问题是电路的逻辑功能,即输入信号的状态(0和1)和输出信号的状态(0和1)之间的关系。

对于电路本身有分析电路和设计电路两部分。

数字逻辑电路设计-(王毓银)讲义.PPT第一章

an1 2n1 an2 2n2 a1 21 a0 20

a1 21 a2 22 am 2m

n1

ai

1.1.2 数制及其转换

小数部分的转换步骤如下: 将小数部分逐次乘以R,取乘 积的整数部分作为R进制的各有关数位,乘积的小数部分 继续乘以R,直至最后乘积为0或达到一定的精度为止。

例4:求(0.3125)10 =(

)2

解: 0.3125 × 2 = 0.625 ……整数为0 b-1

0.625 × 2 = 1.25 ……整数为1 b-2

3基数r为2k各进制之间的互相转换由于3位二进制数构成1位八进制数4位二进制数构成1位十六进制数以二进制数为桥梁即可方便地完成基数r为2k各进制之间的互相转换

西安邮电学院“校级优秀课程”

数字电路与逻辑设计

第一章 绪 论

第一章 绪 论

目的与要求:

1、正确理解一些有关数字电路的基本概念; 2、常用数制数的表示以及它们之间的转换; 3、掌握数字系统中常用的几种BCD码。

1.1.2 数制及其转换

例6:将十进制小数(0.39)10 转换成八进制数, 要求精度达到0.1% 。

解:要求精度达到0.1% ,因为1/83 < 1/1000 < 1/84, 所以需要精确到八进制小数4位。 0.39 × 8 = 3.12 ……整数为3 b-1=3 0.12 × 8 = 0.96 ……整数为0 b-2=0 0.96 × 8 = 7.68 ……整数为7 b-3=7 0.68 × 8 = 5.44 ……整数为5 b-4=5 所以(0.39)10 =(0.3075)8

数字电路实验讲义

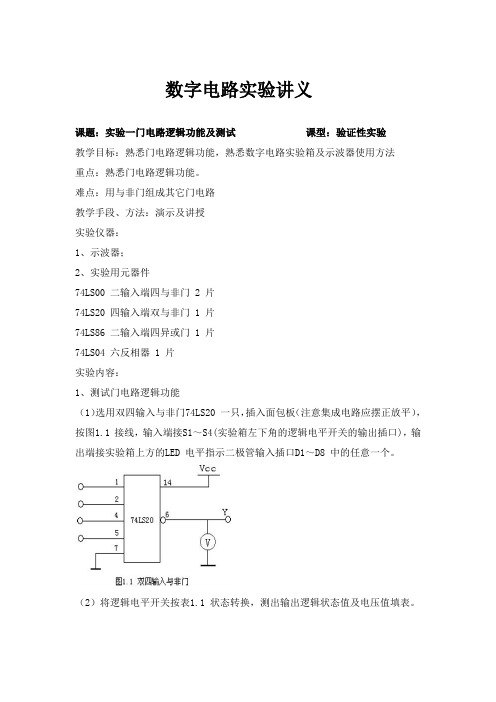

数字电路实验讲义课题:实验一门电路逻辑功能及测试课型:验证性实验教学目标:熟悉门电路逻辑功能,熟悉数字电路实验箱及示波器使用方法重点:熟悉门电路逻辑功能。

难点:用与非门组成其它门电路教学手段、方法:演示及讲授实验仪器:1、示波器;2、实验用元器件74LS00 二输入端四与非门 2 片74LS20 四输入端双与非门 1 片74LS86 二输入端四异或门 1 片74LS04 六反相器 1 片实验内容:1、测试门电路逻辑功能(1)选用双四输入与非门74LS20 一只,插入面包板(注意集成电路应摆正放平),按图1.1接线,输入端接S1~S4(实验箱左下角的逻辑电平开关的输出插口),输出端接实验箱上方的LED 电平指示二极管输入插口D1~D8 中的任意一个。

(2)将逻辑电平开关按表1.1 状态转换,测出输出逻辑状态值及电压值填表。

2、逻辑电路的逻辑关系(1)用74LS00 双输入四与非门电路,按图1.2、图1.3 接线,将输入输出逻辑关系分别填入表1.2,表1.3 中。

(2)写出两个电路的逻辑表达式。

3、利用与非门控制输出用一片74LS00 按图1.4 接线。

S 分别接高、低电平开关,用示波器观察S 对输出脉冲的控制作用。

4、用与非门组成其它门电路并测试验证。

(1)组成或非门:用一片二输入端四与非门组成或非门B==,画出电路图,测试并填+Y∙ABA表1.4。

(2)组成异或门:①将异或门表达式转化为与非门表达式;②画出逻辑电路图;③测试并填表1.5。

5、异或门逻辑功能测试(1)选二输入四异或门电路74LS86,按图1.5 接线,输入端1、2、4、5 接电平开关输出插口,输出端A、B、Y 接电平显示发光二极管。

(2)将电平开关按表1.6 的状态转换,将结果填入表中。

6、逻辑门传输延迟时间的测量用六反相器74LS04 逻辑电路按图1.6 接线,输入200Hz 连续脉冲(实验箱脉冲源),将输入脉冲和输出脉冲分别接入双踪示波器Y1、Y2 轴,观察输入、输出相位差。

数字电路课内实验讲义201004

数字电路实验讲义杭州电子科技大学2010.04实验1 数据选择器的应用1 实验目的1.了解数据选择器的电路结构和特点。

2.掌握数据选择器的逻辑功能和测试方法。

3.掌握数据选择器的基本应用。

2 实验仪器与器件3 实验原理数据选择器又称为多路开关,是一种重要的组合逻辑部件。

它是一个多路输入、单路输出的组合电路,能在通道选择信号(或称地址码)的控制下,从多路数据传输中选择任何一路信号输出。

在数字系统中,经常利用数据选择器将多条传输线上的不同数字信号,按要求选择其中之一送到公共数据线上。

另外,数据选择器还可以完成其它的逻辑功能,例如函数发生器、桶形移位器、并串转换器、波形产生器等。

(一)用门电路设计四选一数据选择器四选一数据选择器表达式为301201101001d A A d A A d A A d A A Y +++=,由表达式可以得到当A 1A 0=00时,Y=d 0;A 1A 0=01时,Y=d 1; A 1A 0=10时,Y=d 2;A 1A 0=11时,Y=d 3,这样就起到数据选择的作用。

同时由表达式可以直接用门电路设计出数据选择器电路,该电路如图2.4.1所示。

(二)双四选一数据选择器74LS153的应用74LS153数据选择器集成了两个四选一数据选择器,外形为双列直插,引脚排列如图2.4.2所示,逻辑符号如图2.4.3所示,其中D 0、D 1、D 2、D 3为数据输入端,Q 为输出端,A 0、A 1为数据选择器的控制端(地址码),同时控制两个数据选择器的输出,S 为工作状态控制端(使能端),74LS153的功能表见表2.4.1。

用数据选择器74LS153实现组合逻辑函数设计举例:当变量数等于地址端的数目时,则直接可以用数据选择器来实现逻辑函数。

现设逻辑函数F (X ,Y )=∑m (1,2),则可用一个四选一完成,根据数据选择器的定义:30120110100101D A A D A A D A A D A A )A ,Q(A +++=,令A 1=X ,A 0=Y ,1S =0(使能信号,低电平有效),1D 0=1D 3=0,1D 1=1D 2=1,那么输出Q=F 。

电子维修讲义——数字电路篇1

数字电子技朮部分数字电子技术是研究电路的‘开’、‘关’状态及其相互间的逻輯关系的,俗称为‘开关电路’。

显然,在开关电路中,其工作状态只有‘开’ 或 ‘关’ 。

所谓‘数字系统’,就是由基本的数字电路(开关电路)组成的。

与模拟电路的线性变化相比,数字电路的电信号是跳变方式,即通常称之谓‘脉冲’。

包括电路中用RC 过渡过程形成的‘脉冲电压、电流’均属数字电子技术涉及的范围。

常用‘逻輯代数’(布尔代数)来分析、表达、设计数字电路及其系统;‘二进制’也是分析、表达电路及其工作过程的重要工具。

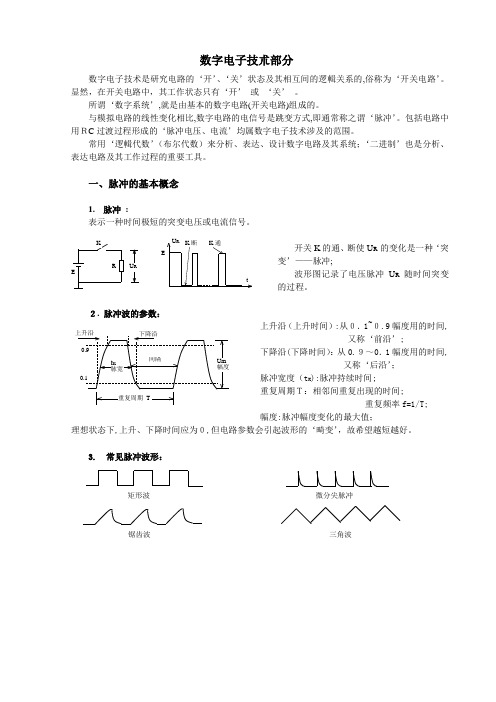

一、脉冲的基本概念1. 脉冲 :表示一种时间极短的突变电压或电流信号。

开关K 的通、断使U R 的变化是一种‘突变’——脉冲;波形图记录了电压脉冲U R 随时间突变的过程。

2. 脉冲波的参数:上升沿(上升时间):从0.1~0.9幅度用的时间,又称‘前沿’;下降沿(下降时间):从0.9~0.1幅度用的时间,又称‘后沿’; 脉冲宽度(t K ):脉冲持续时间;重复周期T:相邻间重复出现的时间;重复频率f=1/T;幅度:脉冲幅度变化的最大值;理想状态下,上升、下降时间应为0,但电路参数会引起波形的‘畸变’,故希望越短越好。

3. 常见脉冲波形:E矩形波 微分尖脉冲 锯齿波 三角波4. RC 电路充放电特点——脉冲形成的过渡过程;若:开关K 合上之前电容C 上无电压(初态为0):K 一合上,E 经R 对C 充电,u c 从0开始呈指数上升; 充电的快慢受时间常数τ= RC 约束;RC 小,充电快,u c 增长迅速;反之,缓慢; 特点:i 从最大值E/R →下降趋于0;uR 从最大值E→下降趋于0;uc 从0上升趋于E,均呈指数规律变化;若:电容C 充滿电(u c = E ),然后接通K:C将放电,从C 正端经R 到C负端;放电快慢受RC 约束,τ大→放电缓慢,τ小→放电迅速。

也呈指数规律。

从E 下降→趋于0;时间常数τ=RC 的单位为秒。