Cadence版图设计

《集成电路版图LAYOUT设计与Cadence》讲义

Set drawing layer Set layer visible Set layer selectable Set valid layer Set layer purpose pair

i. Set drawing layer

工艺信息

基本概念

5、符号,截面图,版图(top view) 对应关系

Inverter

input

VDD

PMOS s

g

b

d

NMOS d

g

b

output

s

GND

Stick-diagram

INPUT

GND

VDD

OUTPUT

Legend of each layer

N-well P-diffusion N-diffusion Polysilicon

mask

芯片代工

Wafer(die)

(Foundry)

封装 (packet)

基本概念

3、Layout design 对于整个IC design 的重要意义:

对Hale Waihona Puke 数字电路设计流程来说:Layout engineer 主要是为设计者提供经过验 证的单元版图库 (library),一般来说这样 的工作主要是由一些 Foundry 和 Service 公司来完成,对于 Fabless 来说,主要是 应用已有的库和IP Core来作布局布线,以 及验证等一些工作;

1、版图设计的重要性

▪前端设计同最终芯片产品之间的一 个重要接口; ▪芯片的品质不仅依靠前端设计的优 劣,在某些情况下,同版图设计的 联系更紧密,尤其在 analog/mixsignal/RF circuit design中。

第二章 cadence ic5141教程版图部分

第二章.Virtuoso Editing的使用简介全文将用一个贯穿始终的例子来说明如何绘制版图。

这个例子绘制的是一个最简单的非门的版图。

§ 2-1 建立版图文件使用library manager。

首先,建立一个新的库myLib,关于建立库的步骤,在前文介绍cdsSpice时已经说得很清楚了,就不再赘述。

与前面有些不同的地方是:由于我们要建立的是一个版图文件,因此我们在technology file选项中必须选择compile a new tech file,或是attach to an exsiting tech file。

这里由于我们要新建一个tech file,因此选择前者。

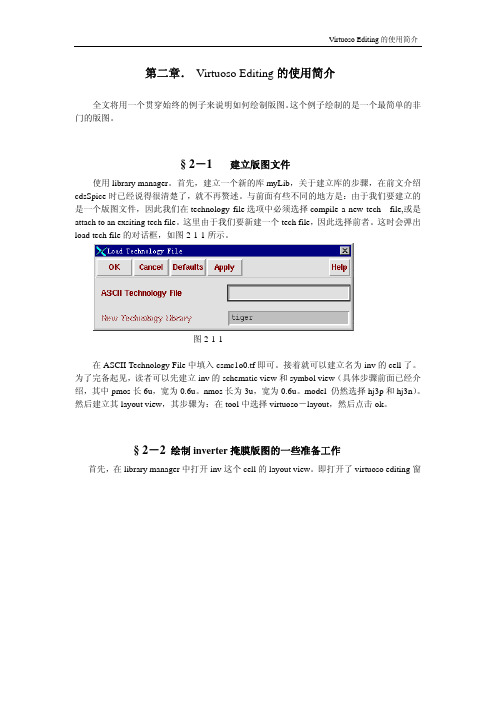

这时会弹出load tech file的对话框,如图2-1-1所示。

图2-1-1在ASCII Technology File中填入csmc1o0.tf即可。

接着就可以建立名为inv的cell了。

为了完备起见,读者可以先建立inv的schematic view和symbol view(具体步骤前面已经介绍,其中pmos长6u,宽为0.6u。

nmos长为3u,宽为0.6u。

model 仍然选择hj3p和hj3n)。

然后建立其layout view,其步骤为:在tool中选择virtuoso-layout,然后点击ok。

§ 2-2绘制inverter掩膜版图的一些准备工作首先,在library manager中打开inv这个cell的layout view。

即打开了virtuoso editing窗图2-2-1 virtuoso editing窗口口,如图2-2-1所示。

版图视窗打开后,掩模版图窗口显现。

视窗由三部分组成:Icon menu , menu banner ,status banner.Icon menu(图标菜单)缺省时位于版图图框的左边,列出了一些最常用的命令的图标,要查看图标所代表的指令,只需要将鼠标滑动到想要查看的图标上,图标下方即会显示出相应的指令。

cadence简介和使用基础

CMOS电路原理图设计

或者CIW窗口→File→Open(打开已有的 Cellview)。

CMOS电路原理图设计

也可以在Library Manager中直接打开。

Cadence的使用基础

双击Schematics,出现原理图编辑器

Cadence的使用基础

之后出现Symbol Generation Options窗口。

Cadence的使用基础

出现界面:

Cadence的使用基础

可将上图修改为惯用图形,以CMOS反相器为例。

CMOS电路原理图设计

电路仿真 仿真环境简介

Schematic图形窗口→Tools→Analog Environment。

Cadence的使用基础

Cadence的使用基础

基本工作环境

局域网资源

Cadence的使用基础

用户登陆 微机登陆后,点击桌面X-manager 图标,

Cadence的使用基础

打开X-manager图标后,点击xstart 图标,出现对话 框,进行如下设置:

Cadence的使用基础

登录时出现Linux-CDE (Common Desktop Environment) 界面

一、 cadence简介和使用

集成电路设计软件技术介绍

EDA技术的概念

EDA技术是在电子CAD技术基础上发展起来 的计算机软件系统,是指以计算机为工作平台, 融合了应用电子技术、计算机技术、信息处理 及智能化技术的最新成果,进行电子产品的自 动设计

EDA工具的功能

利用EDA工具,电子设计师可以从概念、算法、 协议等开始设计电子系统,大量工作可以通过 计算机完成,并可以将电子产品从电路设计、

Cadence SIP Layout软件在多层布线版图设计中的应用

关键 词 C d n eSPL yu 图层 a ec I a ot 规 则 布局 布 线

1 引 言

随着 电路 的数字 化 、 高速化 和小 型化要 求 , 元 器件 的集成 度越 来 越 高 , 由于 P B、 M 等 工 艺 C MC 可 以实 现 多层 布 线 , 布线 密 度 高 , 量越 来 越小 , 质 厚度越 来 越薄 , 耐机 械 冲击 性好 , 有很高 的可 靠 具

过确定主要设计参数 , 选择合理的布局布线方式 ,

完成 电路 的版 图设 计 , 从而 达到事 半功 倍 的效果 。

2 C dneSPL yu 软 件 简 介 aec I aot

C d neSP L yu( 片封 装 基 板 设计 软 件 a e c I ao t 芯 包 ) 件 是 美 国 C d ne公 司 的重 要 产 品 之 一 , 软 ae c SP是 S s m i P cae缩 写 , I yt ak g e n 意为 系 统 级 封 装 ,

C d n eSPL yu 设 计 的是 利 用 约 束 管 理 ae c I ao t

器进行 物理 约束 、 间距 约束 以及 电气 约束 等 规 则 的设 定 , 图 2所 示 , 理 约 束 ( hs a C n 如 物 P yi l o— c

s a t 管理线 路 的物 理 结构 , ti ) rn 比如 l e 布 线 ) i ( n 线

( 方通用 电子 集 团有 限公 司微 电子部 苏州 2 5 6 ) 北 1 13

摘

要

C dneSPLyu 软件 支持 系统 级协 同设计 、 aec I aot 高级 封装 3 D显 示与验证 、 线键合 及 空腔设

Cadence Virtuoso-XL设计流程

中山大学A S IC中山大学A S IC中山大学A S ICCadence Virtuoso-XL设计流程——以反相器为例,从器件生成到验证的全过程图解By研10级李志滔登陆UNIX平台,输入icfb &,进入cadence,鼠标右键选择,新建一个设计库(如mydesign),连接到SMIC0.18的工艺库中(切记)然后新建一个cell单元,用于反相器的设计。

本文档不再讨论手绘反相器版图部分,直接进入利用工艺库的元件生成版图的步骤。

首先进入电路图编辑版面:中山大学A S IC中山大学A S IC中山大学A S IC利用add—instance添加元件(快捷键为“i ”,请各位同学自己记住,下面不再重复叙述)。

按browse选择器件,如PMOS(p33)中山大学A S IC中山大学A S IC中山大学A S IC修改参数如下:主要是把器件的硅栅长度和宽度修改一下,长350nm,宽1um。

然后在主界面点击一下即生成一个器件,如图:同样生成一个NMOS,参数修改:长度350nm,宽500nm。

生成以后进行连线,得到如图所示的电路:中山大学A S IC中山大学A S IC中山大学A S IC然后添加I/O Pin:或者得到设置三个输入一个输出后得到如图所示:中山大学A S IC中山大学A S IC中山大学A S IC在virtuoso使用gen from source命令生成器件:I/O Pin修改成第一层金属(M1),然后apply中山大学A S IC中山大学A S IC中山大学A S IC接着在进行版图布局布线前,先对display进行设置:得到:中山大学A S IC中山大学A S IC中山大学A S IC重点修改左下方的display levels(显示层数),以及右上方的单元间距(snap spacing),前者能够让你看到原件的内部构造,后者能够让你修改更加精确。

然后OK,得到如下:中山大学I C 中山大学A S I C 进入CIW 窗口,options--user preferences, 把Options Displayed When Commands Start 点中,然后OK ,此后,每当你选择一个命令,都会弹出一个菜单,你可以根据你的需要进行参数修改。

Cadence采用全新可支持电学感知设计的Virtuoso版图

Cadence采用全新可支持电学感知设计的Virtuoso版图

【中国,2013 年7 月15 日】全球电子设计创新领先企业Cadence 设计系统公司(NASDAQ:CDNS) 今天宣布推出用于实现电学感知设计的Virtuoso®版图套件,它是一种开创性的定制设计方法,能提高设计团队的

设计生产力和定制IC 的电路性能。

这是一种独特的在设计中实现电学验证功能,让设计团队在创建版图时即可监控电学问题,而不用等到版图完成才能验

证其是否满足最初设计意图。

Virtuoso 版图套件EAD 功能在为工程师们缩短多达30%的电路设计周期的同时,还可优化芯片尺寸和性能。

采用这种创新的全新技术,工程师们能实时地从电学方面分析、模拟和验证

互连线决定,从而在电学上建立时便正确的版图。

这种实时的可见性让工程师

们减少了保守的设计行为或者过度设计这些行为对芯片性能和面积有负面影响。

Virtuoso 版图套件EAD 可提供:

- 从运行于Virtuoso 模拟设计环境的仿真中捕获电流和电压,并将这些电学信息传送给版图环境的能力。

- 让电路设计师能设置电学约束条件(例如匹配的电容和电阻)、并允许版图工程师实时观察这些约束条件是否得到满足的管理功能。

- 一个在版图被创建时即可对它进行快速评估、并提供设计中电学视图来进行实时分析和优化的、内置的互连线寄生参数提取引擎。

- 电迁移(EM)分析,在画版图时如果产生任何电迁移问题即提醒版图工程师注意。

- 部分版图再仿真,有助于防止错误被深藏于密布的版图,从而尽可能减少。

Cadence IC版图工具Virtuso的使用简介

建立一个库(续)

3.在CIW窗口中点击file/ new/ library….. 给库任意取名字(如:lib_1),在右侧选 compile a new techfile. (如图) 点击OK,填入工艺文件的路径和名称。

DRC检查(续)

DRC检查(续)

• 在CIW窗口中查找错误

• 回到layout中改正错误,并重新做DRC。反复修改,直到所 有错误都被修改。

LVS检查

• DRC保证了版图能够在流片中没有违规 • LVS则保证了流片出来逻辑功能的正确性。 • LVS=layout versus schematic • 步骤:

建立一个库(续)

4.在CIW窗口中点击tools/ library manager 我们就看到了新建的库lib_1 在下拉菜单中选择new/ cell view,取一个cell name:INV。 在该窗口中点击tool选择Virtuoso。 OK!这样就建立了一个画版图的平台。

如何调入版图的层

• N-Well

N-Well的规则(续)

Island and Poly

Island and Poly(续)

Poly

PLUS

PLUS(续)

Contact and Metal-1

Contact

Metal-1

Via-1

Metal-2 and Via

Metal-3

Cadence 版图工具Virtuoso简介

作者:卢俊 2006-7-5

内容安排

• 本次上机实验的任务 • 使用Virtuoso设计版图的步骤简介 • 电子58所0.5um工艺设计规则介绍

Cadence中文简明手册

CADENCE芯片版图设计工具VIRTUSO/DIV A/DRACULA入门手册 (2)1、使用V IRTUSO/D IV A/D RACULA之前的准备 (2)1.1、要找一台装有工具IC的计算机 (2)1.2、要能连接到该计算机上 (2)2、工具IC的软件环境配置 (3)2.1、创建工具IC的启动目录,即工作目录。

(3)2.3、将(.cdsinit和.cdsenv)拷贝到工具IC的启动目录 (3)2.4、在工作目录下创建工艺库文件 (3)2.5、启动工具IC,命令为icfb& (3)2.6、配置工艺库路径 (4)2.7、添加工艺提供的一些辅助库............................................................ 错误!未定义书签。

2.8、添加Multipart Path ........................................................................... 错误!未定义书签。

2.9、安装PCELL ....................................................................................... 错误!未定义书签。

3、开始一个新的设计---编辑电路图与版图 (5)3.1、新建一个设计库 (5)3.2、Attach库 (6)3.3、创建新设计 (6)3.4、编辑电路图 (7)3.5 编辑版图 (8)3.6 可以根据习惯改变版图的层次显示特性 (9)3.7、完成版图编辑之后先保存再退出 (10)4版图的DRC检查 (10)4.1、基于Diva的方式 (10)4.2、基于Dracula的方式 (10)5、LVS (12)5.1、准备版图的GDS文件 (12)5.2、准备电路网表 (12)5.3、用LOGLVS转换电路网表成LVS要求格式 (14)5.4、修改lvs的命令文件 (14)5.6、运行dracula来生成lvs任务的可执行文件 (14)5.7、在控制台下,运行文件 (14)5.8、查看错误 (14)5.9、修改 (15)6、PAD相关 (15)6.1、准备pad库 (15)6.2、导入pad版图的GDS文件 (15)6.3、更新gds和cdl (16)6.4、修改cdl (16)7、一些小经验 (17)8、附件清单 (18)9、后记 (18)Cadence芯片版图设计工具Virtuso/Diva/Dracula入门手册(以上华0.6um DPDM工艺设计库为例)Cadence 是一套功能强大的EDA软件,包含有诸如IC、SE等常用芯片设计工具。

cadence画版图快捷键总结(2021年整理精品文档)

cadence画版图快捷键总结编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望(cadence画版图快捷键总结)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为cadence画版图快捷键总结的全部内容。

cadence快捷键总结2009—03—28 11:10Cadence版图布局软件Virtuso Layout Editor快捷键归纳(也就是Virtuso中说的Bindkey)写在前面:以下我所归纳的快捷键是我在版图培训时通过阅读Cadence帮助文件和菜单命令一个个试出来的,有些我只知道作用而暂时想不到相应的中文翻译。

还有一些快捷键帮助文件中有,但我试了没用,可能是要在Unix下吧^_^.希望对学版图设计的有所帮助吧。

有不妥的地方还请多多指教啊.首先介绍下鼠标操作吧。

单击左键选中一个图形(如果是两个图形交叠的话,单击左键选中其中一个图形,再单击选中另一个图形)用左键框选,选中一片图形,某个图形要被完全包围才会被选中。

中键单击调出常用菜单命令(很少用,要点两下,麻烦.我们有快捷键的嘛)右键点击拖放用来放大。

放大后经常配合F键使用,恢复到全部显示.配合Tab 键使用,平移视图。

右键还有“Strokes”,就是点住右键画些图线,就能实现调用某些命令.Shift+左键加选图形,Ctrl+左键减选图形。

(Cadence菜单中大写表示+按shift,Ctrl写成^)F1 显示帮助窗口.F2 保存.F3 这个快捷键很有用,是控制在选取相应工具后是否显示相应属性对话框的.比如在选取Path工具后,想控制Path的走向,可以按F3调出对话框进行设置. F4 英文是Toggle Partial Select,就是用来控制是否可以部分选择一个图形。

Cadnece版图设计技巧总结

Cadnece版图设计技巧总结Cadence 版图设计技巧总结在集成电路设计领域,Cadence 版图设计是至关重要的环节。

它不仅关系到芯片的性能、功耗和可靠性,还直接影响到芯片的制造成本和生产周期。

对于版图设计师来说,掌握一些实用的技巧能够显著提高设计效率和质量。

接下来,就让我们一起深入探讨 Cadence 版图设计中的那些关键技巧。

一、布局规划良好的布局规划是成功版图设计的基础。

在开始设计之前,需要对整个芯片的功能模块进行合理划分,并确定它们之间的连接关系。

这有助于减少布线长度,降低寄生电容和电阻,从而提高芯片的性能。

首先,要考虑电源和地的分布。

电源和地网络应该尽可能地均匀分布,以减少电压降和噪声。

可以采用多层金属来构建电源和地的平面,以提供低阻抗的路径。

其次,对于高速信号线路,要尽量缩短其走线长度,并避免穿越其他信号密集区域。

同时,要注意信号之间的隔离,以防止串扰。

另外,在布局时还要预留足够的空间用于放置 ESD(静电放电)保护器件、测试结构和封装引脚等。

二、器件匹配在模拟和混合信号电路中,器件的匹配性对性能有着重要影响。

为了实现良好的匹配,需要遵循一些原则。

首先,将需要匹配的器件放置在相邻位置,并采用相同的方向。

这样可以减少由于工艺偏差引起的不匹配。

其次,对于对称的电路结构,要保持布局的对称性。

例如,差分放大器的两个晶体管应该具有相同的环境和布局。

此外,在布线时,要确保匹配器件的连线长度和宽度相同,并且走在相同的层次上。

三、布线策略布线是版图设计中的关键步骤之一。

合理的布线策略可以减少信号延迟、串扰和功耗。

对于电源线和地线,要使用较宽的金属线来降低电阻。

同时,要避免出现锐角和狭窄的通道,以防止电流集中和电迁移现象。

对于信号线,要根据信号的频率和特性选择合适的布线层次。

高频信号通常需要走在顶层金属层,以减少寄生电容。

在布线过程中,要注意控制走线的阻抗,以保证信号的完整性。

另外,要合理设置过孔的数量和位置。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cadence cdsSPICE 使用说明

0.6u

1.5u

0.6u(gate length) 6u(gate width) 3.6u

图 2-2-5 display resource editor 3.画整个 pmos

为了表明我们画的是 pmos 管,我们必须在刚才图形的基础上添加一个 pselect 层,这一层 将覆盖整个有源区 0.6u。接着,我们还要在整个管子外围画上 nwell,它覆盖有源区 1.8u。 如下图所示:

口

图 2-2-3 edit layers 2. 在 technology library 中选择库 mylib,先使用 delete 功能去除不需要的层次。然后点击

add 添加必需的层次,add 打开如下图的窗口:

第 4 页 共 78 页

Cadence cdsSPICE 使用说明

图 2-2-4 其中,layer name 中填入所需添加的层的名称。Abbv 是层次名称缩写。Number 是系统给层 次的内部编号,系统保留 128-256 的数字作为其默认层次的编号而将 1-127 留给开发者创 造新层次。Purpose 是所添加层次的功用,如果是绘图层次,一般选择 drawing。Priority 是 层次在 LSW 中的排序位置。其余的选项一般保持默认值。在右边是图层的显示属性。可以 直接套用其中某些层次的显示属性。也可以点击 edit resources 自己编辑显示属性。如图 2-2-5 所示(这个窗口还可以在 LSW 中调出) 编辑方法很简单,读者可以自己推敲,就不再赘 述。上述工作完毕后就得到我们所需的层次。接着我们就可以开始绘制版图了。

制时是否有同设计规则不符的地方。

第 9 页 共 78 页

Cadence cdsSPICE 使用说明

第三章 Diva 验证工具使用说明

版图绘制要根据一定的设计规则来进行,也就是说一定要通过 DRC(Design Rule Checker)检查。编辑好的版图通过了设计规则的检查后,有可能还有错误,这些错误不是 由于违反了设计规则,而是可能与实际线路图不一致造成。版图中少连了一根铝线这样的小 毛 病 对 整 个 芯 片 来 说 都 是 致 命 的 , 所 以 编 辑 好 的 版 图 还 要 通 过 LVS ( Layout Versus Schematic)验证。同时,编辑好的版图通过寄生参数提取程序来提取出电路的寄生参数, 电路仿真程序可以调用这个数据来进行后模拟。下面的框图可以更好的理解这个流程。

连,因此我们必须得借助 metal1 完成连接。具体步骤是: a. 在两 mos 管之间画一个 0.6 乘 0.6 的 contact b. 在这个 contact 上覆盖 poly,过覆盖 0.3u c. 在这个 contact 的左边画一个 0.6 乘 0.6 的 via,然后在其上覆盖 metal2(dg),

0.3u。 3. 为完成衬底连接,我们必须在衬底的有源区中间添加一个 contact。这个 contact 每

边都被 active 覆盖 0.3u。 4. 画用于电源的金属连线,宽度为 3u。将其放置在 pmos 版图的最上方。 布线完毕后的版图如下图所示:

第 7 页 共 78 页

Cadence cdsSPICE 使用说明

Cadence cdsSPICE 使用说明

第二章. Virtuoso Editing 的使用简介

全文将用一个贯穿始终的例子来说明如何绘制版图。这个例子绘制的是一个最简单的非 门的版图。

§ 2-1 建立版图文件

使用 library manager。首先,建立一个新的库 myLib,关于建立库的步骤,在前文介绍 cdsSpice 时已经说得很清楚了,就不再赘述。与前面有些不同的地方是:由于我们要建立的 是一个版图文件,因此我们在 technology file 选项中必须选择 compile a new tech file,或是 attach to an exsiting tech file。这里由于我们要新建一个 tech file,因此选择前者。这时会弹出 load tech file 的对话框,如图 2-1-1 所示。

§ 2-3 绘制版图

一.画 pmos 的版图(新建一个名为 pmos 的 cell) 1. 画出有源区 在 LSW 中,点击 active(dg),注意这时 LSW 顶部显示 active 字样,说明 active 层 为当前所选层次。然后点击 icon menu 中的 rectangle icon,在 vituoso editing 窗口中 画一个宽为 3.6u,长为 6u 的矩形。这里我们为了定标,必须得用到标尺。点击 misc/ruler 即可得到。清除标尺点击 misc/clear ruler。如果你在绘制时出错,点击需 要去除的部分,然后点击 delete icon。 2. 画栅 在 LSW 中,点击 poly(dg),画矩形。与有源区的位置关系如下图:

§ 2-2 绘制 inverter 掩膜版图的一些准备工作

首先,在 library manager 中打开 inv 这个 cell 的 layout view。即打开了 virtuoso editing 窗

第 1 页 共 78 页

Cadence cdsSPICE 使用说明

口,如图 2-2-1 所示。

第 6 页 共 78 页

Cadence cdsSPICE 使用说明

pselect nwell

00.6u0.6u 1.8u

4.衬底连接 pmos 的衬底(nwell)必须连接到 vdd。首先,画一个 1.2u 乘 1.2u 的 active 矩形;然后

在这个矩形的边上包围一层 nselect 层(覆盖 active0。6u)。最后将 nwell 的矩形拉长,完成 后如下图所示:

Undo

------- 取消编辑(u)

Redo

-------恢复编辑 (U)

Move

------- 移动(m)

Stretch

------- 伸缩(s)

Rectangle -------编辑矩形图形(r)

Polygon

------- 编辑多边形图形(P)

Path

------- 编辑布线路径(p)

Copy

应的指令。

menu banner(菜单栏),包含了编辑版图所需要的各项指令,并按相应的类别分组。几 个常用的指令及相应的快捷键列举如下:

Zoom In

-------放大 (z)

Zoom out by 2------- 缩小 2 倍(Z)

Save

------- 保存编辑(f2)

Delete

------- 删除编辑(Del)

图 3-0-1 IC 后端工作流程 验证工具有很多,我们采用的是 Cadence 环境下集成的验证工具集 DIVA。下面先对 DIVA 作一个简单介绍。 DIVA 是 Cadence 软件中的验证工具集,用它可以找出并纠正设计中的错误:它除了可 以处理物理版图和准备好的电气数据,从而进行版图和线路图的对查(LVS)外。还可以在 设计的初期就进行版图检查,尽早发现错误并互动地把错误显示出来,有利于及时发现错误 所在,易于纠正。 DIVA 工具集包括以下部分: 1. 设计规则检查(iDRC) 2. 版图寄生参数提取(iLPE) 3. 寄生电阻提取(iPRE)

过覆盖 0.3u d. 用 metal1 连接 via 和 contact,过覆盖为 0.3u 从下图中可以看得更清楚:

via

contact

metal2

metal1

poly 3. 输出:先将两版图右边的 metal1 连起来(任意延长一个的 metal1,与另一个相交)。

然后在其上放置一个 via,接着在 via 上放置 metal2。 五.作标签

-------复制编辑 (c)

status banner(状态显示栏),位于 menu banner 的上方,显示的是坐标、当前编辑指

令等状态信息。

在版图视窗外的左侧还有一个层选择窗口(Layer and Selection Window LSW)。

第 2 页 共 78 页

Байду номын сангаас

Cadence cdsSPICE 使用说明

标签

Poly

多晶硅,做 mos 的栅

下图是修改后的 LSW。

第 3 页 共 78 页

Cadence cdsSPICE 使用说明

图 2-2-2 LSW 如何来修改 LSW 中的层次呢?以下就是步骤: 1. 切换至 CIW 窗口,在 technology file 的下拉菜单中选择最后一项 edit layers 出现如图窗

图 2-3-1 pmos 版图 通过以上步骤我们完成了 pmos 的版图绘制。接下来我们将绘制出 nmos 的版图。 三.画 nmos 的版图 绘制 nmos 管的步骤同 pmos 管基本相同(新建一个名为 nmos 的 cell)。无非是某些参 数变化一下。下面给出 nmos 管的图形及一些参数,具体绘制步骤就不再赘述。

1. 在 LSW 中选择层次 text(d3),点击 create/label,在弹出窗口中的 label name 中填 入 vdd!并将它放置在版图中相应的位置上。

2. 按同样的方法创制 gnd!、A 和 Out 的标签。完成后整个的版图如下:

图 2-3-4 非门的版图 至此,我们已经完成了整个非门的版图的绘制。下一步将进行 DRC 检查,以检查版图在绘

说明

Nwell

N阱

Active

有源区

Pselect

P 型注入掩膜

Nselect

N 型注入掩膜

Contact

引线孔,连接金属与多晶硅/有源区

Metal1

第一层金属,用于水平布线,如电源和地

Via