Cadence 16.2 学习笔记(一)

Cadence Allegro 16.2规则设置

Spacing规则(约束)Rexdlutarm@2009-07-02 Allegro 16.0以后版本的约束规则设置较之前有很大改变,对于用惯了15.x的人来说,很多不习惯新的约束管理器。

和在对待女人的态度上,恰相反。

80后说90后脑残,15.7说16.2脑残,Xp说Vista脑残。

Vista确实很脑残。

新事物取代旧事物是自然界发展的客观规律。

说明:1本文只介绍了Spacing约束的设置,因为Physical规则通常来说都设置的非常简单。

掌握了Spacing规则Physical规则对你来说一定是小Case。

另外,Physical 规则的设置也写的话,一定显得都是在重复Spacing的设置;2文中所有的规则(约束),如不特殊说明默认情况下均指Spacing规则(约束);3对于Electrical的约束,是另一种约束,本文不作讨论。

约束的设置方式:1直接的:Net中写数值,2 间接的:创建Constraint Set,然后Assign给Net;这两种都很常用,后者管理方便。

在Physical和Spacing设置中用后者比较好,但是在Electrical中,我看到很多很多的人会混合使用。

使用第二种约束设置方式的约束设置步骤:1约束的对象2约束的内容3给对象分配内容1这3个步骤默默的引导着所有间接约束的设置。

基本约束预备先理解:Net class2Net class-classRegionRegion-classRegion-class-classBus……现在不理解,想跳过去。

没关系,你早晚都要理解的。

最简单和稍微复杂一点的约束:最简单的就是default的约束,稍微复杂一点的就是修改了一点默认的约束。

再复杂一些的约束:你可能会想让不断变化的CLK(我们不考虑是不是差分)和其他的线离的远一些。

在Constraint Set中Create规则并设置规则的内容:Creat & Set之后3给Net分配规则:更高级的约束:What Can U Think?有了一根线的约束,贪婪的本性会使你你很快上升到两根线(通常是Diff)和更多线的约束。

(整理)Cadence_SPB16.2入门教程——PCB布线.

Cadence_SPB16.2入门教程——PCB布线(一)PCB布线4.1 PCB层叠结构层叠结构是一个非常重要的问题,不可忽视,一般选择层叠结构考虑以下原则:·元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;·所有信号层尽可能与地平面相邻;·尽量避免两信号层直接相邻;·主电源尽可能与其对应地相邻;·兼顾层压结构对称。

对于母板的层排布,现有母板很难控制平行长距离布线,对于板级工作频率在 50MHZ以上的(50MHZ以下的情况可参照,适当放宽),建议排布原则:·元件面、焊接面为完整的地平面(屏蔽);·无相邻平行布线层;·所有信号层尽可能与地平面相邻;·关键信号与地层相邻,不跨分割区。

基于以上原则,对于一个四层板,优先考虑的层叠结构应该是:·S ←信号·G ←地平面·P ←电源层·S ←信号对于一个六层板,最优的层叠结构是:·S1 ←信号·G1 ←地平面·S2 ←信号·G2 ←地平面·P ←电源层·S4 ←信号对于一个八层板,有两种方案:方案 1:方案2:·S1 ←信号S1 ←信号·G1 ←地平面G1 ←地平面·S2 ←信号S2 ←信号·G2 ←地平面P1 ←电源层·P ←电源层G2 ←地平面·S3 ←信号S3 ←信号·G3 ←地平面P2 ←电源层·S4 ←信号S4 ←信号方案2主要是比方案1多了一个电源层,在电源比较多的情况下可以选择方案2。

对于更多层的结构也是按照上面的原则来定,可以参考其它的资料。

下面以SMDK6410核心板(设计为八层板)来设置层叠结构,包括规则设置,PCB布线等。

打开程序->Cadence SPB 16.2->PCB Editor,然后打开在第3 章布局好的PCB文件。

Cadence学习笔记

Cadence学习笔记Cadence学习笔记1__焊盘一、焊盘前期准备在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。

元件封装大体上分两种,表贴和直插。

针对不同的封装,需要制作不同的Padstack。

名词解释不同层的名词解释:Begin Layer:最上面的铜Default Internal:中间层End Layer:最下面的铜Solder Mask:阻焊层、绿油层。

是反显,有就是没有。

等于是开了个小孔不涂绿油,是为了把焊盘或是过孔露出来,不涂绿油就是亮晶晶的铜,也就是在板子上看到的焊盘,或者是一个个的孔,其它的部分都上阻焊剂,也就是绿油,其实不光是绿色的,还有红色的、黑色的、蓝色的等等。

Paste Mask:助焊层、钢网层、锡膏防护层、锡膏层,也叫胶贴、钢网、钢板。

是正显,有就是有。

等于是钢网开了个窗,过波峰焊时机器就在此窗口内喷上焊锡了。

这一层是针对表面贴装(SMD)元件的,其实不光是表贴,通孔也要用到,因为通孔的表面上也有个焊盘,该层用来制作钢板﹐而钢板上的孔就对应着电路板上的SMD器件的焊点。

在表面贴装(SMD)器件焊接时﹐先将钢板盖在电路板上(与实际焊盘对应)﹐然后将锡膏涂上﹐用刮片将多余的锡膏刮去﹐移除钢板﹐这样SMD器件的焊盘就加上了锡膏,之后将SMD器件贴附到锡膏上面去(手工或贴片机)﹐最后通过回流焊机完成SMD器件的焊接。

通常钢板上孔径的大小会比电路板上实际的焊盘小一些。

Film Mask:预留层,用于添加用户自定义信息,根据需要使用。

不同焊盘的名词解释:Regular Pad:实际焊盘、规则焊盘,正片中使用,也是通孔焊盘的基本焊盘。

可以是:Null、Circle 圆型、Square 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、Shape形状(可以是任意形状)。

Thermal Relief:热焊盘、热风焊盘、花焊盘、防散热焊盘。

cadence学习1

cadence学习11.建立通孔类焊盘,一般都要先出一个flash symbol花焊盘,也叫热风焊盘,防散热热分焊盘。

热风焊盘有以下两个作用:(1)防止散热。

由于电路板上电源和地是由大片的铜箔提供的,所以为了防止因为散热太快而造成虚焊,故电源和接地过孔采用热风焊盘形式;(2)防止大片铜箔由于热胀冷缩作用而造成对过孔及孔壁的挤压,导致孔壁变形。

(3)连接作用2.通孔焊盘尺寸确定以及制作封装的制作必须依据数据手册中的尺寸,DIP元件引脚要与通孔公差配合良好(通孔直径大于元件引脚直径8-20mil)。

为使封装孔径序列化,40mil以上按照5mil递增,即40mil,45mil,50mil,.....;40mil以下按照4mil递减,即36mil,32mil,28mil,24mil,20mil,16mil,12mil,8mil。

元件引脚直径与PCB焊盘孔径(钻孔孔径)的大小关系如下表所示:由表中数据,若元件数据手册上引脚直径D=18mil,则PCB焊盘孔径(钻孔孔径)计算可得D+12mil=30mil,为了保证尺寸序列化,这里取为32mil。

由于焊盘黏锡部分的宽度要保证大于10mil(相对于焊盘孔径,即钻孔孔径),所以盘面尺寸可选择成50mil。

根据Allegro命名规则,所学制作的焊盘名为pad50sq32d和pad50cir32d。

焊盘名称表示的含义如下:(1)Pad表示是一个焊盘(2)50代表焊盘外形大小为50mil(3)cir代表焊盘的外形为圆形,sq代表正方形(4)32代表焊盘的钻孔孔径为32mil(5)d代表钻孔孔壁上必须上锡(PTH,PLATED THROUGH HOLE),用来导通各层面焊盘尺寸大小一般设置如下:DRILL_SIZE(钻孔大小)>=PHYSICAL_PIN_SIZE+10MIL(确定)Regular Pad(焊盘外形大小)>=DRILL_SIZE+16MIL(DRILL SIZE<50)Regular Pad(焊盘外形大小)>=DRILL_SIZE+30MIL(DRILL SIZE>=50)一般情况下,焊盘比钻孔大20mil。

Cadence_SPB16.2中文教程

2

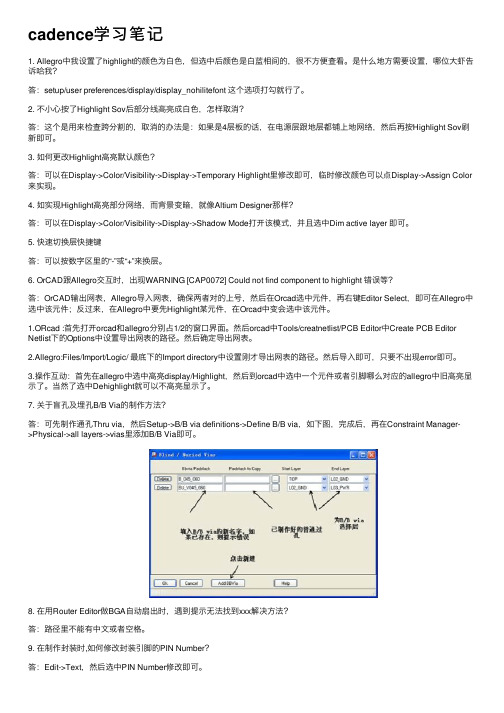

图 1.3 表贴元件焊盘设置

如果是通孔焊盘,需要填写的参数有: BEGINLAYER 层的 Regular Pad,Thermal Relief,Anti Pad; DEFAULTINTERNAL 层的 Regular Pad,Thermal Relief,Anti Pad; ENDLAYER 层的 Regular Pad,Thermal Relief,Anti Pad; SOLDEMASK_TOP 层的 Regular Pad; PASTEMASK_TOP 层的 Regular Pad。 如图 1.4 所示。 在 BEGINLAYER、DEFAULTINTERNAL、ENDLAYER 三个层面中的 Thermal Relief 可以 选择系统提供的默认连接方式,即 Circle、Square、Oblong、Rectangle、Octagon 五种,在 PCB 中这几种连接方式为简单的‘+’形或者‘X’形。也可以选用自己画的热风焊盘连接 方式,即选择 Flash。这需要事先做好一个 Flash 文件(见第二节)。这些参数的设置见下面的 介绍。

第 2 章 建立封装 .......................................................................................................10

第 3 章 元器件布局 ...................................................................................................23

第 5 章 输出底片文件 ...............................................................................................70

Cadence快速入门视频教程的SPB_16.2版本一

2. 教程内容

3. 软件介绍 Design Entry CIS:板级原理图工具 Design Entry HDL:设计芯片的原理图工具,板级设计不用 Layout Plus:OrCAD 自带的 PCB 布线工具,功能不如 PCB Editor 强大 Layout Plus SmartRoute Calibrate:OrCAD 自带的 PCB 布线工具,功能不如 PCB Editor 强大 PCB Editor:Cadence 的 PCB 布线工具 PCB Librarian:Cadence 的 PCB 封装制作工具 PCB Router:Cadence 的自动布线器 PCB SI:Cadence 的 PCB 信号完整性信号仿真的工具 SigXplorer:Cadence 的 PCB 信号完整性信号仿真的工具

接下来,设置输入管脚的正负属性 :点击 Toolbar 的 Place Text,或者菜单 Place/Text,如下图:

输入-,点击 OK,再输入+,点击 OK, 如下图: 接下来放置管脚,如下图:

现在,完成了 NE5532 中两个运放中的一个,现在编辑另一个:

Ctrl+N,或者 View/Next Part,如下图:

4. 软件列表

5. 开始学习 Design Entry CIS 启动:Start/Cadence SPB 16.2/Design Entry CIS 启动后,显示下图:

里面有很多选项,应该是对应不同的 License

本教程使用:OrCAD Capture CIS 我个人认为:Allegro PCB Design CIS XL 是所有可选程序中,功能最强大的,但不知道,强在哪里;而且 本教程的原理图文件可以使用上表中不同的程序打开 6. 选择 OrCAD Capture CIS,启动后显示下图

Cadence_Allegro16.2学习记录

Cadence_Allegro16.2学习记录Orcad中图纸模版的设置1.Option—>Design Template—>Title Block,Symbol栏中输入Title Block所在的.OLB库文件位置(E:\cadence_design\schlib\DIDIDEV.OLB),Title Block中输入模版文件名“TitleBlock_SHU”,内有公司的logo。

2.Text栏内Title中输入正在设计的板的名称,Document Number中输入文件编号,Revision中输入版本号。

3.在添加新页时,模版图纸的上述信息会自动添加Orcad 中快速修改所有零件的Footprint方法一:一页一页修改,打开某页,按CTRL+A,选中当前页所有器件,再点右键,选Edit属性,在弹出对话框中选Parts栏,按要修改REF 排序,用左键拖拉要修改的为同种封装器件再点右键,然后击EDIT,填入封装就成批修改了方法二:选择顶层原理图(SCHEMATIC1),右键选Edit Object Properties,列出所有元件,找到PCB Footprint 那项,可以逐个填入,也可以相同封装填一个,然后拖动该黑框的右下角十字形复制。

Orcad BOM表中输出原件的PCBfootprint封装型号选中顶层项目设计.dsn标题,在tools菜单中选择bill of materials,在header栏追加填入“\tPCBFootPrint”,在Combined property string栏中追加填入“\t{PCB footprint}”,不选Open in Excel,生成.BOM文件后,用excel手工导入.BOM文件,在导入步骤三中选择“文本”方式。

然后在Excell 中修改BOM表的边框等格式。

Orcad还有一处地方可输出带有机械尺寸的BOM表,选中顶层项目设计.dsn标题,在report菜单中选择CIS bill of Materials,有standard和Crystal report两种形式输出。

cadence学习笔记

cadence学习笔记1. Allegro中我设置了highlight的颜⾊为⽩⾊,但选中后颜⾊是⽩蓝相间的,很不⽅便查看。

是什么地⽅需要设置,哪位⼤虾告诉哈我?答:setup/user preferences/display/display_nohilitefont 这个选项打勾就⾏了。

2. 不⼩⼼按了Highlight Sov后部分线⾼亮成⽩⾊,怎样取消?答:这个是⽤来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地⽹络,然后再按Highlight Sov刷新即可。

3. 如何更改Highlight⾼亮默认颜⾊?答:可以在Display->Color/Visibility->Display->Temporary Highlight⾥修改即可,临时修改颜⾊可以点Display->Assign Color 来实现。

4. 如实现Highlight⾼亮部分⽹络,⽽背景变暗,就像Altium Designer那样?答:可以在Display->Color/Visibility->Display->Shadow Mode打开该模式,并且选中Dim active layer 即可。

5. 快速切换层快捷键答:可以按数字区⾥的“-”或“+”来换层。

6. OrCAD跟Allegro交互时,出现WARNING [CAP0072] Could not find component to highlight 错误等?答:OrCAD输出⽹表,Allegro导⼊⽹表,确保两者对的上号,然后在Orcad选中元件,再右键Editor Select,即可在Allegro中选中该元件;反过来,在Allegro中要先Highlight某元件,在Orcad中变会选中该元件。

1.ORcad :⾸先打开orcad和allegro分别占1/2的窗⼝界⾯。

然后orcad中Tools/creatnetlist/PCB Editor中Create PCB Editor Netlist下的Options中设置导出⽹表的路径。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

D:\Cadence\SPB_16.3\share\pcb\pcb_lib\symbols

原理图操作

Friday, September 07, 2012

12:47 PM

为什么我的cadence16。

3绘制原理图DRC 检测没问题之后,生成网表出现错误呢error initializing COM property pages:

无效指针

•

•

I'm using 16.2 demo version on the 64bit version of Windows 7. When I try to create a netlist, it generates generates an error message saying:

"Error initializing COM property pages: Invalid pointer"

The netlist creation window has a blank PCB Editor tab, in which I can't generate a netlist for PCB Editor.Anyone knows the solution?

Thanks.

I found the (partial) solution as following:

Error while creating a netlist in Capture

My operating system is Vista. I get the error -“Error initializing COM property pages: Invalid pointer ”while trying to generate the Allegro net list.

PROBLEM:

While creating a netlist in OrCAD Capture 9.2.3, the following error message appears “Error initializing COM property pages: Invalid pointer ”. Why?

SOLUTION:

This error message appears because of an improper entry in the registry of the pxllite.OCX file. You can solve this problem in the following tree ways:

Solution 1: Manually register the Dynamic Link Libraries (.DLL). To manually register the pxllite.ocx file:

1. Choose Start > Run to open the Run window.

2. Type cmd to open the command line window (CTRL+right click, run as admin)

3. Go to <Install_dir>\tools\capture, where <Install_dir> is the path for the OrCAD Capture installation directory.

4. Type the following two commands, one at a time in the command line window: regsvr32 pxllite.ocx

regsvr32 truereuse.ocx

Netlist 创建

Friday, September 07, 2012

10:57 PM

After each command the following message box appears one after the another: DllRegisterServer in pxllite.ocx succeeded and DllRegisterServer in truereuse.ocx succeeded. If the above message appears, then it should remove the problem of "Error initializing COM property pages".

Pasted from </Community/forums/t/14362.aspx>

只要以管理员身份运行OrCAD Capture CIS就可以了

报告

Friday, September 07, 2012 11:23 PM

Cadence元件库制作Wednesday, September 05, 2012 9:21 AM

焊盘制作Thursday, September 06, 2012 2:54 PM

不规则焊盘Thursday, September 06, 2012 10:42 PM

创建电路板Friday, September 07, 2012 11:49 AM

导入网表Friday, September 07, 2012 11:31 PM

的是非电气栅格点。