BGA封装的PCB_layout指导规则

PCB Layout标准规范

目錄一、目的------------------------------------------------------------------------ 3二、範圍---------------------------------------------------------- 3三、說明----------------------------------------------------------------------- 3四、實施日期------------------------------------------------------------------3五、注意事項及規則須知之訂定程序------------------------------------ 3六、應準備之事項-------------------------------------------------------4七、注意事項及規則須知-------------------------------------------------------4八、注意事項------------------------------------------------------------------------- 178.1M e m b r a n e L a y o u t17 8.2K e y b o a r d P C18 8.3K e y b o a r d D I E18 附錄一------------------------------------------------------------------19 附錄二:F R4a n d F R1L a y o u t注意事項----------------------20 附錄三:C o s t D o w n零件尺寸圖------------------------------21一、目的使PCB Layout之作業規則標準化。

pcb板bga焊盘规则

pcb板bga焊盘规则在PCB(Printed Circuit Board,印刷电路板)设计中,BGA(Ball Grid Array,球栅阵列)是一种常见的封装技术,而焊盘规则对于确保良好的焊接和可靠性至关重要。

以下是在设计PCB板时涉及BGA焊盘的一些规则和注意事项:●焊盘布局:确保BGA焊盘的布局合理,要保持均匀间距和对称性。

避免在BGA阵列中创建不规则的间距或过于密集的焊盘。

●焊盘尺寸:焊盘的尺寸应该足够大,以提供足够的焊接表面积。

较大的焊盘有助于提高焊接的可靠性,并减少由于热膨胀等因素引起的问题。

●焊盘间距:控制相邻焊盘之间的间距,以防止短路或焊接问题。

间距的选择通常依赖于BGA封装的规格,可以参考制造商的建议。

●焊盘形状:通常,BGA焊盘的形状是圆形,但也可以是椭圆形。

确保选择合适的形状,以满足设计要求和制造能力。

●阻焊沉积:在焊盘上应用阻焊沉积以保护它们免受环境的影响。

这有助于防止氧化和其他腐蚀问题,并提高焊接的可靠性。

●过孔设计:如果BGA封装需要连接到内部层,确保通过在相应的焊盘位置安排过孔来实现连接。

过孔可以提供电气连接以及散热的通道。

●热沉和散热设计:对于需要散热的BGA组件,确保周围的热沉设计足够。

这有助于维持适当的温度,防止过热导致焊接问题。

●BGA排列规则:确保BGA焊盘按照指定的排列规则放置,以确保正确的连接和通信。

检查制造商规范:仔细阅读BGA封装的制造商规范和建议,这通常包含有关焊盘设计和其他关键参数的详细信息。

在PCB设计中,BGA焊盘的设计需要综合考虑电气、热学和制造方面的因素。

与制造商的沟通以及使用专业的PCB设计工具可以帮助确保设计符合最佳实践和规格。

bga设计准则

bga设计准则BGA设计准则BGA(Ball Grid Array)是一种常用的集成电路封装技术,它通过将芯片引脚与印制电路板上的焊球连接,实现电子设备的连接和传输功能。

在进行BGA设计时,需要遵循一些准则,以确保设计的可靠性和稳定性。

本文将介绍BGA设计的几个关键准则。

一、布局与走线在进行BGA布局时,应注意将高速信号线与电源线分开布局,以减少互相干扰的可能性。

同时,还要尽量缩短信号线的长度,以降低信号的延迟和损耗。

在进行BGA走线时,应尽量避免交叉走线和直角转弯,以减少信号的串扰和反射。

此外,还要合理规划BGA芯片的引脚分配,以确保信号的良好传输。

二、电源和地线设计在BGA设计中,电源和地线的布局非常重要。

应尽量减少电源和地线的长度,同时避免共享电源和地线。

为了提高电源的稳定性,可以采用多层板设计,在内层板中布线电源和地线。

此外,还要注意电源和地线的宽度和厚度,以满足电流的要求。

三、热管理BGA芯片在工作过程中会产生大量的热量,因此需要进行有效的热管理。

首先,应合理规划散热器的位置和大小,以确保散热器能够有效地散热。

其次,可以采用散热片、散热胶等散热材料来提高散热效果。

此外,还可以在设计中加入风扇或冷却器等辅助散热设备。

四、焊球布局焊球是连接BGA芯片和印制电路板的重要组成部分,它的布局也需要注意。

首先,应确保焊球的数量和尺寸满足设计要求,以确保连接的可靠性。

其次,焊球的间距和间隔要合理,以避免短路和焊接不良的问题。

此外,还要注意焊球的排列方式,可以采用对角排列或交错排列,以提高焊接的可靠性。

五、信号完整性在进行BGA设计时,要注意信号的完整性。

首先,应合理规划信号的传输路径,避免信号的干扰和损耗。

其次,可以采用差分信号传输和终端匹配等技术,提高信号的抗干扰能力和传输质量。

此外,还要进行信号的仿真和分析,以确保信号的稳定性和可靠性。

总结起来,BGA设计的准则包括布局与走线、电源和地线设计、热管理、焊球布局以及信号完整性等方面。

最全的PCBLayout规范

最全的PCBLayout规范PCB Layout规范PCB Layout规范⼀、安全间距1. LN之间3mm以上,空间距离1.8mm以上,不⾜时开1mm以上的槽增加沿⾯距离。

2. 初次级间6.4mm以上,空间距离5mm以上,不⾜时开1mm以上的槽增加沿⾯距离。

3. 初级与外壳地4.5mm以上,空间距离3mm以上,不⾜时开1mm以上的槽增加沿⾯距离。

4.⾼压与地之间铜箔距离1mm以上,其它⽆要求铜箔间距离0.5mm以上。

⼆、⾛线、铜箔、焊盘、过孔1. 电源PCB最⼩⾛线0.3mm以上;2. 铜箔、⾛线与板边、挖槽处距离0.5mm以上;3.焊盘孔边与孔边距1mm以上,与板边距离1mm以上;4.SMD元件焊点与直⽴插件焊点间距需≥0.4mm;4.焊盘孔⼤⼩=元件引脚⼤⼩+(0.2~0.4 mm),变压器多引脚元件、⾃动插件元件应加0.4mm;5.焊盘孔径最⼩为0.8mm,同⼀块PCB孔径⼤⼩的类型越少越好,减少PCB加⼯成本;6.焊盘⼤⼩通常为孔径⼤⼩的2.0~2.3倍;7.后焊零件需开流锡槽,这样过波峰焊时内孔才不会被封住;8.过孔的⼤⼩由它的载流量决定,需要的载流量越⼤,所需的过孔尺⼨越⼤,如电源层和地层与其它层联接所⽤的过孔就要⼤⼀些;9.Chip元件焊盘设计应掌握以下关键要素:三、⾃动插件技术1、零件⽅向以⽔平或垂直为主;2、零件与零件本体距离需1.0mm以上,零件本体与板边距离0.5mm以上;3、焊点与焊点间距离需0.5mm以上;4.⾃动插件元件焊盘孔径需≥1mm,⼀般为元件引脚⼤⼩+0.4mm;4、电阻、⼆极管等元件以卧式放置才可⾃动插件;7.⾃动插件电阻、⼆极管、跳线等卧式元件,脚距应为2.5mm的整数倍四、表⾯贴着技术1.零件⽅向以⽔平或垂直为主;2.SMD 贴⽚零件最⼩间距要求0.3mm;3.SMD零件摆设时需考虑过锡炉的⽅向,以防⽌阴影效应;波峰焊SMD元件的排布⽅向:4.SMD零件两端焊点铺铜应平均分布,以防⽌墓碑效应。

BGA芯片的放置与布线规则

BGA芯片的放置与布线规则BGA是PCB上常用的组件,通常CPU、NORTH BRIDGE、SOUTH BRIDGE、AGP CHIP、CARD BUS CHIP…等,大多是以bga的型式包装,简言之,80﹪的高频信号及特殊信号将会由这类型的package内拉出。

因此,如何处理BGA package的走线,对重要信号会有很大的影响。

通常环绕在BGA附近的小零件,依重要性为优先级可分为几类:1.by pass。

2.clock终端RC电路。

3.damping(以串接电阻、排组型式出现;例如memory BUS信号)4.EMI RC电路(以dampin、C、pull height型式出现;例如USB信号)。

5.其它特殊电路(依不同的CHIP所加的特殊电路;例如CPU的感温电路)。

6.40mil以下小电源电路组(以C、L、R等型式出现;此种电路常出现在AGP CHIP or含AGP功能之CHIP附近,透过R、L分隔出不同的电源组)。

7.pull low R、C。

8.一般小电路组(以R、C、Q、U等型式出现;无走线要求)。

9.pull height R、RP。

1-6项的电路通常是placement的重点,会排的尽量靠近BGA,是需要特别处理的。

第7项电路的重要性次之,但也会排的比较靠近BGA。

8、9项为一般性的电路,是属于接上既可的信号。

相对于上述BGA附近的小零件重要性的优先级来说,在ROUTING上的需求如下:1.by pass => 与CHIP同一面时,直接由CHIPpin接至by pass,再由by pass拉出打via接plane;与CHIP不同面时,可与BGA的VCC、GND pin共享同一个via,线长请勿超越100mil。

2.clock终端RC电路=> 有线宽、线距、线长或包GND等需求;走线尽量短,平顺,尽量不跨越VCC分隔线。

3.damping => 有线宽、线距、线长及分组走线等需求;走线尽量短,平顺,一组一组走线,不可参杂其它信号。

bga 封装库 规则

bga 封装库规则BGA封装库规则BGA封装库规则是指在电子设计中使用的BGA(Ball Grid Array)封装器件的相关规范和标准。

BGA封装是一种常见的集成电路封装形式,其特点是焊盘以球形方式排列在芯片的底部,通过焊球与印刷电路板(PCB)上的焊盘相连接。

BGA封装相比其他封装形式具有较高的集成度和良好的热传导性能,因此在现代电子产品中得到广泛应用。

一、BGA封装库的构成BGA封装库主要由以下几个部分组成:1. 封装尺寸和外形:包括芯片尺寸、焊球排布方式、焊球间距等信息,以确保电子元件能够正确地与PCB连接。

2. 焊盘布局:指定电子元件的焊盘位置和布局方式,确保焊盘与PCB焊盘能够正确对齐,实现稳定可靠的焊接。

3. 引脚定义:明确每个焊盘的功能和连接方式,使得电子元件能够正确地与其他元器件或外部接口进行通信和交互。

4. 电气特性:包括电压、电流、功耗等参数,以便设计师在使用BGA封装器件时能够准确地计算和估算电路的性能。

5. 热特性:包括散热设计、温度范围等信息,以保证BGA封装器件能够在正常工作温度下保持稳定的工作状态。

6. 机械特性:指定BGA封装器件的机械强度、重量、安装方式等信息,以确保其能够在各种环境条件下正常工作。

二、BGA封装库的使用规范在使用BGA封装库时,应遵循以下规范:1. 确认BGA封装库是否与所使用的电子设计软件兼容,以确保能够正确导入和使用。

2. 在导入BGA封装库之前,应仔细阅读相关文档,了解BGA封装器件的规格和特性。

3. 在使用BGA封装库时,应根据实际需求选择合适的封装器件,确保与其他元器件和PCB的兼容性。

4. 在进行布局设计时,应根据BGA封装库提供的尺寸和外形信息,合理安排BGA器件的位置和布局,避免焊盘之间的冲突和干扰。

5. 在进行布线设计时,应根据BGA封装库提供的引脚定义,合理规划信号线和电源线的走向和连接方式,确保信号传输的稳定和可靠。

6. 在进行电路仿真和验证时,应根据BGA封装库提供的电气特性和热特性信息,准确计算和估算电路的性能和工作温度,以确保设计的可靠性和稳定性。

pcb layout指导书

pcb layout指导书pcb layout指导书一、概述⑴目的本pcb layout指导书的目的是为了提供一个详细的指南,帮助设计人员进行pcb布局。

⑵背景pcb布局是电路设计的重要环节之一,它涉及到电路板上元件的布置、连线的规划以及电磁兼容性等问题。

合理的pcb布局可以提高电路性能和可靠性。

二、设计准备⑴系统规格在进行pcb布局之前,需要明确系统规格,包括电路功能、性能要求以及信号传输速率等。

⑵系统拓扑根据系统规格,确定电路板的拓扑结构,包括电路板的层数和板型。

⑶元件选型根据系统规格选定合适的元件,并注意元件的尺寸和布局形式。

⑷连接件选型选定合适的连接件,包括电路板与外部接口的连接器、接线端子等。

三、布局规划⑴元件布置根据系统规格和元件尺寸,选择合适的元件布置方式,确保元件之间的间距和连接线长度符合设计要求。

⑵电源和地线布置合理布置电源和地线,确保电路板上各个元件的供电和地线连接畅通。

⑶敏感信号布置敏感信号的布置需要与其他信号相隔一定距离,并采取屏蔽措施,以减少对敏感信号的干扰。

⑷时钟信号布置时钟信号的布置需要考虑时钟传输的稳定性和抗干扰能力。

⑸热管理合理布置散热器、散热孔和风扇等,确保电路板的温度控制在可接受范围内。

四、连线规划⑴信号层定义根据系统规格和布局需求,将电路板划分为不同的信号层,包括功耗层、地层、电源层和信号层等。

⑵信号线宽度和间距根据信号传输速率和电流要求,确定信号线的宽度和层间间距。

⑶信号线走向根据电路功能和信号传输路径,规划信号线的走向,尽量缩短信号线长度。

⑷差分信号布局差分信号需要保持相等长度,并与其他信号相隔一定距离,以减少互相之间的干扰。

五、电磁兼容性措施⑴地线分割根据电路板的信号层划分和布局需求,采取地线分割策略,减少地线回路的面积。

⑵绕线方式对于高频信号和敏感信号,采用绕线方式减少辐射和串扰。

六、文档附件本指导书相关附件包括:附件1:系统规格说明书附件2:pcb布局图附件3:连线规划图七、法律名词及注释⒈电路板:也称印刷线路板(Printed Circuit Board,PCB),是用于连接和支持电子元件的载体。

PCBlayout要遵行七大规则

PCBlayout要遵行七大规则PCBlayout要遵行七大规则能够应用和生产,继而成为一个正式的有效的产品才是PCB layout最终目的,layout的工作才算告一个段落。

那么在layout的时候,应该注意哪些常规的要点,才能使自己画的文件有效符合一般PCB加工厂规则,不至于给企业造成不必要的额外支出?这篇文章为是为大家总结出目前PCBlayout一般要遵行七大规则:一、外层线路设计规则:(1)焊环(Ring环):PTH(镀铜孔)孔的焊环必须比钻孔单边大8mil,也就是直径必需比钻孔大16mil.Via 孔的焊环必须比钻孔单边大8mil,直径必需比钻孔大16mil.总之不管是通孔PAD还是Via,设置内径必须大于12mil,外径必须大于28mil,这点很重要啊!(2)线宽、线距必须大于等于4mil,孔与孔之间的距离不要小于8mil.(3)外层的蚀刻字线宽大于等于10mil.注意是蚀刻字而不是丝印。

(4)线路层设计有网格的板子(铺铜铺成网格状的),网格空处矩形大于等于10*10mil,就是在铺铜设置时line sPACing不要小于10mil,网格线宽大于等于8mil.在铺设大面积的铜皮时,很对资料都建议将其设置成网状,一来可以防止PCB板的基板与铜箔的黏合剂在浸焊或受热时,产生挥发性气体﹑热量不易排除,导致铜箔膨胀﹑脱落现象;二来更重要的是网格状的铺地其受热性能,高频导电性性能都要大大优于整块的实心铺地。

但是本人认为在散热方面不能以网格铺铜的优点以偏概全。

应考虑到局部受热而会导致PCB变形的情况下,以损耗散热效果而保全PCB完整性为条件应采用网格铺铜,这种铺铜相对铺实铜的好处就是,板面温度虽有一定提高,但还在商业或工业标准的范围之内,对元器件损害有限;但是如果PCB板弯曲带来的直接后果就是出现虚焊点,可能会直接导致线路出故障。

相比较的结果就是采用以损害小为优。

真正的散热效果还是应该以实铜最佳。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

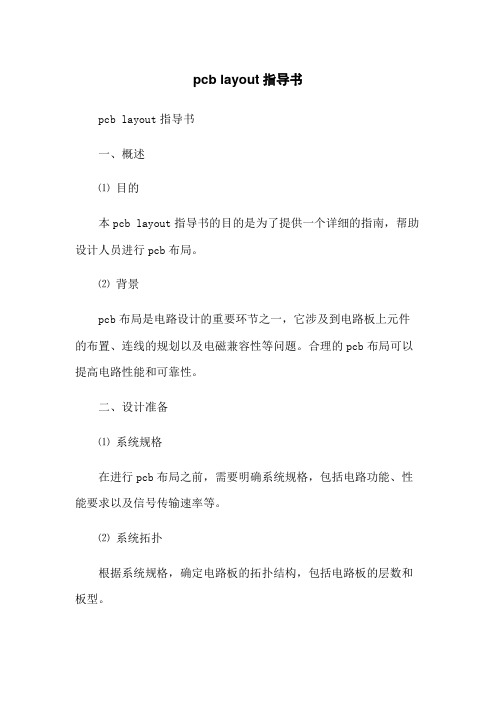

AN10778PCB layout guidelines for NXP MCUs in BGA packagesRev. 01 — 22 January 2009 Application noteDocument informationInfo ContentKeywords LPC2220, LPC2292, LPC2364, LPC2368, LPC2458, LPC2468,LPC2470, LPC2478, LPC2880, LPC2888, LPC3130, LPC3131,LPC3151, LPC3152, LPC3153, LPC3154, LPC3180/10, LPC3220,LPC3230, LPC3240, LPC3250, LH79524, LH7A400, LH7A404,TFBGA100, TFBGA144, TFBGA208, TFBGA180, TFBGA296,LFBGA208, BGA256, LFBGA256, LFBGA324, LFBGA320, LayoutGuidelines, BGA, PCB, Fan-outAbstract This application note is focused on Printed Circuit Board (PCB) layoutissues when using (LF)(TF) BGA packages from the NXP LPCMicrocontroller family.Contact informationFor additional information, please visit: For sales office addresses, please send an email to: salesaddresses@Revision history RevDateDescription01 20090122 Initial release1. IntroductionThe plastic Ball Grid Array (BGA), including Low profile Fine pitch BGA (LFBGA) andThin profile Fine pitch BGA (TFBGA), packages have become, for many applications, thefirst choice for designers requiring medium to high pin-count IC packaging. For thisreason many of the LPC Family of Microcontrollers are available in the LFBGA or TFBGApackage.When comparing it to other common alternative packages, such as the Quad Flat Pack(QFP), the (LF)(TF)BGA device has many advantages. Such as:•The (LF)(TF)BGA has no easy-to-bend leads that can cause deviation fromcoplanarity.•The (LF)(TF)BGA is typically 20% to 25% smaller than an equivalently functionalQFP.•Resolution and smearing problems with respect to the stencil-print process are lessbecause the pitch is larger, and the apertures are circular.•The self-alignment property of the component results in a large process window forautomatic placement.•The (LF) (TF)BGA is compatible with today’s assembly techniques, which means that no adjustments are necessary to standard machines or materials.1.1 ScopeThe scope of this application note is focused on Printed Circuit Board (PCB) layoutissues when using (LF)(TF) BGA packages from the NXP LPC Microcontroller family.Including:•Recommended footprint patterns for the TFBGA180, TFBGA208, TFBGA296 andLFBGA320 pin packages.•Recommended trace, space and via size for fan-out routing of the TFBGA180,TFBGA208, TFBGA296 and LFBGA320 pin packagesIt is recommended that other assembly topics such as the solder paste chemistry, reflowsolder profile and solder paste stencil etching, which are affected by all components onthe board level assembly and not limited to the Microcontroller BGA alone, be acollaborative effort between the system designer and the assembly contractor.2. BGA Package DescriptionA cross section of the typical (LF)(TF)BGA is shown in Fig 1.Fig 1. (LF)(TF)BGA Cross SectionThis application note applies to BGA packages listed in Table 1.Table 1. BGA PackagesPackage Name NXP Outline Code Outline Dimensions Ball Pitch Ball Diam Ball Configuration BGA256 SOT1018-1 [4]17 x 17 x 1.35mm 1.0mm 0.50mm 16 x 16; full matrix TFBGA100 SOT926-1 [2]9 x 9 x 0.7mm 0.8mm 0.45mm 10 x 10; full matrix TFBGA144 SOT569-2 [2]12 x 12 x 0.7mm 0.8mm 0.45mm 13 x 13; partial matrix TFBGA180 SOT570-2 [2]12 x 12 x 0.8mm 0.8mm 0.45mm 14 x 14; partial matrix TFBGA208 SOT950-1 [2]15 x 15 x 0.7mm 0.8mm 0.45mm 17 x 17; partial matrix LFBGA208 SOT1019-1 [5]14 x 14 x 1.27mm 0.8mm 0.45mm 16 x 16; partial matrix LFBGA256 SOT1020-1 [5]14 x 14 x 1.25mm 0.8mm 0.45mm 16 x 16; full matrix TFBGA296 SOT1048-1 [1]15 x 15 x 0.7mm 0.8mm 0.45mm 18 x 18; partial matrix LFBGA324 SOT1021-1 [5]17 x 17 x 1.25mm 0.8mm 0.45mm 20 x 20; partial matrix TFBGA208 SOT930-1 [2]12 x 12 x 0.7mm 0.65mm 0.40mm 17 x 17; partial matrix TFBGA180 SOT640-1 [3]10 x 10 x 0.8mm 0.5mm 0.30mm 18 x 18; partial matrix LFBGA320 SOT824-1 [2]13 x 13 x 0.9mm 0.5mm 0.30mm 24 x 24; partial matrix[1] Reference JEDEC MO-216[2] Reference JEDEC MO-275[3] Reference JEDEC MO-195[4] Reference JEDEC MS-034[5] Reference JEDEC MO-2053. BGA FootprintsWhen building a BGA footprint the number one consideration is ensuring the ball patternand outline matches the device package. This includes correct orientation of ball A1,matching all ball column x row locations, and the ball-to-ball pitch. Solder joint reliabilityis also of primary concern. For cost sensitive applications, minimizing the number ofPCB layers required to route the BGA is a consideration. The BGA land pattern footprintplays a key role in solder joint reliability, and the number of PCB layers required to routethe balls.3.1 Land Pad DesignThe PCB BGA land pads have to be designed to ensure solder joint reliability andprovide optimum manufacturability. The two basic types of BGA land pad design are:•The Solder mask defined land pad (SMD)•The Non-solder mask defined land pad (NSMD); recommended type for PCB3.1.1 Solder mask defined land pad (SMD)The SMD type of BGA land pad design is characterized by the copper pad being largerthan the solder mask opening above this pad. Thus the solder joint area of the land padis defined by the opening in the solder mask.3.1.2 Non-solder mask defined land pad (NSMD)The NSMD type of BGA land pad design is characterized by the copper pad beingsmaller than the solder mask opening. Thus the solder joint area of the land pad isdefined by the size of the land pad. The solder mask clearance around the land padmust be large enough to ensure that no solder mask overlaps the land pad. Typicalsolder mask to land pad clearance is in the range 0.06 – 0.075mm, depending on thePCB manufacturer’s solder mask alignment tolerance.Fig 2. Solder mask vs non-solder mask defined land pad3.2 Recommended BGA FootprintThe NSMD type land pad is recommended for the PCB BGA footprint. In addition to thetop surface of the land pad, the reflowed solder paste will wett to the side wall making amechanically stronger solder joint than the SMD type pad. The smaller NSMD land padalso leaves more space for routing traces between the land pads. It has been shownthat matching the solder joint area of the PCB land pad to that on the BGA packagesubstrate equalizes the ball solder joint stress between the BGA package and PCB landpad thereby reducing the chance of a solder joint stress crack. All of the BGA packagesreferenced in this application note use SMD type pads. The NSMD type pads on the PCBshould be approximately 10 - 15% smaller than the SMD pads on the BGA to achieveequalized stress. This difference between the BGA package SMD pad andrecommended PCB NSMD pad for each BGA package is reflected in Table 2. A genericBGA footprint is shown in Fig 3, and the specific dimensions for each BGA package arelisted in Table 2.Fig 3. Generic BGA FootprintTable 2. Recommended BGA FootprintsPackage Name Ball Pitch Balldiameter BGA substrateLand diameterPCB land paddiameterSolder maskdiameterOutline X & YBGA256 1.0 0.50 0.45 0.45 [4] 0.6 17.6 TFBGA100 0.8 0.45 0.4 0.35 [4] 0.5 9.6 TFBGA144 0.8 0.45 0.4 0.35 [4] 0.5 12.6 TFBGA180 0.8 0.45 0.4 0.35 [4] 0.5 12.6 TFBGA208 (SOT950-1) 0.8 0.45 0.4 0.35 [4] 0.5 15.6 LFBGA208 0.8 0.45 0.4 0.30 [4] 0.42 14.6 LFBGA256 0.8 0.45 0.4 0.30 [4] 0.42 14.6 TFBGA296 0.8 0.45 0.4 0.35 [4][6]0. 5 15.6 TFBGA296 0.8 0.45 0.4 0.30 [4][7] 0. 42 15.6 LFBGA324 0.8 0.45 0.4 0.30 [4] 0.42 17.6 TFBGA208 (SOT930-1) 0.65 0.4 0.26 0.25 [5] 0.37 12.4 TFBGA180 (SOT640-1) 0.5 0.3 n/a 0.25 [5] 0.36 10.4 LFBGA320 0.5 0.3 0.25 0.25 [5] 0.36 13.4 Notes:[1] All dimensions are in millimeters[2] All BGA substrate land pads are SMD type[3] All PCB land pads are NSMD type[4] The recommended solder paste diameter is the same as the PCB land pad[5] The recommended solder paste diameter is 0.02mm larger than the PCB land pad[6] Used for routing 1 trace between land pads[7] Used for routing 2 traces between land pads4. Recommended Fan-out Trace / Space guidelinesThe small pitch between BGA balls and their matrix arrangement makes it impractical toroute all of the BGA balls away from the BGA on a single layer. Fan-out vias (also calledescape vias) are required to route the balls to other layers on the PCB. There areseveral via technologies used on PCB’s. They are: Through-via, Blind via, Buried via,Micro via and In-pad via. Through-vias, where the drilled via hole goes through all layerson the PCB, cost considerably less than Blind, Buried, Micro and In-pad vias. Through-vias are generally larger than the other types of vias as well. All recommended fan-outexamples in this application note use the through-via exclusively.4.1 Recommended 1.0 and 0.8mm pitch BGA via fan-out patternFor 1mm and 0.8mm pitch BGA’s, the recommended via fan-out pattern centers each viawithin the space between four adjacent BGA land pads as shown in Fig 4. Generally, asingle trace is routed between adjacent BGA land pads, allowing the two outer rows ofballs to be routed without a fan-out via. For BGA’s with larger than 0.8mm ball pitch oneor two traces may be routed between adjacent BGA land pads, allowing the three outermost rows of balls to be routed without a fan out via. By reducing the BGA land pad,trace width and trace-to-pad space design rules for the 0.8mm ball pitch TFBGA296, twotraces may be routed between the BGA land pads. See Table 3 for the layout tooldesign rules for 1.0 and 0.8mm pitch BGA via fan-out.Fig 4. 1.0 and 0.8mm pitch BGA Via fan-out patternTable 3. 1.0 and 0.8mm pitch BGA layout design rulesVia Land padto viaspaceBetween viasBetween Land padsBGA Pitch BGA landpadPad Drill size/ finishedhole sizeInner planelayer anti-padTrace /space# of traces Trace /space# oftraces1.0 0.45 0.55 0.3/0.180.800 0.2 0.15 1 0.18 11.0 0.45 0.485 0.25 / 0.1 0.695 0.24 0.1 2 0.11 20.8 0.35 0.485 0.25 / 0.1 0.695 0.148 0.105 1 0.15 10.8 0.30 0.485 0.25 / 0.1 0.695 0.173 0.105 1 0.1 24.2 Recommended 0.65mm pitch BGA via fan-out patternFor 0.65mm pitch BGA’s, the recommended via fan-out pattern centers each via withinthe space between four adjacent BGA land pads. Instead of placing the vias 0.65mmapart they are placed 1.3mm from each other, skipping every other location, andstaggering them between adjacent rows, as the partial fan-out example is shown in Fig 5.With this pattern the TFGBA208 package can use 0.125mm (0.005”) trace and spacedesign rules. With a single trace routed between adjacent BGA land pads, the two outerrows of balls can be routed without a fan-out via. See Table 4 for the layout tool designrules for 0.65mm pitch BGA via fan-out.(1) Note: no connect pins on the LPC3152/54Fig 5. Recommended 0.65mm pitch BGA via fan-out patternTable 4.0.65mm pitch BGA layout design rules ViaBetween viasBetweenLand padsBGA PitchBGA land padPadDrill size / finished hole size Innerplane layer anti-pad Land pad to via space Trace /spaceTrace / space # of traces 0.65 0.25 0.4250.2 / 0.05 0.60.1220.1250.12514.3 Recommended 0.5mm pitch BGA via fan-out patternThe pattern of centering the through-via within the four adjacent BGA land pads can not be used with 0.5mm pitch BGA’s. This is due to the smallest through-via pad being too large to fit in the space available between the land pads. With a single trace routed between adjacent BGA land pads, the two outer rows of balls can be routed without a fan-out via. The two inner rows of balls must be routed to vias in the center area of the BGA and escape routed on other layers. An example fan-out of the LFBGA320 package is shown in Fig 6. See Table 5 for the layout tool design rules for 0.5mm pitch BGA via fan-out.Fig 6. Example fan-out of LFBGA320Table 5. 0.5mm pitch BGA layout design rulesVia BetweenviasBetween Land padsBGA Pitch BGA landpadPad Drill size/ finishedhole size Innerplane layeranti-padLand pad tovia spaceTrace /spaceTrace /space# oftraces0.5 0.25 0.4 0.2 / 0.050.6 0.1 0.1 0.08 1 5. Board Cost considerationsPCB cost is affected by many factors, generally increasing in cost as:1. Overall PCB area increases2. As the number of layers increases3. Using in-pad via, blind via, buried via, micro via4. As the diameter of the through-via decreases5. As the trace width decreases below 0.125mm (5 mils)6. As the space between metal features decreases below 0.125mm (5 mils)Therefore, selecting via size, trace width and spacing for fan-out routing of the BGArequires a balance between feature size, number of PCB layers and overall board area toget the most economical layout.5.1 Area RulesOn many boards the design rules for via size, trace width and space for fan-out routing ofthe BGA may require smaller feature sizes than any other area on the board. If yourlayout tool is capable of defining multiple rule areas, it may be cost effective to limit thearea around the BGA to the smaller feature sizes and use larger vias and larger tracewidths and spacing for the balance of the board. In other words if all but the BGA fan-outcan use 5 or 6 mil trace and space rules, then limiting 3 or 4 mil trace and space rules tothe BGA fan-out area may have only a small cost premium.5.2 How many PCB layers to fan-out the BGAGenerally one trace is routed between adjacent BGA land pads, enabling the two outerrows of BGA balls to be routed on the same layer as the BGA is mounted on. The nexttwo rows in can be routed on the next signal layer, provided the vias are spaced farenough apart to allow one trace between them, as is the case for the 1.0mm, 0.8mm and0.65mm recommended fan-out via patterns in Fig 4 and Fig 5. Each additional BGA rowwill take one additional PCB layer to fan-out. For example, the TFBGA296 has ballsseven rows deep and will take 5 PCB layers to fan-out, including power and ground.Because PCB’s are constructed in even number layers, a PCB using the TFBGA296package would require a minimum of six layers, including one split power plane and oneground plane.NXP SemiconductorsAN10778PCB layout guidelines for NXP MCUs in BGA packagesAN10778_1© NXP B.V. 2009. All rights reserved.6. BGA Power and GroundNXP LPC Microcontroller family devices have many power and ground pins. This is due to having multiple power domains, and the potential for large simultaneous switching currents when all 16-bit or 32-bit external data bus outputs change from all low to allhigh, or all high to all low, at the same time. It is recommended that the MCU VDD(core) and VDD(IO) power nets and VSSx be distributed on a plane layer of the PCB instead of routed by the thin traces, like those used for carrying other signals. BGA power and ground balls are typically routed to a near by fan-out via the same as any signal. It is recommended that the short trace between the BGA ball and fan-out via be no widerthan 0.15mm (6mils). Although it is common to use a wider trace (0.5mm) to route power and ground from other IC packages (SOIC, QFP, TSOP, etc.), using larger than 0.15mm may begin to act like a heat sink that could adversely affect the solder joint. If a BGA power or ground pin must be routed more than 1mm to get to a fan-out via, the trace should be routed the first 1mm with a <= 0.15mm trace then up sized for the balance of the route. It is recommended that all power and ground vias that tie into a plane do so as a solid 360 degree connection, as shown Fig 7a . This provides a lower inductance connection to the plane and will provide a more solid ground plane throughout the BGA area. Avoid the use of thermal (4-point) connections, as shown in Fig 7b .a. Direct via connection to the planeb. Thermal (4-point) connection to the planeFig 7. Via to plane connectionNXP SemiconductorsAN10778PCB layout guidelines for NXP MCUs in BGA packagesAN10778_1© NXP B.V. 2009. All rights reserved.7. Legal information7.1 DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness ofinformation included herein and shall have no liability for the consequences of use of such information.7.2 DisclaimersGeneral — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including withoutlimitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure ormalfunction of a NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmentaldamage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is for the customer’s own risk. Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.7.3 TrademarksNotice: All referenced brands, product names, service names and trademarks are property of their respective owners.NXP SemiconductorsAN10778PCB layout guidelines for NXP MCUs in BGA packagesPlease be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.© NXP B.V. 2009. All rights reserved.For more information, please visit: For sales office addresses, email to: salesaddresses@Date of release: 22 January 2009Document identifier: AN10778_18. Contents1. Introduction.........................................................3 1.1 Scope.................................................................32. BGA Package Description..................................33. BGA Footprints....................................................4 3.1 Land Pad Design................................................4 3.1.1 Solder mask defined land pad (SMD)................5 3.1.2 Non-solder mask defined land pad (NSMD).......5 3.2 Recommended BGA Footprint...........................54. Recommended Fan-out Trace / Spaceguidelines.............................................................7 4.1 Recommended 1.0 and 0.8mm pitch BGA via fan-out pattern....................................................7 4.2 Recommended 0.65mm pitch BGA via fan-out pattern................................................................8 4.3 Recommended 0.5mm pitch BGA via fan-out pattern................................................................9 5. Board Cost considerations...............................10 5.1 Area Rules.......................................................10 5.2 How many PCB layers to fan-out the BGA.......10 6. BGA Power and Ground...................................11 7. Legal information..............................................12 7.1 Definitions........................................................12 7.2 Disclaimers.......................................................12 7.3 Trademarks......................................................12 8. Contents. (13)。