SRD-05VDC-SL-C

水温控制系统设计与报告总结

水温控制系统摘要:本系统以MSP430F149超低功耗MCU为核心,以DS18B20为温度传感器进行温度检测,采用电热棒进行加热。

该控制系统可根据设定的温度,通过PID算法调节和控制PWM波的输出,控制电磁继电器的通断时间从而控制水温的自动调节。

该系统主要包括MSP430F149单片机控制器模块、DS18B20测温模块、键盘模块、继电器控制模块及LCD12864液晶显示模块等构成。

具有电路结构简单、程序简短、系统可靠性高、操作简便等特点。

关键词:MSP430 DS18B20 PID算法PWM LCD12864目录一、任务及要求 (1)1.1设计任务 (1)1.2要求 (1)1.2.1基本要求 (1)1.2.2发挥部分 (1)二、方案设计与论证 (2)2.1 温度检测电路方案选择 (2)2.2显示电路的方案选择 (2)2.3加热和控制方案选择 (2)2.4控制算法选择与论证 (3)三、系统硬件电路设计 (3)3.1系统结构框图 (3)3.2控制器模块 (3)3.3温度检测电路设计 (4)3.4加热控制电路设计 (5)3.5键盘及显示电路设计 (5)3.6电源电路设计 (6)四、软件设计 (6)4.1 PID算法设计 (6)4.2程序流程图 (8)4.2.1主程序框图 (8)4.2.2 LCD12864程序流程图 (9)4.2.3 PID程序流程图 (10)4.2.4 DS18B20水温检测程序流程图 (11)五、系统测试及分析 (12)5.1系统调试 (12)5.1.1控制模块的调试 (12)5.1.2 温度检测模块 (12)5.1.3 继电器的检测 (12)5.2测试结果及分析 (12)5.2.1测试仪器 (12)5.2.2测试方法 (13)5.2.3测试结果 (13)六、设计总结 (14)七、附录 (15)附录1 仪表器件清单 (15)附录2 水温控制系统原理图 (16)附录3 程序设计 (17)一、任务及要求1.1设计任务该水温控制系统是一个典型的检测、控制型应用系统,它要求系统完成从水温检测、信号处理、输入、运算输出控制加热装置以实现水温控制的全过程。

可灵活重配测量与控制系统接口单元设计说明书

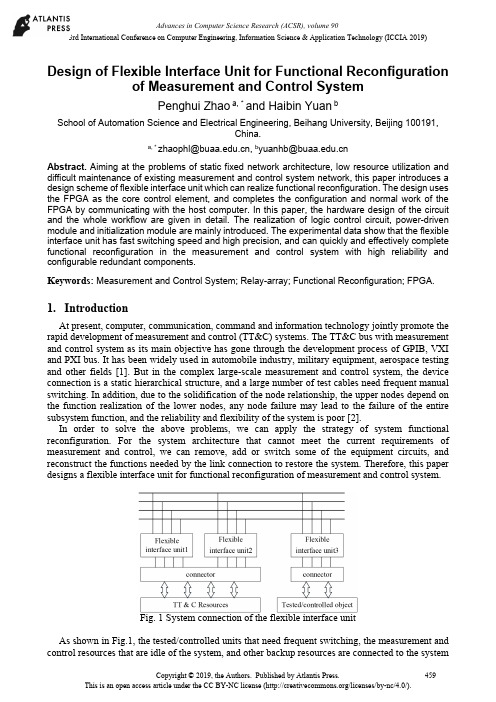

Design of Flexible Interface Unit for Functional Reconfigurationof Measurement and Control SystemPenghui Zhao a, * and Haibin Yuan bSchool of Automation Science and Electrical Engineering, Beihang University, Beijing 100191,China.a, * ****************.cn,b ***************.cnAbstract. Aiming at the problems of static fixed network architecture, low resource utilization and difficult maintenance of existing measurement and control system network, this paper introduces a design scheme of flexible interface unit which can realize functional reconfiguration. The design uses the FPGA as the core control element, and completes the configuration and normal work of the FPGA by communicating with the host computer. In this paper, the hardware design of the circuit and the whole workflow are given in detail. The realization of logic control circuit, power-driven module and initialization module are mainly introduced. The experimental data show that the flexible interface unit has fast switching speed and high precision, and can quickly and effectively complete functional reconfiguration in the measurement and control system with high reliability and configurable redundant components.Keywords: Measurement and Control System; Relay-array; Functional Reconfiguration; FPGA.1. IntroductionAt present, computer, communication, command and information technology jointly promote the rapid development of measurement and control (TT&C) systems. The TT&C bus with measurement and control system as its main objective has gone through the development process of GPIB, VXI and PXI bus. It has been widely used in automobile industry, military equipment, aerospace testing and other fields [1]. But in the complex large-scale measurement and control system, the device connection is a static hierarchical structure, and a large number of test cables need frequent manual switching. In addition, due to the solidification of the node relationship, the upper nodes depend on the function realization of the lower nodes, any node failure may lead to the failure of the entire subsystem function, and the reliability and flexibility of the system is poor [2].In order to solve the above problems, we can apply the strategy of system functional reconfiguration. For the system architecture that cannot meet the current requirements of measurement and control, we can remove, add or switch some of the equipment circuits, and reconstruct the functions needed by the link connection to restore the system. Therefore, this paper designs a flexible interface unit for functional reconfiguration of measurement and control system.Fig. 1 System connection of the flexible interface unitAs shown in Fig.1, the tested/controlled units that need frequent switching, the measurement andcontrol resources that are idle of the system, and other backup resources are connected to the system3rd International Conference on Computer Engineering, Information Science & Application Technology (ICCIA 2019)Advances in Computer Science Research (ACSR), volume 90network through the flexible interface unit. When the system has component failure or needs to switch the measurement and control object, the flexible interface unit is disconnected from the unrelated device, and then the required device is connected to the system network to realize the flexible connection of the system interface. The flexible interface unit can effectively improve the resource utilization efficiency and fault handling capability of the system, reduce the cost and time of system fault repair, and greatly enhance the reliability and maintainability of the measurement and control equipment, and improve intelligence, flexibility and safety of the test system.2.Principle Model of the Flexible Interface UnitThe flexible interface unit connects the redundancy and backup resources in the measurement and control equipment to the system network. When components in the system are damaged, the faulty components can be isolated through the flexible interface unit to initiate backup to quickly restore the system. Therefore, according to the requirements of functional reconstruction, the flexible interface unit should have the following characteristics [3]: 1) The unit has enough interfaces to connect as many measurement and control resources as possible to the network; 2) The flexible unit has a faster response speed and higher precision to quickly switch components and reduce the disturbance when signal passing; 3)The unit has high security and avoids control errors such as line shorting and channel conflict. According to the needs of the measurement and control system, the functional block diagram of the designed flexible unit is shown in Fig.2.Fig. 2 Principle block diagram of flexible interface unitThe flexible interface unit is mainly composed of relay-array, initialization module, driving module and programmable logic control circuit. When there is a component failure, the host computer issues an instruction to the programmable control circuit, and the control circuit decodes and then controls the switch of the relay array through the driving module. The initialization module is used to start or reset to verify whether the flexible unit itself is working properly.3.Design in Hardware of the Flexible Interface Unit3.1The Design of Relay-array ModuleAfter analysis, the SRD-05VDC-SL-C relay was selected for its voltage range is large, and the cost performance is high. The rated voltage of the relay is 5V, the coil power is 360mW and the response time is less than 10ms. The internal structure of the relay is shown in Fig.3. Pin1 and Pin2 are the control signals of the relay, Pin5 is the input signal, Pin3 is the normally closed output, and Pin4 is the normally open output. When voltage of Pin1 is 5V higher than Pin2, the inductor coil is energized, and the generated electromagnetic force attracts the metal switch downward to close thenormally open output, and the Pin 4 and Pin5 are connected electrically. After the 5V control voltage is disconnected, the electromagnetic force disappears and the metal switch bounces back to the normally closed output again.Fig. 3 The internal structure of relayThe relay array can be set to various specifications depending on the number of backup components in the measurement and control system. For different types of backup components, we can continue to add relay-arrays or expand the array size to connect more components to the measurement and control network. This paper designs an 8-input and 8-output relay-array model as shown in Fig.4. When the measurement and control signal is transmitted from an input channel, the switch of the relay can be controlled to select the channel of the output so that the connection of different input ports to the output port can be flexibly realized, and the flexible interface configuration of the measurement and control system is completed.Fig. 4 Relay-array model3.2The Design of Programmable Logic Control CircuitThe main function of the programmable logic control circuit module is to realize data decoding, verification and latching [4]. Taking into account the dynamic changes in demand, we use FPGA to build circuits. With high integration, short development cycle, and rich internal trigger and I/O resources, FPGA is a good choice for designing control circuits, which can be programmed online. The host computer sends an initialization command and a relay on/off command to the FPGA so we can realize the safe start of the flexible interface unit and the function reconstruction when some component fails [5].3.2.1 Introducing the Communication ProtocolFor the 8×8 relay-array, the row number and column number are both marked as 0~7, and the relay can be uniquely determined according to the row number and column number. The host computer communicates with the FPGA through the UART serial port, each communication uses 1 byte of data and the data format of the serial communication is shown in Fig.5. The first two data formats areapplied to the host computer to send instructions to the FPGA, and the FPGA responds to the instructions and returns the result using the third data format. Since the row number and the column number each occupy 3 bits which indicate the labels of 0 to 7(from 000 to 111), so that we specify that in all data communication formats D2 to D4 represent the row numbers and D5 to D7 represent the column numbers. In the host computer control instruction, D0 indicates the control mode: when D0 is 1, if D1 is 1, it means to turn on the relay, and if D0 is 1, it means to turn off the relay. When D0 is 1, FPGA is required to check whether the relay can work normally. In the signal returned by the FPGA, that D0 is 0 indicates that the instruction received by the FPGA is legal and that D0 is 1 indicates the instruction is illegal. When D1 is 0, we can get the flexible interface unit executed successfully, and D1 is 1 indicates the execution failed. The specific relay label in all of the formats of transmitted data discussed above is given by D2~D7.Fig. 5 UART serial communication frame format3.2.2 FPGA Internal ProgrammingThe FPGA device we selected is Xilinx's XC6SLX9, with XCF04 as configured Flash, which is programmed to decode, verify, and latch the circuit. We use the hardware design tool ISE to complete the input, synthesis, implementation, verification, download and other aspects of FPGA product development. After the design is completed, the simulation software ModelSim is used to simulate and analyze the logic circuit.The decoding circuit analyzes the control commands received by the FPGA from the host computer, and determines operations to be performed according to the communication protocol. The latch circuit which is simple to implement in the FPGA can define Verilog register variables and assign them to the I/O port. Each relay is controlled by an I/O port for the corresponding output pin is locked while the register variable is unchanged [6].Inspection circuit is used to determine whether the received instructions are legitimate. Any input row of the relay-array can only have one relay on at the same time. Otherwise, signal crosstalk may be disturbed and even serious faults may occur such as power shortage, device burnout, etc. Therefore, for the received instruction, the FPGA internally generates a status table to record whether rows and columns of relay-array have been occupied. For example, after the initialization is completed the host computer sends the instruction “01011101” to the FPGA, that is, the relay of row 3 and has been turned on, and the recording line number 3 is occupied at this time. After that we assumes the FPGA received the instruction of “01011001” which means the relay at row 3 and column 1 in array should be turned on. Comparing the status table at this time, we find the row 3 has been already occupied so that the instruction is illegal and cannot be executed, and the FPGA sends error feedback to the host computer.3.3 The Design of Driving ModuleThe driving circuit module needs to be designed for the I/O port of FPGA can only lock the high or low level, but its current and sink current are insufficient, and the relay cannot be driven to complete the switching action. Here we choose the inverting driver MC1413, which consists of 7 NPN Darlington tubes, can be directly connected to TTL and CMOS circuits at 5V operating voltage.It sinks up to 500mA and can withstand 50V in the off state, fully meeting the control requirements of the I/O port for relays [7]. The specific circuit schematic is shown in Fig.6.Fig. 6 Driving circuit schematic diagramA1~A7 of MC1413 are input pins, Y1~Y7 are output pins, and K is connected to +5V voltage. The input pins are connected to the I/O ports of FPGA, the output pins are connected to negatives of relays, and the anodes of relays are connected to +5V. The diode is used for circuit freewheeling to prevent the back electromotive force generated by the coil from damaging the device when the relay is disconnected [8]. For example, the I/O1 of the FPGA is set to a high level of 3.3V. At this time, the output of the inverting driver Y1 is low, the current of the relay coil is passed, the metal piece is closed, and the relay is turned on. Similarly, when I/O1 is set to a low level, Y1 is connected to +5V due to the action of the inverter. Both ends of the relay are high level, no current flows through the coil, and the relay is disconnected.3.4 The Design of Initialization ModuleThe initialization module can detect whether the relay-array works normally when the flexible interface unit is started or reset to avoid the problems of the switch failure, poor contact, abnormal resistance of the relay-array itself, which may have an influence on the signal transmission of the measurement and control system, and can effectively improve the flexible interface unit safety and reliability [9].Fig. 7 Initialization circuit schematic diagramFig.7 is the circuit diagram of the initialization module which uses a +5V DC power supply. The figure shows four relays J00, J01, J10, J11 in the first two rows and the first two columns of the relay-array. The output port of the operational amplifier, Vout, is connected to the I/O port of FPGA, and the level characteristic of the I/O port is set to LVCMOS 3.3V. When the relay is closed, the resistance effect is ignored, the voltage of the non-inverting input terminal and the inverting input terminal of the operational amplifier are equal, the output voltage Vout is equal to 0, and the I/O port of the FPGA is detected as a low level. When the relay is disconnected, the voltage of the non-inverting input terminal of the operational amplifier is 1.647V and the inverting input terminal is grounded through R4 and R5 and connected with the output terminal through R7. We calculate that Vout is equal to 3.294V at this time, and the I/O port of the FPGA is detected as high level.After the FPGA receives the initialization command, it closes the corresponding relay. For the initialization of a single relay, the I/O port connected to Vout is “1” when the relay is disconnected, and Vout is “0” when the relay is closed. A detection level error indicates that the relay cannot be normally switched or the resistance is abnormal. For a faulty relay, the FPGA sends an error message and the corresponding relay number to the host computer.4.Design in Software of Flexible Interface UnitThe main program flow chart of the flexible interface unit is shown in Fig.8.Fig. 8 Main program flow chart of flexible interface unit After the flexible interface unit is started, the host computer sends an initialization command. The FPGA sequentially checks whether each relay is normal and when the relay is found to be faulty the system stops working. If no fault is found, the FPGA generates a status table of relay-array and records whether the relays are turned on in each row. Since all relays are disconnected at this time, the row and column values in the status table are all 0, indicating that they are not occupied. If therelay is required to be disconnected by the control signal, directly perform the operation to set the corresponding I/O port low and change the status of the row to 0. If the command requires the relay to close, check whether the row is occupied in the status table. If it is closed, the command is illegal and cannot be executed. For legitimate operations, the FPGA executes control instruction and sets the I/O port high and changes the value of the row and column in the status table to 1. After the action is completed, the execution result is sent to the host computer, and then the host computer is requested to end the process. If the request is successful, the process ends, otherwise it continues to wait for the control command.5.The Results of ExperimentIn order to determine the safety and feasibility of the above design, the flexible interface unit is connected to the measurement and control system for verification by experiment. We add +12V DC power supply to the system, and control the 3×2 relays to turn on and off in turn, and record the execution time of the host computer program, that is, the time from when the command is issued until the last disconnected feedback signal is received. The above operation was repeated 4 times to obtain Table 1. The average time taken to continuously complete 6 relays is 75.843ms and the average switching time of each relay is 6.321ms.Table 1. Execution time of relay switchingExperiment number Execution time(ms)Mean of execution time(ms)1 75.996 6.3322 75.731 6.3103 75.775 6.3124 75.851 6.320Average value 75.843 6.321 The experiment also tested the voltage error of the flexible interface unit. The above 3×2 relay array was closed, and the input voltage and output voltage values were measured for comparison. The data results are shown in Table 2. The maximum difference between the test input voltage and the output voltage is 13mV, and the maximum relative error is 0.108%.Table 2. Voltage measurement resultsRelay number Input voltage(V)Output voltage(V)Relative error(%) J0012.01212.008-0.033J0112.00912.0150.050J1012.00512.0180.108J1112.00312.000-0.025J2012.00812.0010.058J2112.011 12.007 -0.0336.ConclusionThe above experimental results show that the flexible interface unit controls the relay on and off by the drive circuit through the host computer control, effectively completes its own initialization function and the function reconstruction task of the measurement and control system, and can be applied to the systems whose architecture is prone to failure, inconvenient maintenance or have redundant device. In the experiment, the test relay switching time is within 6.332ms, and relative error of the voltage is within 0.108%, which ensures the rapidity and reliability of the system reconstruction task. Due to the free implementation of the programmable control circuit, the flexible interface unit can be developed in terms of integration, intelligence and low power consumption, and has a good application prospect.References[1].Hong C, Xin-Yu J. The Analysis and Actuality of Measure-control System Bus Technology[J].Mechanical & Electrical Engineering Magazine, 2003.[2].Neves, Saotome. Comparison between Redundancy Techniques for Real Time Applications[C]//International Conference on Information Technology: New Generations. IEEE Computer Society, 2008.[3].Xiang Xuezhi, Kai Xianglong, Zhang Zhenyu. Design of switching matrix module based on PXIbus[J]. Foreign Electronic Measurement Technology, 2013, 32(12):76-79.[4].Wang Jie. Xilinx FPGA / CPLD Design Manual [M]. The Posts and Telecommunications Press,2011.[5].Zhang H G, Xing H G, Wang D S, et al. Design of Massive Switching Matrix Module Based onField Programmable Gate Array (FPGA)[J]. Torpedo Technology, 2006.[6].Ren Xiaodong, Wen Bo. CPLD/FPGA Advanced Application Development Guide[M].Electronic Industry Press, 2003.B. R. Jackson and T. Pitman, U.S. Patent No. 6,345,224 (8 July 2004).[7].Chen Jiandong. A Practical Circuit of MC1413[J]. Home electronics, 1998(01):21. R. C.Mikkelson (private communication).[8].Han Zhiqiang, Zhang Jianjun, Yan Ruliang. Relay Fault Analysis and MATLAB Simulation [J].Electrician technology, 2006(10):13-14.[9].Ge Genhua, Zang Chunhua. Horizontator measurement and control cabinet with self-inspectionand self-protection functions[J]. Electronic Technique, 2006(08):44-48.。

【GL9型51单片机开发学习系统】原理图集V7.1

湿度传感器 7 U6 6 5 R59 4 3 2 N 超声波测距模块接口 温度传感器

10 3

XT1

P10

P17

C3

P30

C4

P37

P30 P31

N N 2 3 4 5 6 7

+

R56

STC

MAX485

S1

102

S2

U8

89C54RD+ 40C-PDIP40 1039C1P746907

IIC存储器

51单片机 学习开发系统 型号:GL9

C8

100 16V RVT

E2

103

103

103

R45 R44

T1 K2

102

T2 K3 K4

红外接收

RS485接口

101

U9 R63 R64 R62

U7

R61

B A

CN11

CN10

K1

K9

K10

K11

K12

CN1

R60

温度传感器

10 3

P1

P2

P3

P4

U5

PS /2键盘接口

N

GND ECHO TRIG +5V

P1.0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 P3.0 P3.1 P3.2 P3.3 P3.4 P3.5 P3.6 P3.7 P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7 P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0

液晶接口 液晶接口

1602

CN26 VR3 CN27

VR2

K A Vlcd RST CS2 CS1 DB7 CN29 DB6 h g DB5 DB4 f DB3 e DB2 d DB1 c DB0 b E a 1位静态数码管 R/W RS Vo Vdd Vss

基于4G手机远程智能花卉浇灌系统的研究

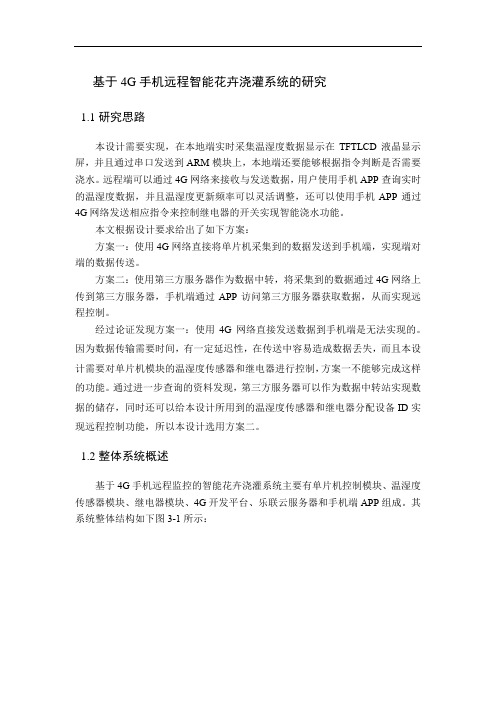

基于4G手机远程智能花卉浇灌系统的研究1.1研究思路本设计需要实现,在本地端实时采集温湿度数据显示在TFTLCD液晶显示屏,并且通过串口发送到ARM模块上,本地端还要能够根据指令判断是否需要浇水。

远程端可以通过4G网络来接收与发送数据,用户使用手机APP查询实时的温湿度数据,并且温湿度更新频率可以灵活调整,还可以使用手机APP通过4G网络发送相应指令来控制继电器的开关实现智能浇水功能。

本文根据设计要求给出了如下方案:方案一:使用4G网络直接将单片机采集到的数据发送到手机端,实现端对端的数据传送。

方案二:使用第三方服务器作为数据中转,将采集到的数据通过4G网络上传到第三方服务器,手机端通过APP访问第三方服务器获取数据,从而实现远程控制。

经过论证发现方案一:使用4G网络直接发送数据到手机端是无法实现的。

因为数据传输需要时间,有一定延迟性,在传送中容易造成数据丢失,而且本设计需要对单片机模块的温湿度传感器和继电器进行控制,方案一不能够完成这样的功能。

通过进一步查询的资料发现,第三方服务器可以作为数据中转站实现数据的储存,同时还可以给本设计所用到的温湿度传感器和继电器分配设备ID实现远程控制功能,所以本设计选用方案二。

1.2整体系统概述基于4G手机远程监控的智能花卉浇灌系统主要有单片机控制模块、温湿度传感器模块、继电器模块、4G开发平台、乐联云服务器和手机端APP组成。

其系统整体结构如下图3-1所示:图3-1 智能花卉浇灌系统整体结构图单片机主要负责本地部分数据采集和控制,DHT11温湿度传感器将采集到温湿度数据传送给单片机,单片机处理后传送到TFT LCD显示屏显示出来,同时通过串口将数据传递给4G开发平台。

单片机还会根据程序控制继电器的开关实现浇水和遮阳的功能。

4G开发平台由4G模块、ARM和显示屏组成,将单片机传送过来的数据通过移动4G网络发送到乐联云服务器,同时用户通过手机端APP从服务器接收数据,实现远程监控功能。

LED路灯远程控制系统使用说明

本方案技术重点主要分为LED照明技术和Z igBee协议组网技术和GPRS远程传输技术。

设计了一种无线LED路灯远程控制系统,构建为底层为路灯控制节点,中间为中心传输节点,顶层计算机控制终端。

本设计硬件由atmage16、atmega128单片机,ZigBee sz05模块和sz11GPRS模块,和LED路灯灯头以及路灯电源相关器件组成,软件基于Delphi的上位机设计和基于c的下位机程序设计。

本设计旨在提供一种以ZigBee无线技术为主的城市路灯照明系统解决方案,目的是使设计低成本、高效能、全自动化的城市照明系统。

第一部分上位机使用说明中央控制中心为PC机,主要负责建立和管理路灯控制网络.PC机装有人机界面,适合监控人员操作.该PC机通过3G能上网,打开人机界面,即可进行网络连接和管理路灯。

主要功能包括:◆向中心控制节点发送控制命令,具体包括路灯开关,若是选择手动控制则可以直接发送亮度等级,可以根据需求采集数据光强、温度、电压电流。

若是选择自动控制那么中心控制节点自行对本路灯组进行24小时自动定时开关和调光控制,并且定时接受光强、温度、电压电流数据,这样可以将节省的功率随时上传以供观测。

一安装准备工作1、本无线路灯控制上位机不用安装,直接将应用程序拷贝到电脑适当位置,双击即可打开使用.2、在使用本系统之前,要确保电脑是开放相应端口且运行在公共网络上的一台电脑主机(或服务器),IP地址是指数据服务中心接入Internet获得公网的IP地址,此IP地址必须为合法的公网IP地址,如果使用内网的计算机来架设数据服务中心,必须在相应的代理网关上做NAT或者DMZ设置来开放数据服务中心所需要的通讯端口号。

这里有两种方式解决该问题。

(1)申请固定IP地址,在GPRS里面就设置成这个固定IP,每次上网连接的时候就都可以连接该台电脑的上位机程序。

(2)没有固定IP地址,但是该电脑能够运行在公共网络,每次连接上网IP 地址都会改变。

基于NB-IoT的智能灌溉系统设计

44 集成电路应用 第 38 卷 第 6 期(总第 333 期)2021 年 6 月

否符合要求,若LED闪烁则说明超出限度应停止灌 溉。最后对湿度数据进行转换并储存。

2.3 灌溉控制模块程序设计 本系统的灌溉控制方式由手动和自动两种构

成。手动控制是通过操作上位机界面或手机端界面 的浇灌按钮来执行对继电器的操作。自动控制则是 收集到的土壤湿度数据与设置的阈值比较,当土壤 湿度值低于设定值时就自动执行程序控制继电器打 开,开始灌溉,当设定的灌溉量达到时,程序自动 控制继电器关闭,停止灌溉。

[18] 周岩,江冰,邬智俊,胡钢.提水式泵站农业灌 溉用水全智能化计量系统研究[J].测控技术, 2020,39(05):107-111.

[19] 张明.基于物联网的农田灌溉系统设计——以 甘肃省张掖市甘州区沿山灌区为例[J].甘肃 科技纵横,2021,50(04):8-11.

集成电路应用 第 38 卷 第 6 期(总第 333 期)2021 年 6 月 45

册状态信息并进行上报; (5)复位NB模块,查询网络的注册状态,若

为“1”,表示正在联网运行,若为“2”,表示正 在搜索网络。

(6)AT寻查默认IP地址是否为默认PDN,若是 默认的PDN,则查询IMEI号,然后发送数据,入网 配置完成。

2.5 电信云平台配置 进入电信云平台,根据步骤注册用户并开通

基于NB-IoT智能灌溉系统硬件终端主要由MCU 主控模块、NB-IoT无线传输模块、数据采集模块、 灌溉控制模块、以及电源供电电路组成。

(1)MCU主控模块:从功耗、性能、价格和开 发难度这四个方面考虑。使用STM32单片机作为本 系统的MCU主控芯片。

(2)NB无线传输模块:采用移远公司的 BC95-B5模块。

GL9程序下载操作指导书(WIN7)

P20

R

U1 给力者

51单片机 学习开发系统

C7 +

74HC138 U4

74HC138

有源蜂鸣器 无源蜂鸣器

100 16V RVT IIC存储器

103

AT24C02

R56

R55

XT1

AT系列下载接口

89C54RD+

STC 40C-PDIP40 1039C1P746907

型号:GL9

E2

103

S1

S2

7,步骤4 : 设置其它参数,此处按照默认即可。

宁波芯动电子有限公司

04

程序下载操作指导书

R

给力者

GEILIER

G

L

9型5

1单

片

机

开

发

学

习

系

统

8,步骤5 : 下载,点击 Download/下载 键即可启动下载,点击前要保证GL9型开发板 已经正确的通过USB数据线连接于电脑的USB接口上,并且将开关SW1置于左侧。

R41

103

CN23

5 6 7 CN4

+

22 16V RVT

R49 R53 V10

R52 R51 R50

+ R49 R48 JP1

SW4

TXD

模数、数模转换

123

C5

0

331

PCF8591

1

103

101

103

2

3 CN3

U3

103

101

103

E3

100 16V RVT 100 16V RVT

+

331

03

程序下载操作指导书

【GL9型51单片机开发学习系统】综合实验原理图V70

F1 F2

U15

74HC138

h g f e d c b a

103

CN30

CN18

U10

R65

AT系列下载接口

R55

CN32

CN33

4×4矩阵式按键

22.1184

C1 C2

V6.0

E5 22 16V RVT

22

22

CN23

CN4

12.0000

XT2

CN34

芯片放置方向

51 MCU

R41

10 3

TXD RXD

103

16×16 LED点阵屏

U14

C10 C11 R67R86

102

102

102

102

102

102

102

102

U11

7 6 5 4 3 2 1 0

CD4060

07 06 05 04 03 02 01 00

U12

CN17

实时时钟

SONGLE

+

103

SRD-05VDC-SL-C

10A 250VAC 10A 125VAC 10A 30VDC 10A 28VDC

湿度传感器 7 U6 6 5 R59 4 3 2 N 超声波测距模块接口 温度传感器

10 3

XT1

P10

P17

C3

P30

C4

P37

P30 P31

N N 2 3 4 5 6 7

+

R56

STC

MAX485

S1

102

S2

U8

89C54RD+ 40C-PDIP40 1039C1P746907

srd-05vdc-sl-c继电器原理

srd-05vdc-sl-c继电器原理:只要在线圈两端加上一定的电压,线圈中就会流过一定的电流,从而产生电磁效应,衔铁就会在电磁力吸引的作用下克服返回弹簧的拉力吸向铁芯,从而带动衔铁的动触点与静触点(常开触点)吸合。

当线圈断电后,电磁的吸力也随之消失,衔铁就会在弹簧的反作用力返回原来的位置,使动触点与原来的静触点(常闭触点)释放。

这样吸合、释放,从而达到了在电路中的导通、切断的目的。

对于继电器的“常开、常闭”触点,可以这样来区分:继电器线圈未通电时处于断开状态的静触点,称为“常闭触点”;处于接通状态的静触点称为“常开触点”。

继电器一般有两股电路,为低压控制电路和高压工作电路。

粮食水分检测装置设计

粮食水分检测装置设计胥保文;蔡健荣;孙力;张文松;安玉亭;何振鲁【摘要】开发了一套对射式微波水分检测装置.以STC89C52芯片为主处理器,控制各部件执行顺序.为保证物料装载的一致性,采用光电开关控制装载量;为消除温度影响,实时采集样本料温,建立温度补偿模型;为避免微波产生热效应,采用时序控制采集温度及微波信号,以实现粮食水分的准确测量.经实验验证,物料实际水分与微波检测水分之间的相关系数>0.96,满足实际检测要求.%A set of grain moisture detection device based on incident microwave was designed,and the STC89C52 chip was used as the main processor to control the execution order of each component.Moreover,the photoelectric switch was used to keep the amount of the loading material in line.In order to eliminate the influence of temperature,it was detected in real time,and the temperature compensation model is established.To avoid the thermal effect of microwave,the sequential control system was applied to collect temperature and microwave signals,ensuring the accurate measurement of grain moisture.The results showed that the correlation coefficient between actual moisture content and microwave moisture content was greater than 0.96,and it could meet the requirements of actual test.【期刊名称】《食品与机械》【年(卷),期】2017(033)009【总页数】3页(P81-83)【关键词】粮食水分;微波;检测装置【作者】胥保文;蔡健荣;孙力;张文松;安玉亭;何振鲁【作者单位】江苏大学,江苏镇江212013;江苏大学,江苏镇江212013;山东同泰集团股份有限公司,山东日照276801;江苏大学,江苏镇江212013;山东同泰集团股份有限公司,山东日照276801;山东同泰集团股份有限公司,山东日照276801;山东同泰集团股份有限公司,山东日照276801【正文语种】中文粮食在储藏过程中应及时掌握水分变化情况,水分过高易引起霉变、生虫等,造成粮食变质;水分过低会破坏其有机物质[1]。