计算机组成原理指令系统

计算机组成原理第4章指令系统课件

4.2 指令的格式

4.2.1 指令的编码格式

操作码OC

AC1

AC2

(1)把保存操作前原来操作数的地址称为源点地址(SS), 把保存指令执行结果的地址称为终点地址或目的地址(DD)。

(2)将源点与终点操作数进行操作码规定的操作后,将 结果存入终点地址。通常二地址指令又称为双操作数指令。

ADD R0,R1表示将R0寄存器的内容和R1寄存器的内容相加以

5 异或XOR

XOR指令对两个操作数进 行按位异或运算。

4.4 指令的种类

4.4.4 移位、循环类指令

CF

位移指令SAL/SHL操作示意图

CF

SAR操作示意图

CF 0

SHR操作示意图

4.4 指令的种类

4.4.4 移位、循环类指令

不带进位标志的循环左移指令ROL MSB 操作数 LSB

CF

不带进位标志的循环右移指令ROR MSB 操作数 LSB

例如:在IBM-PC指令系统中

MOV

AX,05FFH

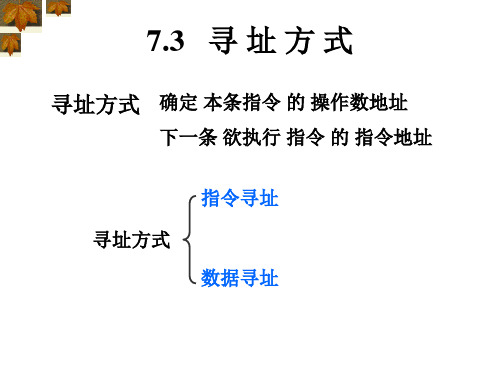

4.3 寻址方式

4.3.2 常用的寻址方式

2.直接寻址方式

(1)含义: 是指地址字段直接指明操作数在存储器内的位置的寻址 方法。即形式地址等于有效地址。 (2)优缺点: A、优点:简单,不需要进行加法运算。 B、缺点:地址空间指令地址字段长度的限制。

4.2 指令的格式

4.2.3 指令助记符

通常采用一些符号来代表二进制数据,这些符号即指 令助记符。

指令助记符 ADD SUB MUL DIV

助记符示例

含义

指令助记符

相加

AND

相减

OR

相乘

LOAD

相除

STORE

《计算机组成原理》教程第4章指令系统

4

二 指令的格式

即指令字用二进制代码表示的结构形式

包括 操作码:操作的性质 操作码 地址码:操作数(operand)的存储位置,即参加操作的 operand , 地址码 数据的地址和结果数的地址

操作码域(op) 地址码域(addr)

5

1.操作码 操作码

指令的操作码表示该指令应进行什么性质的操作。 组成操作码字段的位数一般取决于计算机指令系统的 规模。 固定长度操作码:便于译码,扩展性差 . 可变长度操作码:能缩短指令平均长度 操作码的的位数决定了所能表示的操作数,n位操 作码最多表示2n种操作

(2). 堆栈工作过程 .

(一)进栈操作 ① 建立堆栈,由指令把栈顶地址送入SP,指针 指向栈顶。 ② 进栈:(A)→Msp, (sp)-1→SP ;Msp:存储 器的栈顶单元 (二)出栈操作 (SP)+1→SP, (Msp)→A

22

五.指令类型

一个较完善的指令系统应当包括: 数据传送类指令: 例)move、load、store等 算术运算类指令: 例)add、sub、mult、div、comp等 移位操作类指令: 例) shl,shr,srl,srr 逻辑运算类指令: 例)and、or、xor、not等 程序控制类指令: 例)jump、branch、jsr、ret、int等 输入输出指令: 例)in、out等 字符串类指令: 例)如alpha中cmpbge、inswh、extbl等 系统控制类指令: 例)push、pop、test等

18

10) *段寻址方式 段寻址方式 Intel 8086 CPU中采用了段寻址方式(基址寻址的特例)。 由16位段寄存器和16位偏移量产生20位物理地址 11)*自动变址寻址 自动变址寻址 指在变址方式中,每经过一次变址运算时,都自动改变变址寄存 器的内容,以后在PDP-11中详讲.

计算机组成原理-指令系统

一地址指令格式: OP10扩bi展t 6bit A 6bit 设为Z 剩余(24-X)26-Z

零地址指令格式: OP16bit ∴Z= (24-X)26- Y 2-6

扩展6bit Y种 ((24-X)26-Z) 26=Y

操作码扩展技术

鲁东大学 LUDONG UNIVERSITY

EX2.机器指令长度为16位,地址码长度为6位,包含单地址 指令,双地址指令和无地址指令,试问单地址指令最多有 多少条?此时双地址指令和无地址指令各多少条?

鲁东大学 LUDONG UNIVERSITY

强调:操作码扩展技术思考方向

EX2:假设指令字长16位,操作数的地址码为必6须位是,操指作令码有增零长地方址向、

一地址、二地址三种格式。要求:

(1) 设操作码固定,若零地址有P种,一地址指令有Q种,则二 地址最多有多少对种定?长操作码指令格式,应满足最长地址码要求

指令格式-操作码字段

变长操作码指令系统 鲁东大学 LUDONG UNIVERSITY

--随着地址码长度的变化,操作码长度变化 --特点:与定长刚好相反

常用技术: 操作码扩展技术★

OP 4b A1 A2 A3

三地址指令格式

0000 … 1110

三地址指令15条

OP 4b A1 A2

1111 0…000 1110

用于零地址指令扩展的编码最少为1个

指令格式-地址码字段

鲁东大学 LUDONG UNIVERSITY

2.指令的一般格式

分析指令地址码类型

地址码

OP A1 A2 A3 A4

作用:用于指明操作数的地址; ① 四地址指令 ② 三地址指令 ③ 二地址指令 ④ 一地址指令 ⑤ 零地址指令

计算机组成原理-第4章_指令系统

7. 段寻址方式(Segment Addressing)

方法:E由段寄存器的内容加上段内偏移地址而形成。

应用:微型机采用段寻址方式,20位物理地址为16位 段地址左移四位加上16位偏移量。

分类:① 段内直接寻址; ② 段内间接寻址; ③ 段间直接寻址; ④ 段间间接寻址;

9 堆栈寻址方式

堆栈:是一组能存入和取出数据的暂时存储单元。

*** 指令字长度

概念 指令字长度(一个指令字包含二进制代码的位数) 机器字长:计算机能直接处理的二进制数据的位数。 单字长指令 半字长指令 双字长指令

多字长指令的优缺点

优点提供足够的地址位来解决访问内存任何单元的寻址问题 ; 缺点必须两次或多次访问内存以取出一整条指令,降低了CPU的运 算速度,又占用了更多的存储空间。

*** 指令系统的发展与性能要求

*** 指令系统的发展

指令:即机器指令,要计算机执行某种操作的命令。

指令划分:微指令、机器指令和宏指令。

简单

复杂

指令系统:一台计算机中所有指令的集合;是表征

计算机性能的重要因素。

系列计算机:基本指令系统相同、基本体系结构相同 的一系列计算机。

*** 对指令系统性能的要求

(2)立即数只能作为源操作数,立即寻址主要用来给寄存 器或存储器赋初值。以A~F开头的数字出现在指令中时,前 面要加0。

(3)速度快(操作数直接在指令中,不需要运行总线周期)

(4)立即数作为指令操作码的一部分与操作码一起放在代 码段区域中。

(5)指令的长度(翻译成机器语言后)较长,灵活性较差。

【例】MOV AX, 10H 执行后(AX)=? 其中:这是一条字操作指令,源操作数为立即寻址 方式,立即数为0010H,存放在指令的下两个单元。

《计算机组成原理》5-指令系统

◆ CPU中设置程序计数器(PC)对指令的顺序号进行计 数。PC开始时存 放程序的首地址,每执行一条指令,PC 加”1”,指出下条指令的地址, 直到程序结束。

跳跃寻址 Leabharlann 转移指令指出AA22AA33

…

…

…

…

1111 1110 A2 A3

12 位操作码

1111 1111 0000 1111 1111 0001

AA33

…

…

…

…

1111 1111 1110 A3

16 位操作码

…

…

1111 1111 1111 0000 1111 1111 1111 0001 1111 1111 1111 1111

24

双字

28

双字(地址32)▲

32

双字

36

边界未对准

地址(十进制)

字( 地址2)

半字( 地址0)

0

字节( 地址7) 字节( 地址6)

字( 地址4)

4

半字( 地址10)

半字( 地址8)

8

5.2.2 数据类型

2、数据在计算机中存放方式

存储字长内部字节的次序

例: 12345678H如何存储? 12 34 56 78H

5.3.1指令寻址

指令寻址----计算指令有效地址的方法

指令地址

指令

指令地址寻址方式

PC +1

0 LDA

11 ADD 22 DEC 33 JMP

4 LDA

5 SUB 6 INC

77 STA 88 LDA

计算机组成原理-第4章 指令系统

0000 0001

AA11

AA22

AA33

…

…

…

…

1110 A1 A2 A3

1111 0000 1111 0001

AA22

AA33

…

…

…

…

1111 1110 A1 1111

0000 0001

AA33

…

…

…

…

1111 1111 1110 A3

1111 1111 1111 0000 1111 1111 1111 0001

操作码字段

地址码字段

•操作码:表征指令的操作特性和功能。不同指令有不 同编码。

•地址码:指定参与操作的操作数的地址。

4.2 指令格式

一、操作码设计 1、分类 • 固定长度操作码:操作码的长度固定,且集中放在指令字 的一个字段中 – 便于译码,扩展性差 • 可变长度操作码:操作码的长度可变,且分散放在指令字 的不同字段中 – 能缩短指令平均长度;指令的译码复杂

2、操作码位数的确定 1)要点:组成操作码字段的位数取决于指令系统的指令条数。 2)举例 • 指令系统8条指令8=23 3位操作码 • 指令系统32条指令32=25 5位操作码 • 指令系统2n条指令n位操作码

3) 扩展(可变长度)操作码技术

•基本思路: • 让操作数地址个数多的指令操作码 字段短些,让操作数地址个数少的 指令操作码字段长些

– 等长指令字结构:在一个指令系统中,各种指令字长度是相等的。结 构简单,取指快、译码简单

– 变长 指令字结构: …………………,…………………….不相等 结 构灵活,可提高编码效率,控制复杂

4.1指令系统的基本概念

4、指令系统:一台机器中所有机器指令的集合。它对计算机性能的影响主要体 现在三个方面: – 机器的硬件结构 – 机器的系统软件 – 机器的适用范围

计算机组成原理(白中英)第4章指令系统

计算机组成原理(白中英)第4章指令系统指令系统概述寻址方式指令系统20XX年3月15日10时45分概述指令:是指示计算机某种操作的命令。

微指令,机器指令,宏指令指令系统:一台计算机中所有机器指令的集合。

它是机器硬件设计的依据,也是软件设计的基础。

它决定了一台计算机硬件的主要性能和基本功能。

是硬件和软件间的界面。

系列计算机:有共同的指令集,相同的基本体系结构。

CISC和*****X年3月15日10时45分2一个完善的指令系统应满足:1.完备性:指令丰富,功能齐全,使用方便。

1.完备性:指令丰富,功能齐全,使用方便。

完备性 2.有效性程序占空间小,执行速度快。

有效性: 2.有效性:程序占空间小,执行速度快。

3.规整性对称性,匀齐性,规整性:3.规整性:对称性,匀齐性,指令格式和数据格式的一致性。

据格式的一致性。

4.兼容性兼容性:4.兼容性:向上兼容”----系列机中低档机上运行“向上兼容”----系列机中低档机上运行的软件可以在高档机上运行。

的软件可以在高档机上运行。

20XX年3月15日10时45分计算机语言与硬件结构的关系高级语言的语句和用法与具体机器的指令系统无关;低级语言分机器语言和汇编语言,他们和具体机低级语言分机器语言和汇编语言,器的指令系统密切相关。

器的指令系统密切相关。

汇编语言与硬件的关系密切,编写的程序紧凑、汇编语言与硬件的关系密切,编写的程序紧凑、占内存小、速度快,占内存小、速度快,特别适合与编写经常与硬件打交道的系统软件;打交道的系统软件;而高级语言不涉及机器的硬件结构,通用性强、编写程序容易,件结构,通用性强、编写程序容易,特别适合与编写与硬件没有直接关系的应用软件。

编写与硬件没有直接关系的应用软件。

20XX年3月15日10时45分4概述机器指令的要素C C C C 操作码源操作数目的操作数下一条指令的引用指令字(简称指令)即表示一条指令的机器字。

指令字(简称指令)即表示一条指令的机器字。

计算机组成原理指令系统

…

Ri 操作数

Rn 寄存器

• 执行阶段不访存,只访问寄存器,执行速度快 • 寄存器个数有限,可缩短指令字长

6. 寄存器间接寻址

EA = ( Ri )

寻址特征

OP

Ri

指令中的形式地址为寄存器的编 号,寄存器的内容是操作数的有 效地址。

主存

R0

…

…

Ri 地址

操作数

…

…

MOV AX , [BX]

Rn 寄存器

PC

7. 基址寻址

(1) 采用专用基址寄存器(隐式)

EA = ( BR ) + A

BR 为基址寄存器

寻址特征

OP

A

主存

BR

ALU

操作数

• 可扩大寻址范围 • BR 内容由操作系统或管理程序确定 • 在程序的执行过程中 BR 内容不变,形式地址 A 可变

(2) 采用通用寄存器作基址寄存器(显式)

寻址特征

(1) 寄存器寻址 R (2)寄存器间接寻址 (R)

(3)直接寻址 1000 (4)存储器间接寻址 (1000)

(5)相对寻址-2000(PC) (6)立即数寻址 #2000

解: (1) Data=( R)=1000 (2) Data=( ( R) )=(1000)=2000 (3) Data=(1000)=2000 (4) Data=((1000))=(2000)=3000 (5) EA=(PC)-2000=4000-2000=2000

(1) 相对寻址举例

LDA # 0

LDX # 0

M

ADD X, D

M+1 INX

M+2 M+3

CPX # N BNE M DIV # N

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(1) 三地址双操作

50

指令

数指执令行一条三地址的加法指令需要访问514

下条指令

次主.存。

个 ( 假 单 存A显 设 元 放1号第中地指中在三单)址令,主一取地O,存第存元址次第P指放一的(双中从二令在、1A操2取5操的主第0作第0作含存二0)数一义 的 操号数存指和→为 5 作操令单,的2: 0 数A有作元第303分3号0数中四0别,取次0第指将号三令加单次,法元从第的。2二结1200000次果0从保第第1存一二号操操0到...单作作0主元数数

操作数和存放加法的结果都不需要访问主存。

(4) 零地址双操作数指令

零地址双操作数指令中只有操作码字段, 操作数地址都是隐含的。操作数在堆栈的栈 顶位置和次栈顶位置,它们分别从堆栈中弹 出,送到运算器中进行运算,运算的结果再 压入堆栈。执行一条零地址的加法指令访问 主存的次数取决的定义及性能要求 3.2 指令格式及指令类型 3.3 指令和数据的编码及寻址方式 3.4 堆栈寻址方式 3.5 RISC机型

指令系统是指一台计算机所有机

器指令的集合,构成了计算机的机器 语言,是计算机硬件与上层软件的接 口。计算机的指令系统决定了计算机 的CPU的功能和结构。CISC和RISC 是现代两大典型指令系统体系结构。 设计一台机器的指令系统应考虑到其 完备性和完整性、兼容性、均匀性、 可扩充性。

DIV X ,Y ,X

共需5 条三地址指令,每条指令4 次访存,执行此 程序共访存20 次。

(2) 二地址指令程序

MOV X ,A MUL X ,B ADD X ,C SUB X ,D MOV Y ,E ADD Y ,F DIV X ,Y 共需7 条二地址指令,MOV 指令3 次访存,算术运 算指令4 次访存,执行此程序共访存2 × 3 + 5 × 4 = 26 次。

双操作数运算类指令的执行

对于双操作数运算类指令(如加法指令)来 说,每条指令中都需要包含以下4 个地址信 息:

① 第一操作数地址A1 ; ② 第二操作数地址A2 ; ③ 操作结果存放地址A3 ; ④ 下条将要执行指令的地址A4 。

这些地址信息可以明显地给出,称为显地址; 也可以依照某种事先的约定,用隐含的方式 给出,称为隐地址。

例:分别利用三地址、二地址、一地址和零地址指令 编制计算算术表达式x = (a×b+ c - d) ÷ (e+ f)的程序。

解:假设a、b 、c 表示操作数,A 、B 、C 表示操作 数所在存储地址。

(1) 三地址指令程序

MUL A ,B ,X

ADD SUB

X ,C ,X X ,D ,X

ADD E ,F ,Y

(1) 分别用三地址、二地址、一地址和零地 址指令编写程序,计算A = (B - C) × (D -E)(不允许覆盖任何操作数,可以使 用暂存单元) 。

(2) 分别计算所写程序的总字节数。 (3) 分别计算程序执行时的访存次数。

① 三地址指令程序

SUB B ,C ,A

SUB D ,E ,Tmp

MUL A ,Tmp ,A

从100 号单元中取第一操作数,第三次从2 00 号单元中取第二操作数,第四次将加法的 结果保存到主存的100 号单元。

(3) 一地址双操作数指令

一地址双操作数指令只有一个显地 执址行,一参条一加地运址算的加的法另指一令只个需操要作访问数两来次自主 累加 存1寄,0存第0器一号次单A从c元c5中。0取指号操单作令元数的中。含取由指于义令第为,一:第操二作次数从和 运算(结A果c都c)放在O累P加(寄A存1器中),→所以A读cc取第一

② 因为操作码8 位,地址码16 位,所以: 三地址指令程序中每条指令占7 个字节,程 序的字节总数为21 个字节;

③因为三地址指令占7 个字节,每条指令需访 存4 次才能取出,接下来每条指令还需要访 存3 次,所以3 条指令共访存21 次。

① 二地址指令程序

MOV A ,B SUB A ,C MOV Tmp ,D SUB Tmp ,E MUL A ,Tmp ②二地址指令程序中每条指令占5 个字节,程 序的字节总数为25 个字节;

号单元中,结果存放在主存的3

.

00 号单元,如图 所示。

.

300

(2) 二地址双操作数指令

二地址双操作数指令有两个显地址,第一操 作数地址同时兼作结果存放地址(目的地 址执)行一,条指二令地的址含的加义法为指令同样需要访问4 次 (主存A1。第)一O次P从(5A02号)单→元中A1取指令,第二次

软件 裸机

指令系统

指令格式

操作码 (OP)

操作数(D) 寻址方式 地址码

数寄 内 值存 存

器地 址

操作码表示指令要完成的操作,其长度决 定了指令系统可以表示的指令条数;操作数是 操作的对象,对象的类型由寻址方式部分决定

指令分类:依据操作数个数来分

OP

OP D

OP

D1

D2

OP D1 D2 D3

指令中地址个数的选取要考虑诸多的因 素。从缩短程序长度,用户使用方便,增加 操作并行度等方面来看,选用三地址指令格 式较好;从缩短指令长度,减少访存次数, 简化硬件设计等方面来看,一地址指令格式 较好。对于同一个问题,用三地址指令编写 的程序最短,但指令长度最长,而用二、一、 零地址指令来编写程序,程序的长度一个比 一个长,但指令的长度一个比一个短。

共需12 条指令,其中7 条一地址的进、出栈指令, 5 条零地址的算术运算指令。进、出栈指令3 次访 存,算逻指令4 次访存,执行此程序共访存7 × 3 + 5 × 4 = 41 次。

例: 某一机器的指令系统,操作码8 位, 地址码均为16 位,CPU 与主存之间每次传 送16 位数据。A 、B 、C 、D 、E 表示字地 址,存放16 位数据。

(3) 一地址指令程序 LOAD E

ADD F

STORE X LOAD A MUL B ADD C SUB D DIV X STORE X 共需9 条一地址指令,每条指令2 次访存,执行此 程序共访存9 × 2 = 18 次。

(4) 零地址指令程序

PUSH A PUSH B MUL PUSH C ADD PUSH D SUB PUSH E PUSH F ADD DIV POP X