用veriloghdl设计计数器

FPGA实验二:基于HDL的十进制计数器

《FPGA》课程报告设计题目:基于HDL的十进制计数器学生班级:学生学号:学生姓名:指导教师:时间:成绩:一、实验目的:1.掌握基于语言的ISE设计全流程;2.熟悉、应用VerilogHDL描述数字电路;3.掌握基于Verilog的组合和时序逻辑电路的设计方法。

二、实验原理:本次实验是使用Verilog HDL进行编写十进制计数器与显示器代码而进行的实验,实验原理图如下:本次实验的内容包括十进制计数器模块,七段译码显示器模块,以及消抖模块。

十进制计数器:对输入时钟进行计数输入:CLK -------待计数的时钟CLR ---------异步清零信号,当CLR =1,输出复位为0,当CLR =0,正常计数ENA---------使能控制信号,当ENA=1,电路正常累加计数,否则电路不工作输出:SUM[3:0]---------- 计数值的个位。

即,在CLK上升沿检测到SUM=9时,SUM将被置0,开始新一轮的计数。

COUT ------------计数值的十位进位,即:只有在时钟CLK上升沿检测到SUM=9时,COUT将被置1,其余情况下COUT=0;LED显示驱动模块:输入:sum[3:0] -------待显示的数值out[6:0] ----------驱动数码管的七位数值七段数码管的字符显示真值表如下:消抖模块:三、实验过程:1.首先建立一个新的工程,添加一个新的Verilog Module,在其中编写十进制计数模块的代码,如下:module liao1(CLR,CLK,ENA,SUM,COUT);input CLR,CLK,ENA;output[3:0] SUM;output COUT;reg[3:0] SUM;reg COUT;always@(posedge CLK or posedge CLR)if(CLR)beginSUM<=4'b0000;COUT<=1'b0;endelseif(ENA)beginif(SUM==9)beginSUM<=4'b0000;COUT<=1'b1;endelsebeginSUM<=SUM+1'b1;COUT<=1'b0;endendendmodule然后执行综合,确认无误后,新建一个Test Bench WaveForm文件,进行仿真,仿真图如下:2.再新建一个Verilog Module,在其中编写七段数码显示模块的代码,如下:module liao2(SUM,out);input[3:0] SUM;output[6:0] out;reg [6:0] out;always @(SUM)begincase(SUM)4'b0000: out<=7'b0000001;4'b0001: out<=7'b1001111;4'b0010: out<=7'b0010010;4'b0011: out<=7'b0000110;4'b0100: out<=7'b1001100;4'b0101: out<=7'b0100100;4'b0110: out<=7'b0100000;4'b0111: out<=7'b0001111;4'b1000: out<=7'b0000000;4'b1001: out<=7'b0000100;default :out<=7'b0000001;endcaseendendmodule执行综合,确认无误后新建一个Test Bench WaveForm文件,进行仿真,仿真图如下:3.添加消抖模块,然后再新建一个Verilog Module,编写例化文件,制成顶层文件,其例化文件代码如下:module liao(CLK_50M,CLK,CLR,ENA,COUT,out);input CLR,CLK,ENA;input CLK_50M;output[6:0] out;output COUT;wire[3:0] SUM;debounce_module u1(CLK_50M,CLR,CLK,clk_out);liao1 u2(CLR,clk_out,ENA,SUM,COUT);liao2 u3(SUM,out);endmodule保存之后形成顶层文件:4.执行综合,确认无误后,根据实验指导书进行锁引脚操作:锁引脚完成后,修改、编辑约束文件:5.生成下载配置文件,下载到开发板进行经行验证。

用verilog HDL语言设计可逆计数器。

西安邮电学院

实验报告书

系部名称:电子工程学院学生姓名:xxx

专业名称:xxxx

班级:xxxx

实验时间:2011 年11月17日

1、掌握可逆计数器的工作原理。

2、学习用verilog HDL语言设计可逆计数器。

二、实验设备:

计算机一台,TD-EDA实验箱一台

三、实验内容:

用verilog HDL语言设计可逆计数器并进行仿真、引脚分配及下载到电路开发板进行功能验证。

四、实验程序:

module keni8(clk,enable,sum,col);

input clk,enable;

output[7:0] sum;

reg[7:0] sum;

output col;

reg col;

always @(posedge clk )

if(enable==1)

sum=sum+1;

else if(enable==0)

sum=sum-1;

else if(sum >= 8)

begin

sum=0;

col=1;

end

endmodule

五、运行结果:

1、在编程过程中,需小心谨慎,特别是注意标点符号的标注。

2、实验结果有一定的延时。

3、实验前需对TD-EDA实验箱进行了解,这样可以使实验更有效率。

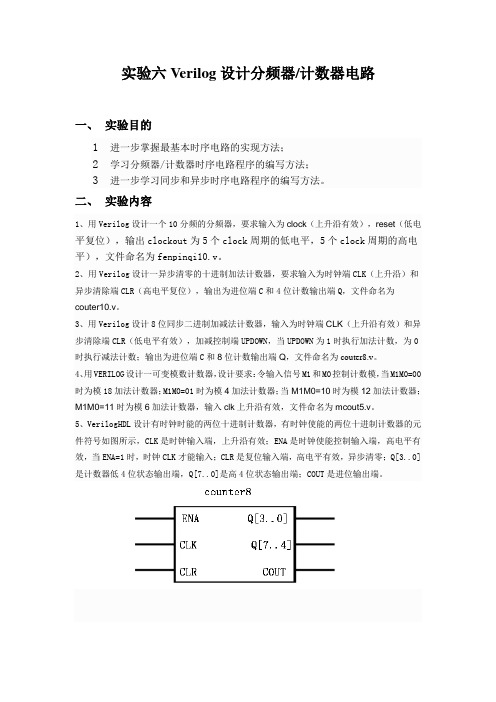

实验六Verilog设计分频器计数器电路

实验六Verilog设计分频器/计数器电路一、实验目的1进一步掌握最基本时序电路的实现方法;2学习分频器/计数器时序电路程序的编写方法;3进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为5个clock周期的低电平,5个clock周期的高电平),文件命名为fenpinqi10.v。

2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为couter10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5.v。

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。

三、实验步骤:第一个实验:1、打开QuartusII,新建一个工程f_fenpinq10yjq2、新建一个Verilog HDL文件3、输入程序:module fenpinqi10(clk,reset,clkout);input clk,reset;output clkout;reg clkout;reg[2:0] cnt;always @(posedge clk , negedge reset)beginif(!reset)begin clkout<=0;cnt<=0;endelse if(cnt==4)begin cnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule4、设置顶层实体名(点settings>general >下拉选fenpinqi10)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真结果如下:总结:仿真结果与实验一的题意相符,所以仿真正确。

使用Verilog HDL设计2位 16进制计数器,由DE2的KEY0输入计数值,在HEX1,HEX0上显示计数值。

FPGA实验实验二实验目的:学习计数器的设计、仿真和硬件测试方法。

实验内容及步骤:1.使用Verilog HDL设计2位 16进制计数器,由DE2的KEY0输入计数值,在HEX1,HEX0上显示计数值。

2.使用嵌入式逻辑分析仪进行仿真;3.将实验程序下载到DE2运行。

实验注意事项:去抖动程序:module jishu(clk,k,Rst,x0,x1,Clk,K,C,key);input clk,k,rst;output [6:0]x1;output [6:0]x0;reg [3:0]g1;reg [3:0]g0;reg [19:0]C;reg[9:0]K;always @(clk)if (C<20’d5000)C<=C+1,Clk<=0;else C<=0,Clk<=1;endalways @(Clk)if(K<10d20)K<=K+1,Key<=0;else K<=0,Key<=1;endalways @(posedge Clk ot negedge Rst)beginif(!Rst) g0<=0,g1<=0;else if(!Key)beginif(g0<4’d15)g0<=g0+1;else g0<=4’b0000;endendalways @(g0)if (g0==4’d15)if(g1<4’d15) g1<=g1+1; else g1<=4’b0000;end endalways @(g0)begincase (g0)4'b0000:x0<=7'b 1000000; 4'b0001:x0<=7'b 1111001; 4'b0010:x0<=7'b 0100100; 4'b0011:x0<=7'b 0110000; 4'b0100:x0<=7'b 0011001; 4'b0101:x0<=7'b 0010010; 4'b0110:x0<=7'b 0000010; 4'b0111:x0<=7'b 1111000; 4'b1000:x0<=7'b 0000000; 4'b1001:x0<=7'b 0011000; 4'b1010:x0<=7'b 0001000; 4'b1011:x0<=7'b 0000011; 4'b1100:x0<=7'b 1000110; 4'b1101:x0<=7'b 0100001; 4'b1110:x0<=7'b 0000110; 4'b1111:x0<=7'b 0001110; endcaseendalways @(g1)begincase (g1)4'b0000:x1<=7'b 1000000; 4'b0001:x1<=7'b 1111001; 4'b0010:x1<=7'b 0100100; 4'b0011:x1<=7'b 0110000; 4'b0100:x1<=7'b 0011001; 4'b0101:x1<=7'b 0010010; 4'b0110:x1<=7'b 0000010; 4'b0111:x1<=7'b 1111000; 4'b1000:x1<=7'b 0000000; 4'b1001:x1<=7'b 0011000; 4'b1010:x1<=7'b 0001000; 4'b1011:x1<=7'b 0000011; 4'b1100:x1<=7'b 1000110; 4'b1101:x1<=7'b 0100001; 4'b1110:x1<=7'b 0000110;4'b1111:x1<=7'b 0001110; endcaseendend module实验结果:。

Verilog_HDL十进制计数器实验Quartus90非常详细的步骤

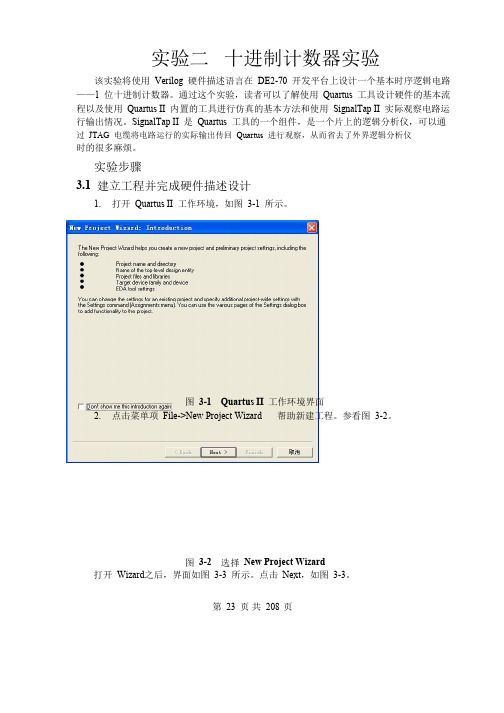

实验二十进制计数器实验该实验将使用Verilog硬件描述语言在DE2-70开发平台上设计一个基本时序逻辑电路——1位十进制计数器。

通过这个实验,读者可以了解使用Quartus工具设计硬件的基本流程以及使用Quartus II内置的工具进行仿真的基本方法和使用SignalTap II实际观察电路运行输出情况。

SignalTap II是Quartus工具的一个组件,是一个片上的逻辑分析仪,可以通过JTAG电缆将电路运行的实际输出传回Quartus进行观察,从而省去了外界逻辑分析仪时的很多麻烦。

实验步骤3.1建立工程并完成硬件描述设计1.打开Quartus II工作环境,如图3-1所示。

图3-1Quartus II工作环境界面2.点击菜单项File->New Project Wizard帮助新建工程。

参看图3-2。

图3-2选择New Project Wizard打开Wizard之后,界面如图3-3所示。

点击Next,如图3-3。

第23页共208页图3-3New Project Wizard界面3.输入工程工作路径、工程文件名以及顶层实体名。

这次实验会帮助读者理解顶层实体名和工程名的关系,记住目前指定的工程名与顶层实体名都是Counter10,输入结束后,如图3-4所示。

点击Next。

图3-4输入设计工程信息4.添加设计文件。

界面如图3-5所示。

如果用户之前已经有设计文件(比如.v文件)。

那么再次添加相应文件,如果没有完成的设计文件,点击Next之后添加并且编辑设计文件。

图3-5添加设计文件5.选择设计所用器件。

由于本次实验使用Altera公司提供的DE2-70开发板,用户必须选择与DE2-70开发板相对应的FPGA器件型号。

在Family菜单中选择Cyclone II,Package选FBGA,Pin Count选896,Speed grade 选6,确认Available devices中选中EP2C70F896C6,如图3-6。

哈尔滨工业大学数字电子技术基础课程设计报告:基于Verilog HDL语言的计数器设计

H a r b i n I n s t i t u t e o f T e c h n o l o g y

数字电子技术基础大作业报告

课程名称:数字电子技术基础

设计题目:V erilog HDL 计数器编程

院系:航天学院控制科学与工程系班级:0904102班

姓名:某某某

学号:xxxxxxxxxx

指导教师:王淑娟

设计时间:2011年12月

哈尔滨工业大学

Verilog HDL计数器编程

1设计任务

利用Verilog HDL设计一个模为学号后三位的计数器,设计要求:

1)编写源程序;

2)给出仿真电路图和仿真波形图。

2设计步骤

1.安装Quartus II软件并破解。

2.根据设计要求编写程序代码。

3.生成仿真电路图和波形如图。

3程序代码

4仿真电路图和波形图

如下图所示。

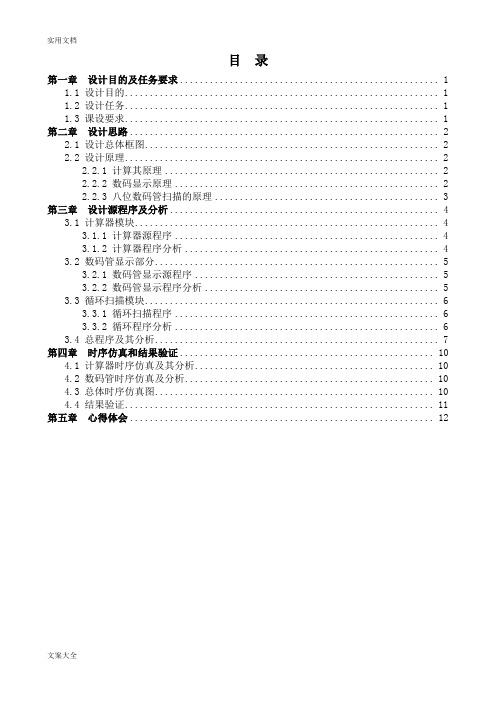

VerilogHDL简单计算器设计

实用文档目录第一章设计目的及任务要求 (1)1.1 设计目的 (1)1.2 设计任务 (1)1.3 课设要求 (1)第二章设计思路 (2)2.1 设计总体框图 (2)2.2 设计原理 (2)2.2.1 计算其原理 (2)2.2.2 数码显示原理 (2)2.2.3 八位数码管扫描的原理 (3)第三章设计源程序及分析 (4)3.1 计算器模块 (4)3.1.1 计算器源程序 (4)3.1.2 计算器程序分析 (4)3.2 数码管显示部分 (5)3.2.1 数码管显示源程序 (5)3.2.2 数码管显示程序分析 (5)3.3 循环扫描模块 (6)3.3.1 循环扫描程序 (6)3.3.2 循环程序分析 (6)3.4 总程序及其分析 (7)第四章时序仿真和结果验证 (10)4.1 计算器时序仿真及其分析 (10)4.2 数码管时序仿真及分析 (10)4.3 总体时序仿真图 (10)4.4 结果验证 (11)第五章心得体会 (12)第一章设计目的及任务要求1.1 设计目的(1)进一步加强熟练EDA基础知识。

(2)熟练掌握Quartus 6.0软件的使用以及用该软件编程和仿真的全过程。

(3)培养独立思考问题,解决问题的能力以及查阅相关资料和资料的正确使用能力,为明年的毕业设计打下良好的设计基础。

1.2 设计任务设计一个简单计算器,输入为8位二进制数,分别用两位数码管显示,输出的计算结果为16位二进制数,并用四位数码管显示,能够实现+、-、 *、/ 四种运算,其中除法的结果显示分为商和余数两部分,分别用两位数码管显示。

1.3 课设要求(1)说明题目的设计原理和思路、采用方法及设计流程。

(2)系统框图、Verilog语言设计程序或原理图。

(3)对各子模块的功能以及各子模块之间的关系做较详细的描述。

(4)详细说明调试方法和调试过程。

(5)说明测试结果:仿真时序图和结果显示图,并对其进行说明和分析。

第二章设计思路2.1 设计总体框图有分析可知,本次课程设计可以分成五个木块来实现相应的功能,分别是输入模块,计算模块,扫描模块,输出模块以及显示模块。

verilog hdl开关计数回路编程

Verilog HDL开关计数回路编程在数字电路设计中,开关计数回路是一种非常重要的电路结构。

它可以用来实现计数功能,是数字系统中常见的一种功能模块。

在本文中,我将就Verilog HDL开关计数回路编程这一主题展开深入探讨,并带你逐步理解这个概念。

1. Verilog HDL简介Verilog Hardware Description Language(HDL)是一种硬件描述语言,用于描述、建模和仿真数字电路。

它是一种行为级的描述语言,在FPGA和ASIC设计中被广泛应用。

Verilog HDL的使用使数字电路设计工程师能够更轻松地实现所需的功能,并对其进行仿真和验证。

2. 开关计数回路的原理开关计数回路是一种使用触发器和计数器构成的计数电路。

在Verilog HDL中,我们可以通过描述触发器的行为和计数器的逻辑来实现开关计数回路。

触发器用于存储当前的计数值,而计数器用于控制计数的逻辑。

通常,我们会使用寄存器或者移位寄存器来实现计数器。

这种组合结构可以实现从二进制数0到N的自动计数。

3. Verilog HDL中的开关计数回路编程在Verilog HDL中,我们可以通过module、always、initial等关键字来描述开关计数回路的行为。

我们需要定义输入和输出接口,然后编写描述触发器和计数器行为的代码。

在Verilog HDL中,我们可以使用时钟信号来控制计数的节奏,通过简单的逻辑操作实现计数的增加和重置。

这样,我们就可以完整地描述一个开关计数回路的功能。

4. 实例分析下面,我以一个4位二进制计数器为例,来展示Verilog HDL中开关计数回路的编程过程:module counter(input clk,input rst,output reg[3:0] count);always @(posedge clk or posedge rst)beginif (rst)count <= 4'b0000;elsecount <= count + 1;endendmodule在这个例子中,我们定义了一个4位二进制计数器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用Verilog HDL设计计数器

一、实验目的

1. 学习使用Verilog HDL语言,并学会使用进行QuartusⅡ软件编

程和仿真;

2. 掌握数字电路的设计方法,熟悉设计过程及其步骤;

3. 培养学生的动手能力,能学以致用,为今后从事电子线路设计

打下良好基础;

4. 巩固加深对数电知识的理解,在仿真调试过程中,能结合原理

来分析实验现象;

二、实验内容

1.设计内容及要求

1)利用Verilog HDL设计一个以自己学号后三位为模的计数器;

2)编写源程序;

3)给出仿真电路图和仿真波形图;

2.需求分析:

由于本人的学号后3位为212,所以应编一个以212为模的加法计数器。

若采用同步清零的方法,则计数为0~211,化为二进制数即为0 0000 0000计到0 1101 0011。

3.编写源代码:

module count_212(out,data,load,reset,clk);

output [8:0] out;

input [8:0] data;

input load,reset,clk;

reg [8:0] out;

always @(posedge clk)

+

<

计数器功能表

Clk Reset Load Out

上升沿0X清零

上升沿10置数(data)

上升沿11计数

2. 应熟知计数器的使用方法,并能设计出任意进制的计数器,在设计时才能得心应手。

计数进制的改变,包括清零法(同步清零和异步清零)和置数法。

假定计数器的计数进制为N,要将其改为M进制的计数器,M < N 。

当计数器从全零状态开始计数,若采用同步清零法,设计时应经过M-1个状态后清零;若采用异步清零法,设计时应经过M个状态后清零。

这样就跳过了M个状态,实现了M进制计数器。

因为采用异步清零法会产生清零不可靠的问题,本实验采用的为同步清零法。

3. 本实验采用的是数据流描述方式来描述电路,通过assign 连续赋值实现组合逻辑功能,使用简单,语句易于读懂。

4. 调试过程中,应沉着冷静,出现错误时,应该根据数电知识原理来分析,找

出错误原因,对症下药;也可上网搜查该错误的含义,可能是软件的使用方法不对。