千兆以太网原理图

以太网技术

2.2 以太网技术以太网是最早使用的局域网,也是目前使用最广泛的网络。

本节内容包括以太网的诞生及标准系列、命名规则、10Mbps、100Mbps、千兆以太网、层次结构及其功能模块、帧结构、媒体访问控制方式、共享式以太网、交换式以太网。

2.2.1 以太网的发展1.以太网的起源以太网(Ethernet)技术于1973年由施乐公司研发,而后由Xerox、Digital Equipment 和Intel三家公司开发成为局域网组网规范,并于80年代初首次出版,称为DIX1.0。

1982年修改后的版本为DIX2.0。

这三家公司将此规范提交给IEEE(电子电气工程师协会)802委员会,经过IEEE成员的修改并通过,变成了IEEE的正式标准,并编号为IEEE802.3。

Ethernet和IEEE802.3虽然有很多规定不同,但术语Ethernet通常认为与802.3是兼容的。

1983年,IEEE将802.3标准提交给国际标准化组织(ISO)第一联合技术委员会(JTC1),再次经过修订变成了国际标准ISO802.3。

2.几个主要以太网标准1982年10BASE5(DIX)802.3 粗同轴电缆1985年10BASE2 802.3a 细同轴电缆1990年10BASET 802.3j 双绞线1993年10BASEF 802.3j 光纤1995年100BASET 802.3u 双绞线1997年全双工以太网802.3x 双绞线、光纤1998年1000BASEX 802.3z 双绞线、光纤2000年1000BASET 802.3ab 双绞线3.IEEE 802.3命名规则– IEEE 802.3 X TYPE-Y NAME– X表示传输速率<1> 10表示10Mbps<2> 100表示100Mbps<3> 1000表示1000Mbps– TYPE表示信号传输方式<1> Base指基带传输<2> Broad指宽带传输– Y表示传输媒体<1> 5指粗同轴电缆<2> 2指细同轴电缆<3> T指双绞线<4> F指光纤举例:10BASE-5,表示该以太网的带宽为10Mb/s,以基带传输,最大传输距离为500m;10BASE-TX,表示该以太网的带宽为100Mb/s,以基带传输,传输介质(媒体)为双绞线。

二层基本知识_转发_协议

二层交换基本过程

通过识别MAC进行

A

Switch

B

C

D

二层交换机工作模型

工作在链路层

应应应 表表应 会会应 传传应 网网应 链链应 物物应 链链应 物物应 链链应 物物应 应应应 表表应 会会应

S witch

传传应 网网应 链链应 物物应

二层交换引擎

ASIC--Application Specific Integrated Circuit L2FDB—Layer 2 forwarding database

. .

出口集合 {1} {2} {3}

. .

交换机工作过程—转发

MAC 1234.ABCD.0001 1234.ABCD.0002 1234.ADCB.0005

. .

出口集合 {1} {2} {3}

. .

交换机接收到数据帧后,根据目的 地址查询CAM,找到出口后,把 数据包从该出口集合发送出去。 在单播的情况下,出口列表集合只 有一个元素,但在多播情况下,出 口列表集合就可能不只一个元素。 CAUTION: 多播情况下,CAM表项的建立不是 通过学习得到的,而是通过IGMP 窥探,CGMP等协议获得的。

MACD MACA

端口2

......

MACD

MACA

端口1

......

MAC地地

所所所所

MACA MACB MACC MACD

1 1 2 2

二层交换机的局限性

二层交换机将网段上的冲突域限制到了端口级、但是无法限制广播域的大小 端口间已经不存在冲突 但是广播域仍然为整个LAN

LAN LAN

广广广

冲冲广

Frame Load:有效载荷 FCS: 帧检测序列

epon

长光OLT1500,含8个PON口

1*4PLC光分路

1*8光分路

分线箱1

分线箱

光放大器

1*10FBT光分路

设备箱

设备箱

用户EOC终端

用户EOC终端

分前端机房

主干光缆网络

电缆分配网络

长光OLT1500,含8个PON口

1*4PLC光分路

1*8光分路

分线箱1

分线箱

光放大器

长光ONU分为三个型号:野外式,用于落地设备箱的安装;楼道式,用于楼道设备箱的安装;野外设备箱式,针对我们目前的网络结构定制,用于野外设备箱的安装。

光分路器采用平面波导式(PLC),分为1分4型(主要用于机房,直接连接PON口)和1分8型(主要用于线路分线箱)。

1*10FBT光分路

设备箱

设备箱

用户EOC终端

用户EOC终端

分前端机房

主干光缆网络

电缆分配网络

图1

2、EOC网络

EOC即将以太网信号调制叠加在同轴电缆网络上传输的技术,该技术种类繁多,目前我们选用美国因特龙芯片的Home plug Av 方案,信号传输频带为7~30MHz。

千兆网口Freescale ETSEC + Marvell 88E1111 uboot Linux 驱动分析

在连续两个平台的uboot和Linux系统移植过程中,在千兆网口调试这块都遇到了很大的麻烦。

由于寄存器数量庞大,千兆网口MAC和PHY内部结构复杂,MAC和PHY接口种类多,千兆以太网驱动的调试成了系统移植过程中最让人烦心的一个环节。

就像火箭队,每次都让球迷无比揪心,不是输的窝囊,就是伤兵满营,现在新赛季又两连败了,打的比勇士还勇士,后场两个比我还瘦的家伙,怎么防守。

算了,不扯这么多了,今天要说的是网口MAC+PHY的一些原理和代码分析。

(以Freescale的ETSEC和Marvell的88E1111为例。

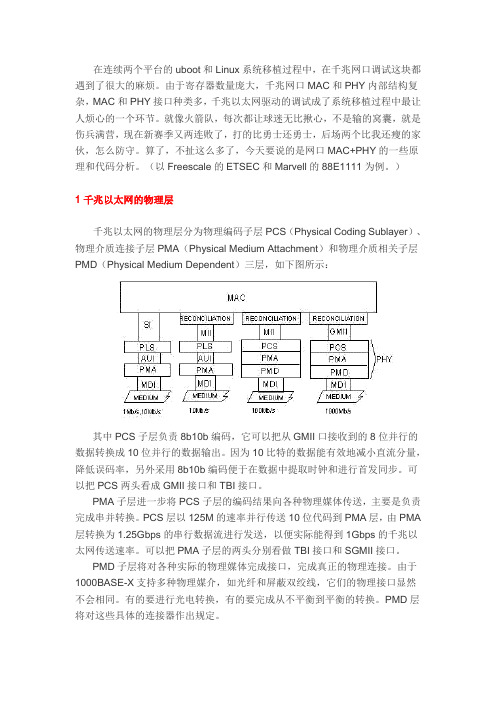

)1 千兆以太网的物理层千兆以太网的物理层分为物理编码子层PCS(Physical Coding Sublayer)、物理介质连接子层PMA(Physical Medium Attachment)和物理介质相关子层PMD(Physical Medium Dependent)三层,如下图所示:其中PCS子层负责8b10b编码,它可以把从GMII口接收到的8位并行的数据转换成10位并行的数据输出。

因为10比特的数据能有效地减小直流分量,降低误码率,另外采用8b10b编码便于在数据中提取时钟和进行首发同步。

可以把PCS两头看成GMII接口和TBI接口。

PMA子层进一步将PCS子层的编码结果向各种物理媒体传送,主要是负责完成串并转换。

PCS层以125M的速率并行传送10位代码到PMA层,由PMA 层转换为1.25Gbps的串行数据流进行发送,以便实际能得到1Gbps的千兆以太网传送速率。

可以把PMA子层的两头分别看做TBI接口和SGMII接口。

PMD子层将对各种实际的物理媒体完成接口,完成真正的物理连接。

由于1000BASE-X支持多种物理媒介,如光纤和屏蔽双绞线,它们的物理接口显然不会相同。

有的要进行光电转换,有的要完成从不平衡到平衡的转换。

PMD层将对这些具体的连接器作出规定。

2 Freescale 的ETSEC与PHY之间的接口Freescale的MPC8314和P2020都自带了三速以太网控制器ETSEC,可以提供10M,100M,1000M三种速率的接口。

POE原理介绍

课程内容

POE简介

POE供电原理

应用实例

测试用例

应用实例

支持十兆百兆千兆POE供电器示意图

应用实例

支持十兆百兆千兆POE供电器原理图

课程内容

PO

POE网线检测

测试设备:POE供电器、网线 测试工具:万用表 测试方法:万用表接触网线水晶头各脚 1、通过10M/100M POE供电器后网线各脚功能

但理论上,802.3at规范中重要的改进之一是将一对线电流的上限值规定为600mA。现在 ,PSE必须要能够连续提供至少600mA的电流,一个50V的最小输出电压和57V的最大输出电 压。这转化为一个34.2W的PSE输出功率。电缆电阻的模型化设计值不大于12.5Ω,根据 , 有4.5W的损耗,因而在PD连接器上产生了34.2W- 4.5W= 29.7W的可用功率。有必要把48V 转换效率考虑在内,有0.9W的损耗,这样最终传输至PD负载的可用功率约为29.7 W -0.9W = 28.8W。 如果在两对线上同时施加电压,传递两组600mA的电流,理论输出功率可达到28.8W * 2 = 57.6W。

测试用例

测试案例

测试目的 测试POE交换机与POE供电器混合工作,以及长网线供电 测试方式 按工程接法连接交换机、供电器和AP,采用自制POE网口转接板串在 AP网口处,用万用表测试到AP侧的实际供电线对地电压。 测试连接图如下:

测试用例

测试案例

AP1到AP8是500MW高功率AP,采用弘浩供电器供电;AP9是100MW 双频AP,直接用烽火POE交换机供电。 POE网口转接板有两个直接连通网口,并有引出网线的1、3、5、8 的金属片方便测量网线上的电压(用普通万用表电压档测量1、3或5、8 )。

以太网简要教程

以太网简要教程一、概述通常我们所说的以太网主要是指以下三种不同的局域网技术:以太网/IEEE 802.3—采用同轴电缆作为网络媒体,传输速率达到10Mbps;100Mbps以太网—又称为快速以太网,采用双绞线作为网络媒体,传输速率达到100Mbps;1000Mbps以太网—又称为千兆以太网,采用光缆或双绞线作为网络媒体,传输速率达到1000Mbps(1Gbps)以太网以其高度灵活,相对简单,易于实现的特点,成为当今最重要的一种局域网建网技术。

虽然其它网络技术也曾经被认为可以取代以太网的地位,但是绝大多数的网络管理人员仍然把将以太网作为首选的网络解决方案。

为了使以太网更加完善,解决所面临的各种问题和局限,一些业界主导厂商和标准制定组织不断的对以太网规范做出修订和改进。

也许,有的人会认为以太网的扩展性能相对较差,但是以太网所采用的传输机制仍然是目前网络数据传输的重要基础。

二、以太网工作原理以太网是由Xeros公司开发的一种基带局域网技术,使用同轴电缆作为网络媒体,采用载波多路访问和碰撞检测(CSMA/CD)机制,数据传输速率达到10Mbps。

虽然以太网是由Xeros公司早在70年代最先研制成功,但是如今以太网一词更多的被用来指各种采用CSMA/CD技术的局域网。

以太网被设计用来满足非持续性网络数据传输的需要,而IEEE802.3规范则是基于最初的以太网技术于1980年制定。

以太网版本2.0由Digital Equipment Corporation、Intel、和Xeros 三家公司联合开发,与IEEE 802.3规范相互兼容。

太网结构示意图如下:以太网/IEEE 802.3通常使用专门的网络接口卡或通过系统主电路板上的电路实现。

以太网使用收发器与网络媒体进行连接。

收发器可以完成多种物理层功能,其中包括对网络碰撞进行检测。

收发器可以作为独立的设备通过电缆与终端站连接,也可以直接被集成到终端站的网卡当中。

FMC 4 路千兆以太网模块 FL2121 用户手册说明书

FMC4路千兆以太网模块FL2121用户手册Rev1.0版权声明:Copyright©2012-2018芯驿电子科技(上海)有限公司公司网址:技术论坛:官方旗舰店:邮箱:**************.cn电话:************传真:************ALINX微信公众号:文档修订记录:版本时间描述1.02022/11/20First Release第一部分FMC高速以太网模块说明介绍黑金FMC千兆以太网模块FL2121为4路10/100/1000Mbps自适应的以太网通信接口模块。

FMC模块的千兆PHY芯片采用了4片景略半导体公司的JL2121以太网PHY芯片,支持10/100/1000Mbps网络传输速率。

4路网络接口采用常用的RJ45连接器跟外部网络连接和通信。

模块有一个标准的LPC的FMC接口,用于连接FPGA开发板,FMC的连接器型号为:ASP_134604_01FL2121模块实物照片如下:FL2121模块实物图1.1FL2121模块的参数说明以下为FL2121千兆以太网模块的详细参数:千兆以太网芯片:4片JL2121网络接口:4路RJ45;以太网通信速率:支持10/100/1000Mbps;通信方式:RGMII;配置接口:MDIO接口;工作温度:-40°~85°;1.2FL2121模块的结构图FL2121千兆以太网模块尺寸结构图第二部分模块功能说明2.1FL2121模块原理框图FL2121模块的原理设计框图如下:2.2太网芯片以太网芯片采用景略半导体的工业级以太网GPHY芯片(JL2121-N040I)为用户提供网络通信服务。

PS端的以太网PHY芯片是连接到ZYNQ的PS端BANK502的MIO接口上。

PL端的以太网PHY芯片是连接到BANK66的IO上。

JL2121芯片支持10/100/1000Mbps网络传输速率,通过RGMII接口跟MPSOC 系统的MAC层进行数据通信。

超五类与六类实现千兆传输的区别

超五类系统与六类系统实现千兆传输的区别正如我们所知的,超五类系统只是“能够”支持千兆以太网,而六类系统才是“真正有保证”地运用千兆以太网。

这种保证的优势具体体现在相对于普通超五类系统,六类系统拥有与生俱来更佳的技术参数,使得其更能够适应当下的建筑环境,尤其是在那些集中了大量的双绞线并拥有很多干扰源的地方,比如说拥有许多电器(电脑、电话、各种生产设备等)的房间、设备间、邻近有电力线、照明线的地方。

可以说随着科技的发达、人们生活方式的发展,这样的环境现在早已无处不在环绕在我们的周围,这就造成了在绝大多数使用超五类系统的的千兆以太网系统在投入使用后,实际网络速度不足设计速度的30%。

以下就通过超五类系统及六类系统传输千兆以太网的不同的方式为您揭示造成以上差别的原因:超五类系统1000Base-T就是超五类系统传输千兆网络所采用的标准。

1000Base-T标准可支持在符合ANSI/TIA/EIA-568A(1995)标准的五类双绞线上运行千兆以太网。

1000Base-T采用4对五类双绞线完成1000Mbps的数据传送,每一对双绞线传送250Mbps的数据流。

但因为五类及超五类双绞线的设计带宽仅有100MHz,要实现双向传输1000Mbps的网络,必须满足以下要求:● 4对线全都使用(全双工)● 全双工运行网络设备需要串扰/回声消除技术● 4级编码(PAM-5)● 每个信号电平代表2比特● 每秒发送125M符号● 与100Base-Tx符号速率相同● 降低噪声的干扰每对线支持250Mbps的数据速率(每个方向)下图就是4级信号编码的原理图可见正常的方波电压被压缩调制成4个台阶分别对应4个2位二进制数,这就造成了4级信号之间的峰值电压差距不大,受干扰叠加后容易造成误码。

再加上每条链路必须双向全双工传输信号,误码的可能更大大加强。

所以为了能使网络设备能正确地辨识每一个方波信号,在网络设备中必须增加大量的串扰/回声消除DSP处理器,这就造成了支持1000Base-T 的交换机平均端口成本大大增加,即需要复杂而特殊的网络设备接收电路设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4

3

2

1

Block diagram of board

Table on contents:

D

Page 1: Block diagram Page 2: Top_sheet Page 3: CPU interface Flash + RAM Page 4: Local power regulators Page 5: Switch power conections Page 6: SW_Cat5_Port_0-7 Page 7: PHY MISC Page 8: PHY Ports Page 9: PHY Power

TP3 J_nRST

3V3

R7 0 0603 C349

3V3

C

100n 0603

C

R16 130k 0603

3V3 (IF U6 INSTALLED - 2K) U5 TCM809TVNB713-NOPOP SOT-23 2 nRESET Xtal mount option or Not mount

R13 330R SW_LED_10 0603

44 45

54 51

R23 330R SW_LED_13 0603

R19 SW_LED_2

330R 0603

YL

44 45

54 51

R18 330R SW_LED_5 0603

46 47

52 49

R24 330R SW_LED_4 0603

48

50

R26

Xtal1 Xtal2

L2 L1

C8

27pF-NOPOP 0603

R15 330R SW_LED_11 0603

46 47

52 49

R28 330R SW_LED_12 0603

R20 SW_LED_3

330R 0603

GR

2.00k 0603

U1C VSC7388-SparX-G8

C6 27pF-NOPOP X1 0603 25MHz-NOPOP

Main change(s): Initial release for PCB layout

1 1 1 1

A

A

H10 fiducial_BGA

H9 fiducial_BGA

H8 fiducial_BGA

Hoerkaer 16 DK-2730 Herlev

Vitesse Semiconductor, Copyright 2003-2006

1

Rev 01-05 9

1

of

5

4

3

2

5

4

3

2

1

3V3 3V3 R42 SW1 5 2 4 1 3 R45 2.00k 0603 R44 330R R43

Status indicator, CPU controlled

330R 330R LED-GREEN D11 1206 LED-ORANGE D12 1206 1 2 U1B VSC7388-SparX-G8 SW_IO0 SW_IO1 SW_IO2 SW_IO3 JTAG_nRST JTAG_TCK JTAG_TMS JTAG_TDI JTAG_TDO AL1 AL2 AM1 AM2 AJ1 AJ2 AK1 AK2 AH2 GPIO_0 GPIO_1 GPIO_2 GPIO_3 JTAG_nTRST JTAG_TCK JTAG_TMS JTAG_TDI JTAG_TDO Reserved_2 Reserved_1 Reserved_0 Reserved_5 Test_Code2 Test_Code1 Test_Code0 Reserved_3 Reserved_4 H38 C28 C11 J2 AR1 AP2 AP1 AN2 AN1 R5 2.00k 1% 0603 R9 2.00k 1% 0603 TP31 TP32 TP33 TP34 3V3 TP35 TP37 TP39

R36 2.00k Y2 4

N3141750

SW_LED_8

J302E RJ-45_TAB_UP 41 GR Port 1, left GR Port 4, right

3V3 55 SW_LED_15 SW_LED_0

J301E RJ-45_TAB_UP 41 GR Port 1, left Port 4, right GR

B

Close J5 and open J1 when programming serial EEPROM

TP0805 nRESET

LABEL: 3.3V

3V3

Vin D13 A K 1 L6 2 1206 R335 2.00k-NOPOP 0603

1V2

TP12 TP0805 1.2V

Local 3V3 and 1V2 DC-DC converters.

42 43

56 53 YL

R22 330R SW_LED_14 0603

R11 SW_LED_1

330R 0603

42 43

56 53 YL

R17 330R SW_LED_6 0603

YL

GR

GR

GR

YL Port 2

Port 3

YL Port 2

C9 G39 H39 Ref_Filt_0 Ref_RExt_0 Ref_Filt_1 Ref_RExt_1 H1 J1 R31

C47 100n 0603

3V3

LED outputs: two LEDs per port + one optional.

R10 2.00k-NOPOP 1% 0603 R333 2.00k-NOPOP 1% 0603 3V3 SW_LED_0 SW_LED_1 R434 D30 1206 TP61 LED-ORANGE-NOPOP SW_LED_2 SW_LED_3 330R-NOPOP 0603 R436 D32 1206 TP65 LED-ORANGE-NOPOP SW_LED_4 SW_LED_5 330R-NOPOP 0603 R438 D34 1206 TP69 LED-ORANGE-NOPOP SW_LED_6 SW_LED_7 330R-NOPOP 0603 R440 D36 1206 TP73 LED-ORANGE-NOPOP K39 K38 L39 L38 M39 M38 N39 N38 P39 P38 R39 R38 T39 T38 U39 U38 U1N VSC7388-SparX-G8 LED0_0/SD LED0_1/SCK LED0_2 LED0_3 LED1_0 LED1_1 LED1_2 LED1_3 LED2_0 LED2_1 LED2_2 LED2_3 LED3_0 LED3_1 LED3_2 LED3_3 LED4_0 LED4_1 LED4_2 LED4_3 LED5_0 LED5_1 LED5_2 LED5_3 LED6_0 LED6_1 LED6_2 LED6_3 LED7_0 LED7_1 LED7_2 LED7_3 Y2 Y1 W2 W1 V2 V1 U2 U1 T2 T1 R2 R1 P2 P1 N2 N1 SW_LED_8 SW_LED_9 D31 TP62 LED-ORANGE-NOPOP SW_LED_10 SW_LED_11 D33 TP66 LED-ORANGE-NOPOP SW_LED_12 SW_LED_13 D35 TP70 LED-ORANGE-NOPOP SW_LED_14 SW_LED_15 D37 TP74 LED-ORANGE-NOPOP 1206 R441 330R-NOPOP 0603 1206 R439 330R-NOPOP 0603 1206 R437 330R-NOPOP 0603 1206 R435 330R-NOPOP 0603 3V3

DD-SS24T3-S SMB R3 0-NOPOP 0603

A

C(+) (-)

1 2

A

D14 LED-ORANGE-NOPOP 1206 Power Schematic5 RJ45 Schematic6 Schematic8 COOPERS' PORTS Schematic9 Coopers' Power

D

C

C

B

B

H5 Logo_Vitesse_10mm

VITESSE

H1 3_5mm_8via

H6 ECO_Box ECO:

H7 Ser_no_Box No:

H2 3_5mm_8via

H3 3_5mm_8via

H4 3_5mm_8via

Version: 01-00

Date: 16-Nov-05

Author: NGITNIK

C350 1.0uF 0603

2 1

YL

R30

2.00k 0603

2.00k 0603

R21

330R 0603

Hale Waihona Puke 4850R27330R 0603

R14

330R 0603

YL

1.0uF 0603

Port 3

0 0603

2.00k 0603 1.0uF 0603

AH1 V38

Osc_En Clk125_En

D

D

J303 HD-1X2-TT No Jumper = Initialize with Cooper devices present Jumper = Initialize as Luton switch with no Coopers 3V3

330R-NOPOP 0603

R1 2.00k-NOPOP 0603 1%

330R 0603

B

TP7 nRESET nRESET MDIO MDC R8 130k-NOPOP 0603 CPU interfaces Schematic3 MDIO MDC SW_IO0 SW_IO1 SW_IO2 SW_IO3 COOPERS' MISC. MDIO MDC SCHEMATIC7 TP1 GND TP2 GND TP8 TP9 TP10 TP0805 TP0805 TP0805 GND GND GND C31 100n 0603 C34 100n 0603 C36 100n 0603 C30 100n 0603 C33 100n 0603 C29 100n 0603 C35 100n 0603 C40 100n 0603 C39 100n 0603 C41 100n 0603 C42 100n 0603 C43 100n 0603 C45 100n 0603 C46 100n 0603 C10 100n 0603 C11 100n 0603 C12 100n 0603 C13 100n 0603 C14 100n 0603 C16 100n 0603 C17 100n 0603 C15 1.0uF 0603 SW_IO0 SW_IO1 SW_IO2 SW_IO3 TP11 TP0805