数字逻辑设计及应用 本科3 答案82870

数字逻辑与数字系统设计习题参考答案

(4)(0.785)10=(0.011110000101)8421BCD

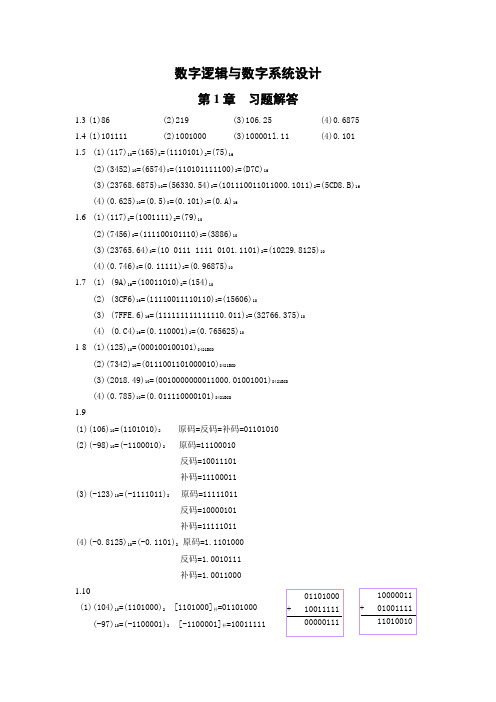

1.9

(1)(106)10=(1101010)2原码=反码=补码=01101010

(2)(-98)10=(-1100010)2原码=11100010

不考虑无关项,化简后的表达式:

F=

按考虑无关项化简结果绘制的逻辑电路习题4.10图(a)所示:

习题4.10图(a)

按不考虑无关项化简结果绘制的逻辑电路如习题4.10图(b)所示

习题4.10图(b)

4.11解:这是一个优先编码器的问题,设特快为A,直快为B,慢车为C,没有开车要求,输出为0,若A要求开车则输出,1,B要求开车输出为2,C要求开车输出3,根据A-B-C的优先顺序列功能表如下:

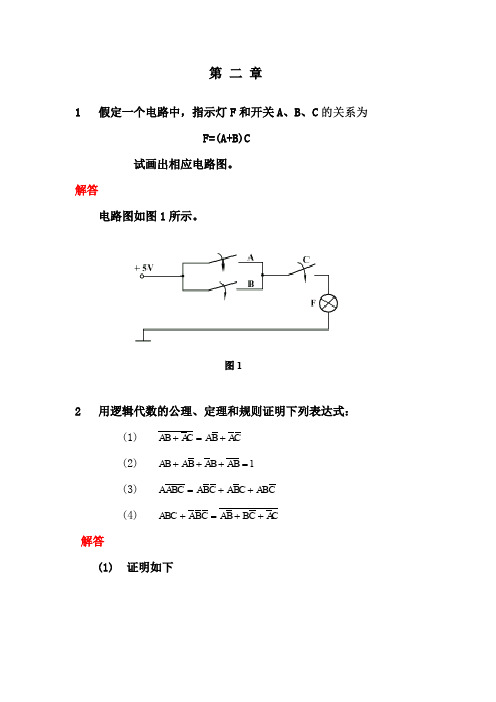

4.6解:根据题意:F= ,所以,可绘制电路如习题4.6图所示

习题4.6图

4.7解:根据题意:F= ,所以,可绘制电路如习题4.7图所示

习题4.7图

4.8解:

习题4.8图

4.9解:根据题意,三个变量有两个为1的卡诺图如习题4.9图(a)所示:

习题4.9图(a)

由此可列出逻辑表达式为:F= ,根据逻辑表达式可绘制逻辑电路习题4.9图(b)所示:

输入

输出

A

B

C

T1

T0

0

0

0

0

0

0

0

1

1

1

0

1

0

1

0

0

1

1

1

0

1

0

0

0

1

1

0

数字逻辑课后习题答案

第一章开关理论基础1.将下列十进制数化为二进制数和八进制数十进制二进制八进制491100016153110101651271111111177635100111101111737.493111.11117.7479.4310011001.0110111231.3342.将下列二进制数转换成十进制数和八进制数二进制十进制八进制1010101211110161751011100921340.100110.593750.4610111147570110113153.将下列十进制数转换成8421BCD码1997=000110011001011165.312=01100101.0011000100103.1416=0011.00010100000101100.9475=0.10010100011101014.列出真值表,写出X的真值表达式A B C X00000010010001111000101111011111X=A BC+A B C+AB C+ABC5.求下列函数的值当A,B,C为0,1,0时:A B+BC=1(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,1,0时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,0,1时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=06.用真值表证明下列恒等式(1)(A⊕B)⊕C=A⊕(B⊕C)A B C(A⊕B)⊕C A⊕(B⊕C)0000000111010110110010011101001100011111所以由真值表得证。

(2)A⊕B⊕C=A⊕B⊕CA B C A⊕B⊕C A⊕B⊕C00011001000100001111100001011111011111007.证明下列等式(1)A+A B=A+B 证明:左边=A+A B=A(B+B )+A B =AB+A B +A B =AB+A B +AB+A B =A+B =右边(2)ABC+A B C+AB C =AB+AC 证明:左边=ABC+A B C+AB C=ABC+A B C+AB C +ABC =AC(B+B )+AB(C+C )=AB+AC =右边(3)E D C CD A C B A A )(++++=A+CD+E证明:左边=ED C CD A C B A A )(++++=A+CD+A B C +CDE =A+CD+CD E =A+CD+E =右边(4)C B A C B A B A ++=CB C A B A ++证明:左边=CB AC B A B A ++=C B A C AB C B A B A +++)(=C B C A B A ++=右边8.用布尔代数化简下列各逻辑函数表达式(1)F=A+ABC+A C B +CB+C B =A+BC+C B (2)F=(A+B+C )(A+B+C)=(A+B)+C C =A+B (3)F=ABC D +ABD+BC D +ABCD+B C =AB+BC+BD (4)F=C AB C B BC A AC +++=BC(5)F=)()()()(B A B A B A B A ++++=B A 9.将下列函数展开为最小项表达式(1)F(A,B,C)=Σ(1,4,5,6,7)(2)F(A,B,C,D)=Σ(4,5,6,7,9,12,14)10.用卡诺图化简下列各式(1)CAB C B BC A AC F +++=0 ABC00 01 11 1011111化简得F=C(2)CB A D A B A DC AB CD B A F++++=111111AB CD 00 01 11 1000011110化简得F=DA B A +(3)F(A,B,C,D)=∑m (0,1,2,5,6,7,8,9,13,14)1111111111ABCD 00 01 11 1000011110化简得F=DBC D C A BC A C B D C ++++(4)F(A,B,C,D)=∑m (0,13,14,15)+∑ϕ(1,2,3,9,10,11)Φ1ΦΦ1ΦΦ1Φ1AB CD 00 01 11 1000011110化简得F=ACAD B A ++11.利用与非门实现下列函数,并画出逻辑图。

2012-2013-2《数字逻辑设计及应用》期末考试题-A参考解答

电子科技大学2012 -2013学年第二学期期末考试 A 卷课程名称:_数字逻辑设计及应用__ 考试形式:闭卷考试日期:20 13 年07 月05 日考试时长:_120___分钟课程成绩构成:平时30 %,期中30 %,实验0 %,期末40 %本试卷试题由___七__部分构成,共__7___页。

I. Fill out your answers in the blanks (3’ X 10=30’)1. If a 74x138 binary decoder has 110 on its inputs CBA, the active LOW output Y5 should be ( 1 or high ).2. If the next state of the unused states are marked as “don’t-cares” when designing a finite state machine, this approach is called minimal ( cost ) approach.3.The RCO_L of 4-bit counter 74x169 is ( 0 or low ) when counting to 0000 in decreasing order.4. To design a "001010" serial sequence generator by shift registers, the shift register should need ( 4 ) bit at least.5. One state transition equation is Q*=JQ’+K’Q. If we use T flip-flop with enable to complete the equation,the enable input of T flip-flop should have the function EN=( JQ’+KQ ).6. A 4-bit Binary counter can have ( 16 ) normal states at most, 4-bit Johnson counter with no self-correction can have ( 8 ) normal states, 4-bit linear feedback shift-register (LFSR) counter with self-correction can have ( 16 ) normal states.7. If we use a ROM, whose capacity is 16 × 4 bits, to construct a 4-bit binary code to gray code converter, when the address inputs are 1001, ( 1101 ) will be the output.8. When the input is 10000000 of an 8 bit DAC, the corresponding output voltage is 2V. The output voltage is ( 3.98 ) V when the input is 11111111.II. Please select the only one correct answer in the following questions.(2’ X 5=10’)1. If a 74x85 magnitude comparator has ALTBIN=1, AGTBIN=0, AEQBIN=0, A3A2A1A0=1101, B3B2B1B0=0111 on its inputs, the outputs are ( D ).A) ALTBOUT=0, AEQBOUT=0, AGTBOUT=0 B) ALTBOUT=1, AEQBOUT=0, AGTBOUT=0C) ALTBOUT=1, AEQBOUT=0, AGTBOUT=1 D) ALTBOUT=0, AEQBOUT=0, AGTBOUT=12. As shown in Figure 1, what would the outputs of the 4-bit adder 74x283 be ( B ) when A3A2A1A0=0100, B3B2B1B0=1110 and S/A=1.A) C4=1, S3S2S1S0=0010 B) C4=0, S3S2S1S0=0110 C) C4=0, S3S2S1S0=1010D) C4=0, S3S2S1S0=1110Figure 13. Which of the following statements is INCORRECT? ( A )A) A D latch is edge triggered and it will follow the input as long as the control input C isactive low.B) A D flip flop is edge triggered and its output will not change until the edge of thecontrolling CLK signal.C) An S-R latch may go into metastable state if both S and R are changing from 11 to 00simultaneously.D) The pulse applying to any input of an S -R latch must meet the minimum pulse width requirement.4. The capacity of a memory that has 13 bits address bus and can store 8 bits at each address is ( B ).A) 8192 B) 65536 C) 104 D) 2565. Which state in Figure 2 is NOT ambiguous ( C ).A) A B) B C) C and D D) CABCD WX W+Y ZZ ’X ’+YYZ1X ’Z ’Figure 2III. Analyze the sequential-circuit as shown in Figure 3, D Flip-Flop with asynchronouspreset and clear inputs. [15’]1.Write out the excitation equations, transition equations and output equation. [5’]2.Assume the initial state Q 2Q 1=00, complete the timing diagram for Q 2 ,Q 1 and Z. [10’]Figure 3参考答案:激励方程: D 1=Q 2/,D 2= Q 1转移方程:Q 1 *= D 1=Q 2/,Q 2 *=D 2= Q 1 输出方程:Z= (CLK+Q 2)/参考评分标准:1. 5个方程正确得5分;每错一个扣1分,扣完5分为止;2. Q 1、Q 2、Z 的波形边沿判断正确,得3分,错一个,扣1分,扣完3分为止;每个上升沿和下降沿各0.5分,错1处扣0.5分,扣完7分为止。

数字逻辑第3章习题参考解答

3.68

分析图 3-37 所示反相器的下降时间,设 RL=900Ω ,VL=2V。

解:该电路图可以等效为下列带开关的一阶电路图。当输出从高态转 为低态时,可以等效为开关 K 从位置 1 转到位置 2。

按照一阶电路三要素法的分析方法,对于电容上的电压分析如下: 初态:VH=4.45V 终态:VL=0.2V

VOUT VL VH VL (1 e t / )

由上式可以得出从 1.5V 到 3.5V 的上升时间为:

t ln VH 1.5 19ns VH 3.5

可以驱动。

I=(3.84-2.03)/0.487 = 3.72 < 4mA

可以驱动。

3.40 一个发光二极管导通时的电压降约为 2.0V,正常发光时需要约 5mA 的电流。当发光二极管如图 3-54(a)那样连接时,确定上拉电 阻的适当值。 解:根据 3.7.5 所给的条件,低态输出电平 VOLmax=0.37V。 对应等效 电路如下:

13 画出 NOR3 对应的电路图。 解:3 输入端或非门结构应为:上部 3 个 P 管串联,下部 3 个 N 管并 联,结构如图所示。

3.15 画出 OR2 所对应的电路图。 解:在 NOR2 电路的输出端后面级联一个 INV。

3.59 解:

画出图 X3.59 逻辑图所对应的电路图。

3.21 若输出低电平阈值和高电平阈值分别设置为 1.5V 和 3.5V,对 图 X3.21 所示的反相器特性,确定高态与低态的 DC 噪声容限。 解:由图中可以看到,输出 3.5V 对应的输入为 2.4V,输出 1.5V 对应 的输入为 2.5V; 所以,高态噪声容限为:3.5-2.5=1 V ;低态噪声 容限为:2.4-1.5=0.9 V。

数字电路与逻辑设计习题及参考答案全套

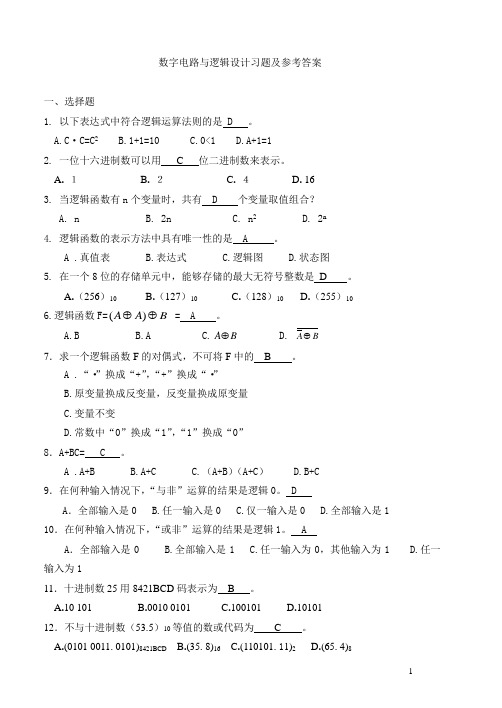

数字电路与逻辑设计习题及参考答案一、选择题1. 以下表达式中符合逻辑运算法则的是 D 。

A.C ·C=C 2B.1+1=10C.0<1D.A+1=12. 一位十六进制数可以用 C 位二进制数来表示。

A . 1B . 2C . 4D . 163. 当逻辑函数有n 个变量时,共有 D 个变量取值组合?A. nB. 2nC. n 2D. 2n4. 逻辑函数的表示方法中具有唯一性的是 A 。

A .真值表 B.表达式 C.逻辑图 D.状态图5. 在一个8位的存储单元中,能够存储的最大无符号整数是 D 。

A .(256)10B .(127)10C .(128)10D .(255)106.逻辑函数F=B A A ⊕⊕)( = A 。

A.BB.AC.B A ⊕D. B A ⊕7.求一个逻辑函数F 的对偶式,不可将F 中的 B 。

A .“·”换成“+”,“+”换成“·”B.原变量换成反变量,反变量换成原变量C.变量不变D.常数中“0”换成“1”,“1”换成“0”8.A+BC= C 。

A .A+B B.A+C C.(A+B )(A+C ) D.B+C9.在何种输入情况下,“与非”运算的结果是逻辑0。

DA .全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是110.在何种输入情况下,“或非”运算的结果是逻辑1。

AA .全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为111.十进制数25用8421BCD 码表示为 B 。

A .10 101B .0010 0101C .100101D .1010112.不与十进制数(53.5)10等值的数或代码为 C 。

A .(0101 0011.0101)8421BCDB .(35.8)16C .(110101.11)2D .(65.4)813.以下参数不是矩形脉冲信号的参数 D 。

A.周期B.占空比C.脉宽D.扫描期14.与八进制数(47.3)8等值的数为: BA. (100111.0101)2B.(27.6)16C.(27.3 )16D. (100111.101)215. 常用的BCD码有 D 。

数字逻辑第3章答案

F, A B[(C D)E G]

5 (1) 如果已知 X + Y 和 X + Z 的逻辑值相同,那么 Y 和 Z 的逻

辑值一定相同。正确吗?为什么? (2) 如果已知 XY 和 XZ 的逻辑值相同,那么那么 Y 和 Z 的逻辑值

一定相同。正确吗?为什么? (3)如果已知 X + Y 和 X + Z 的逻辑值相同,且 XY 和 XZ 的逻辑

(1) F(A, B,C, D) BD AD CD CD ACD ABD

(2) F(A, B,C, D) (AB AB) C (AB AB) C

解答

G(A, B,C, D) AB BC AC (A B C) ABC

(1) 当 b a 时,令 a=1,b=0 能得到最简“与-或”表达式: F BC CD ACD (3 项)

(2) 当 a=1,b=1 时,能得到最简的“与-或”表达式:

F BC CD AC (3 项)

11 用列表法化简逻辑函数

F(A, B,C, D) m(0,2,3,5,7,8,10,11,13,15)

10

0

0

01 0 0 1 1

1

1

10 0 0 1 1

1

1

11 0 1 0 1

0

0

4 求下列函数的反函数和对偶函数: (1) F AB AB

(2) F A B A C C DE E

(3) F (A B)(C DAC)

(4) F A B CD E G

值相同,那么 Y = Z。正确吗?为什么? (4) 如果已知 X+Y 和 X·Y 的逻辑值相同,那么 X 和 Y 的逻辑值

《数字逻辑设计及应用》试题2答案

n 1

2

1

0

0

0

0

0

0

1

0

0

1

0

1

0

Q2Q1Q0

0

1

0

1

0

0

0

1

1

1

1

0

101

011

1

0

0

0

0

0

1

0

1

0

1

0ቤተ መጻሕፍቲ ባይዱ

000

001

010

100

110

1

1

0

1

0

0

1

1

1

1

1

0

111

可见,该电路是一个可自启动的四进制计数器。 (2 分)

命题人签名:

年月日

CLK

O

J

t

O

K

t

O

Q

t

O

Q

t

O

t

六、(14 分) 解:实现方法一:

实现方法二:

七、(14 分) 解:(1)列驱动方程

(4 分)

J 0 Q0Q1Q2 ,K 0 Q0Q1Q2 J1 Q0 ,K1 Q0 J 2 Q1 ,K 2 Q1 (2)求状态方程 (3 分)

Q n1 0

电子科技大学中山学院试题标准答案及评分标准

课程名称 命题人

基 本 要 求

(2009-2010 学年第一学期)

数字逻辑设计及应用 考试班级

石建国

送题时间

试题套数 考试形式

A 闭卷

对填空题、选择题、判断题等客观类题目的答案须做到答题标准唯

一,简述题、论述题、分析题等主观类题目的答案,须提供"答题要点

数字逻辑设计基础答案_(第1-13章)

第 3 章 逻辑代数基础

[题 3-1] 分别指出变量(A,B,C,D)在何种取值组合时,下列函数的值为 1。 (1) Y AB C CD (2) Y ( A B D)( A C D ) 解: (1) 要使函数的值为 1, 当且仅当 ABC 取 101,D 可取 0 或 1; 当且仅当 CD 取 11,AB 可取 00、01、10、11。即 ABCD 对应取值组合有 1010、1011、0011、0111、1111 时,函数 的值为 1。 (2)对于或与式,可先求函数的值为 0 的组合。当且仅当 ABD 取 100, C 可取 0 或 1; 当且仅当 ACD 取 001, B 可取 0 或 1。即 ABCD 对应取值组合有 1000、1010、0001、0101 时,函数的值为 0。则函数的值为 1 的 ABCD 对应取值组合有 0000、0010、0011、0100、 0110、0111、1001、1011、1100、1101、1110、1111。 [题 3-2] 试用真值表验证下列表达式: (1) AB B C A B B C (2) AB A B ( A B)( A B ) (3) ( A B)C AC BC (4) A B A B 1 解: (1)将等式左边和右边对应列出真值表,如表题 3.2(1)所示。则 AB B C A B B C 的恒等关系得以证明。

现代数字系统设计主要依托于计算机辅助的设计设计者先在装有eda软件的计算机上用图形输或文本输入方式把要设计的数字系统的模型搭建好然后利用相关的eda软件将用图形或文本表达的设计思想自动转化为目标芯片pld所能识别的网表文件最终通过相应的下载工具下载到目标芯片里让目标芯片按照即定的逻辑执行相应的功能

《数字逻辑设计基础》习题解答

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

.

.

电子科技大学网络教育考卷(C 卷)

(20 年至20 学年度第 学期)

考试时间 年 月 日(120分钟) 课程 数字逻辑设计及应用(本科) 教师签名_____

大题号 一 二 三 四 五 六 七 八 九 十 合 计 得 分

一、填空题(每空1分,共20分)

1、10111012= 135 8= 5D 16= 1110011 格雷码

2、FF 16= 255 10= 001001010101 8421BCD = 010********* 余3码

3、已知某数的反码是1010101,则该数的对应的原码是 1101010 ,补码是 1101011 ;

4、逻辑运算的三种基本运算是 与或非 ;

5、一个逻辑在正逻辑系统下,表达式为B A +,则该逻辑在负逻辑系统下,表达式为 AB ;

6、逻辑式A /(B+CD /)的反演式为 A+B /(C /+D) ;

7、已知∑=

)3,1,0(),,(m C B A F ,则∑=m F

/

( 2,4,5,6,7 )

M ∏=( 2,4,5,6,7 )

; 8、请问图1-8逻辑为Y= (AB)/ ;

9、n 选1的数据选择器的地址输入的位数为 log 2n(向上取整) 位,多路输入端得个数为 n 个;

10、如果用一个JK 触发器实现D 触发器的功能,已知D 触发器的输入

信号为D ,则该JK 触发器的驱动为: J=D;K=D / ;

11、如果用一个D 触发器实现T 触发器的功能,已知T 触发器的输入信号为T ,则该D 触发器的驱动为: T ⊕Q ;

12、如果让一个JK 触发器只实现翻转功能,则该触发器的驱动为: J=K=1 ;

13、利用移位寄存器实现顺序序列信号1001110的产生,则该移位寄存器中触发器的个数为: 大于或等于3 个;

二、选择题(每题1分,共10分)

1、以下有关原码、反码和补码的描述正确的是: ①.二进制补码就是原码除符号位外取反加1; ②.补码即是就是反码的基础上再加1; ③.负数的原码、反码和补码相同; ④.正数的原码、反码和补码相同;

2、下列逻辑表达式中,与D BC C A AB F /

/

/

1++=不等的逻辑是: ①./

/

/

BC C A AB ++

②./

///D BC C A AB ++ ③./

/C A AB + ④.BD C A AB ++/

/

3、已知门电路的电平参数如下:,,,,V 3.0V V 0.3V V 25.0V V 2.3V L I IH OL OH ≤≥≤≥请问其低电平的噪声容限为:

①. 0.05V ②. 0.2V ③. 2.95V ④. 2.7V

4、下列逻辑中,与/

A Y =相同的逻辑是:

①.1A Y ⊕= ②.0A Y ⊕= ③.A A Y ⊕= ④./

)A A (Y ⊕=

5、有如下所示波形图,已知ABC 为输入变量,Y 为输出变量,我们可以得到该逻辑的函数式为:

①.AC AB Y += ②.C B A Y ++=

③.C B A Y ⋅⋅= ④./

/

/

C B A Y ++=

6、在同步状态下,下面哪种时序逻辑器件的状态更新仅仅发生在时钟触发沿来临的瞬间,并且状态更新的依据也仅仅取决于当时的输入情况:

①.锁存器

②.电平触发的触发器

③.脉冲触发的触发器 ④.边沿触发的触发器器

7、或非门所构成的SR 触发器的输入为S 和R ,则其工作时的约束条件为:

①.1R S =+ ②.0R S =⋅

③.0R S /

/

=+ ④.R S =

8、要实现有效状态数为8的扭环计数器,则所需移位寄存器中的触发器个数为:

①.8 ②.4 ③.3 ④.2

9、下面的电路,属于组合逻辑的电路是:

①.串行数据检测器 ②.多路数据选择器 ③.顺序信号发生器 ④.脉冲序列发生器

10、下面哪些器件不能够实现串行序列发生器 ①.计数器和组合门电路 ②.数据选择器和组合门电路 ③.移位寄存器和组合门电路 ④.触发器和组合门电路

姓名__________________ 专业名称__________________ 班号________________学号__________________教学中心_________________

…………………… …… … … … … …密………………… …… … … … … ……封……………… …… … … …线… … … …… … … ……………………

图1-8 图2-5

.

三、判断题(每题1分,共10分) 1、如果逻辑AB=AC ,则B=C ;( Х) 2、如果逻辑A+B=A+C ,则B=C ;(Х ) 3、如果逻辑AB+AC=1,则A=1;( √ ) 4、如果逻辑AB+AC=0,则A=0;(Х )

5、若干个逻辑信号进行异或操作,如果这些信号中逻辑“1”的个数为奇数,则输出结果为1;( √ )

6、A ⊕1=A /;( √ )

7、A+A+A=A ·A ·A ;( √ )

8、对于CMOS 集成门电路而言,与门的结构比与非门的结构更为简单一些;(Х ) 9、TTL 逻辑比CMOS 逻辑的运行功耗更低,所以更利于集成;(Х ) 10、影响CMOS 集成门电路的运行速度主要是传输延迟和转换时间;( √ )

四、卡诺图化简(8分)

将逻辑F (A,B,C,D )=∑m(0,1,3,4,6,7,14,15)+d(8,9,10,11,12,13)化成最简或与函数式;

F=C /D /

+B /

D+BC

答案不唯一

五、组合逻辑分析,要求如下(8分)

完成图5所示电路的逻辑分析,并写出: 1、 逻辑Y 的函数式 2、 写出该逻辑的真值表 1、 函数式

2、 真值表

六、时序逻辑分析,要求如下:(14分)

请分析图6所示电路的逻辑,并写出: 1、 驱动方程和输出方程; 2、 状态方程;

3、 画出状态转换图或者状态转换表;

驱动方程:21'⋅=Q X EN ,

12Q J =,12=K

状态方程:121121111*1Q Q Q X Q Q X Q EN Q EN Q ⋅+⋅'+'⋅'⋅=⋅'+'⋅=

122222*2Q Q Q K Q J Q ⋅'=⋅'+'⋅=

输出方程:21'⋅+⋅'=Q X Q X Z 状态表:

或者状态图:

图5

图6

C

B A

C B A C B A C B A F ///

///••+••+••+••=

.

七、组合逻辑设计,要求如下:(8分)

请利用一块8选1的数据选择器芯片74153来实现如下逻辑:BC AC AB Y ++=;可加一定的门电路来实现。

先对数据选择器进行扩展, 然后在赋值

八、时序逻辑设计,要求如下:(10分)

请利用移位寄存器74194和一定的门电路结构,设计一个3位的扭环计数器,要求该电路能够自行启动 1、画出能够自行启动的3位扭环计数器状态图

2、请在74194芯片上完成该逻辑,已知74194芯片的逻辑功能定义如下:

能够自行启动的3

位扭环计数器,其状态图和反馈函数定义如下: 求反馈函数:

F=Q2/

+Q1/

Q0

选择右移方式,完成电路图如下:

九、时序逻辑设计,要求如下:(12分)

已知一个时序逻辑的状态转换图如图9所示。

请完成该逻辑电路的设计,无须考虑自启动问题。

选择D 触发器来实现。

要求写出:

1、 状态方程

2、 驱动方程和输出方程;

3、 画出逻辑图

(已知三个状态的编码分别为S0:Q1Q0=00;S1:Q1Q0=01;S2:Q1Q0=10; 状态表如下:

状态方程:

Q X 0Q 1XQ 0Q 1Q X 0XQ 1Q /

/

/

*

/*+=+=

驱动方程和输出方程:

1

XQ Y 0Q X 0Q 1XQ 0Q 0D 1Q X 0XQ 1Q 1D ///*/*=+==+== 电路图略;

图9

1/1。