锁相环CD4046 原理及应用

cd4046中文资料

CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

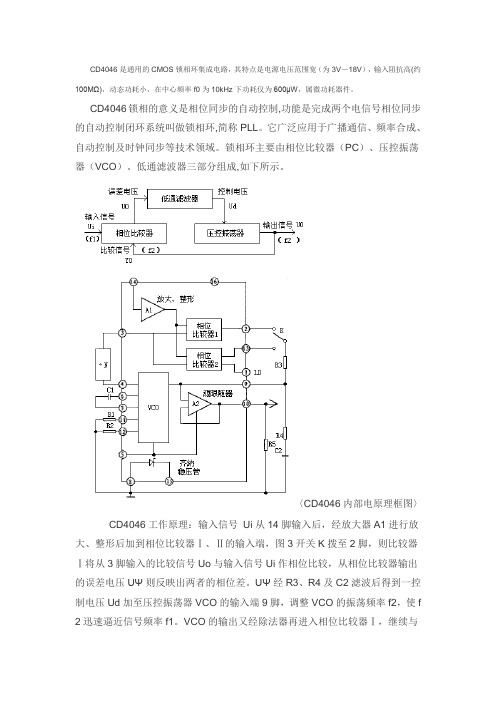

CD4046锁相的意义是相位同步的自动控制,功能是完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)。

低通滤波器三部分组成,如下所示。

〈CD4046内部电原理框图〉CD4046工作原理:输入信号Ui从14脚输入后,经放大器A1进行放大、整形后加到相位比较器Ⅰ、Ⅱ的输入端,图3开关K拨至2脚,则比较器Ⅰ将从3脚输入的比较信号Uo与输入信号Ui作相位比较,从相位比较器输出的误差电压UΨ则反映出两者的相位差。

UΨ经R3、R4及C2滤波后得到一控制电压Ud加至压控振荡器VCO的输入端9脚,调整VCO的振荡频率f2,使f 2迅速逼近信号频率f1。

VCO的输出又经除法器再进入相位比较器Ⅰ,继续与Ui进行相位比较,最后使得f2=f1,两者的相位差为一定值,实现了相位锁定。

若开关K拨至13脚,则相位比较器Ⅱ工作,过程与上述相同,不再赘述。

下图是CD4046的引脚排列,采用16脚双列直插式,各管脚功能:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

〈CD4046引脚图〉CD4046典型应用电路。

图6是用CD4046的VCO组成的方波发生器,当其9脚输入端固定接电源时,电路即起基本方波振荡器的作用。

CD4046锁相环在感应加热电源中的应用

CD4046 锁相环在感应加热电源中的应用

应用于钎焊、熔炼等热加工工艺的感应加热电源在运行过程中,随着负载温度升高和炉料的熔化,负载等效参数会产生时变,从而引起负载固有谐振频率的变化。

为了使逆变器始终工作在功率因数接近或等于 1 的准谐振或谐振状态,控制电路必须能够实现频率自动跟踪。

本文采用LEM 电流传感器、电压比较器和CD4046 锁相环对负载电流

进行频率跟踪,实现了功率器件的零电流开关(ZCS),减小了开关损耗和电磁干扰(EMI)。

由于在电路刚起动时,电流反馈信号为零,CD4046 不能入锁。

本文提出了一种利用CD4046 自身特点实现的它激到自

激的转换电路,很好地解决了这一问题。

另外,加上相位补偿电路的引入,最终实现了频率自动跟踪控制。

整个电路具有跟踪速度快、跟踪频率准确、保护容易、抗干扰能力强等优点。

CD4046 锁相环在感应加热电源中的应用----锁相环功能原理

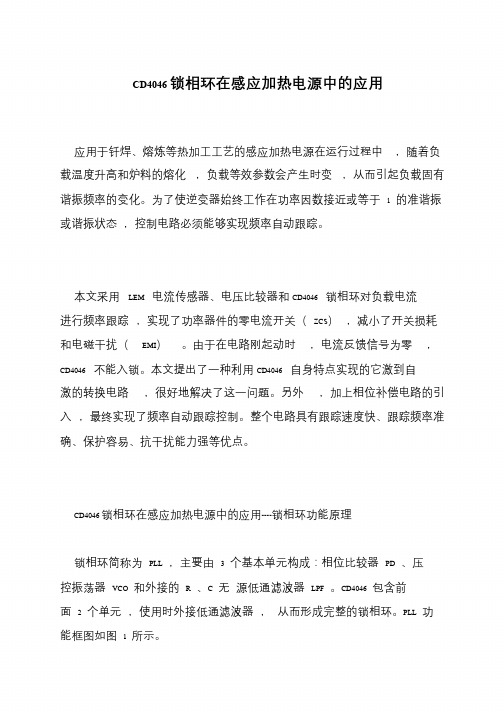

锁相环简称为PLL ,主要由3 个基本单元构成:相位比较器PD 、压

控振荡器VCO 和外接的R 、C 无源低通滤波器LPF 。

CD4046 包含前

面 2 个单元,使用时外接低通滤波器,从而形成完整的锁相环。

PLL 功能框图如图1 所示。

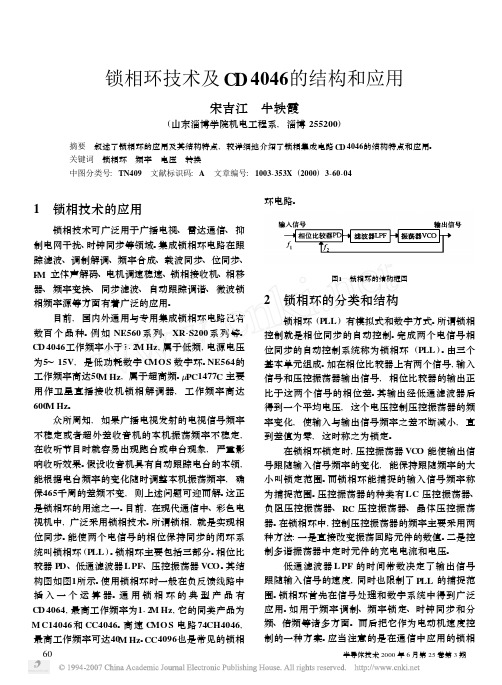

锁相环技术及CD4046的结构和应用

锁相环技术及CD4046的结构和应用宋吉江 牛轶霞(山东淄博学院机电工程系,淄博255200) 摘要 叙述了锁相环的应用及其结构特点,较详细地介绍了锁相集成电路C D4046的结构特点和应用。

关键词 锁相环 频率 电压 转换中图分类号:TN409 文献标识码:A 文章编号:1003-353X(2000)3-60-041 锁相技术的应用锁相技术可广泛用于广播电视、雷达通信、抑制电网干扰、时钟同步等领域。

集成锁相环电路在跟踪滤波、调制解调、频率合成、载波同步、位同步、F M立体声解码、电机调速稳速、锁相接收机、相移器、频率变换、同步滤波、自动跟踪调谐、微波锁相频率源等方面有着广泛的应用。

目前,国内外通用与专用集成锁相环电路已有数百个品种。

例如NE560系列、XR-S200系列等。

CD4046工作频率小于112M Hz,属于低频,电源电压为5~15V,是低功耗数字C MOS数字环。

NE564的工作频率高达50M Hz,属于超高频。

ΛPC1477C主要用作卫星直播接收机锁相解调器,工作频率高达600M Hz。

众所周知,如果广播电视发射的电视信号频率不稳定或者超外差收音机的本机振荡频率不稳定,在收听节目时就容易出现跑台或串台现象,严重影响收听效果。

假设收音机具有自动跟踪电台的本领,能根据电台频率的变化随时调整本机振荡频率,确保465千周的差频不变,则上述问题可迎而解。

这正是锁相环的用途之一。

目前,在现代通信中、彩色电视机中,广泛采用锁相技术。

所谓锁相,就是实现相位同步。

能使两个电信号的相位保持同步的闭环系统叫锁相环(PLL)。

锁相环主要包括三部分。

相位比较器PD、低通滤波器L PF、压控振荡器VCO。

其结构图如图1所示。

使用锁相环时一般在负反馈线路中插入一个运算器。

通用锁相环的典型产品有CD4064,最高工作频率为112M Hz,它的同类产品为M C14046和CC4046。

高速C MOS电路74CH4046,最高工作频率可达40M Hz。

MC4046应用

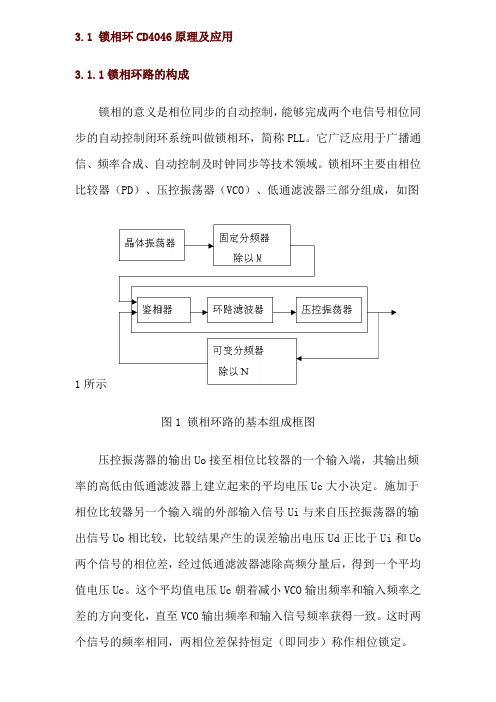

3.1 锁相环CD4046原理及应用3.1.1锁相环路的构成锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

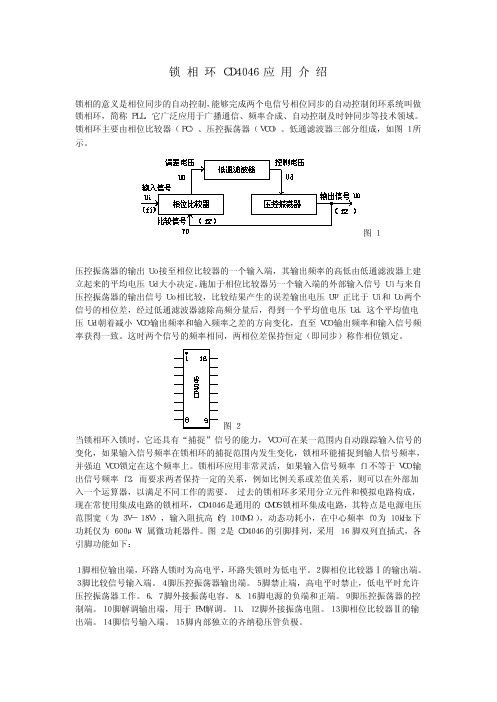

锁相环主要由相位比较器(PD)、压控振荡器(VCO)、低通滤波器三部分组成,如图1所示图1 锁相环路的基本组成框图压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Uc大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压Ud正比于Ui和Uo 两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Uc。

这个平均值电压Uc朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO 输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

3.1.2CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如下:图1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

cd4046中文资料

锁 相 环 CD4046 应 用 介 绍 锁相的意义是相位同步的自动控制, 能够完成两个电信号相位同步的自动控制闭环系统叫做 锁相环,简称 PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)。

低通滤波器三部分组成,如图 1 所 示。

图 1 压控振荡器的输出 Uo 接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建 立起来的平均电压 Ud 大小决定。

施加于相位比较器另一个输入端的外部输入信号 Ui 与来自 压控振荡器的输出信号 Uo 相比较,比较结果产生的误差输出电压 UΨ 正比于 Ui 和 Uo 两个 信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压 Ud。

这个平均值电 压 Ud 朝着减小 VCO 输出频率和输入频率之差的方向变化,直至 VCO 输出频率和输入信号频 率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

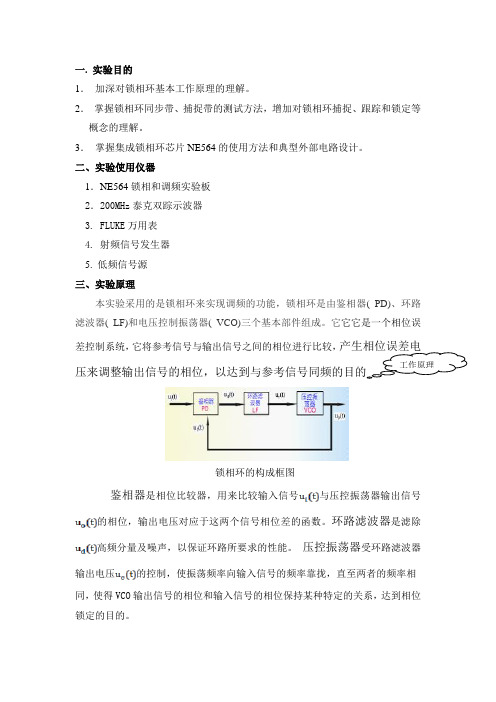

图 2 当锁相环入锁时,它还具有“捕捉”信号的能力,VCO 可在某一范围内自动跟踪输入信号的 变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率, 并强迫 VCO 锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率 f1 不等于 VCO 输 出信号频率 f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加 入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成, 现在常使用集成电路的锁相环,CD4046 是通用的 CMOS 锁相环集成电路,其特点是电源电压 范围宽(为 3V-18V),输入阻抗高(约 100MΩ),动态功耗小,在中心频率 f0 为 10kHz 下 功耗仅为 600μW,属微功耗器件。

图 2 是 CD4046 的引脚排列,采用 16 脚双列直插式,各 引脚功能如下: 1 脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

锁相环的CD4046应用

一. 实验目的1.加深对锁相环基本工作原理的理解。

2.掌握锁相环同步带、捕捉带的测试方法,增加对锁相环捕捉、跟踪和锁定等概念的理解。

3.掌握集成锁相环芯片NE564的使用方法和典型外部电路设计。

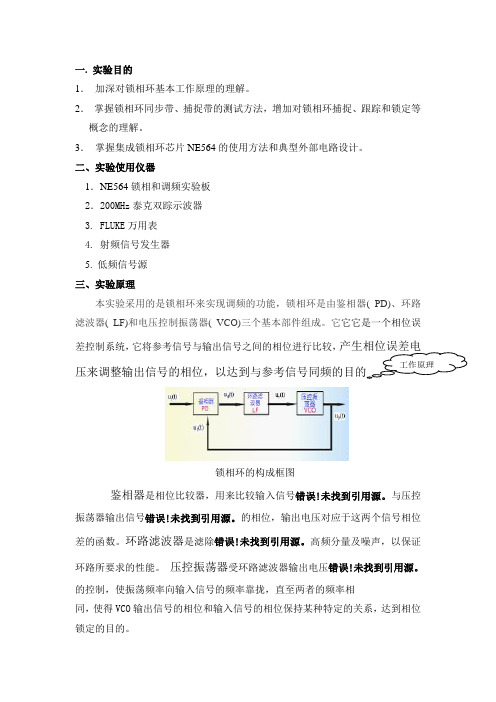

二、实验使用仪器1.NE564锁相和调频实验板2.200MHz泰克双踪示波器3. FLUKE万用表4. 射频信号发生器5. 低频信号源三、实验原理本实验采用的是锁相环来实现调频的功能,锁相环是由鉴相器( PD)、环路滤波器( LF)和电压控制振荡器( VCO)三个基本部件组成。

它它它是一个相位误差控制系统,它将参考信号与输出信号之间的相位进行比较,产生相位误差电工作原理压来调整输出信号的相位,以达到与参考信号同频的目的。

锁相环的构成框图鉴相器是相位比较器,用来比较输入信号与压控振荡器输出信号的相位,输出电压对应于这两个信号相位差的函数。

环路滤波器是滤除高频分量及噪声,以保证环路所要求的性能。

压控振荡器受环路滤波器输出电压的控制,使振荡频率向输入信号的频率靠拢,直至两者的频率相同,使得VCO输出信号的相位和输入信号的相位保持某种特定的关系,达到相位锁定的目的。

*判断环路是否锁定的方法在有双踪示波器的情况下,开始时环路处于失锁状态,加大输入信号频率,用双踪示波器观察压控振荡器的输出信号和环路的输入信号,当两个信号由不同步变成同步,且时,表示环路已经进入锁定状态。

锁相调频电路在普通的直接调频电路中,振荡器的中心频率稳定度较差,而采用晶体振荡器的调频电路,其调频范围又太窄。

采用锁相环的调频器可以解决这个矛盾。

锁相调频原理框图如下图所示锁相调频原理图 正如上面锁相调频原理图所示,实现锁相调频的条件是调制信号的频谱要处于低通滤波器通带之外。

使压控振荡器的中心频率锁定在稳定度很高的晶振频率上,而随着输入调制信号的变化,振荡频率可以发生很大偏移。

这种锁相环路称载波跟踪型PLL ,本实验中使用的锁相环是NE564。

NE564内部压控振荡器的最高工作频率是50MHz ,从图10-5的逻辑框图中可以看到,NE564的内部包含一个限幅放大器,对外部的输入信号进行限幅放大,抑制寄生调幅,内部还包含压控振荡器和相位比较器。

锁相环的CD4046应用

一. 实验目的1.加深对锁相环基本工作原理的理解。

2.掌握锁相环同步带、捕捉带的测试方法,增加对锁相环捕捉、跟踪和锁定等概念的理解。

3.掌握集成锁相环芯片NE564的使用方法和典型外部电路设计。

二、实验使用仪器1.NE564锁相和调频实验板2.200MHz泰克双踪示波器3. FLUKE万用表4. 射频信号发生器5. 低频信号源三、实验原理本实验采用的是锁相环来实现调频的功能,锁相环是由鉴相器( PD)、环路滤波器( LF)和电压控制振荡器( VCO)三个基本部件组成。

它它它是一个相位误差控制系统,它将参考信号与输出信号之间的相位进行比较,产生相位误差电工作原理压来调整输出信号的相位,以达到与参考信号同频的目的。

锁相环的构成框图鉴相器是相位比较器,用来比较输入信号错误!未找到引用源。

与压控振荡器输出信号错误!未找到引用源。

的相位,输出电压对应于这两个信号相位差的函数。

环路滤波器是滤除错误!未找到引用源。

高频分量及噪声,以保证环路所要求的性能。

压控振荡器受环路滤波器输出电压错误!未找到引用源。

的控制,使振荡频率向输入信号的频率靠拢,直至两者的频率相同,使得VCO输出信号的相位和输入信号的相位保持某种特定的关系,达到相位锁定的目的。

*判断环路是否锁定的方法在有双踪示波器的情况下,开始时环路处于失锁状态,加大输入信号频率,用双踪示波器观察压控振荡器的输出信号和环路的输入信号,当两个信号由不同步变成同步,且错误!未找到引用源。

时,表示环路已经进入锁定状态。

锁相调频电路在普通的直接调频电路中,振荡器的中心频率稳定度较差,而采用晶体振荡器的调频电路,其调频范围又太窄。

采用锁相环的调频器可以解决这个矛盾。

锁相调频原理框图如下图所示锁相调频原理图 正如上面锁相调频原理图所示,实现锁相调频的条件是调制信号的频谱要处于低通滤波器通带之外。

使压控振荡器的中心频率锁定在稳定度很高的晶振频率上,而随着输入调制信号的变化,振荡频率可以发生很大偏移。

cd4046

锁相环 CD4046 应用介绍朗清锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)。

低通滤波器三部分组成,如图1所示。

图1压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压U?正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

图2当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100M?),动态功耗小,在中心频率f0为10kHz下功耗仅为600?W,属微功耗器件。

图2是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如下:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

锁相环 CD4046 原理及应用

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成,如图1所示。

图1

压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud朝着减小CO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如下:

图2•1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

•2脚相位比较器Ⅰ的输出端。

•3脚比较信号输入端。

•4脚压控振荡器输出端。

•5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

•6、7脚外接振荡电容。

•8、16脚电源的负端和正端。

•9脚压控振荡器的控制端。

•10脚解调输出端,用于FM解调。

•11、12脚外接振荡电阻。

•13脚相位比较器Ⅱ的输出端。

•14脚信号输入端。

•15脚内部独立的齐纳稳压管负极。

图3是CD4046内部电原理框图,主要由相位比较Ⅰ、Ⅱ、压控振荡器(VCO)、线性放大器、源跟随器、整形电路等部分构成。

比较器Ⅰ采用异或门结构,当两个输人端信号Ui、Uo的电平状态相异时(即一个高电平,一个为低电平),输出端信号UΨ为高电平;反之,Ui、Uo电平状态相同时(即两个均为高,或均为低电平),UΨ输出为低电平。

当Ui、Uo的相位差Δφ在0°-180°范围内变化时,UΨ的脉冲宽度m亦随之改变,即占空比亦在改变。

从比较器Ⅰ的输入和输出信号的波形(如图4所示)可知,其输出信号的频率等于输入信号频率的两倍,并且与两个输入信号之间的中心频率保持90°相移。

从图中还可知,fout不一定是对称波形。

对相位比较器Ⅰ,它要求Ui、Uo的占空比均为50%(即方波),这样才能使锁定范围为最大。

图3

相位比较器Ⅱ是一个由信号的上升沿控制的数字存储网络。

它对输入信号占空比的要求不高,允许输入非对称波形,它具有很宽的捕捉频率范围,而且不会锁定在输入信号的谐波。

它提供数字误差信号和锁定信号(相位脉冲)两种输出,当达到锁定时,在相位比较器Ⅱ的两个输人信号之间保持0°相移。

对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”;反之则输出逻辑“1”。

如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器Ⅱ输出的为正脉冲,当相位超前时则输出为负脉冲。

在这两种情况下,从1脚都有

与上述正、负脉冲宽度相同的负脉冲产生。

从相位比较器Ⅱ输出的正、负脉冲的宽度均等于两个输入脉冲上升沿之间的相位差。

而当两个输入脉冲的频率和相位均相同时,相位比较器Ⅱ的输出为高阻态,则1脚输出高电平。

上述波形如图5所示。

由此可见,从1脚输出信号是负脉冲还是固定高电平就可以判断两个输入信号的情况了。

图5

CD4046锁相环采用的是RC型压控振荡器,必须外接电容C1和电阻R1作为充放电元件。

当PLL对跟踪的输入信号的频率宽度有要求时还需要外接电阻R2。

由于VCO是一个电流控制振荡器,对定时电容C1的充电电流与从9脚输入的控制电压成正比,使VCO的振荡频率亦正比于该控制电压。

当VCO控制电压为0时,其输出频率最低;当输入控制电压等于电源电压VDD时,输出频率则线性地增大到最高输出频率。

VCO振荡频率的范围由R1、R2和C1决定。

由于它的充电和放电都由同一个电容C1完成,故它的输出波形是对称方波。

一般规定CD4046的最高频率为1。

2MHz(VDD=15V),若VDD<15V,则fmax要降低一些。

CD4046内部还有线性放大器和整形电路,可将14脚输入的100mV左右的微弱输入信号变成方波或脉冲信号送至两相位比较器。

源跟踪器是增益为1的放大器,VCO的输出电压经源跟踪器至10脚作FM解调用。

齐纳二极管可单独使用,其稳压值为5V,若与TTL电路匹配时,可用作辅助电源。

综上所述,CD4046工作原理如下:输入信号 Ui从14脚输入后,经放大器A1进行放大、整形后加到相位比较器Ⅰ、Ⅱ的输入端,图3开关K拨至2脚,则比较器Ⅰ将从3脚输入的比较信号Uo与输入信号Ui作相位比较,从相位比较器输出的误差电压UΨ则反映出两者的相位差。

UΨ经R3、R4及C2滤波后得到一控制电压Ud加至压控振荡器VCO的输入端9脚,调整VCO的振荡频率f2,使f2迅速逼近信号频率f1。

VCO的输出又经除法器再进入相位比较器Ⅰ,继续与Ui进行相位比较,最后使得f2=f1,两者的相位差为一定值,实现了相位锁定。

若开关K拨至13脚,则相位比较器Ⅱ工作,过程与上述相同,不再赘述。

下面介绍CD4046典型应用电路。

图6是用CD4046的VCO组成的方波发生器,当其9脚输入端固定接电源时,电路即起基本方波振荡器的作用。

振荡器的充、放电电容C1接在6脚与7脚之间,调节电阻R1阻值即可调整振荡器振荡频率,振荡方波信号从4脚输出。

按图示数值,振荡频率变化范围在20Hz至2kHz。

图6

图7是CD4046锁相环用于调频信号的解调电路。

如果由载频为10kHz组成的调频信号,用400Hz音频信号调制,假如调频信号的总振幅小于400mV时,用CD4046时则应经放大器放大后用交流耦合到锁相环的14脚输入端环路的相位比较器采用比较器Ⅰ,因为需要锁相环系统中的中心频率f0等于调频信号的载频,这样会引起压控振荡器输出与输入信号输入间产生不同的相位差,从而在压控振荡器输入端产生与输入信号频率变化相应的电压变化,这个电压变化经源跟随器隔离后在压控振荡器的解调输出端10脚输出解调信号。

当VDD为10V,R1为10kΩ,C1为100pF时,锁相环路的捕捉范围为±0.4kHz。

解调器输出幅度取决于源跟随器外接电阻R3值的大小。

图7

图8用CD4046与BCD加法计数器CD4518构成的100倍频电路。

刚开机时,f2可能不等于f1,假定f2<f1,此时相位比较器Ⅱ输UΨ为高电平,经滤波后Ud逐渐升高使VCO输出频率f2迅速上升,f2增大值至 f2=f1,如果此时 Ui滞后 U0,则相位比较器Ⅱ输出UΨ为低电平。

UΨ经滤波后得到的Ud信号开始下降,这就迫使VCO对f2进行微调,最后达到f2/N=f1,并且f2与f1的相位差Δφ=0°。

,进入锁定状态。

如果此后f1又发生变化,锁相环能再次捕获f1,使f2与f1相位锁定。

图8。