IC版图设计1讲解学习

IC版图设计课程

目录第1章绪论 (1)1.1版图设计基础知识 (1)1.1.1 版图设计方法 (1)1.1.2 版图设计规则 (1)1.2标准单元版图设计 (2)第2章:D触发器介绍 (6)2.1 D触发器简介 (6)2.2维持阻塞式边沿D触发器 (6)2.3真单相时钟(TSPC)动态D触发器 (7)第3章 0.35um工艺基于TSPC原理的D触发器设计 (9)3.1电路原理图设计 (9)3.2 创建 D触发器版图 (10)3.3设计规则的验证及结果 (11)第4章课程设计总结 (13)参考文献 (14)第1章绪论1.1版图设计基础知识集成电路从60年代开始,经历了小规模集成,中规模集成,大规模集成,到目前的超大规模集成。

单个芯片上已经可以制作含几百万个晶体管的一个完整的数字系统或数模混合的电子系统。

在整个设计过程中,版图(layout)设计或者称作物理设计(physical design)是其中重要的一环。

他是把每个原件的电路表示转换成集合表示,同时,元件间连接的线网也被转换成几何连线图形。

对于复杂的版图设计,一般把版图设计分成若干个子步骤进行:划分为了将处理问题的规模缩小,通常把整个电路划分成若干个模块。

版图规划和布局是为了每个模块和整个芯片选择一个好的布图方案。

布线完成模块间的互连,并进一步优化布线结果。

压缩是布线完成后的优化处理过程,他试图进一步减小芯片的面积。

1.1.1 版图设计方法可以从不同角度对版图设计方法进行分类。

如果按设计自动化程度来分,可将版图设计方法分成手工设计和自动设计2大类。

如果按照对布局布线位置的限制和布局模块的限制来分,则可把设计方法分成全定制(fullcustom)和半定制(semicustom)2大类。

而对于全定制设计模式,目前有3种CAD工具服务于他:几何图形的交互图形编辑、符号法和积木块自动布图。

对于两极运算放大器版图设计的例子,采用的是Tanner公司的LEdit软件。

这是一种广泛使用在微机上的交互图形编辑器。

《IC单元版图设计》课件

IC单元版图设计的未来展望

发展趋势展望

IC单元版图设计将更加注重功耗 和性能的平衡,实现更高效、可 靠的集成电路。

未来方向

未来的IC单元版图设计将更加注 重深度学习和人工智能技术的应 用,推动集成电路的创新。

研究热点

当前的研究热点包括低功耗设计、 器件集成和整合等,为IC单元版 图设计带来更多机遇和挑战。

《IC单元版图设计》PPT 课件

IC单元版图设计是集成电路设计中的重要环节,本课程将介绍IC单元版图设计 的基本概念、流程、工具、注意事项以及未来展望。

什么是IC单元版图设计?

IC单元版图设计是集成电路设计中的一项关键技术,旨在实现IC单元的物理布 局和连接,确保电路的正常工作。

IC单元版图设计的应用广泛,涵盖了从处理器到传感器等多个领域,对于电 子设备的性能和稳定性起着至关重要的作用。

IC单元版图设计流程

1

流程概述

IC单元版图设计包括物理设计准备、版图规划、电路布局、连线布局、设计规则 验证等阶段。

2

数字IC单元版图设计

数字IC单元版图设计流程包括逻辑综合、时序优化、布局布线、电器规则检查等 步骤。Байду номын сангаас

3

模拟IC单元版图设计

模拟IC单元版图设计流程包括电路拓扑设计、布局优化、电压栅极等步骤。

本次IC单元版图设计PPT课件的大纲

本次课程涵盖了IC单元版图设计的基本概念、流程、工具、注意事项以及未来展望。 希望通过本课程的学习,能够加深对IC单元版图设计的理解,并为未来的集成电路设计提供参考和启示。 谢谢观看!

Mentor Graphics Calibre 基础操作教程

提供了Mentor Graphics Calibre的基础操作教程,包 括设计规则的设置和验证等。

第1章 IC设计的基本知识

第一章IC设计的基本知识集成电路设计方法大致可分为定制(Custom)、半定制(Semi-custom)、可编程逻辑器件(PLD)等设计方法,如图1.1所示。

定制设计方法又可分为全定制(Full-Custom)设计和基于包(Cell-Based)的设计方法二类。

本课程讲授集成电路定制设计方法。

半定制和可编程逻辑器件安排在其它课程中。

图1.1 ASIC设计方法分类1.1 集成电路设计流程全定制(Full-Custom)设计和基于包(Cell-Based)的设计方法使用不同的设计流程,所使用的设计工具也会有所不同。

1.1.1全定制设计流程全定制(full custom)集成电路设计方法,是按规定的功能与性能要求,对电路的结构布局与布线进行最优化设计,实现最小面积,最佳布线布局、最优功耗速度积,以求获得尽可能最优的设计。

全定制(full custom)集成电路设计方法通常用于高性能的设计场合:规模较小性能要求较高的中小规模专用集成电路;大批量高性能集成电路,例如CPU与内存;需要最佳优化设计的标准单元库等等。

图1.2是全定制设计流程,大致的步骤如下:1)电路图绘制:根据芯片的功能要求与性能指标,选择合适的集成电路工艺库,使用电路图编辑工具绘制电路图。

2)前仿真:利用HSPICE对电路图进行仿真(版图前仿真),并进行性能优化。

3)绘制版图:根据Foundry(代工厂)提供的版图设计规则,利用版图编辑工具绘制芯片版图。

4)版图验证:包括几个主要步骤:设计规则检查DRC(Design Rule Check),版图与电路对照验证LVS(Layout Versus Schematic), 版图寄生参数抽取LPE(Layout Parasite Extract)等。

为了保证设计的版图能被正确制造出来,流片厂家会根据工艺定义很多设计规则,DRC 就是对版图进行全面的设计规则检查。

LVS的任务是证明版图实现的功能与电路网表描述的完全一致。

IC版图设计1PPT课件

含义 N阱层 N+或P+有源区层 多晶硅层 接触孔层 金属层 焊盘钝化层

标示图

第10页/共78页

➢ NWELL层相关的设计规则

编号

描述

尺寸(um)

目的与作用

1.1

N阱最小宽度

10.0

保证光刻精度和器件尺寸

1.2

N阱最小间距

10.0

防止不同电位阱间干扰

1.3

N阱内N阱覆盖P+ 2.0

保证N阱四周的场注N区环的 尺寸

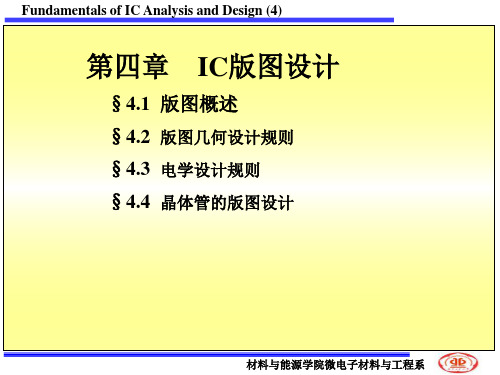

4.1 版图概述

➢ 版图定义

版图(Layout)是集成电路设计者将设计并模拟、优化后 的电路转化成的一系列几何图形,它包含了集成电路尺寸 大小、各层拓扑定义等器件相关的物理信息。

➢ 版图的作用

集成电路制造厂家根据 版 图 提 供 的 信 息 来 制 造 掩 膜 (Mask)。所以,版图是从设计走向制造的桥梁。

5.2 金属间距 2.0

目的与作用 保证铝线的良好

电导

防止铝条联条

➢ Metal设计规则示意图

第18页/共78页

➢ Pad相关的设计规则列表

编号

描述

尺寸

目的与作用

6.1

最小焊盘大小

90

封装、邦定需要

6.2

最小焊盘边间距

80

防止信号之间串绕

6.3

最小金属覆盖焊盘

6.0

6.4

焊盘外到有源区最 小距离

25.0

➢ 布线规则 1. 电源线和地线应尽可能地避免用扩散区和多晶硅走线,特别是通过较大电

流的那部分电源线和地线。 多采用梳状走线,避免交叉;或者用多层金属工艺,提高设计布线的灵活 性。

第34页/共78页

IC模拟版图设计ppt课件

MIM电容版图

MOS电容版图

19

第二部分:版图设计基础

2.2互连

2.2.1金属(第一层金属,第二层金属……)

1) 金属连线

✓

M1,M2,M3,M4……

2.2.2 通孔

2)过孔

✓

Via1,Via2,Via3……

20

第二部分:版图设计基础 2.2互连

1) 典型工艺 ✓ CMOS N阱 1P4M工艺剖面图

CIW窗口

24

第二部分:版图设计基础

3. 版图编辑器 4) virtuoso编辑器--工作区和层次显示器

LSW

工作区域

25

第二部分:版图设计基础 3. 版图编辑器

5) virtuoso编辑器 --版图层次显示(LSW)

26

第二部分:版图设计基础 3. 版图编辑器

6) virtuoso编辑器 --版图编辑菜单

连线与孔之间的连接

21

3. 版图编辑器 1) virtuoso编辑器

建立LIBRARY

第二部分:版图设计基础

CIW窗口

22

第二部分:版图设计基础 3. 版图编辑器

2) virtuoso编辑器--Library manager

23

第二部分:版图设计基础 3. 版图编辑器

3) virtuoso编辑器-- 建立cell

YES LAYOUT CASE

YES

第三部分:版图的准备

4. LVS文件 4.4 layer mapping: 1) 右图描述了文件的层次定义、 层次描述及gds代码; 2) Map文件 是工艺转换

之间的一个桥梁。

第三部分:版图的准备

4. LVS文件 4.5 Logic operation: 定义了文件层次的 逻辑 运算。

IC版图设计 入门培训材料

现在就可以使用提取的网表通过SPICE仿真确定 电路的实际性能。

2. 设计规则

如果仿真出的电路性能(如瞬态响应时间 或功耗)与期望值不相符,就必须对版图 进行修改并重复上面的过程。版图修改主 要是对晶体管尺寸中的宽长比进行修改。 这是因为管子的宽长比决定器件的跨导和 寄生源极和漏极电容。

应用Leff、Weff、 Weff/ Leff 不要用L、W、W/L

3. 基本工艺层版图

有源区接触

有源区接触(Active Contact):硅与互连金属的接触

3. 基本工艺层版图 金属层:与有源区接触

信号互连线 金属层1(Metal1) 电源线、地线

Metal1至有源区 接触的最小间距

Metal1线的 最小宽度

宽度指封闭几何图形的内边之间的距离

最小宽度 最大宽度

2. 设计规则 间距规则(Separation rule)(1)

间距指各几何图形外边界之间的距离

同一工艺层的间距 (spacing)

不同工艺层的间距 (separation)

2. 设计规则 交叠规则(Overlap rule)(1)

交叠有两种形式:

为了减小寄生效应,设计者也必须考虑对 电路结构进行局部甚至全部的修改。

掩膜版图设计流程

2. 设计规则

CMOS反相器版图设计

通过对CMOS反相器掩膜版图的设计来逐步讲解版图设 计规则的应用。

首先,我们要根据设计规则生成每个晶体管。

假设我们要设计一个具有最小晶体管尺寸的反相器。

IC模拟版图设计PPT课件

3) virtuoso编辑器-- 建立

cell

CIW窗口

.

24

第二部分:版图设计基础

3. 版图编辑器 4) virtuoso编辑器--工作区和层次显示器

LSW

工作区域

.

25

第二部分:版图设计基础

3. 版图编辑器 5) virtuoso编辑器 --版图层次显示(LSW)

.

26

第二部分:版图设计基础

IC模拟版图设计

.

1

目录

第一部分:了解版图

1. 版图的定义 2. 版图的意义 3. 版图的工具 4. 版图的设计流程

第二部分:版图设计基础

1. 认识版图 2. 版图组成两大部件 3. 版图编辑器 4. 电路图编辑器 5. 了解工艺厂商

.

2

目录

第三部分:版图的准备

1. 必要文件 2. 设计规则 3. DRC文件 4. LVS文件

3. 版图编辑器 6) virtuoso编辑器 --版图编辑菜单

.

27

第二部分:版ห้องสมุดไป่ตู้设计基础

3. 版图编辑器 7) virtuoso编辑器 --显示窗口

.

28

第二部分:版图设计基础

3. 版图编辑器 8) virtuoso编辑器 --版图显示

.

29

第二部分:版图设计基础

3. 版图编辑器 9) virtuoso编辑器--数据流格式版图输出

.

8

IC模拟版图设计

第二部分:版图设计基础

1. 认识版图 2. 版图组成两大部件

2.1 器件 2.2 互连

3. 版图编辑器 4. 电路图编辑器 5. 了解工艺厂商

.

第四章IC版图设计1

技术水平而制定的。

因此不同的工艺,就有不同的设计规则。 设计规则是版图设计和工艺之间的接口。

厂家提供的设计规则

设计者只能根据厂家提供的设计规则进行版图设计。

严格遵守设计规则可以极大地避免由于短路、断路造成

的电路失效和容差以及寄生效应引起的性能劣化。

材料与能源学院微电子材料与工程系

VDD

OUT

5.1

N-well

N+

P+

Poly

Metal

Contact

反相器版图设计中需要考虑的各项规则示意图

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

N-well

N+

P+

Poly

Metal

Contact

反相器版图设计中需要考虑的各项规则示意图

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

IN GND

4 .4 1.4 4.2 1. 3 2.2 3.1 3.4 4.5 4.7 2.1 2.1 5.2 4.7 3.1

1.3

4.2 4 .4 4.5 4.7 3.4 1.1

描

述

尺

90

寸

目的与作用

封装、邦定需要

最小焊盘大小

6.2

6.3

最小焊盘边间距

最小金属覆盖焊盘

80

6.0

防止信号之间串绕

保证良好接触

6.4

焊盘外到有源区最 小距离

25.0

提高可靠性需要

材料与能源学院微电子材料与工程系

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IC版图设计1

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

➢ 设计规则(design rule)

由于器件的物理特性和工艺的限制,芯片上物理层的尺 寸和版图的设计必须遵守特定的规则。

以上两点要求均反映在版图的几何设计规则文件中。

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

(3)定义设计人员设计时所用的电参数的范围。 通常,这些电参数中包括晶体管增益、开启电压、

电容和电阻的数值,均反映在版图的电学设计规则文件 中。

这些规则是各集成电路制造厂家根据本身的工艺特点和 技术水平而制定的。

因此不同的工艺,就有不同的设计规则。 设计规则是版图设计和工艺之间的接口。

➢ 厂家提供的设计规则

设计者只能根据厂家提供的设计规则进行版图设计。 严格遵守设计规则可以极大地避免由于短路、断路造成

的电路失效和容差以及寄生效应引起的性能劣化。

一般来讲,设计规则反映了性能和成品率之间可能的最 好的折衷。

规则越保守,能工作的电路就越多(即成品率越高)。 规则越富有进取性,则电路性能改进的可能性也越大,

这种改进可能是以牺牲成品率为代价的。

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

➢ N阱设计规则示意图

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

➢ P+、N+有源区相关的

设计规则列表

Байду номын сангаас编 号

描 述

尺 寸

目的与作用

2.1

P+、N+有 源区宽度

3.5 保证器件尺寸, 减少窄沟道效应

2.2

P+、N+有 源区间距

➢ 最小交叠(minOverlap)

交迭有两种形式: a)一几何图形内边界到另一图形的内边界长度(overlap), 如下图(a)所示 b)一几何图形外边界到另一图形的内边界长度(extension), 如下图(b)所示

Y

X

(a)

(b)

交叠的定义

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

➢ 最小间距(minSep)

间距指各几何图形外边界之间的距离,如下图所示

间距的定义

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

➢ 层次

人们把设计过程抽象成若干易于处理的概念性版图层次, 这些层次代表线路转换成硅芯片时所必需的掩模图形。

下面以某种N阱的硅栅工艺为例分别介绍层次的概念。

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

➢ NWELL硅栅的层次标示

3.5

减少寄生效应

➢ P+、N+有源区设计

规则示意图

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

➢ Poly相关的设计规则列表

编号 3.1 3.2 3.3 3.4 3.5

描述

多晶硅最小宽 度

多晶硅间距

与有源区最小 外间距

多晶硅伸出有 源区

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

3.2 版图几何设计规则 ➢ 版图几何设计规则可看作是对光刻掩模版制备要求。 ➢ 这些规则在生产阶段中为电路的设计师和工艺工程师提供了

一种必要的信息联系。

➢ 设计规则与性能和成品率之间的关系:

与有源区最小 内间距

尺寸

目的与作用

3.0

保证多晶硅线的必要电导

2.0

防止多晶硅联条

1.0

保证沟道区尺寸

➢ 从设计的观点出发,设计规则可以分为三部分:

(1)决定几何特征和图形的几何尺寸的规定 作用:保证各个图形彼此之间具有正确的关系。 每层掩膜上的各个图形部件应该相切,或者应该保持互相分 开;不同掩膜上的各个图形部件应该套合,或者应该保持互相分 开。

(2)确定掩膜制备和芯片制造中都需要的一组基本图形部件的强制性 要求。 典型的图形部件可能包括制造中所用的各块掩膜精确套准所 需的对准标志,把各个电路从硅片切下来的划片间距以及供压焊 封装用的压焊点尺寸。

层次表示 NWELL Locos Poly

Contact Metal Pad

含义 N阱层 N+或P+有源区层 多晶硅层 接触孔层 金属层 焊盘钝化层

标示图

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

➢ NWELL层相关的设计规则

编号

描述

尺寸(um)

目的与作用

1.1

N阱最小宽度

10.0

保证光刻精度和器件尺寸

1.2

N阱最小间距

10.0

防止不同电位阱间干扰

1.3

N阱内N阱覆盖P+

2.0

保证N阱四周的场注N区环的尺 寸

1.4

N阱外N阱到N+距 离

8.0

减少闩锁效应

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

➢ 常用的有两种方法可以用来描述设计规则:

微米(micron)规则:以微米为分辨单位; λ(lambda)规则:以特征尺寸为基准。

通常以特征尺寸的一半为单位。 如:特征尺寸L为1um时, λ为0.5um。

➢ 设计规则具体内容主要包括各层的最小宽度、层与层之间的

最小间距和最小交叠等。

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

➢ 最小宽度(minWidth)

最小宽度指封闭几何图形的内边之间的距离,如下图所示

宽度定义 在利用DRC(设计规则检查)对版图进行几何规则检查时,

对于宽度低于规则中指定的最小宽度的几何图形,计算机 将给出错误提示。