基于CPLD的SPI接口设计

基于CPLD的测试系统接口设计(1)

基于CPLD 的测试系统接口设计高相铭,李国伟(安彩集团,河南省安阳市455000)摘 要:介绍了一种用CPLD (复杂可编程逻辑器件)作为核心控制电路的测试系统接口,通过对CPLD 和TTL 电路的比较及CPLD 在系统中实现的强大功能,论述了CPLD 在测试系统接口中应用的可行性和优越性,简单介绍了VHDL 在CPLD 设计中的应用。

实验证明用CPLD 实现的电路具有集成度高、灵活性强、可靠性高、易于升级和扩展等特点。

给出了主要电路图和时序仿真图。

关键词:CPLD;测试系统接口;VH DL 中图分类号:TM 930.9收稿日期:2006-11-06;修回日期:2007-01-09。

0 引 言CPLD (复杂可编程逻辑器件)兼容了PLD (可编程逻辑器件)和通用门阵列的优点,具有编程灵活、可实现较大规模电路的特点,同时具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定、可实时在线检验等优点,因此广泛应用于产品的原型设计和产品生产之中。

1 CPLD 在测试系统中的作用随着计算机和微电子技术的迅猛发展,单片机技术被广泛应用到各种智能仪表、工业控制及家用电器控制领域。

但是它们在提高电路板的集成度、增强系统功能的同时也带来了很多测试和维修上的问题。

传统的测试仪器和设备(如万用表、示波器、逻辑分析仪等)已不能适应现代测试要求,更无法快捷地诊断出系统的故障所在,因此给一个产品的生产和维护带来了诸多困难。

为了提高诊断效率,我们设计了一套基于虚拟仪器的单片机电路板故障测试诊断系统。

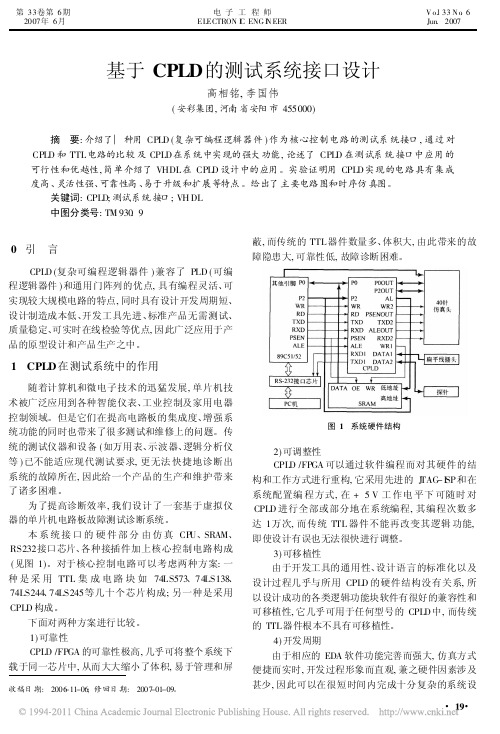

本系统接口的硬件部分由仿真CP U 、SRAM 、RS232接口芯片、各种接插件加上核心控制电路构成(见图1)。

对于核心控制电路可以考虑两种方案:一种是采用TTL 集成电路块如74LS573、74LS138、74LS244、74LS245等几十个芯片构成;另一种是采用CPLD 构成。

下面对两种方案进行比较。

毕业设计171基于CPLD的DSP系统接口设计

基于CPLD的DSP系统接口设计中文摘要本论文详细介绍了基于CPLD的DSP系统接口设计的方案与实现方法。

在本次设计过程中,主要是以模块思想来设计整个DSP系统。

在整个硬件系统设计中,以DSP芯片为核心,用CPLD来实现控制数据中转、与外围设备的通信。

本论文介绍了如何利用CPLD设计并实现TMS320C5416芯片与SRAM、FLASH、串并转换器等外围设备之间的接口,即利用了CPLD 实现TMS320C5416系统接口的扩展。

关键词:DSP;系统接口; CPLDDesign DSP system connection with CPLDAbstractThe present paper in detail introduced the DSP system connection of based on the CPLD designs plan and the realization method. In this design process, mainly designs the entire DSP system by the module of thought.In the entire hardware system design process, takes the DSP chip as the core, realizes the control data relay by the CPLD decoding, and the auxiliary equipment correspondence. This introduced how switching using CPLD connection designs the between TMS320C5416 chip and SRAM, FLASH, string and auxiliary equipment and so on, namely used CPLD to design the TMS320C5416 system connection the expansion.Key words: DSP ; The interface of system ;CPLD第一章:绪论§1.1 课题的提出及意义随着信息化技术的飞速发展,各种便携式电子产品和个人助理不断涌现,但是,许多消费电子的采集处理系统有着自身的不足,采集装置的复杂化,图像实时处理对处理器的依赖,图像处理系统的造价、速度及体积都成为限制图像技术应用的瓶颈。

基于 CPLD 的计算机接口电路设计技巧

基于CPLD的计算机接口电路设计技巧郭志友孙慧卿华南师范大学光电子材料与技术研究所广州 510631摘要:本文介绍了利用计算机ISA、PCI总线和打印机接口设计密码电路。

基于CPLD 设计密码电路,具有加密性能好的特性。

通过并行打印机接口设计一个密码电路,密码存储在电路中,通过操作接口读取密码。

ISA总线可以直接读取电路密码,PCI总线可以通过W89C940af对密码电路进行操作,读取设置密码。

关键词:计算机密码电路ISA和PCI总线Dsigned Skill of Computer Interface Circuit Based on CPLDGuoZhiYou SunHuiqing(South China Normal University of School for Information and Optoelectronic Science and Engineering, Guangzhou 510631, China)Abstract: The paper proposes a password circuit that by using computer ISA and PCI bus and printer interface. A password circuit is designs by using CPLD. Its characteristic is very secure. Using serial printer interface designs a circuit of password deposited in circuit. The circuit may read and get passwords. ISA buses read and get passwords directly. PCI buses may be manipulated by W89C940af in order to read and get and set passwords.Key words: computer; password circuit; ISA and PCI buses1 引言随着计算机CPU的运行速度在不断提高,至今已经到约2GHz,基本内存也达到了1M~512M,给计算机的应用软件运行提供了较好的运行条件,同时也足金促进了计算机软件的发展。

利用MAX II CPLD 实现SPI 至I2C 接口

AN-486-1.0

应用笔记 486:利用 MAX II CPLD 实现 SPI 至 I2C 接口

I2C

I2C 主机 SPI 从机 SPI 主机

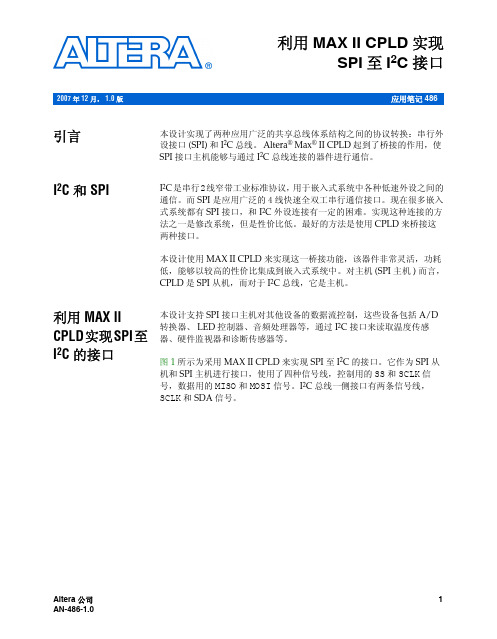

图 1. 利用 MAX II CPLD 实现 SPI 至 I2C 的接口

Altera MAX II

UP ASIC MCU FPGA

SCLK SS

MOSI MISO

f

请访问下面的网址,下载 SPI 仿真软件:

/files/soft_dev_tools/software/device_driv ers/SPIGen.html

2. 完成注册后,下载并安装 SPIGen。您需要对它进行配置,以适应您 的应用程序以及由 MDN-B2 演示板提供的并口至 SPI 软件狗。

图 4 所示为演示布局。

图 4. 演示布局

基于PC并口的SPI主机 采用了Freescale的 SPIGen

并口至 SPI 接口

CPLD 桥接

DS2745 电池量表

I2C 主机 SPI 从机

Altera 公司

4. 选择16位格式,以十六进制(Intel格式)文件格式(.hex)来显示SPI值。 5. 按照以下步骤来配置 SPI Pins 标签:

f

14. 每次发送 SPI 数据时,使用表 5 的 .hex 数据,单击 Send Once。确定收 到了应答数据。

15. 观察接收到的电池量表数据。收到的有两部分,首先是 MSB 8 位数 据,然后是 LSB 3 位数据 ( 最后一行 )。

16. 改变电池量表模块的黄色预置部分,观察接收数据的变化。黄色预置 部分改变了电池量表芯片 (Maxim DS2745) 的输入电压值,该芯片通 过其 I2C 接口,以 11 位 2 进制兼容格式来提供电压读数。

用Verilog语言写的CPLD和MCU通讯的SPI接口程序

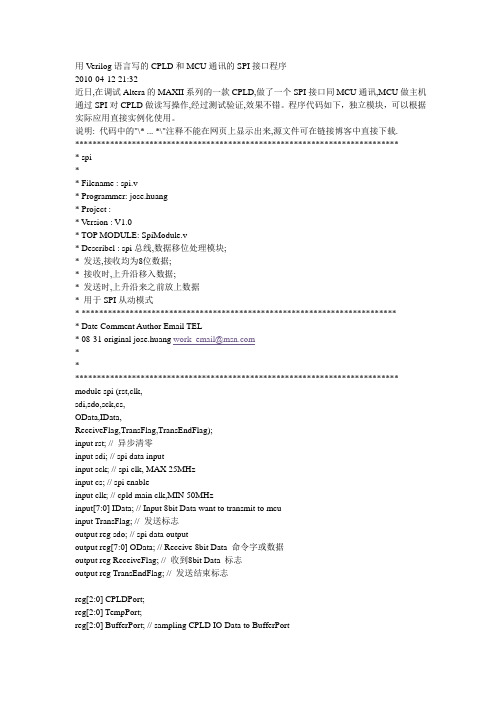

用Verilog语言写的CPLD和MCU通讯的SPI接口程序2010-04-12 21:32近日,在调试Altera的MAXII系列的一款CPLD,做了一个SPI接口同MCU通讯,MCU做主机通过SPI对CPLD做读写操作,经过测试验证,效果不错。

程序代码如下,独立模块,可以根据实际应用直接实例化使用。

说明: 代码中的"\* ... *\"注释不能在网页上显示出来,源文件可在链接博客中直接下载.*************************************************************************** spi** Filename : spi.v* Programmer: jose.huang* Project :* Version : V1.0* TOP MODULE: SpiModule.v* Describel : spi总线,数据移位处理模块;* 发送,接收均为8位数据;* 接收时,上升沿移入数据;* 发送时,上升沿来之前放上数据* 用于SPI从动模式* ************************************************************************* Date Comment Author Email TEL* 08-31 original jose.huang work_email@* ------- ----*************************************************************************** module spi (rst,clk,sdi,sdo,sck,cs,OData,IData,ReceiveFlag,TransFlag,TransEndFlag);input rst; // 异步清零input sdi; // spi data inputinput sck; // spi clk, MAX 25MHzinput cs; // spi enableinput clk; // cpld main clk,MIN 50MHzinput[7:0] IData; // Input 8bit Data want to transmit to mcuinput TransFlag; // 发送标志output reg sdo; // spi data outputoutput reg[7:0] OData; // Receive 8bit Data 命令字或数据output reg ReceiveFlag; // 收到8bit Data 标志output reg TransEndFlag; // 发送结束标志reg[2:0] CPLDPort;reg[2:0] TempPort;reg[2:0] BufferPort; // sampling CPLD IO Data to BufferPortreg[7:0] samplnum;always@(posedge clk)beginCPLDPort[0] <= sdi;CPLDPort[1] <= sck;CPLDPort[2] <= cs;endalways@(posedge clk or negedge rst)beginif(!rst) // 异步清零beginsamplnum <= 8'b0;endelse if(TempPort == CPLDPort)beginsamplnum <= samplnum + 1'b1;endelsebeginsamplnum <= 8'b0;TempPort <= CPLDPort;endendalways@(posedge clk or negedge rst)beginif(!rst) // 异步清零beginBufferPort[0] <= 1'b0; //CPLDPort[0] <= sdi; BufferPort[1] <= 1'b0; //CPLDPort[1] <= sck; BufferPort[2] <= 1'b1; //CPLDPort[2] <= cs;endelsebeginif(samplnum > 10) // set by cpld main clk and spi clk beginBufferPort <= TempPort;endelse BufferPort <= BufferPort;endendwire wsdi;wire wsck;wire wcs;assign wsdi = BufferPort[0]; //CPLDPort[0] <= sdi; assign wsck = BufferPort[1]; //CPLDPort[1] <= sck; assign wcs = BufferPort[2]; //CPLDPort[2] <= cs;// 计数reg[7:0] ShiftCounter;reg[7:0] ClrFlagCounter;reg Bwsck;always@(posedge clk or negedge rst or posedge wcs) beginif(!rst) // 异步清零beginShiftCounter <= 8'b0;ReceiveFlag <= 1'b0;TransEndFlag <= 1'b0; // shift状态清接收标志Bwsck <= 1'b0;endelse if(wcs) // 结束异步清零beginShiftCounter <= 8'b0;Bwsck <= 1'b0;if(ClrFlagCounter == 10)beginReceiveFlag <= 1'b0; // SPI操作结束清接收标志TransEndFlag <= 1'b0; // shift状态清接收标志endelse ClrFlagCounter <= ClrFlagCounter + 1'b1;endelsebeginBwsck <= wsck;ClrFlagCounter <= 8'b0;if(wsck && (!Bwsck)) // 上升沿处理beginif(ShiftCounter == 7)beginShiftCounter <= 8'b0;if(!TransFlag) // receive data from mcu ReceiveFlag <= 1'b1; // 收到8bit dataelseTransEndFlag <= 1'b1; // 发送完成endelsebeginShiftCounter <= ShiftCounter + 1'b1;ReceiveFlag <= 1'b0; // shift状态清接收标志TransEndFlag <= 1'b0; // shift状态清接收标志endendendend// 移位always@(posedge clk or negedge rst or posedge wcs) beginif(!rst)sdo <= 1'b0;else if(wcs)sdo <= 1'b0;else if(wsck && (!Bwsck)) //上升沿处理beginif(!TransFlag) // receive data from mcubeginOData <= {OData[6:0],wsdi};endelse // transmit data to mcubeginsdo <= IData[7-ShiftCounter];endendendendmodule波形图。

基于CPLD的8位总线接口设计

基于CPLD 的8位总线接口设计谢付正,郭树旭(吉林大学电子科学与工程学院 吉林长春 130012)摘 要:基于CPLD 技术设计了双通道总线接口并给出该接口的通道模型和控制方法。

本接口采用存储器访问模式,克服了某些CPU 外围通信接口少的缺点,易于实现双CPU 间的总线对接,且无需考虑复杂的总线仲裁机制。

该接口适用于双主机间的数据传输,具有使用方便、速率匹配、实时响应等优点。

同时采用V HDL 硬件描述语言,使设计易于模块化,也为基于CPLD 的总线转换及其他接口电路的设计提供了新的思路。

关键词:CPLD ;V HDL ;总线接口;总线仲裁中图分类号:TN92 文献标识码:B 文章编号:1004373X (2006)0607902Design of 8bits Bus Interface B ased on CPLDXIE Fuzheng ,GUO Shuxu(College of Electronic Science and Engineering ,Jilin University ,Changchun ,130012,China )Abstract :Based on CPLD (Complex Programmable Logic Device )8bits bus interface ,channel model and control method arecarried out.This type of bus interface can be accessed by memory mode and be applied to the exchange of data between two hosts ,which can overcome the lack of communication interface in some types of CPU.It possesses the features of convenience ,speed match and real time response.Moreover ,the modularization and reuse are easily to realize for the induction of V HDL (Very High Speed Integrated Cir 2cuit Hardware Description Language ).It also brings a new ideal for the conversation f rom bus to other interface circuits.Keywords :CPLD ;V HDL ;bus interface ;bus arbitration收稿日期:200509191 引 言在现代工业控制或通信系统中,多主机进行数据传输的需求非常广泛。

应用CPLD实现ASI_SPI接口转换的方法

应用CP LD 实现ASI -SPI 接口转换的方法□廖晓维,朱 红(电子科技大学,四川成都610054)摘 要:遵照国家的DVB 标准及SPI 接口标准,提出一种不需要使用FIFO ,就能恢复出SPI 接口的PSY NC 、DAV LI D 信号的方案。

经硬件实现,仅使用CP LD 芯片就能完成该功能,实时稳定地产生出PSY NC 、DAV LI D 信号,避免了使用FPG A 芯片及FIFO 带来的高成本问题。

对SPI 时钟的恢复提出一种新的解决方法,简化了ASI —SPI 转换卡的硬件设计。

关键词:CP LD ;ASI ;SPI ;接口转换中图分类号:T N911.25 文献标识码:A 文章编号:1007-7022(2004)18-0074-02Converting Signals from ASI to SPI Using CP LD□LI AO X iao 2wei ,ZH U H ong(University of Electronic and T echnology ,Sichuan Chengdu 610054,China )Abstract :We gave a new alg orithm to convert signals from ASI to SPI without FIFO ,according to the national DVB standard and SPI interface standard.This method can recover PSY NC and DAV LI D signals only use CP LD chips ,reduced the cost.And m ore in this paper we found a new way to recover SPI clock ,which sim plified the hardware design of ASI -SPI card.K ey w ords :CP LD ;ASI ;SPI ;Interface C onversion1 引言在数字技术高速发展的今天,可编程逻辑器件的制造工艺不断提高,CP LD 等可编程器件的速度和规模也有了很大的提高,而且具有集成度高、体积小、功耗低、设计灵活等优点。

【CPLD Verilog】CPLD实现SPI接口

CPLD实现SPI接口1 实现原理CPLD实现SPI接口模块,通过对寄存器的操作,实现SPI接口功能,对外部SPI设备进行访问。

CPLD内部SPI模块逻辑框图如下所示。

通过对主时钟分频,得到的SPI接口时钟,其分频值可通过spi_clk_div值设定,最小为6分频,当设置分频值低于6分频时,默认6分频。

SPI接口的片选信号spi_cs在写数据传输寄存器spi_tx_data时,通过自动产生写脉冲spi_tx_data_we_pulse,逻辑综合生成。

spi_rx_data_rd_pulse在读取接收数据spi_rx_data的数据时自动产生。

spi_di和spi_do分别由数据移位寄存器通过数据移位产生和接收。

spi_clk由内部分频时钟和传输状态逻辑综合输出,在有数据时输出,无数据时保持高电平。

状态逻辑spi_tx_data_we_busy信号分别表示数据正在传输,无法写入spi_tx_data寄存器;spi_rx_data_rd_ready信号表示数据接收完成,可读取spi_rx_data寄存器的值。

错误状态逻辑spi_data_tx_we_overflow信号表示在spi_tx_data寄存器中写入了待传输值后,还未传输就又写入新的传输数据,表示写数据溢出。

spi_data_rx_rd_nop信号表示在spi_rx_data寄存器中没有接收值时,去读取了无效的数据,表示读空数据。

spi_data_rx_rd_overtime信号表示在spi_rx_data寄存器中有接收数据时,在下一次接收数据接收完成时都没有读走,表示读取数据超时。

产生接口错误时,通过reset_n复位SPI接口模块,可清楚错误。

最终传输生成的时序图如下。

在数据发送时,将待发送数据写入spi_tx_data,数据将自动发送,之后检测spi_tx_data_we_busy状态值,待此信号无效(0)时,写入下一个待发送的数据,重复此动作,直到数据发送完成,在正在发送的数据传输完成都没有新数据写入时,传输自动完成。

SPI接口设计与实现

SPI接口设计与实现SPI(SerialPeripheralInterface)总线是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

SPI总线应用广泛,已经成为很多器件的标准配置,可以直接和各个厂家生产的多种标准外围器件直接接口。

其它常用的串行接口还有I2C、UART这两种接口,这三种接口互有优缺点。

与I2C接口相比,SPI接口速度更快、协议更简单、并且是全双工的,但连线也相对多一些。

与UART接口相比,SPI更灵活,因为其使用主设备的时钟进行同步,所以两个比特之间的时间间隔可以是任意的。

在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显得简单高效。

1SPI总线工作原理SPI总线一般以主/从模式工作,通常有一个主设备和一个或多个从设备,数据传输由主机控制,典型SPI结构框图如图1所示。

SPI总线包含四条信号线,分别是sclk、miso、mosi和cs,其中,sclk为数据传输时钟,由主机产生;miso是从机输出,主机输入数据线;mosi是主机输出,从机输入数据线;cs是从设备片选信号,由主机控制,当连接多个从设备时,通过该信号选择不同的从设备。

SPI总线是按字节发送数据的,主机和从机内部都包含一个8位串行移位寄存器,在时钟信号控制下,寄存器内的数据由高到低输出至各自的数据线,8个时钟后,两个寄存器内的数据就被交换了。

如果只进行写操作,主机只需忽略接收到的字节;反之,若主机要读取从机的一个字节,就必须发送一个空字节来引发从机的传输。

当主机发送一个连续的数据流时,可以进行多字节传输,在这种传输方式下,从机的片选端必须在整个传输过程中保持低电平。

根据串行同步时钟极性和相位不同,SPI有四种工作方式。

时钟极性(CPOL)为0时,同步时钟的空闲状态为低电平,为1时,同步时钟的空闲状态为高电平。

时钟相位(CPHA)为0时,在同步时钟的第一个跳变沿采样数据,为1时,在同步时钟的第二个跳变沿采样数据。

基于CPLD的数据采集与显示接口电路仿真设计

基于CPLD的数据采集与显示接口电路仿真设计黄崇富;李建华【摘要】常规数据采集与显示方法是应用CPU或DSP通过软件控制数据采集的模/数转换,这样将会频繁中断系统的运行,从而降低系统的运算速度,数据采集的速度也将受到限制.通过CPLD实现由硬件控制模/数转换和数据显示,最大限度地提高系统的信号采集和处理能力.这里运用VHDL硬件编程语言,通过状态机设计程序,完成A/D转换芯片与可编程逻辑芯片的接口.将A/D转换结果以BCD码形式通过CPLD芯片进行显示,实时观测转换进程,给出了BCD码转换流程图,完成相应电路设计,通过QuartusⅡ软件进行仿真,并在开发系统上成功实现功能验证,提高了系统的运算速度.【期刊名称】《现代电子技术》【年(卷),期】2009(032)024【总页数】4页(P147-150)【关键词】可编程逻辑器件;模数转换;二-十进制码显示;接口电路【作者】黄崇富;李建华【作者单位】重庆工程职业技术学院,重庆,400037;重庆工程职业技术学院,重庆,400037【正文语种】中文【中图分类】TP368.10 引言CPLD称为复杂可编程逻辑设计芯片,它是大规模可编程器件,具有高集成度、高可靠性、高速度的特点。

CPLD是利用EDA技术进行电子系统设计的载体。

硬件描述语言是EDA技术进行电子系统设计的主要表达手段,VHDL语言是常用的硬件描述语言之一;软件开发工具是利用EDA技术进行电子系统设计的智能化的自动化设计工具,常用开发工具有QuartusⅡ,Ispexpert,Foundation等。

CPLD 以高速、高可靠性、串并行工作方式等特点在电子设计中广泛应用。

它打破了软硬件之间的界限,加速了产品的开发过程。

同样单片机具有性价比高、功能灵活、良好的数据处理能力等特点。

CPLD芯片与单片机结合在高性能仪器仪表中应用广泛。

1 电路的仿真设计1.1 硬件电路功能用一片MCS-51芯片、一片CPLD/FPGA芯片、模/数转换器ADC0809和数/模转换器DAC0832构成一个数据采集系统[1,2],并用CPLD/FPGA实现数据采样、D/A转换输出、有关数据显示的控制,单片机完成对A/D转换数据运算。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于CPLD 的SP I 接口设计

D esign i ng SP I I n terface ba sed on CPLD

何永泰

(楚雄师范学院 楚雄 675000)

【摘 要】 根据SP I 同步串行接口的通信协议,介绍了在X ilinx Coo lR unnct XPLA 3CPLD 中利用V HDL 语言实现SP I 接口的设计原理和编程思想,通过用此接口,使得那些没有SP I 接口功能的微处理器和微控制器,也能通过SP I 接口与外围设备进行数据交换。

【关键词】 SP I 接口,CPLD ,接口扩展,接口设计,串行接口

ABSTRACT A cco rding to comm un icati on p ro toco l of SP I synch ronou s serial in terface ,th is paper p resen ts the design theo ry and p rogramm ing idea of i m p lem en ting SP I in terface w ith V HDL language in X ilinx Coo lR unner XPLA 3CPLD .T h is in terface can be u sed to data exchange w ith peri pheral apparatu s fo r m icrop rocesso r and m icrocon tro ller w h ich have no t SP I in terface functi on .KEYWOR D S SP I in terface ,CPLD ,in terface expan si on ,in terface design ,serial in terface

1 SP I 总线接口协议

SP I (Seri on Perp heral In terface )总线接口是一个

全双工,同步串行数据接口。

许多微处理器,微控制器和外部设备具有这个接口。

它能够实现在微控制器之间或微控制器与外部设备之间通信。

SP I 总线通常有4条线组成,即:串行时钟线(SCK )、主机输出从机输入

线(M O S I )、

主机输入从机输出线(M ISO )和从机选择线SS N 。

SCK 靠主机和数据流来驱动。

M O S I 数据线从主机输出数据作为从机的输入数据。

M ISO 数据线传送从机输出的数据作为主机的输入数据。

在大多数情况下,使用一个SP I 作为主机,它控制数据向1个或几个从机传送。

主机驱动数据从它的SCK 和M O S I 端到各从机的SCK 和M O S I 端,被选择的从机驱动数据从它的M ISO 端到主机的M ISO 端。

SS N 控制线用于从机选择控制。

SCK 的相位和极性能改变SP I 的数据格式,时钟极性CPOL =‘0’,串行数据的移位操作由时钟正脉冲触发,时钟极性CPOL =‘1’,串行数据的移位操作由负脉冲触发;时钟相位CPHA =‘0’,

串行数据的移位

图1 CPHA =‘0’时SP I 的数据转换时序图

操作由时钟脉冲前沿触发,时钟相位CPHA =‘1’,串行数据的移位操作由时钟脉冲后沿触发。

时钟相位CPHA =‘0’时SP I 的数据转换时序图如图1所示。

在图1中SCK 信号在第一个SCK 周期中的前半周期无效,在这种模式中,SS 的下降沿示意数据传送的开始,因此,SS 在连续串行字节之间必须被取反和重新申明。

时钟相位CPHA =‘1’时SP I 的数据转换时序图如图2所示。

在图2中SCK 信号从无效电平到有效电平的第一边沿意味着在这种模式下数据传送的开始,SS 信号能保持有效的低电平在连续串行字节之间,这种模式用于只有一个主机和一个从机的系统中。

在SP I 传送数据时,8位数据从一个SP I 接口移出时,另一个SP I 接口也开始移出8位数据,这样主机的8位移位寄存器和从机的8位移位寄存器可以被看作是16移位寄存器,16位移位寄存器移动8个位置就实现了在主机和从机之间交换数据。

基于CPLD 的SP I 接口设计中,从SP I 总线上接收的数据被保存在一个接收寄存器中,发送的数据被写到一个发送寄存器中。

图2 CPHA =‘1’时SP I 的数据转换时序图

3 20040414收到,20040724改回

33 何永泰,男,1970年生,讲师,在读硕士,研究方向:电子工程设计。

・

72・第17卷 第10期 电脑开发与应用 (总497)

2 基于Coo lR unner CPLD的SP I 设计结构

基于CPLD设计的SP I接口其目的在于为

那些没有SP I接口功能的微控制器(如8031等)

扩展SP I接口功能。

8031单片机与Coo lR unner CPLD SP I接口的连接框图如图3所示。

为了满足扩展微控制器的SP I接口功能,基于CPLD的SP I接口必须具有以下功能:①与微控制器的接口功能;②8位外部从机选择功能;③时钟极性和相位选择的不同,有四种数据传输模式;④SP I数据传送完成标志。

在SP I接口中Coo lR unner XPLA3 CPLD的35个I O口被定义为SP I接口的控制线、数据线和地址线等。

SP I接口的结构框图如图4所示。

从图中可以看出基于CPLD的SP I设计主要由两大部分组成,即与微控制器接口的控制部分和SP I 接口控制部分。

与微控制器接口的控制部分通过三总线方式使SP I与微控制器相连接,实现微控制器的SP I接口功能扩展。

SP I接口控制部分主要实现SP I 接口与其他SP I接口的通信。

3 软件设计

微控制器8031单片机通过基于CPLD的SP I接口,实现了SP I接口的扩展。

其系统的软件设计主要包括两部分。

第一部分是8031单片机与SP I接口之间通信的软件设计,在这一部分中,主要是对SP I接口中数据传送完成位的检测和对CPLD中各寄存器的读写操作。

第二部分是SP I接口功能的V HDL语言软件设计,在这一部分中采用层次化设计的方法。

顶层中包括两大模块,即:微控制器接口模块和SP I接口模块。

在微控制器接口模块中建立了接口中各寄存器的地址和构造了各寄存器。

在SP I接口控制模块中又包括SP I 控制模块、SP I逻辑模块、SP I移位接收模块和SP I移位发送模块等。

4 结束语

V HDL语言编写的SP I接口程序,下载到Coo l2 R unner XPLA3CPLD中,占用了256个宏单元中的125个,还留有50%多的资源供用户作其他方面的逻辑设计。

通过使用Coo lR unner XPLA3CPLD SP I接口,使得那些没有SP I接口功能的微处理器和微控制器,也能通过SP I接口与外围设备进行数据交换。

Coo lR unner XPLA3CPLD SP I接口,虽然以8031为例介绍其SP I扩展,但只需要作适当的变换,就能用于其他微控制器的SP I扩展接口。

参考文献

1 赵俊超.集成电路设计V HDL教程[M].北京:希望电子出版社,2002

(上接第26页)

压块1为例,在输入各参数的值后,点击计算按钮,将计算结果显示在相应位置。

4 结 论

夹具远程设计系统采用模块化设计思想,基于W eb开发,达到了使用不受时间和地点的限制[4]。

提供了方便的参数化三维图库和数据查询功能,实现了各种设计计算,实现快速夹具设计,提高夹具设计资源的共享程度,对于夹具设计的效率和精度有很重要的作用。

对于协同设计和建立企业动态联盟具有重要的应用前景。

参考文献

1 W ang H u ifen,Zhang You liang.CAD CAM In tegrated Sys2 tem in Co llabo rative D evelopm en t Environm en t.Robo tics and Compu ter In tegrated M anufactu ring,2002,18(3):135~145

2 蔡 瑾,段国林,李翠玉等.夹具设计技术发展综述[J].河北工业大学学报,2002,31(5):35~40

3 王光斗,王春福,机床夹具设计手册(第三版)[M].上海:上海科技出版社.2000

4 李旭荣,崔 磊,周京平.基于W eb的钢板弹簧设计系统开发[J].机电工程技术,2004,33(1):24~25

・

8

2

・ (总498) 基于CPLD的SP I接口设计 2004年。