SPI接口详细说明

SPI通信总线接口定义及数据传输流程

SPI通信总线接口定义及数据传输流程SPI是一种高速的、全双工的、同步的通信总线,并且至多仅需使用4根线,节约了芯片的管脚,SPI通信协议主要应用于EEPROM、FLASH、ADC、DAC等芯片,还有数字信号处理器和数字信号解码器之间。

SPI接口无线模块设备之间采用全双工模式通信,是一个主机和一个或者多个从机的主从模式。

主机负责初始化帧,这个数据传输帧可以用于读与写两种操作,片选线可以从多个从机选择一个来响应主机的请求。

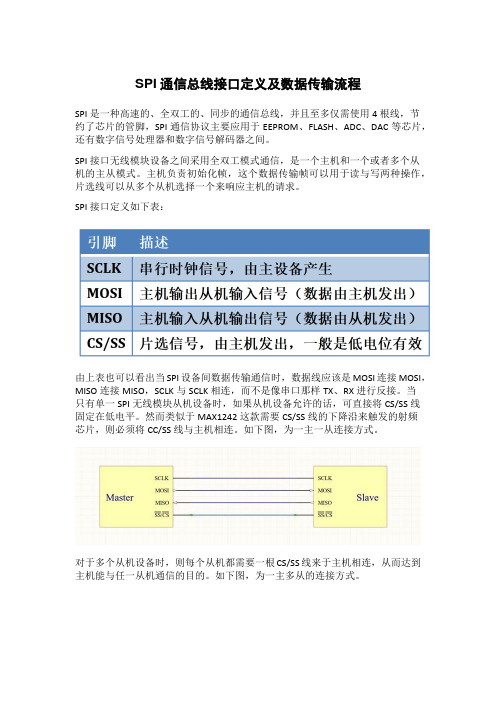

SPI接口定义如下表:由上表也可以看出当SPI设备间数据传输通信时,数据线应该是MOSI连接MOSI,MISO连接MISO,SCLK与SCLK相连,而不是像串口那样TX、RX进行反接。

当只有单一SPI无线模块从机设备时,如果从机设备允许的话,可直接将CS/SS线固定在低电平。

然而类似于MAX1242这款需要CS/SS线的下降沿来触发的射频芯片,则必须将CC/SS线与主机相连。

如下图,为一主一从连接方式。

对于多个从机设备时,则每个从机都需要一根CS/SS线来于主机相连,从而达到主机能与任一从机通信的目的。

如下图,为一主多从的连接方式。

大多数从机设备都有着三态逻辑的特性,因此当设备未被选中时,它们的MISO 信号线会变成高阻抗状态(电气断开)。

没有三态输出的设备则需外接三态缓冲器才能与其他的从机设备共享SPI总线。

数据传输在SPI通信中,SPI主机设备以从机设备支持的频率通过SCLK线给到SPI从机设备,这点也意味着从机是无法主动向主机发送数据的,只能主机轮询向从机发或者从机设备主动通过一个IO口来告知主机数据到达。

在SPI每个时钟周期内,都会进行一次全双工数据的传输。

主机通过MOSI线上发送1bit时,从机也会在读取到之后通过MISO线发送1bit数据出去。

这说明,即使只进行单工通信,也会保持此通信顺序。

SPI传输通常涉及到两个给定了字长的移位寄存器。

例如在主机、从机中的8bit 的移位寄存器。

SPI接口详解1

SPI接口是一种同步串行总线(Serial Peripheral Interface)。

四线SPI接口连线图:CS为片选脚,用于选中从机。

SCLK为时钟脚,用于数据传输时提供时钟信号。

MOSI为主output,从input,即主机发送脚。

对应从机的引脚为SDI。

MISO为主input,从output,机主机接收脚。

对应从机的引脚为SDO。

上述SPI为标准SPI协议(Standard SPI)或单线SPI协议(Single SPI),其中的单线是指该SPI协议中使用单根数据线MOSI 进行发送数据,单根数据线MISO 进行接收数据。

为了适应更高速率的通讯需求,半导体厂商扩展SPI协议,主要发展出了Dual/Quad/Octal SPI协议,加上标准SPI协议(Single SPI),这四种协议的主要区别是数据线的数量及通讯方式,见下表:除了上述接法,SPI还支持半双工1bit模式:SCLK:时钟线。

I/O:数据线,同一时刻要么主机发送,要么主机接收。

SS:片选脚。

Dual SPI的2bit模式:由于是半双工,同一时刻要么主机使用MOSI、MISO线,要么从机使用MOSI、MISO线。

Quad SPI(4线)模式与Dual SPI类似,也是针对SPI Flash,也是半双工,Quad SPI Flash增加了两根I/O线(SIO2,SIO3),目的是SCLK一次触发传输4bit数据。

以AC63芯片SPI接口为例,进行代码分析:根据SPI接口的时序要求,SPI接口可以通过软件实现,也可以通过硬件实现。

这里仅分析硬件实现方式。

查看数据手册可知,芯片最多支持三个SPI接口,SPI接口支持DMA发送、接收功能。

每个SPI接口引脚可以映射到不同的引脚,分别为不同的组,即组A、组B、组C、组D。

SPI硬件包含控制寄存器、波特率寄存器、buf缓冲区寄存器、DMA地址寄存器、DMA计数寄存器。

寄存器结构体定义如下:typedef struct {__RW __u32 CON;__WO __u32 BAUD;__RW __u32 BUF;__WO __u32 ADR;__WO __u32 CNT;} JL_SPI_TypeDef;每个SPI接口寄存器基地址:#define JL_SPI0_BASE (ls_base + map_adr(0x1c, 0x00))#define JL_SPI0 ((JL_SPI_TypeDef *)JL_SPI0_BASE)#define JL_SPI1_BASE (ls_base + map_adr(0x1d, 0x00))#define JL_SPI1 ((JL_SPI_TypeDef *)JL_SPI1_BASE)#define JL_SPI2_BASE (ls_base + map_adr(0x1e, 0x00))#define JL_SPI2 ((JL_SPI_TypeDef *)JL_SPI2_BASE)现将三个SPI寄存器首地址定义在数组中:static JL_SPI_TypeDef *const spi_regs[SPI_MAX_HW_NUM] = { JL_SPI0,JL_SPI1,JL_SPI2,};通过SPI的编号就可以进行对应SPI寄存器的访问操作。

串行外设接口SPI

SPI波特率寄存器(SPI1BR)

数据位 定义 复位

D7 0 0 D6 SPPR2 0 D5 SPPR1 0 D4 SPPR0 0 D3 0 0 D2 SPR2 0 D1 SPR1 0 D0 SPR0 0

D6~D4—SPPR[2:0]为SPI波特率预分频系数 D2~D0—SPR[2:0]为SPI波特率系数源自D1SPISWAI 0

D0

SPC0 0

复位

第7、6、5和2位无效,总为0 D4—MODFEN为主模式故障功能使能 D3—BIDIROE为双向模式输出使能—双向模式由SPI管脚控制0 (SPC0=1)使能时,BIDIROE决定SPI数据输出驱动器是否被使能 为单个双向SPI I/O管脚 D1—SPISWAI为SPI停止在等待模式中 D0—SPC0为SPI管脚控制0。SPC0位用于选择单线双向模式

CPHA=0,CPOL=0时的数据/时钟时序图

CPHA=0,CPOL=1时的数据/时钟时序图

CPHA=1,CPOL=0时的数据/时钟时序图

CPHA=1,CPOL=1时的数据/时钟时序图

8.1.4

模拟SPI

对于不带SPI串行总线接口的MCU来说,可以使用软 件来模拟SPI的操作。举例说明,我们可以使用三个 普通I/O口,分别定 义为pin_SPSCK、pin_MISO、 pin_MOSI来模拟SPI器件的SPSCK、MISO、MOSI

SPI寄存器简介

偏移地址

寄存器名称与缩写

基本功能

配置SPI的基本操作模式(中断 使能、系统使能、发送中断使 能、主从模式、时钟相位、时 钟极性等) 主模式故障功能使能、双向模 式输出 为SPI主机设定预定位速率分频 因子 返回SPI的状态 读取该寄存器将返回从接收数 据缓冲器中读取的数据。写该 寄存器将会把数据写入发送数 据缓冲器

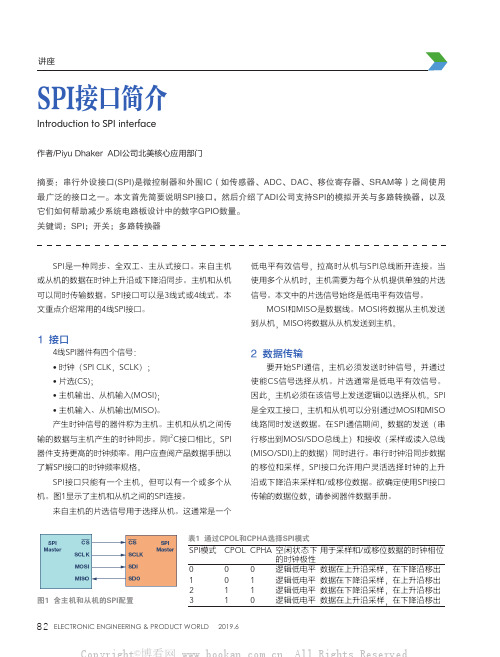

SPI接口简介

图1 含主机和从机的SPI配置

图7 多从机SPI菊花链配置

图3 SPI模式1,CPOL = 0,CPHA = 1:CLK空闲状态 = 低电平,数据在下降沿采样,并在上升沿移出

图2 SPI模式0,CPOL = 0,CPHA = 0:CLK空闲状态 = 低电平,数据在上升沿采样,并在下降沿移出

图4 SPI模式2,CPOL = 1,CPHA = 1:CLK空闲状态 = 高电平,数据在下降沿采样,并在上升沿移出

图5 SPI模式3,CPOL = 1,CPHA = 0:CLK空闲状态 = 高电平,数据在上升沿采样,并在下降沿移出

图6 多从机SPI配置

图3给出了SPI 模式1的时序图。

在此模式下,时钟极性为0,表示时钟信号的空闲状态为图8 菊花链配置:数据传播

图9 微控制器GPIO用作开关的控制信号

图11 使用串行转并行转换器的多从机开关

图12 支持SPI的开关节省微控制器GPIO

图13 菊花链配置的SPI开关可

进一步优化GPIO

下一个从机。

在此配置中,所有从机同时接收同一

时钟。

来自主机的数据直接送到第一个从机

数据提供给下一个从机,依此类推

使用该方法时,由于数据是从一个从机传播到下一个从机,所以传输数据所需的时钟周期数与菊花链中的从机位置成比例。

例如在图7所示的

3个从机能够获得数据,需要24

模式下只需8个时钟脉冲。

图8

菊花链的数据传播。

并非所有SPI。

CAN、I2S、I2C、SPI、SSP总线的介绍和比较

一、SPI总线说明串行外围设备接口SPI(serial peripheral interface)总线技术是Motorola公司推出的一种同步串行接口,Motorola公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。

SPI 用于CPU与各种外围器件进行全双工、同步串行通讯。

SPI可以同时发出和接收串行数据。

它只需四条线就可以完成MCU 与各种外围器件的通讯,这四条线是:串行时钟线(CSK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)、低电平有效从机选择线CS。

这些外围器件可以是简单的TTL移位寄存器,复杂的LCD显示驱动器,A/D、D/A转换子系统或其他的MCU。

当SPI工作时,在移位寄存器中的数据逐位从输出引脚(MOSI)输出(高位在前),同时从输入引脚(MISO)接收的数据逐位移到移位寄存器(高位在前)。

发送一个字节后,从另一个外围器件接收的字节数据进入移位寄存器中。

主SPI的时钟信号(SCK)使传输同步。

其典型系统框图如下图所示。

SPI主要特点有: 可以同时发出和接收串行数据;•可以当作主机或从机工作;•提供频率可编程时钟;•发送结束中断标志;•写冲突保护;•总线竞争保护等。

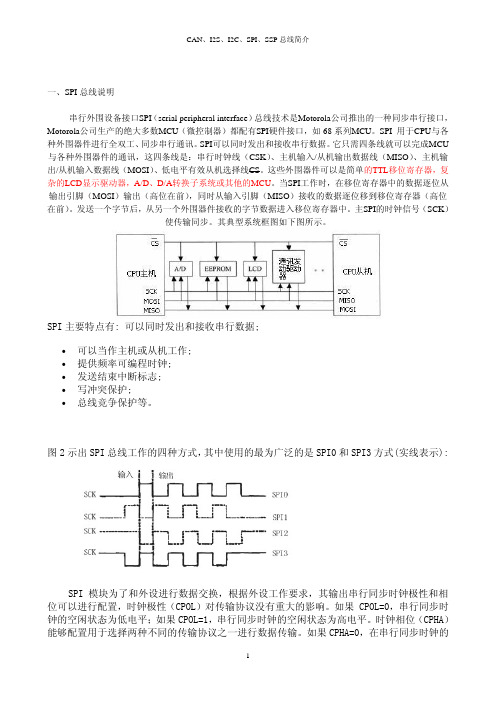

图2示出SPI总线工作的四种方式,其中使用的最为广泛的是SPI0和SPI3方式(实线表示):SPI 模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果 CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI主模块和与之通信的外设音时钟相位和极性应该一致。

SPI通信

1 SPI通信SPI信号线:一般的SPI接口使用4条信号线与外围设备接口,其具体功能如下:∙SCLOCK:主机的时钟线,为数据的发送和接收提供同步时钟信号。

每一位数据的传输都需要1次时钟作用,因而发送或接收1个字节的数据都需要8个时钟作用。

主机的时钟可以通过固件进行设置,并和从机的时钟线相连。

∙MISO:主机输入/从机输出数据线。

主机的MOSO应与从机的发送数据端相连,进行高位在前的数据交换。

∙SS:低电平有效的从机选择线。

当该线置低时,才能跟从机进行通信。

SPI工作模式:SPI的工作模式分为:主模式和从模式。

∙主模式的特点是不论发送还是接收始终有SCLOCK信号,SS信号不是必需的,由于SPI只能有一个主机,因而不存在主机的选择问题。

∙从模式的特点是无论发送还是接收必须在时钟信号SCLOCK的作用下才能进行,并且SS信号必须有效。

不论是在主模式下还是在从模式下,都要在时钟极性和时钟相位的配合下才能有效的完成一次数据传输。

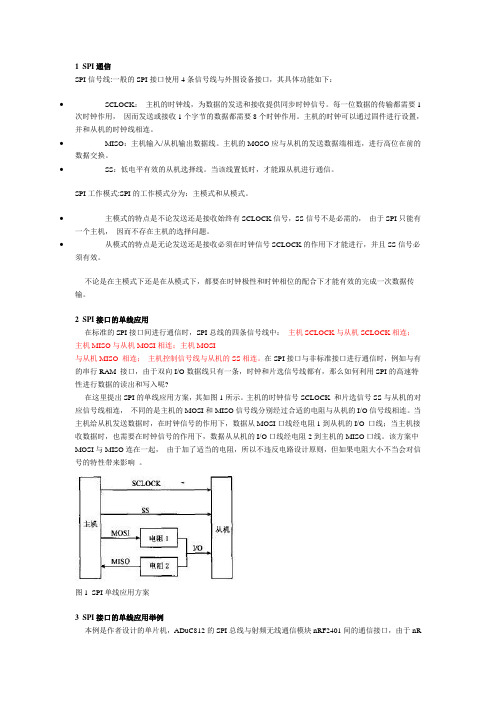

2 SPI接口的单线应用在标准的SPI接口间进行通信时,SPI总线的四条信号线中:主机SCLOCK与从机SCLOCK相连;主机MISO与从机MOSI相连;主机MOSI与从机MISO 相连;主机控制信号线与从机的SS相连。

在SPI接口与非标准接口进行通信时,例如与有的串行RAM 接口,由于双向I/O数据线只有一条,时钟和片选信号线都有,那么如何利用SPI的高速特性进行数据的读出和写入呢?在这里提出SPI的单线应用方案,其如图1所示。

主机的时钟信号SCLOCK 和片选信号SS与从机的对应信号线相连,不同的是主机的MOSI和MISO信号线分别经过合适的电阻与从机的I/O信号线相连。

当主机给从机发送数据时,在时钟信号的作用下,数据从MOSI口线经电阻1到从机的I/O 口线;当主机接收数据时,也需要在时钟信号的作用下,数据从从机的I/O口线经电阻2到主机的MISO口线。

该方案中MOSI与MISO连在一起,由于加了适当的电阻,所以不违反电路设计原则,但如果电阻大小不当会对信号的特性带来影响。

SPI接口详细讲解

四 SPI串行外设接口举例

• SPI串行数据传输结构由MISO、MOSI、SCLK、/SS构成, 主要是在SCLK的控制下,两个双向移位寄存器进行数据 交换。 • CPOL(时钟极性)=0; • 上升沿发送、下降沿接收、高位先发送。 • 上升沿到来的时候,MOSI上的电平将被发送到从设备 的寄存器中。 • 下降沿到来的时候,MISO上的电平将被接收到主设备 的寄存器中。 • 假设主机和从机初始化就绪:并且主机的sbuf=0xaa (10101010),从机的sbuf=0x55 (01010101),下面将分步 对SPI的8个时钟周期的数据情况演示一遍(假设上升沿发 送数据)。Sbuf(串行接收和发射缓冲器)

脉冲 0 1↑

主机sbuff 10101010 0101010X

从机sbuff 01010101 1010101X

MISO 0 0

MOSI 0 1

1↓

2↑ 2↓ 3↑ 3↓ 4↑ 4↓ 5↑ 5↓ 6↑ 6↓

01010100

1010100X 10101001 0101001X 01010010 1010010X 10100101 0100101X 01001010 1001010X 10010101

00101010 0101010X

1101010X

11010101 1010101X

0

0 1

1

1 0

五SPI时序图分析

(1)CPOL=0, SCLK为低时总线空闲: • CPHA=0 数据在SCLK的上升沿(rising edge)被读取;数据在下降沿(f alling edge)写入;

• CPHA=1 数据在SCLK的下降沿(falling edge)被读取;数据在上升沿(r ising edge)写入;

SPI接口——精选推荐

SPI接⼝串⾏外设接⼝(Serial Peripheral Interface)是⼀种同步外设接⼝,它可以使单⽚机与各种外围设备以串⾏⽅式进⾏通信以交换信息。

SPI最早是Motorola公司提出的全双⼯三线同步串⾏外围接⼝,采⽤主从模式(Master—Slave)架构,⽀持⼀个或多个Slave设备,由于其简单实⽤、性能优异,因此许多⼚家的设备都⽀持该接⼝,⼴泛应⽤于单⽚机和外设模块之间的连接。

SPI接⼝只需4条线:串⾏时钟线(SCK)、主机输⼊/从机输出数据线(MISO)、主机输出/从机输⼈数据线(MOSI)和低电平有效的从机选择线(SS)。

(1)MISO:主设备输⼊/从设备输出引脚。

该引脚在从模式下发送数据,在主模式下接收数据。

(2)MOSI:主设备输出/从设备输⼊引脚。

该引脚在主模式下发送数据,在从模式下接收数据。

(3)SCK:串⼝时钟,作为主设备的输出,从设备的输⼊。

(4)SS:从设备选择。

这是⼀个可选的引脚,⽤来选择主/从设备。

它的功能是⽤来作为⽚选引脚,让主设备可以单独地与特定从设备通信,避免数据线上的冲突。

SPI是⼀个环形总线结构,MOSI引脚相互连接,MISO引脚相互连接,数据在主和从之间串⾏地传输(MSB位在前),具体如下图所⽰。

SPI有主从两种⼯作模式,在主模式下,SPI为其他节点的CLK引脚提供串⾏时钟,数据从MOSI引脚输出,从MISO引脚输⼊。

在从模式下,数据从MISO引脚移出并由MOSI引脚移⼊,CLK引脚作为串⾏移位时钟的输⼊。

LPC824⽚内设计有SPI接⼝,具体的引脚取决于开关矩阵SWM的配置。

LPC824的SPI接⼝具有以下特点:•直接⽀持1⾄16位的数据发送。

软件⽀持更⼤的帧。

•主机和从机操作。

•⽆需读取输⼊数据即可将数据发送⾄从机,这在设置SPI存储器的时候很有⽤。

•控制信息还可与数据⼀同写⼊,这样便实现了极为丰富的操作,包括任意长度的帧。

•最多4个从机选择输⼊/输出,极性可选且使⽤灵活。

spi工作原理

spi工作原理SPI(Serial Peripheral Interface)是一种全双工、同步、串行通信总线,它在数字系统中得到了广泛的应用。

SPI接口是一种主从式接口,通常由一个主设备和一个或多个从设备组成。

在SPI接口中,主设备负责产生时钟信号和控制信号,而从设备则根据主设备的指令进行数据传输。

SPI接口的工作原理主要包括四个方面,时钟信号、数据传输、控制信号和传输模式。

首先,SPI接口采用的是同步通信方式,主设备产生的时钟信号会驱动数据的传输,从而保证了数据的同步性。

其次,SPI接口的数据传输是通过主设备和从设备之间的数据线进行的,数据的传输是双向的,主设备和从设备可以同时发送和接收数据。

这种双向传输的方式使得SPI接口在数据传输速度方面具有较大的优势。

再者,SPI接口通过控制信号来实现数据的传输和接收,主设备通过控制信号来选择从设备并控制数据的传输。

最后,SPI接口的传输模式有四种,分别是模式0、模式1、模式2和模式3,不同的传输模式会影响时钟信号和数据传输的相位和极性。

SPI接口的工作原理可以简单概括为以下几个步骤,首先,主设备产生一定频率的时钟信号,从设备根据时钟信号进行数据传输。

然后,主设备通过控制信号选择从设备,并将数据发送给从设备。

接着,从设备接收数据并进行处理,然后将处理后的数据发送给主设备。

最后,主设备接收从设备发送的数据,并进行相应的处理。

总的来说,SPI接口的工作原理主要包括时钟信号、数据传输、控制信号和传输模式四个方面。

SPI接口通过同步、双向、控制信号和传输模式的方式实现了主设备和从设备之间的高速数据传输,广泛应用于数字系统中。

SPI接口的工作原理清晰明了,为数字系统的设计和应用提供了重要的技术支持。

SPI的项目接口说明

极性1

SCK (CPOL = 1)

从机选择

SSEL

时钟相位 为0

时钟前沿 数据采样 时钟后沿 数据输出

CPHA = 0 Cycle # CPHA = 0 MOSI (CPHA = 0) MISO (CPHA = 0)

时钟相位为 1

时钟前沿数 据输出 时钟后沿数 据采样

CPHA = 1 Cycle # CPHA = 1 MOSI (CPHA = 1) MISO (CPHA = 1)

SPI寄存器描述——SPI模式寄存器

PCS: 外设片选;该域仅适用于固定外设选择有效(PS = 0)。

若PCSDEC = 0:PCS = xxx0

NPCS[3:0] = 1110;

PCS = xx01

NPCS[3:0] = 1101;

PCS = x011

NPCS[3:0] = 1011;

PCS = 0111

根据学习、总结,形成一个较完备的多路中间件SPI总线设备的驱动框架结 构:实现要求:A方便后续SPI设备扩展;B方便实时、高速、大容量数据 流的读写;C存在数据信息的容错处理机制,避免数据错误的产生等。

多线程处理机制,处理方法如何实现,(本处所指spi驱动,并不一定是 FLASH存储器件,如可以是A/D、液晶、无线处理单元、gps模块等)如液 晶显示初始化、同时大批量开关量数据流需要向FLASH中存储数据时,处 理机制是怎样的………………

SPI寄存器描述——SPI状态寄存器

OVRES: 溢出错误状态 0 = 上次读SPI_SR 后未检测到溢出错误。 1 = 上次读SPI_SR 后出现溢出错误。 上次读SPI_RDR 后当SPI_RDR 至少两次载入串行器,出溢出错误。

ENDRX: RX 缓冲结束 0 = 上次写SPI_RCR 或SPI_RNCR 后接收计数寄存器仍未达到0。 1 = 上次写SPI_RCR 或SPI_RNCR 后接收计数寄存器已达到0。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SPI 串行外设接口总线,最早由Motorola提出,出现在其M68系列单片机中,由于其简单实用,又不牵涉到专利问题,因此许多厂家的设备都支持该接口,广泛应用于外设控制领域。

SPI接口是一种事实标准,并没有标准协议,大部分厂家都是参照Motorola的SPI接口定义来设计的。

但正因为没有确切的版本协议,不同家产品的SPI接口在技术上存在一定的差别,容易引起歧义,有的甚至无法直接互连(需要软件进行必要的修改)。

虽然SPI接口的内容非常简单,但本文仍将就其中的一些容易忽视的问题进行讨论。

SPI ( Serial Peripheral Interface )

SPI接口是Motorola 首先提出的全双工三线同步串行外围接口,采用主从模式(Master Slave)架构;支持多slave模式应用,一般仅支持单Master。

时钟由Master控制,在时钟移位脉冲下,数据按位传输,高位在前,低位在后(MSB first);SPI 接口有2根单向数据线,为全双工通信,目前应用中的数据速率可达几Mbps的水平。

SPI接口信号线

SPI接口共有4根信号线,分别是:设备选择线、时钟线、串行输出数据线、串行输入数据线。

设备选择线SS-(Slave select,或CS-)

SS-线用于选择激活某Slave设备,低有效,由Master驱动输出。

只有当SS-信号线为低电平时,对应Slave设备的SPI接口才处于工作状态。

SCLK:同步时钟信号线,

SCLK用来同步主从设备的数据传输,由Master驱动输出,Slave设备按SCK的步调接收或发送数据。

串行数据线:

SPI接口数据线是单向的,共有两根数据线,分别承担Master到Slave、Slave到Master的数据传输;但是不同厂家的数据线命名有差别。

Motorola的经典命名是MOSI和MISO,这是站在信号线的角度来命名的。

MOSI:When master, out line; when slave, in line

MISO:When master, in line; when slave, out line

比如MOSI,该线上数据一定是Master流向Slave的。

因此在电路板上,Master的MOSI引脚应与Slave的MOSI引脚连接在一起。

双方的MISO也应该连在一起,而不是一方的MOSI连接另一方的MISO。

不过,也有一些产家(比如Microchip)是按照类似SDI,SDO的方式来命名,这是站在器件的角度根据数据流向来定义的。

SDI:串行数据输入

SDO:串行数据输出

这种情况下,当Master与Slave连接时,就应该用一方的SDO连接另一个方的SDI。

由于SPI接口数据线是单向的,故电路设计时,数据线连接一定要正确,必然是一方的输出连接另一方的输入。

其实这个问题本来很简单的,但由于不同厂家产品的命名习惯可能不同,因此还需小心,以免低级出错。

数据传输的时序模式

为了适用不同产品接口应用需要,SPI接口定义了多种时序传输模式,并可通过设置接口单元寄存器中的相关控制位来选择。

在Motorola的产品中,时序即是由两个控制位(极性控制、相位控制)来控制的。

时钟极性选择位CPOL:

在设备被使能激活后,还未进行数据传输时或两个字节数据传输间歇期间(见图3中的○1与○2处),SCLK处于空闲(Idle)电平,通过"CPOL空闲状态极性控制位"可以选择此空闲电平电平是0还是1。

时钟相位选择位CPHA:

该控 制位用来选择数据接收端设备的采样时刻。

可能在Idle to Active的跳变沿(见图3中的红色圈处),也可能在Active to Idle的跳变沿(见图3中的蓝色圈处)。

在该采样时刻,线上数据必须已经稳定可靠,因此数据发送端设备应提前将数据移出到数据线上。

为了降低设计难度, 大部分接口电路都是用同一时钟周期中前一个时钟沿(即相反时钟变化方向)将数据移出。

SPI线上的Master,Slave设备必须根据具体情况设置匹配的传输时序模式,时序只有匹配,数据传输才能正常进行。

如果设置的不匹配,可能导致数据接收方和发送方在同一时钟沿作用,导致数据传输失败。

我们以手机设计中非常流行的触摸屏控制器TSC2046为例,介绍SPI接口的实际应用。

由于TSC2046采样触摸屏信息并量化出最高位需要一定时间,而SPI总线没有握手机制,为避免Master过早的启动传输,接收无效数据,TSC2046引入了BUSY信号作为TSC2046向Master的指示。

TSC2046 是在时钟的第一个Idle to Active沿采集数据(下图1处),而在第一个(下一字节)Active to Idle 沿开始移出数据(下图2处),这导致Master只能在第二个dle to Active沿采集到

的数据才是有效的(下图3处),而在第一个Idle to Active沿(下图1处)采集的数据是无效的,因此在软件中需要将该Bit丢弃。

可见,必须根据Master与Slave的实际时序进行匹配,软件也需要进行对应的调整,才能保证数据传输的正常进行。

多Slave的应用

SPI 也支持多Slave应用。

多个Slave共享时钟线、数据线,可以直接并接在一起;而各Slave的片选线SS则单独与Master连接,受Master 控制。

在一段时间内,Master只能通过某根SS线激活一个Slave,进行数据传输,而此时其他Slave的时钟线和数据线端口则都应保持高阻状态, 以免影响当前数据传输的进行。

SPI Vs I2C

SPI协议没有定义寻址机制,需通过外部SS信号线选择设备,当出现多slave应用时,需要多根SS信号线,实施起来较I2C要复杂。

此外,SPI总线不支持总线控制权仲裁,故只能用在单Master的场合;而I2C可以支持多Master的应用。

SPI 协议相对I2C要简单,没有握手机制,数据传输效率高,速率也更快,通常应用中可达几Mbps;此外SPI是全双工通信,可同时发送和接收数据,因此, SPI比较适合用于数据传输的场合。

比如需要较大批量数据传输的场合(比如MMC/SD卡的数据传输就支持SPI模式),或者无需寻址传输的场合。

而I2C协议功能较丰富,但也相对复杂,多用在传输一些控制命令字等有意义数据的场合。

比如TSC2046只有一个控制寄存器(一个8bit的命令字),使用SPI接口即可控制,因为无需寻址。

而OV的Cmos Sensor内有多个控制寄存器,此时就必须使用I2C接口才能实现寻址控制(哦,确切的是SCCB,一个很像I2C的东东)。

SPI接口属于一种非常基本的外设接口,但是应用却很广泛。

SPI也有所发展,比兔NS推出的SPI 的精简接口Microwire,满足通常外设的扩展需求。

Motorola还推出了扩展功能的QSPI(Queued SPI)接口,应用更为广泛。