CORTEX-M4知识点总结

CortexM4内核及DSP指令

An introduction of the Cortex-M4 An introduction of some DSP instructions

Content

An introduction to the Cortex-M4 Core And introduction to some of the DSP instructions

Thumb-2 Technology DSP and SIMD extensions Single cycle MAC (Up to 32 x 32 + 64 -> 64) Optional single precision FPU Integrated configurable NVIC Compatible with Cortex-M3

5

Different Instruction Set

Cortex M0/M1

•A subset of the Cortex-M3 instructions

Cortex M3

•16 and 32 bits instructions •mixed in the same flow (Thumb2)

Cortex M4

Single-cycle SIMD instructions

Stands for Single Instruction Multiple Data

Allows to do simultaneously several operations with several 8-bit or 16-bit data groups

• DSP instructions • Floating point unit

CORTEX-M4知识点总结

Cortex-M4内核知识点总结余明目录Cortex-M4内核知识点总结 (1)1 ARM处理器简介 (5)2 架构 (6)2.1架构简介 (6)2.2编程模型 (6)2.3存储器系统 (9)2.4复位和复位流程 (13)3 指令集 (15)3.1 CM4指令集特点 (15)3.2 Cortex-M处理器间的指令集比较 (15)3.3 汇编指令简要介绍 (15)3.3.1 处理器内传送数据 (15)3.3.2 存储器访问指令 (16)3.3.3 算数运算 (17)3.3.4 逻辑运算 (18)3.3.5 移位 (18)3.3.6 异常相关指令 (18)4 存储器系统 (19)4.1 存储器外设 (19)4.2 Bootloader (19)4.3位段操作 (20)4.4 存储器大小端 (20)5 异常和中断 (22)5.1 中断简介 (22)5.2异常类型 (22)5.3 中断管理 (23)5.4 异常或中断屏蔽寄存器 (24)5.4.1 PRIMASK (24)5.4.2 FAULMASK (M0中无) (24)5.4.3 BASEPRI(M0中无) (24)5.5 中断状态及中断行为 (24)5.5.1 中断状态 (24)5.5.2 中断行为 (25)5.6 各Cortex-M处理器NVIC差异 (28)6 异常处理 (29)6.1 C实现的异常处理 (29)6.2 栈帧 (29)6.3 EXC_RETURN (30)6.4异常流程 (31)6.4.1 异常进入和压栈 (31)6.4.2 异常返回和出栈 (32)7 低功耗和系统控制特性 (33)7.1 低功耗模式 (33)7.1 SysTick定时器 (33)8 OS支持特性 (35)8.1 OS支持特性简介 (35)8.2 SVC和PendSV (35)8.3 实际的上下文切换 (36)1 ARM处理器简介ARM处理器的种类很多,从手机上的高端处理器芯片到面向微控制器的芯片,都有ARM的身影。

ARMCortex-M4指令列表.docx

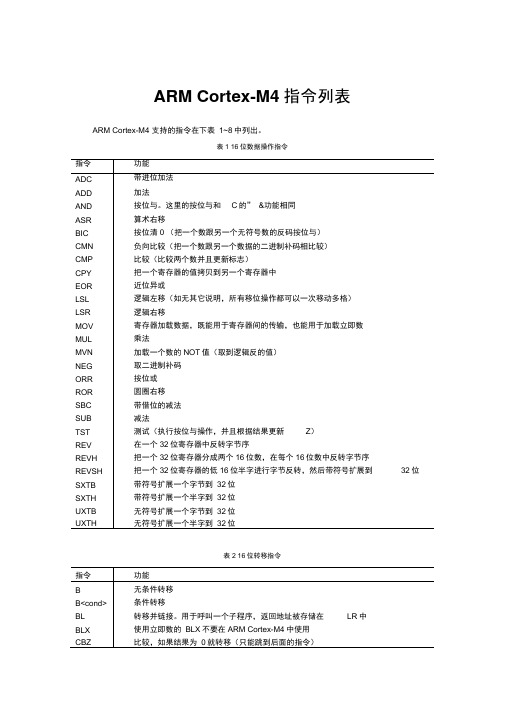

ARM Cortex-M4指令列表ARM Cortex-M4 支持的指令在下表1~8中列出。

表1 16位数据操作指令指令功能ADC带进位加法ADD加法AND按位与。

这里的按位与和C的” &功能相同ASR算术右移BIC按位清0 (把一个数跟另一个无符号数的反码按位与)CMN负向比较(把一个数跟另一个数据的二进制补码相比较)CMP比较(比较两个数并且更新标志)CPY把一个寄存器的值拷贝到另一个寄存器中EOR近位异或LSL逻辑左移(如无其它说明,所有移位操作都可以一次移动多格)LSR逻辑右移MOV寄存器加载数据,既能用于寄存器间的传输,也能用于加载立即数MUL乘法MVN加载一个数的NOT值(取到逻辑反的值)NEG取二进制补码ORR按位或ROR圆圈右移SBC带借位的减法SUB减法TST测试(执行按位与操作,并且根据结果更新Z)REV在一个32位寄存器中反转字节序REVH把一个32位寄存器分成两个16位数,在每个16位数中反转字节序REVSH把一个32位寄存器的低16位半字进行字节反转,然后带符号扩展到32位SXTB带符号扩展一个字节到32位SXTH带符号扩展一个半字到32位UXTB无符号扩展一个字节到32位UXTH无符号扩展一个半字到32位表2 16位转移指令指令功能B无条件转移B<cond>条件转移BL转移并链接。

用于呼叫一个子程序,返回地址被存储在LR中BLX使用立即数的BLX不要在ARM Cortex-M4中使用CBZ比较,如果结果为0就转移(只能跳到后面的指令)CBNZ IT 比较,如果结果非0就转移(只能跳到后面的指令)If - Then表3 16位存储器数据传送指令指令LDR LDRH LDRB LDRSH LDRSB STR STRH STRB LDMIA STMIA PUSH POP 功能从存储器中加载字到一个寄存器中从存储器中加载半字到一个寄存器中从存储器中加载字节到一个寄存器中从存储器中加载半字,再经过带符号扩展后存储一个寄存器中从存储器中加载字节,再经过带符号扩展后存储一个寄存器中把一个寄存器按字存储到存储器中把一个寄存器存器的低半字存储到存储器中把一个寄存器的低字节存储到存储器中加载多个字,并且在加载后自增基址寄存器加载多个字,并且在加载后自增基址寄存器压入多个寄存器到栈中从栈中弹出多个值到寄存器中16位数据传送指令没有任何新内容,因为它们是Thumb指令,在v4T时就已经固定下来了。

ARM Cortex-M4 支持的指令

ARM Cortex-M4 支持的指令在下表1~8 中列出。

表1 16 位数据操作指令指令功能ADC 带进位加法ADD 加法AND 按位与。

这里的按位与和C 的”&”功能相同ASR 算术右移BIC 按位清0(把一个数跟另一个无符号数的反码按位与)CMN 负向比较(把一个数跟另一个数据的二进制补码相比较)CMP 比较(比较两个数并且更新标志)CPY 把一个寄存器的值拷贝到另一个寄存器中EOR 近位异或LSL 逻辑左移(如无其它说明,所有移位操作都可以一次移动多格)LSR 逻辑右移MOV 寄存器加载数据,既能用于寄存器间的传输,也能用于加载立即数MUL 乘法MVN 加载一个数的NOT 值(取到逻辑反的值)NEG 取二进制补码ORR 按位或ROR 圆圈右移SBC 带借位的减法SUB 减法TST 测试(执行按位与操作,并且根据结果更新Z)REV 在一个32 位寄存器中反转字节序REVH 把一个32 位寄存器分成两个16 位数,在每个16 位数中反转字节序REVSH 把一个32 位寄存器的低16 位半字进行字节反转,然后带符号扩展到32 位SXTB 带符号扩展一个字节到32 位SXTH 带符号扩展一个半字到32 位UXTB 无符号扩展一个字节到32 位UXTH 无符号扩展一个半字到32 位表2 16 位转移指令指令功能B 无条件转移B<cond> 条件转移BL 转移并链接。

用于呼叫一个子程序,返回地址被存储在LR 中BLX 使用立即数的BLX 不要在ARM Cortex-M4 中使用CBZ 比较,如果结果为0 就转移(只能跳到后面的指令)CBNZ 比较,如果结果非0 就转移(只能跳到后面的指令)IT If‐Then表3 16 位存储器数据传送指令指令功能LDR 从存储器中加载字到一个寄存器中LDRH 从存储器中加载半字到一个寄存器中LDRB 从存储器中加载字节到一个寄存器中LDRSH 从存储器中加载半字,再经过带符号扩展后存储一个寄存器中LDRSB 从存储器中加载字节,再经过带符号扩展后存储一个寄存器中STR 把一个寄存器按字存储到存储器中STRH 把一个寄存器存器的低半字存储到存储器中STRB 把一个寄存器的低字节存储到存储器中LDMIA 加载多个字,并且在加载后自增基址寄存器STMIA 加载多个字,并且在加载后自增基址寄存器PUSH 压入多个寄存器到栈中POP 从栈中弹出多个值到寄存器中16 位数据传送指令没有任何新内容,因为它们是Thumb 指令,在v4T 时就已经固定下来了。

arm cortex-m4f处理器 知识点

Arm Cortex-M4F处理器知识点1. 简介Arm Cortex-M4F处理器是一种低功耗、高效能的嵌入式处理器,广泛应用于物联网设备、消费类电子产品、工业控制系统等领域。

它采用了先进的指令集架构,具有丰富的外设接口和强大的数字信号处理能力,适合处理实时控制、信号处理和通信任务。

2. 处理器架构Arm Cortex-M4F处理器采用了Harvard结构,拥有独立的指令和数据总线,可以同时取指令和访问数据,从而提高了数据访问的效率。

它具有内置的浮点运算单元(FPU),支持单精度和双精度浮点运算,适用于处理需要高精度计算的应用场景。

3. 特性Cortex-M4F处理器具有以下特性:- 高性能:最高主频可达到几百兆赫,功耗较低。

- 丰富的外设接口:支持多种外设接口,如SPI、I2C、UART等,便于与外部设备进行通信和控制。

- 低功耗设计:通过动态电压和频率调节以及睡眠模式等技术,实现了低功耗设计,适合于电池供电的应用。

- 强大的数字信号处理能力:内置的FPU可以加速浮点运算,提高信号处理和算法运算的效率。

- 软件兼容性:与其他Cortex-M系列处理器兼容,可使用标准的开发工具和软件库进行开发。

4. 应用领域Cortex-M4F处理器广泛应用于以下领域:- 物联网设备:如智能家居、智能穿戴设备、智能传感器等。

- 消费类电子产品:如智能手机、平板电脑、便携式音频设备等。

- 工业控制系统:如工业机器人、自动化生产设备、智能仪表等。

- 医疗设备:如便携式医疗诊断设备、可穿戴医疗器械等。

5. 开发工具和资源开发Cortex-M4F处理器的工具和资源包括:- 集成开发环境(IDE):如Keil、IAR、MCUxpresso等,提供了丰富的开发工具和调试功能。

- 软件库:如CMSIS(Cortex Microcontroller Software Interface Standard)、HAL库等,提供了丰富的驱动和函数库,方便开发者快速开发应用程序。

Cortex-M4特性

Cortex-M4 处理器特性简介ARM Cortex™-M4 处理器是由ARM 专门开发的最新嵌入式处理器,在M3的基础上强化了运算能力,新加了浮点、DSP、并行计算等,用以满足需要有效且易于使用的控制和信号处理功能混合的数字信号控制市场。

其高效的信号处理功能与Cortex-M 处理器系列的低功耗、低成本和易于使用的优点的组合,旨在满足专门面向电动机控制、汽车、电源管理、嵌入式音频和工业自动化市场的新兴类别的灵活解决方案。

1、高能效数字信号控制Cortex-M4 提供了无可比拟的功能,以将32 位控制与领先的数字信号处理技术集成来满足需要很高能效级别的市场。

Cortex-M4 处理器采用一个扩展的单时钟周期乘法累加(MAC) 单元、优化的单指令多数据(SIMD)指令、饱和运算指令和一个可选的单精度浮点单元(FPU)。

这些功能以表现ARM Cortex-M 系列处理器特征的创新技术为基础。

包括:a) RISC 处理器内核:高性能32 位CPU、具有确定性的运算、低延迟3 阶段管道,可达1.25DMIPS/MHz;b) Thumb-2® 指令集:16/32 位指令的最佳混合、小于8 位设备3 倍的代码大小、对性能没有负面影响。

提供最佳的代码密度;c) 低功耗模式:集成的睡眠状态支持、多电源域、基于架构的软件控制;d) 嵌套矢量中断控制器(NVIC):低延迟、低抖动中断响应、不需要汇编编程、以纯 C 语言编写的中断服务例程。

能完成出色的中断处理;e) 工具和RTOS 支持:广泛的第三方工具支持、Cortex 微控制器软件接口标准(CMSIS)、最大限度地增加软件成果重用。

f) CoreSight 调试和跟踪:JTAG 或2 针串行线调试(SWD) 连接、支持多处理器、支持实时跟踪。

此外,该处理器还提供了一个可选的内存保护单元(MPU),提供低成本的调试/追踪功能和集成的休眠状态,以增加灵活性。

Cortex-M4内存映射

与传统的ARM架构有所不同,自ARMv7以后的Cortex系列(这里只以Cortex-M为例),其内存映射结构发生了很大的变化。

首先是ARMv7-M的内存映射是大致框架预定义好的了(即其内存映射已经固定好了,哪个地址范围用使用什么总线支持什么外设等都已经在框架里规定好了的,这样带来的一个好处是方便软件在不同的ARM芯片中的移植),其次就是ARMv7-M的存储器系统支持所谓的“位带”(Bitband),可以方便实现“位”的原子操纵,还有就是支持非对

齐访问、互斥访问和大小端配置,下面就以Cortex-M4的Kinetis为例说说其内存映射的安排:

这里有个概念需要细说一下,即Write-Back和Write-through(这部分摘自ARM CM3 权威指南)。

其中写回(即

Write-Back)是指写入的数据先逗留在缓存中,待到必要的时候在落实到最终的目的地,即实现Cache的功能,利于改善数据传送的效率,减少主存储器的访问操作;而Write-through(即写通),指绕够cache,直接落实到目的存储器,写操作立即生效,常用于和片上外设或者其他处理器共享内存中,怎么样是不是想到了“volatile”这个关键字了,对了,他们两个就是对应的,即用Volatile声明的变量时放在写通区RAM里的。

STM32F4入门前的热身之一:认识stm32F4 Cortex-M4

STM32F4 入门前的热身之一:认识stm32F4 Cortex-M41 简介STM32F4 系列基于ARM® Cortex™-M4 内核,采用了90纳米的NVM 工艺和ART(自适应实时存储器加速器,Adaptive Real-Time MemoryAccelerator™)。

ART 技术使得程序零等待执行,提升了程序执行的效率,将Cortext-M4 的性能发挥到了极致。

STM32 F4 系列可达到210DMIPS@168MHz。

集成了单周器DSP 指令和FPU(floating point unit,浮点单元),提升了计算能力,可以进行一些复杂的计算和控制。

STM32 F4 系列引脚和软件兼容于当前的STM32 F2 系列产品。

技术特征超快速数据传送采用多达7 重AHB 总线矩阵和多通道DMA 控制器,支持程序执行和数据传输并行处理,数据传输速率非常快FPU(浮点单元)集成了单精度FPU,提升控制算法的执行速度和代码效率高集成度达1M 字节的片上FLASH 存储器,192K 字节的SRAM ,复位电路,内部RC,PLL,1uA 的连接性Camera 接口8 到14 位camera 接口可连接CMOS 的camera 传感器,可支持达加密/哈希硬件处理器AES 128,192,256,Triple DES, HASH (MD5, SHA-AES-256 加密能力达Ethernet MAC10/100 IEEE 1588 支持MII 和 2 个USB 音频专用的音频PLL 和2 个全双工的多达15 个通讯接口包括6 个UASRT,可运行到 3 个SPI,可运行到 3 个2 个 1 个SDIO 模拟 2 个12 位3 个12 位ADC,可达到2.4MSPS 或在交替模式中达多达17 个定时器16 位的和32 位的定时器,可运行到其他外设CRC 计算单元模拟的真正随机数发生。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cortex-M4内核知识点总结余明目录Cortex-M4内核知识点总结 (1)1 ARM处理器简介 (4)2 架构 (5)2.1架构简介 (5)2.2编程模型 (5)2.3存储器系统 (8)2.4复位和复位流程 (12)3 指令集 (14)3.1 CM4指令集特点 (14)3.2 Cortex-M处理器间的指令集比较 (14)3.3 汇编指令简要介绍 (14)3.3.1 处理器内传送数据 (14)3.3.2 存储器访问指令 (15)3.3.3 算数运算 (16)3.3.4 逻辑运算 (17)3.3.5 移位 (17)3.3.6 异常相关指令 (17)4 存储器系统 (18)4.1 存储器外设 (18)4.2 Bootloader (18)4.3位段操作 (19)4.4 存储器大小端 (19)5 异常和中断 (21)5.1 中断简介 (21)5.2异常类型 (21)5.3 中断管理 (22)5.4 异常或中断屏蔽寄存器 (23)5.4.1 PRIMASK (23)5.4.2 FAULMASK (M0中无) (23)5.4.3 BASEPRI(M0中无) (23)5.5 中断状态及中断行为 (23)5.5.1 中断状态 (23)5.5.2 中断行为 (24)5.6 各Cortex-M处理器NVIC差异 (26)6 异常处理 (28)6.1 C实现的异常处理 (28)6.2 栈帧 (28)6.3 EXC_RETURN (29)6.4异常流程 (30)6.4.1 异常进入和压栈 (30)6.4.2 异常返回和出栈 (31)7 低功耗和系统控制特性 (32)7.1 低功耗模式 (32)7.1 SysTick定时器 (32)8 OS支持特性 (34)8.1 OS支持特性简介 (34)8.2 SVC和PendSV (34)8.3 实际的上下文切换 (35)1 ARM处理器简介ARM处理器的种类很多,从手机上的高端处理器芯片到面向微控制器的芯片,都有ARM的身影。

2011年基于ARM处理器的芯片的出货量已经到达79亿。

这一章首先对ARM处理器有个简单的了解。

在早期的时候,ARM处理器使用后缀表明特性。

例如ARM7TDMI,T表示支持Thumb指令,D表示JTAG,M表示快速乘法器,I则表示嵌入式ICE模块。

近几年,ARM改变处理器的命名方式,统一使用了Cortex处理器的名称。

Cortex处理器下分为三类:·Cortex-A系列:需要处理高端嵌入式系统等复杂应用的应用处理器·Cortex-R系列:实时、高性能的处理器,面向较高端的实时市场·Cortex-M系列:面向微控制器和混合信号设计等小型应用,注重低成本、低功耗。

不同系列的处理器使用不同版本的架构在Cortex-M系列中,进一步都处理器进行了划分2 架构2.1架构简介Cortex-M3和Cortex-M4处理器都是基于ARMv7-M架构。

最初ARMv-7M 架构是随着Cortex-M3处理器一同引进的,而在Cortex-M4发布时,架构中又额外增加了新的指令和特性,改进后的架构有时也被称为ARMv7E-M。

2.2编程模型2.2.1操作模式和状态Cortex-M4处理器包括两种操作状态和模式,还有两种访问等级。

1.操作状态·调试状态:处理器被暂停后,就会进入调试状态,比如利用调试器触发断点,单步执行等。

·Thumb状态:处理器执行程序代码,它就是处在Thumb状态,因为Cortex-M4用的是Thumb指令,所以称为Thumb状态,并且在Cortex-M 处理器中已经不支持ARM指令,也就不存在ARM状态。

2.操作模式·处理模式:执行中断服务程序等异常处理。

在处理模式下,处理器总是具有特权访问等级。

·线程模式:执行普通的程序代码。

3.访问等级·特权访问等级:可以访问处理器中的所有资源。

·非特权访问等级:有些存储器区域无法访问,有些操作也无法使用。

访问等级有特殊寄存器CONTROL 控制。

软件可将处理器从特权访问等级转换至非特权访问等级,但反之无法直接转换,需要借助异常机制。

处理器的操作模式和状态可由图1.1来表示,在上电后,默认处于特权线程模式下的Thumb 状态。

2.2.2 寄存器对于ARM 架构来讲,处理存储器中的数据时,需将其从存储器加载到寄存器中,处理完毕后,若有必要,还可以再写回存储器。

这种方式被称作“加载-存储架构”(LOAD -STORE)。

Cortex -M4处理器的寄存器组中有16个寄存器,其中包括13个通用寄存器和3个有特殊用途的寄存器。

1 通用寄存器R0-R12R0-R7被称作低寄存器,许多16位指令只能访问低寄存器。

R8-R12称作高寄存器,可用32位指令和几个16位指令访问。

R0-R12初始值未定义。

2 栈指针R13R13为栈指针,可通过PUSH 和POP 操作实现栈存储的访问。

栈指针包括两个:主栈指针MSP 和进程栈指针PSP 。

MSP 为默认指针,复位后或处理模式时只能是MSP ,而PSP 只能在线程模式使用。

栈指针的选择有CONTROL 寄存器控制。

MSP 和PSP 的最低两位必须是0,也就是栈指针的地址操作必须4字节对齐。

链接寄存器程序计数器通用寄存器3 链接寄存器(LR )R14用于函数或子程序调用时返回地址的保存,在异常中则用来保存进异常前状态信息,包括系统模式、栈指针模式等。

异常返回时参考LR中的信息返回到相应状态。

4 程序计数器(PC)R15R15为程序计数器,读操作返回当前地址加4,写操作引起跳转。

2.2.3 特殊寄存器特殊寄存器有三类:程序状态寄存器、中断/异常屏蔽寄存器、处理器控制寄存器。

1 程序状态寄存器:应用PSR(APSR)、执行PSR(EPSR)、中断PSR(IPSR)。

三个寄存器可以单独访问,也可以组合到一个寄存器中访问。

在APSR中包含N(负标志)、Z(零标志)、C(进位标志)、V(溢出标志)、Q(饱和标志)和GE(大于或等于标志,只在M4中有)。

IPSR中是中断号,只读。

EPSR中,T为表示Thumb状态,由于M4支持Thumb状态,不支持ARM状态,T位始终为1。

ICI是中断继续指令位,保存的是中断被打断时的信息。

IT指令时IF-THEN指令,用于条件执行。

2 PRIMASK、FAULTMASK、和BASEPRI寄存器:这三个寄存器只能在特权模式下使用。

PRIMASK可屏蔽除NMI和HardFault之外的所有异常。

FAULTMASK还可屏蔽HardFault。

BASEPRI可以根据设置屏蔽低优先级的中断,可控制8个或16个中断,相应的改寄存器的宽度为3位或4位。

3 CONTROL寄存器CONTROL寄存器主要有以下几项作用:·线程模式下的访问等级·指针的选择·当前代码是否使用了浮点单元分别对应了寄存器的低三位2.2.4 浮点寄存器1 S0-S31和D0-D15S0-S31都为32位寄存器,也可以D0-D15的方式成对访问,但M4不支持双精度浮点运算,只是可以传输双精度数据。

2 浮点状态和控制寄存器(FPSCR)FPSCR两个功能·提供浮点运算结果的状态信息,如负标志、进位标志等。

·定义一些浮点运算动作,如何舍入等3 经过存储器映射的浮点单元控制寄存器(CPACR)该寄存器经过了映射,也就是说需要通过通用寄存器加载进行设置,寄存器的功能是可以设置浮点单元的访问权限,拒绝访问、特权访问,全访问。

2.3存储器系统2.3.1 存储器系统特性·4GB线性地址空间·架构定义的存储器映射。

4GB的存储器空间被划分为多个区域,用于预定义的存储器和外设。

·支持大端和小端的存储器系统。

·位段访问。

·写缓冲·存储器保护单元MPU·非对齐传输支持2.3.2 存储器映射CORTEX-M处理器的4GB地址空间被分为了多个存储器区域,如图所示。

区域根据各自典型用法进行划分,他们主要用于:·程序代码访问(如CODE区域)·数据访问(如SRAM区域)·外设(如外设区域)某款芯片的存储器映射分配0x5000_00000x5010_00000x5020_00000x5021_00000x5022_00000x5050_00000x5060_00000x5070_00000x5071_00000x5090_00000x50B0_00000x50C0_00000x50D0_00000x50F0_00000x5030_00000x5023_00000x5072_00000x5061_00000x5062_00000x5073_00000x5040_0000 一般Code 放在Flash 当中,数据放在RAM 中。

数据在RAM 存放有一定的顺序,可以分为数据段,BSS 段、堆和栈区域。

· 数据段,存储在内存的底部,包含初始化的全局变量和静态变量。

·BSS段,未初始化的数据。

·堆,C函数自动分配存储器区域,例如alloc()和malloc()。

·栈,用于临时数据存储,局部变量,函数调用2.3.3 栈存储同几乎所有的处理器架构一样,Cortex-M处理器在运行时需要栈存储和栈指针R13。

ARM处理器将系统主存储器用于栈空间操作,使用PUSH指令往栈中存储数据以及POP指令从栈中提取数据。

处理器使用的是满递减的模型,栈指针是向下增长的。

处理器启动后,SP 被设置为栈存储空间的最后的位置,也就是最低位置,PUSH时,SP指针首先减小,然后将数据压入栈中。

POP的时候相反,先将当前SP所指的数据出栈,然后再修改SP,SP此时增大。

可用下面两幅图加以理解,栈中主要用于:· 存储局部变量· 异常产生时保存处理器状态(LR 、xPSR )和寄存器数值 · 函数调用时2.4复位和复位流程对于典型的Cortex -M 处理器,复位类型有三种:· 上电复位。

复位微控制器中所有部分。

· 系统复位。

只会复位处理器和外设,不包括处理的调试支持部件 · 处理器复位。

只复位处理器。

在复位后以及处理器开始执行程序前,处理器会从存储器中读出头两个字节。

第一个字表示主栈指针的初始值。

第二个字代表复位处理起始地址的复位向量。

处理器读出这两个自己后,就会将这些数值赋给MSP 和PC 。

读地址0x00000000读地址0x00000004读取复位向量表示的地址时间之前在栈存储时讲到过,Cortex -M 处理器的栈操作时基于满递减的,所以S P 的初始值应该设置在栈顶的位置。