化学气相淀积全解

描述化学气相淀积的原理

描述化学气相淀积的原理今天来聊聊化学气相淀积的原理。

你知道吗,这就像是一场在微观世界里悄悄进行的“建筑工程”。

我先从生活中的一个小现象说起吧。

你看到过家里的水壶底部有水垢吧?其实这水垢就是某些物质慢慢从液体里面跑出来,然后在水壶底部沉积起来的。

化学气相淀积呢,也有点这个意思,但更加复杂神奇。

想象一下,在一个充满各种气体的小空间里,就好像是一个特殊的“小社会”。

这里面的气体分子就是各种“小工匠”和“原材料”。

这些气体分子在高温、等离子体或者光等能量条件的激励下,就像是被下达了指令的小工匠一样,开始变得活跃起来。

开始的时候,这些气体分子各自游离在这个小空间里。

然后某一刻,它们开始发生化学反应,这个过程就好比一些游手好闲的人,突然找到了目标开始合作做事情。

在这个过程中,会生成一些分子,而这些分子很特别,它们在这种环境下不会像其他气体分子一样乱跑,而是慢慢在一个基底表面“安家落户”,一层一层地堆积起来,就像工匠们用砖块依次砌墙一样。

这些生成的分子就像是专门设计好的“魔法砖块”,它们凭借化学键或者其他相互作用,牢牢地结合在基底上,从而逐渐形成薄膜或者固体材料,这个过程就叫做化学气相淀积。

说到这里,你可能会问,这些气体分子怎么就知道要变成能在基底安家的分子呢?老实说,我一开始也不明白,后来随着学习才发现,这取决于我们投入的气体原料和反应条件,这些设定好了整个反应的大框架。

比如,如果我们想要在一块半导体基底上淀积一层氧化硅薄膜,我们就可以选择合适的硅源气体和氧气混合,在特定的温度和压力下让它们反应,硅源气体和氧气反应生成的二氧化硅分子就会沉积在半导体基底上。

我们再打个更通俗的比方,这就好比做蛋糕。

如果要做一个有草莓夹心的蛋糕(代表一种特殊功能的淀积层),我们就得有鸡蛋、面粉等基本原料(各种气源),还得有合适的烤箱温度和烘焙时间(反应条件)。

不同的原料和烘焙条件就会做出完全不同的蛋糕。

在实际应用中,化学气相淀积的例子太多了。

第06章化学气相淀积

当气体反应剂被消耗而出现的反应剂浓度改变的现象 措施:

在水平方向上逐渐提高温度来加快反应速度,从而提高了淀积 速率

采用分布式的气体入口 增加反应室中的气流速度

常压CVD:一个大气压,101Kpa.

1000℃

低压CVD :100Pa左右

C 高温CVD(HT~):1000----

1300℃

按反应器形状分

等离子体增强CVD:既是低温 100~400℃,又是低压(与LPCVD同)

立式,(又可细分为钟罩式和桶式);

B.卧式。

第25页,共76页。

§6.2 化学气相淀积系统

膜中所有的材料物质都源于外部的源。 化学气相淀积工艺中的反应物必须以气相形式参加反应。

第2页,共76页。

引言

三. CVD工艺优点

设备简单,重复性好。

淀积速率一般高于PVD,效率高。 薄膜的成分精确可控、配比范围大。

淀积膜结构完整、致密,良好的台阶覆盖能力,且与衬底粘附性好。 厚度范围广,由几百埃至数毫米,可以实现厚膜淀积,且能大量生产。

Ea kT

0

低温时,表面化学反应较慢, 反应剂到达表面的速率(数量) 超过了表面化学反应对反应剂 的消耗速率(数量),G由ks控 制。

第15页,共76页。

§6.1 CVD模型

b) 高温时,G由质量输运速率控 制

∵T↑→ks↑ ∴输运到表面的反应剂数量低

于该温度下表面化学反应所需 的数量,则G转为由hg控制, G基本上不随温度变化。

CVD成膜温度远低于体材料的熔点。因此减轻了衬底片的热形变,抑制了缺陷生成。 CVD方法几乎可以淀积集成电路工艺中所需要的各种薄膜,例如掺杂或不掺杂的

SiO2、多晶硅、非晶硅、氮化硅、金属(钨、钼)等。

化学气相淀积

❖ 电阻直接加热(热壁式和冷壁式) ❖ 电感加热或高能辐射灯加热(多为冷壁式)

常用的几种CVD系统

APCVD系统(Atmospheric Pressure CVD)

❖ 操作简单;较高的淀积速率;适于介质薄膜淀积; ❖ 易发生气相反应,产生颗粒污染;台阶覆盖性和均匀性较差;一

般是质量输运控制,需精确控制各处的反应剂浓度均匀; ❖ 水平式反应系统;连续式淀积系统。

LPCVD系统(Low Pressure CVD)

❖ 污染小;均匀性和台阶覆盖性较好;一般是表面反应控制,精确控 制温度比较容易;

❖ 气缺现象;较低的淀积速率;较高的淀积温度; ❖ 立式淀积系统;管式淀积系统。

PECVD系统(Plasma Enhanced CVD)

❖ 相对最低的淀积温度,最高的淀积速率;淀积的薄膜具 有良好的附着性、低针孔密度、良好的阶梯覆盖、良好 的电学特性、可以与精细图形转移工艺兼容;

X=0

X=L

U

y

? (x) x

dx

L

Grove模型

❖ F1=hg(Cg-Cs) ❖ F2=ksCs ❖ Cs=Cg/(1+ks/hg)

G F kshg Cg N1 ks hg N1

气体

薄膜

Cg Cs

❖ Ks<< hg时,表面反应控制: G= (Cg ks ) /N1

hg << Ks时,质量输运控制: G= (Cg hg ) /N1

§6.2 化学气相淀积系统

CVD系统通常包括: ❖ 气态源或液态源 ❖气体输入管道 ❖气体流量控制 ❖反应室 ❖ 基座加热及控制系统(其他激活方式) ❖ 温度控制及测量系统 ❖ 减压系统(可选)

CVD的气体源

化学气相沉积

集成电路芯片工艺化学气相沉积(CVD)化学汽相淀积(CVD)化学汽相淀积是指通过气态物质的化学反应在衬底上淀积一层薄膜材料的过程。

CVD膜的结构可以是单晶、多晶或非晶态,淀积单晶硅薄膜的CVD过程通常被称为外延。

CVD技术具有淀积温度低、薄膜成分和厚度易于控制、均匀性和重复性好、台阶覆盖优良、适用范围广、设备简单等一系列优点。

利用CVD方这几乎可以淀积集成电路工艺中所需要的各种薄膜,例如掺杂或不掺杂的SiO:、多晶硅、非晶硅、氮化硅、金属(钨、钼)等。

一:化学气相沉积方法常用的CVD方法主要有三种:常压化学汽相淀积(APCVD)、低压化学汽相淀积(LPCVIi~)和等离子增强化学汽相淀积(PECVD).APCVD反应器的结构与氧化炉类似,如图1-1所示,该系统中的压强约为一个大气压,因此被称为常压CVD。

气相外延单晶硅所采用的方法就是APCVD。

图1-1APCVD反应器的结构示意图,LPCVD反应器的结构如图1-2所示,石英管采用三温区管状炉加热,气体由一端引入,另一端抽出,半导体晶片垂直插在石英舟上。

由于石英管壁靠近炉管,温度很高,因此也称它为热壁CVD装置,这与利用射频加热的冷壁反应器如卧式外延炉不同.这种反应器的最大特点就是薄膜厚度的均匀性非常好、装片量大,一炉可以加工几百片,但淀积速度较慢.它与APCVD的最大区别是压强由原来的1X10SPa降低到1X102Pa左右。

图1-2LPCVD反应器的结构示意图图1-3平行板型PECVD反应器的结构示意图PECVD是一种能量增强的CVD方法,这是因为在通常CVD系统中热能的基础上又增加了等离子体的能量.图1-3给出了平行板型等离子体增强CVD反应器,反应室由两块平行的金属电极板组成,射频电压施加在上电极上,下电极接地。

射频电压使平板电极之间的气体发生等离子放电。

工作气体由位于下电极附近的进气口进入,并流过放电区。

半导体片放在下电极上,并被加热到100—400;C左右.这种反应器的最大优点是淀积温度低。

第六章化学气相淀积

6.1.3 Grove模型

.

6.1 CVD模型

? 6.1.3 Grove 模型

①假定边界层中反应剂的浓度梯度为线性近似,则

流密度为: F1=h g(Cg-Cs)

hg-气相质量转移系数, Cg-主气流中反应剂浓度, CS-衬底表面处反应剂浓度;

②表面的化学反应淀积薄膜的速率正比于 Cs,则 流密度为: F2=ksCs

第六章 化学气相淀积

主 讲:毛 维

mwxidian@ 西安电子科技大. 学微电子学院

概述

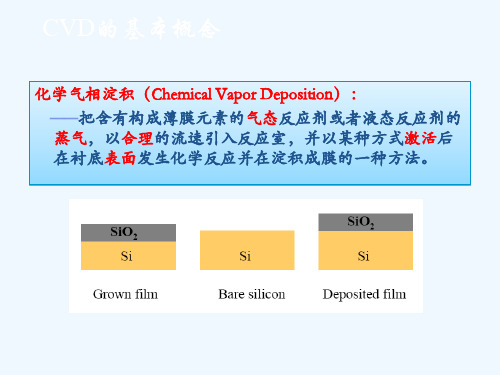

? 化学气相淀积:CVD——Chemical Vapour Deposition 。 ? 定义:一种或数种物质的气体,以某种方式激活后,在衬

底发生化学反应,并淀积出所需固体薄膜的生长技术2H2(g) ,

②掩蔽膜:用于选择性氧化;

③DRAM 电容的绝缘材料;

④MOSFETs 中的侧墙;

⑤浅沟隔离的CMP 停止层。 ? Si3N4薄膜的特性: ①扩散掩蔽能力强,尤其对钠、水汽、氧;

②对底层金属可保形覆盖;

可作为钝化层的原因

③针孔少;压应力可以很低(PECVD) ;

④介电常数较大:(εSi3N4=6-9,εSiO2 =4.2. ) ,不能作层间的绝缘层。

? 硅烷和N2O(NO) :PECVD 淀积机理 : SiH 4+N2O 200-400℃ SiO2+N2+H2O

? 原位掺P:形成PSG

淀积机理 : PH 3(g)+5O 2=2P2O5(固)+6H 2 优点: 温度低;反应机理简单。

缺点: 台阶覆盖差。

.

6.4 CVD二氧化硅

②液态TEOS 源:PECVD ? 淀积机理: Si(OC 2H5)4+O 2 250-425℃ SiO 2+H2O+C XHY ? 优点:安全、方便;厚度均匀;台阶覆盖好。 ? 缺点:SiO 2膜质量较热生长法差;

5化学气相淀积

化学气相淀积教学目的:1 了解化学气相淀积概念2 了解化学气相淀积系统和方法3 了解外延的概念和生成方法4 掌握CVD质量检测教学重点:化学气相淀积系统和方法、外延的概念和生成方法、CVD质量检测教学难点:外延的概念教学过程:5.1引言5.1.1 薄膜淀积的概念所谓薄膜,是指一种在硅衬底上生长的薄固体物质。

薄膜与硅片表面紧密结合,在硅片加工中,通常描述薄膜厚度的单位是纳米(nm)。

半导体制造中的薄膜淀积是指在硅片衬底上增加一层均匀薄膜的工艺。

在硅片衬底上淀积薄膜有多种技术,主要的淀积技术有化学气相淀积(CVD)和物理气相淀积(PVD),其他的淀积技术有电镀法、旋涂法和分子束外延法。

化学气相淀积(CVD)是通过混合气体的化学反应生成固体反应物并使其淀积在硅片表面形成薄膜的工艺。

而物理气相淀积(PVD)是不需通过化学反应,直接把现有的固体材料转移至硅片表面形成薄膜的工艺。

电镀法是制备铜薄膜时主要采用的淀积技术。

旋涂法采用的设备是标准的旋转涂胶机,比CVD工艺更经济,通常用于制备低k(k 指介电常数)绝缘介质膜。

分子束外延法是一种制备硅外延层的较先进的淀积技术。

5.1.2 常用的薄膜材料在半导体制造中所包含的薄膜材料种类很多,早期的芯片大约含有数十种,而随着集成电路结构和性能的发展,芯片中薄膜材料种类也越来越多,如图5⁃1所示,这些薄膜材料在器件中都起到了非常重要的作用。

总的来说,薄膜材料的种类可分为金属薄膜层、绝缘薄膜层和半导体薄膜层三种。

早期和现代MOS结构中的各层薄膜1) 金属薄膜层在半导体制造中的应用主要是制备金属互连线。

2) 常见的绝缘薄膜材料有二氧化硅(SiO2)、掺杂二氧化硅(如PSG、BPSG)、氮化硅(Si3N4)等。

3) 半导体薄膜材料主要有多晶硅、外延硅层等。

5.1.3 半导体制造中对薄膜的要求在图5⁃1中给出了制作一个早期NMOS管所需的淀积层。

图中器件的特征尺寸远大于。

由于特征高度的变化,硅片上的各层薄膜并不平坦,质量不高。

化学气相沉积简介

• CVD Process Overview • PECVD Process Overview • PECVD Process Recipe And Clean Recipe Overview • PECVD Equipment Overview

CVD Process Overview

CVD Process Overview

PECVD中plasma的特点:

➢ Plasma组分:包括电子、离子、未电离的中性粒子,电离度小于0.01;属 于低温plasma(非平衡态的等离子体),电子温度(104K)>>粒子体温度 (300~500K);

➢ Plasma中的碰撞(collision)过程: 1)弹性碰撞(elastic collision):没有能量交换的碰撞,它是plasma 中最频繁发生的,但也是没有重要意义的碰撞; 2)非弹性碰撞(inelastic collision):发生能量交换的,有新的成分 产生的碰撞,其中三个比较重要: ➢ 离子化(Ionization) e-+A(atom\molecule)->A++2e➢ 激发与跃迁(excitation-relaxation) e-+A(atom\molecule)->A*+eA*->A+hv(photons) ➢ 离解(dissociation) e-+AB->A+B+e-

稳定性; 缺点:设备比较复杂,需要TEOS传输系统;厚膜下容易发生discolor;

wafer整体range较大;

P1E)CVDOxPirdoec(essPOEvesrivlieawne oxide and PE TEOS oxide

化学气相淀积--基本概念

化学气相淀积的基本概念薄膜制备-化学气相淀积薄膜淀积种类:导体、半导体、绝缘体物理气相淀积PVD)薄膜淀积:化学气相淀积CVD)化学气相淀积的含义化学气相淀积,简称CVD,它是通过气体混合的化学反应的方式在硅片表面淀积一层固体薄膜的工艺。

化学气相淀积的基本原理1)参加反应的气体混合物被输运到沉积区2)反应物由主气流扩散到衬底表面3)反应物分子吸附在衬底表面上4)吸附物分子间或吸附分子与气体分子间发生化学反应,生成原子和化学反应副产物,原子沿衬底表面迁移并形成薄膜5)反应副产物分子从衬底表面解吸,扩散到主气流中,排出沉积区(a)形成晶核:(b)晶粒聚集:(c)形成连续的膜气体分子成核聚集连续的膜化学气相淀积的过程按工艺条件分APCVD 常压CVDLPCVD 低压CVDPECVD 等离子体增强型CVDHDPCVD 高密度等离子体CVDLCVD 光化学气相淀积按生成膜的性质分金属CVD半导体CVD介质CVD化学气相淀积的分类1)APCVD 常压化学气相淀积连续加工的APCVD反应炉•反应速度和淀积速度较快淀积速度可达1000nm/min)•APCVD淀积膜的均匀性较差•气体消耗量大•台阶覆盖能力差2)LPCVD 低压化学气相淀积LPCVD反应腔•在同样的膜厚均匀性要求下,LPCVD硅片的间距可以更小,使LPCVD的生产效率更高3)PECVD 等离子体增强型化学气相淀积•反应温度低200-400℃)和良好的台阶覆盖能力,可以应用在AL等低熔点金属薄膜上淀积,•缺点是淀积过程引入的粘污本课重点•化学气相淀积的概念•不同化学气相积淀方法的特点和应用THANKS 谢谢。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

淀积物本身必须具有足够低的蒸气压;

化学反应速率必须足够快以缩短淀积时间; 淀积温度必须足够低以避免对先前工艺产生影响; 化学反应应该发生在被加热的衬底表面,如果在气相发生 化学反应,将导致过早核化,降低薄膜的附着性和密度,

增加缺陷。

天津工业大学 集成电路工艺原理

边界层理论

黏滞性流动:当气压较高时(平均自由程远小于反应室尺寸),

天津工业大学 集成电路工艺原理

CVD的气体源

气态源(SiH4)

许多气体有毒、易燃、腐蚀 性强。

冒泡法(温度) 液态源(TEOS,TetraEthyl-Oxy-Silane)

液体气压低,危险性小,运 输方便,淀积的薄膜特性好。

加热液态源 液态源直接注入法

天津工业大学 集成电路工艺原理

冒泡法液态源

天津工业大学 集成电路工艺原理

CVD中常采用的源

天津工业大学 集成电路工艺原理

CVD反应室热源

CVD反应室热源:

热壁式:Tw=Ts,气流稳定,结构简单,侧壁淀积严重;

冷壁式: Tw<Ts,侧壁淀积少,降低了颗粒剥离的污染, 减少了反应剂的损耗

加热方式:

电阻直接加热(热壁式和冷壁式) 电感加热或高能辐射灯加热(多为冷壁式)

天津工业大学 集成电路工艺原理

边界层厚度:

( x) x / U

气流

平流层 边界层 X=0 X=L U ?(x) dx L

பைடு நூலகம்L /(3 Re )

y

x

雷诺数:

Re= ρUL / μ

雷诺数表示流体运动中惯性效应与粘滞 效应的比值,Re较低时,气流为平流 型,Re较大时,气流为湍流型

对于质量输运控制,保持处处恒定的反应剂浓度

天津工业大学 集成电路工艺原理

淀积速率与温度的关系

天津工业大学 集成电路工艺原理

§6.2 化学气相淀积系统

CVD系统通常包括:

气态源或液态源

气体输入管道

气体流量控制 反应室 基座加热及控制系统(其他激活方式) 温度控制及测量系统 减压系统(可选)

天津工业大学 集成电路工艺原理

常用的几种CVD系统

APCVD系统(Atmospheric Pressure CVD)

操作简单;较高的淀积速率;适于介质薄膜淀积; 易发生气相反应,产生颗粒污染;台阶覆盖性和均匀性较差;一 般是质量输运控制,需精确控制各处的反应剂浓度均匀; 水平式反应系统;连续式淀积系统。

气体与固体间的摩擦力使紧贴固体表面的气流速度降为零,如果沿 气流方向没有速度梯度,而沿垂直气流方向的流速为抛物线型变化, 则称为泊松流。

边界层(附面层、滞流层)概念:当气体流过硅片表面时,

存在着一个速度受到扰动并按抛物线型变化,同时还存在反应剂浓 度梯度的薄层被称为边界层,也称为附面层、滞流层。

天津工业大学 集成电路工艺原理

LPCVD系统(Low Pressure CVD)

污染小;均匀性和台阶覆盖性较好;一般是表面反应控制,精确控 制温度比较容易;

气缺现象;较低的淀积速率;较高的淀积温度;

淀积速率一般高于PVD,厚度范围广,由几百埃到数 毫米,且能大量生产;

淀积薄膜结构完整,致密,与衬底粘附性好,且台阶 覆盖性能较好; 薄膜纯度较差,一般用于制备介质膜。

天津工业大学 集成电路工艺原理

CVD薄膜的应用

浅槽隔离(STI,USG) 侧墙掩蔽(Sidewall, USG) 前金属化介质层(PMD,PSG、BPSG) 金属间介质层(IMD,USG、FSG) 钝化保护层(PD,Oxide/Nitride) 抗反射涂层(ARC,SiON)

G= (Cg hg ) /N1

天津工业大学 集成电路工艺原理

决定ks的主要因素:温度

ks=k0exp(-EA/kT)

决定hg的主要因素:气体流速,气体成分,系统压力

hg=Dg/δs;

( x) x / U

所以为了保证统一的淀积速率,就必须:

对于表面反应控制,保持处处恒定的温度

Chap.6 化学气相淀积(CVD)

CVD的基本概念、特点及应用

1 2 3 4 5

CVD的基本模型及控制因素

CVD系统的构成和分类

CVD SiO2的特性和方法 CVD多晶硅和氮化硅的方法

天津工业大学 集成电路工艺原理

CVD的基本概念

化学气相淀积(Chemical Vapor Deposition): ——把含有构成薄膜元素的气态反应剂或者液态反应剂的 蒸气,以合理的流速引入反应室,并以某种方式激活后 在衬底表面发生化学反应并在淀积成膜的一种方法。

天津工业大学 集成电路工艺原理

CVD氧化膜与热生长氧化膜

天津工业大学 集成电路工艺原理

CVD的工艺特点

CVD成膜温度远低于衬底的熔点或软点,减轻了对衬 底的热形变,减少了沾污,抑制了缺陷的生成,减轻 了杂质的再分布,适合于制造浅结分离器件及VLSI电 路,而且设备简单,重复性好; 薄膜的成分精确可控,配比范围大;

反应剂在表面被吸附; 吸附的反应剂在表面发生反应,淀积成膜; 反应的副产物和未反应剂离开衬底表面,排除。

主气流区 反应室

气流入口

边界层

气流出口 硅片 基座及加热装置

天津工业大学 集成电路工艺原理

能用于CVD的化学反应必须满足的条件

淀积温度下,反应剂必须具备足够高的蒸气压; 除淀积物外,反应的其他产物必须是挥发性的;

天津工业大学 集成电路工艺原理

天津工业大学 集成电路工艺原理

浅槽隔离(STI)

天津工业大学 集成电路工艺原理

侧墙掩蔽

天津工业大学 集成电路工艺原理

§6.1 CVD模型

天津工业大学 集成电路工艺原理

天津工业大学 集成电路工艺原理

CVD的基本过程

反应剂在主气流中的输送; 反应剂从主气流中扩散通过边界层到达衬底表面;

天津工业大学 集成电路工艺原理

Grove模型

F1=hg(Cg-Cs)

F2=ksCs Cs=Cg/(1+ks/hg)

Cg Cs

气体

薄膜

ks hg Cg F G N1 ks hg N1

Ks<< hg时,表面反应控制:

F1

F2

G= (Cg ks ) /N1

hg << Ks时,质量输运控制: