北邮数字逻辑课程设计..

北邮数字逻辑课程设计

北邮数字逻辑课程设计一、教学目标本课程的教学目标是使学生掌握数字逻辑的基本概念、原理和方法,能够运用数字逻辑设计简单的数字系统。

具体来说,知识目标包括:了解数字逻辑的基本概念,掌握逻辑门、逻辑函数、逻辑电路、组合逻辑电路、时序逻辑电路等基本知识;技能目标包括:能够使用数字逻辑设计简单的数字系统,能够进行逻辑电路的仿真和测试;情感态度价值观目标包括:培养学生的创新意识,提高学生的问题解决能力,使学生认识到数字逻辑在现代科技中的重要性。

二、教学内容本课程的教学内容主要包括数字逻辑的基本概念、原理和方法。

具体来说,包括以下几个部分:1. 逻辑门:介绍与门、或门、非门、异或门等基本逻辑门的功能和特点;2. 逻辑函数:介绍逻辑函数的定义、表达式和性质,以及逻辑函数的化简方法;3. 逻辑电路:介绍逻辑电路的分类、功能和特点,以及逻辑电路的设计方法;4. 组合逻辑电路:介绍组合逻辑电路的分类、功能和特点,以及组合逻辑电路的设计方法;5. 时序逻辑电路:介绍时序逻辑电路的分类、功能和特点,以及时序逻辑电路的设计方法。

三、教学方法本课程的教学方法主要包括讲授法、案例分析法和实验法。

在教学过程中,将结合具体的教学内容,采用不同的教学方法,以激发学生的学习兴趣和主动性。

例如,在讲解逻辑门、逻辑函数、逻辑电路等基本概念时,可以采用讲授法,通过清晰的讲解,使学生掌握基本知识;在讲解组合逻辑电路、时序逻辑电路等设计方法时,可以采用案例分析法,通过分析具体的案例,使学生理解设计方法的应用;在讲解实验时,可以采用实验法,通过实际的操作,使学生掌握逻辑电路的测试和仿真方法。

四、教学资源本课程的教学资源主要包括教材、实验设备和多媒体资料。

教材是学生学习的基本资源,将提供清晰的逻辑电路图和丰富的实例,帮助学生理解和掌握基本知识;实验设备是学生进行实验的重要资源,将通过实际的操作,使学生掌握逻辑电路的设计和测试方法;多媒体资料是学生学习的辅助资源,将通过视频、动画等形式,使学生更直观地理解逻辑电路的工作原理。

北京邮电大学数字电路与逻辑设计本科课件 第六章

Q0

1

C1

R

(1)74161:4位同 D0

& G9

& 1K

步二进制计数器。 功能:二进制加法

G5

& G10G17

FF1 & 1J

Q1

&

1

C1

R

计数、预置数、保持、D1

异步清零等。

CP

1 G2

计数脉冲

G6

& G11

& G12G18

& 1K

FF2 & 1J

Q2

&

1

C1

R

LOAD 为预置数控 D2

制端;

RD

(3)复位功能 复位也称为“清零”,将计数器的状态恢复到0状

态。复位是由复位控制端来控制。复位也分异步复

位和同步复位,异步复位不受时钟的控制,同步复

位除需要复位信号有效外,还必须在时钟的有效边 沿到来才能实现复位。

(4)进位(借位)功能 同步计数器可以有进位(借位)输出信号功能。当计

数器进入最大状态(例如输出全1),会产生进位输 出;或者当减法计数进入最小状态(输出全0),会 产生借位输出。进位/借位输出一般都是宽度等于 一个周期的脉冲,但是,脉冲的极性(正脉冲或负脉 冲)则要取决于具体的芯片,可从手册中的描述或功 能表中获得。

CKB的时钟),实现8421码十进制异步计数;

4.从CKB输入外部时钟,且 QD接到CKA,实现5421

码十进制异步计数。QA

QB

QC

QD

1J SD

C1

1KRD

1J C1

1KRD

1J C1

1KRD

& SD

大学数字逻辑实验课程设计

大学数字逻辑实验课程设计一、课程目标知识目标:1. 掌握数字逻辑电路的基本原理和设计方法;2. 熟悉数字逻辑电路的仿真与实验操作;3. 了解数字逻辑电路在实际工程中的应用。

技能目标:1. 能够运用所学知识设计简单的数字逻辑电路;2. 能够使用相关软件对数字逻辑电路进行仿真与测试;3. 能够分析并解决数字逻辑电路中存在的问题。

情感态度价值观目标:1. 培养学生对数字逻辑电路的探究兴趣,激发学生学习积极性;2. 培养学生的团队协作能力,增强合作意识;3. 培养学生的创新意识,提高实践能力。

课程性质:本课程为大学电子信息类专业的实验课程,旨在帮助学生将数字逻辑理论知识与实际操作相结合,提高学生的动手能力和实践能力。

学生特点:学生已具备一定的数字逻辑理论知识,但对于实验操作和相关软件的使用相对陌生。

教学要求:结合学生特点,注重理论与实践相结合,强调实验操作技能的培养。

通过课程学习,使学生能够将所学知识应用于实际工程设计中,提高学生的综合素质。

课程目标分解为具体学习成果,以便于后续教学设计和评估。

1. 数字逻辑电路基本原理:包括逻辑门、组合逻辑电路、时序逻辑电路等基本概念和原理。

- 教材章节:第1章 数字逻辑电路基础- 内容列举:逻辑门功能与真值表、组合逻辑电路设计、时序逻辑电路原理。

2. 数字逻辑电路设计方法:介绍常用数字逻辑电路设计方法,如原理图设计、硬件描述语言等。

- 教材章节:第2章 数字逻辑电路设计方法- 内容列举:原理图设计方法、硬件描述语言基础、数字逻辑电路设计实例。

3. 数字逻辑电路仿真与实验操作:学习使用相关软件进行数字逻辑电路的仿真与实验操作。

- 教材章节:第3章 数字逻辑电路仿真与实验- 内容列举:仿真软件介绍、仿真流程、实验操作步骤。

4. 数字逻辑电路在实际工程中的应用:分析数字逻辑电路在通信、计算机等领域的应用案例。

- 教材章节:第4章 数字逻辑电路应用- 内容列举:数字通信系统中数字逻辑电路的应用、计算机硬件中数字逻辑电路的应用。

北京邮电大学数字电路与逻辑设计实验报告.

北京邮电大学数字电路与逻辑设计实验报告学院:xxxx学院姓名:xxx班级:xxxxxxxxxx128学号:xxxxxxxxxx实验一Quartus II原理图输入法设计与实现一、实验目的(1)熟悉用Quartus II原理图输入法进行电路设计和仿真;(2)掌握Quartus II图形模块单元的生成与调用;(3)熟悉实验板的使用。

二、实验所用仪器及元器件(1)计算机;(2)直流稳压电源;(3)数字系统与逻辑设计实验开发板。

三、实验任务要求(1)用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模块单元。

(2)用实验(1)中生成的半加器模块和逻辑门设计实现一个全加器,仿真验证其功能,并下载到实验板测试,要求用拨码开关设定输入信号,发光二极管显示输出信号。

(3)用3线-8线译码器(74LS138)和逻辑门设计实现函数,仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号。

四、实验原理图及仿真波形图228328(1)半加器【实验原理图】【仿真波形图】【仿真波形图分析】由波形图可以看出,真值表如下:a b so co 000001101010111由此可得,,满足半加器的设计要求。

(2)全加器428【实验原理图】【仿真波形图】【仿真波形图分析】由波形图可以看出真值表如下:ain bin cin sum cout 00000001100101001101100101115281100111111用分别表示信号ain 、bin 、cin 、sum 和cout ,则可得逻辑表达式为满足全加器的设计要求。

(3)3线-8线译码器实现函数【实验原理图】【仿真波形图】【仿真波形图分析】由波形图可得真值表如下:A B C F00010011010101101000101011001111则逻辑表达式为。

实验二用VHDL设计与实现组合逻辑电路一、实验目的(1)熟悉用VHDL语言设计组合逻辑电路的方法;(2)熟悉用Quartus II文本输入法进行电路设计;(3)熟悉不同的编码及其之间的转换。

北邮数字逻辑课程设计实验报告(交通灯控制)

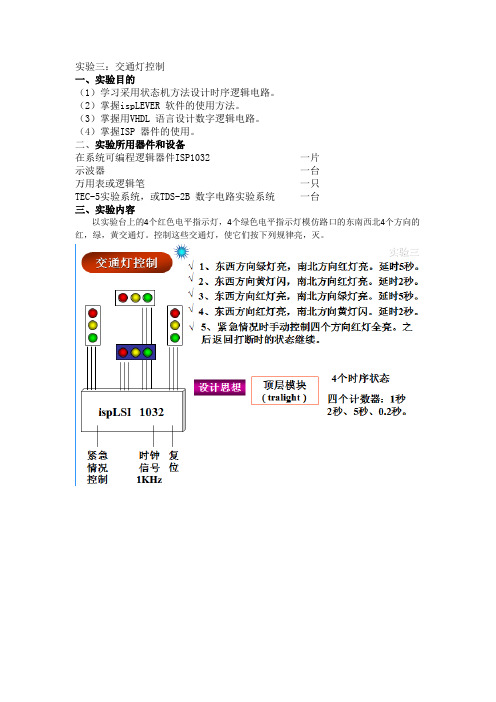

实验三:交通灯控制一、实验目的(1)学习采用状态机方法设计时序逻辑电路。

(2)掌握ispLEVER 软件的使用方法。

(3)掌握用VHDL 语言设计数字逻辑电路。

(4)掌握ISP 器件的使用。

二、实验所用器件和设备在系统可编程逻辑器件ISP1032 一片示波器一台万用表或逻辑笔一只TEC-5实验系统,或TDS-2B 数字电路实验系统一台三、实验内容以实验台上的4个红色电平指示灯,4个绿色电平指示灯模仿路口的东南西北4个方向的红,绿,黄交通灯。

控制这些交通灯,使它们按下列规律亮,灭。

VHDL源代码:LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY light isport (restfunc,emergency,clk: in std_logic;--restfunc为复位信号,emergency为紧急信号,clk为50kHz频率时钟light : out std_logic_vector(11 downto 0));--12个指示灯ARCHITECTURE func of light istype state is (s1,s2,s3,s4); --交通灯4个状态signal current_state,next_state: state;--current_state,next_state为别为当前状态,转移状态signal en1,en2,en3,en4, c,c1,c2,c3,c4: std_logic;--en为使能信号,c为进位信号signal temp1: integer range 0 to 49999;signal temp2: integer range 0 to 99999;signal temp3: integer range 0 to 249999;signal temp4: integer range 0 to 9999;begin--1s计数器,对50kHz进行50000分频process(clk,en1)beginif (clk'event and clk='1') then --上升沿判断if (temp1=49999 and en1='1' and emergency='0') thentemp1<=0;c1<='1';--进位elsif (en1='1' and emergency='0') thentemp1<=temp1+1;c1<='0';end if;end if;if (en1='0') thenc1<='0';temp1<=0;end if;end process;process(clk,en2)--2s计数器,对50kHz进行100000分频beginif (clk'event and clk='1') thenif (temp2=99999 and en2='1' and emergency='0') thentemp2<=0;c2<='1';elsif (en2='1'and emergency='0') thentemp2<=temp2+1;c2<='0';end if;end if;if (en2='0') thenc2<='0';temp2<=0;end if;end process;process(clk,en3)--5s计数器,对50kHz进行250000分频beginif (clk'event and clk='1') thenif (temp3=249999 and en3='1' and emergency='0') thentemp3<=0;c3<='1';elsif (en3='1' and emergency='0') thentemp3<=temp3+1;c3<='0';end if;end if;if (en3='0') thentemp3<=0;c3<='0';end if;end process;process(clk,en4) --0.2s计数器,对50kHz进行10000分频beginif (clk'event and clk='1') thenif (temp4=9999 and en4='1') thentemp4<=0;c4<=not c4;elsif (en4='1') thentemp4<=temp4+1;end if;end if;end process;c<=c1 or c2 or c3; --进位信号process (c,restfunc) --状态转移,复位情况beginif (restfunc='1') then--复位信号current_state<=s1;elsif (c'event and c='0') then--遇到计数器进位转移到下一状态current_state<=next_state;end if;end process;process (current_state,emergency) --状态转移,紧急情况beginif(emergency='1') then--紧急状态红灯全亮light<="000000001111";elsecase current_state iswhen s1=> --东西方向绿灯亮,南北方向红灯亮,延时5秒en1<='0';en2<='0';light<="010*********";en3<='1';next_state<=s2; --继续下一状态,下同when s2=>--东西方向黄灯闪,南北方向红灯亮,延时2秒en3<='0';en2<='1';en4<='1';light(11 downto 7 )<="00000";light(6)<=c4;light(5)<='0';light(4)<=c4;light(3 downto 0)<="1010";next_state<=s3;when s3=>--东西方向红灯亮,南北方向绿灯亮,延时5秒en2<='0';en4<='0';en3<='1';light<="101000000101";next_state<=s4;when s4=> --东西方向红灯闪,南北方向黄灯闪,延时2秒en3<='0';en2<='1';en4<='1';light(11 downto 8 )<="0000";light(7)<=c4; --闪灯控制light(6)<='0';light(5)<=c4;light(4 downto 0)<="00101";next_state<=s1;end case;end if;end process;end func;四、实验小结依旧注意4个分频。

北邮数电实验之组合逻辑电路、时序逻辑电路

北京邮电大学数字电路与逻辑设计实验报告(实验2)电子202-赵依然-2018212048摘要:本次数字电路与逻辑设计实验以初步掌握VHDL语言设计简单的数字电路,并且在QuartusⅡ上仿真为目的,加深组合逻辑电路和时序逻辑电路的基本原理、设计理念、运转方式。

关键词:组合逻辑电路时序逻辑电路VHDL QuartusⅡ仿真一:实验1实验内容11.1.1实验名称:VHDL组合逻辑电路设计-4选1数据选择器1.1.2实验任务要求:用VHDL语言设计实现一个4选1数据选择器,根据地址端的不同取值选择不同的数据端到输出端,仿真验证其功能。

1.2 电路设计及VHDL代码及注释1.2.1 设计原理:利用功能表进行判断。

设计数据输入端a3-a0和地址端s1-s0,输出端c,当地址端为11时c端输出a3的值,当地址端为10时c端输出a2的值,当地址端为01时c端输出a1的值,当地址端为00时c端输出a0的值。

这样就确定了电路的逻辑。

1.2.2 VHDL代码及注释:library ieee;use IEEE.STD_LOGIC_1164.all;use IEEE.STD_LOGIC_arith.all;use ieee.STD_LOGIC_unsigned.all;entity mux4 isport(a:in std_logic_vector(3 downto 0);s:in std_logic_vector(1 downto 0);c:out std_logic);end mux4;architecture mux4_arch of mux4 isbeginprocess(s)begincase s iswhen "00"=>c<=a(0);--当输入00,输出a(0)when "01"=>c<=a(1);when "10"=>c<=a(2);when "11"=>c<=a(3);end case;end process;end;1.3仿真波形图(请放大查看)1.4 仿真波形图分析由图可知,当s端地址端输入11,c端输出和a3一致,s端输入10,c端输出和a2一致,s端输入01,c端输出和a1一致,s端输入00,c端输出和a0一致。

北邮数电教材

北邮数电教材

北邮数电教材是《数字逻辑与微处理器设计》。

这本教材是北京邮电大学出版社出版的,主要是为数电与微处理器课程编写的教材。

该教材涵盖了数字逻辑电路的基础知识和原理、数字系统的设计方法、数字逻辑电路的建模和仿真等内容。

此外,还包括了微处理器的基本原理和设计方法,以及常用的微处理器体系结构和指令集。

《数字逻辑与微处理器设计》教材的特点是理论与实践相结合,重点突出了数字逻辑与微处理器的系统设计和应用。

教材中还包括了大量的实例和案例,帮助学生理解和应用所学的知识。

此外,北邮数电教材还有其他一些参考书,如《数字系统设计与应用》、《数字逻辑与设计》等,提供给学生更多的资料和参考。

需要注意的是,北邮数电教材可能会随着课程的不同而有所变化,因此建议参考学校或教师提供的具体教材名称和版本。

北邮数字逻辑课程设计..

实验要求

●熟练掌握isp EXPERT软件的使用方法

●熟练掌握isp器件的使用方法

●熟练掌握用VHDL进行数字逻辑电路设计 ●熟练掌握isp器件的下载方法 ●认真写出课程设计报告 ●7月7日~7月17日在实验室完成四个实验

实验要求

信号流程 Multimedia

输入信号

→

I/O单元 → 全局布线

→ 通用逻辑单元 →

结构体

x1 x2

f

x3

VHDL语言结构

存放已编译的实体、 结构体、程序包和 配置

存放各种设计模块 能共享的数据类型、 常数、程序等

库

描述所设计硬件系 统的外部接口信号

程序包

实体 结构体

描述所设计硬 件系统的内部 结构和功能

用来从库中选取 所需单元来组成 新系统

配置 VHDL结构

VHDL语言结构组成

ispLSI 1032

1~1MHz 时钟基 检 待测信号 准信号 测 100KHz 开 始

计 数

显 示

实验二

交通灯控制

√ 1、初始四个方向的红灯全亮。延时1秒。 √ 2、东西方向绿灯亮,南北方向红灯亮。延时5秒。 √ 3、东西方向黄灯闪,南北方向红灯亮。延时2秒。 √ 4、东西方向红灯亮,南北方向绿灯亮。延时5秒。 √ 5、东西方向红灯闪,南北方向黄灯闪。延时2秒。 6、返回2,继续运行。 √ 7、紧急情况时手动控制四个方向红灯全亮。之 后返回打断时的状态继续。 六个时序状态 设计思想

A B

S CO

结构体格式

实体名一致

A B

tmp1

S

tmp2

ARCHITECTURE <结构体名> OF <实体名> IS

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CLK q3 q2 q1 q0

× 0 0 0 0 上升 预置值 上升 计数值加1 × 保持不变

同步预置为 “1010”

仿真波形 counter16.vhd

简易电子琴

音符 (C)

1

2

3

4

5

6

7

i

频率(Hz) 262 294 330 349 392 440 494 523

输入的主频=100KHz 不同的键对100KHz进行分频

实验要求

●熟练掌握isp EXPERT软件的使用方法

●熟练掌握isp器件的使用方法

●熟练掌握用VHDL进行数字逻辑电路设计 ●熟练掌握isp器件的下载方法 ●认真写出课程设计报告 ●7月7日~7月17日在实验室完成四个实验

实验要求

信号流程 Multimedia

输入信号

→

I/O单元 → 全局布线

→ 通用逻辑单元 →

A B

S Co

实体说明、结构体格式

四位二进制同步计数器 areset R sset S enable EN CLK clk

R 1 0 0 0 S × 1 0 0 EN × × 1 0

CO Q0 Q1 Q2 Q3

cout

q0 q1 q2 q3

LIBRARY IEEE; 标准无符号 USE IEEE.std_logic_1164.ALL; 类型程序包 USE IEEE.std_logic_arith.ALL; USE IEEE.std_logic_unsigned.ALL; ENTITY counter IS PORT (clk, areset, sset ,enable : IN std_logic; cout : OUT std_logic; q : BUFFER std_logic_vector(3 DOWNTO 0)); END counter; ARCHITECTURE rtl_arc OF counter IS BEGIN PROCESS (clk,areset) BEGIN IF (areset ='1') THEN q <= '0'; ELSIF (clk'event AND clk ='1') THEN IF (sset ='1') THEN q <= "1010"; ELSIF (enable ='1') THEN q <= q +1; ELSE q <= q; END IF; END IF; END PROCESS; cout <= '1' WHEN q = "1111" AND enable ='1' ELSE '0'; END rtl_arc;

输出布线

→ I/O单元→ 输出信号

1032管脚定义

设计四位二进制计数器 (模16)

74LS163

演示_WEB

74LS163

模16计数器

用VHDL语言设计四位二进制计数器(模16)

ispLSI 1032

时钟 信号 K1 复 K2 位

模16计数器VHDL语 言

可编程逻辑的VHDL文本设计方式

● VHDL语言结构 LIBRARY ieee ;

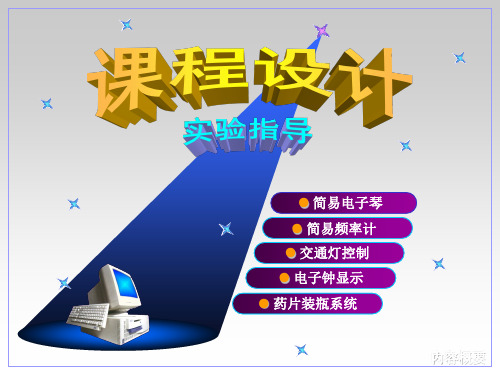

● 简易电子琴 ● 简易频率计 ● 交通灯控制 ● 电子钟显示

● 药片装瓶系统

内容概要

知识准备

● 复习

《数字逻辑与数字系统》 第五章 在系统编程技术

●图书馆借阅《VHDL数字电路设

计与应用实践教程》或硬件描述 语言类书籍

实验环境

● 主楼720实验室

● 60台实验仪

● 四人一组(限定每班7组)

知识准备

实体说明、结构体格式

半加器

A 0 0

B 0 1

S 0 1

Co 0 0

1

1

0

1

1

0

0

1

LIBRARY ieee ;

A B

Σ

ቤተ መጻሕፍቲ ባይዱS CO

USE ieee.std_logic_1164.all ;

ENTITY half_adder IS PORT ( A,B : IN std_logic; Co : OUT std_logic; S : OUT std_logic); END half_adder; ARCHITECTURE rtl OF half_adder IS BEGIN S <= A XOR B; Co <= A AND B; END rtl;

ispLSI 1032 多模计数器

时 钟 信 号

设计思想 1234567i K0K1K2K3K4K5K6K7 二分频计数器 判断当前按键 是否有效

A B

S CO

结构体格式

实体名一致

A B

tmp1

S

tmp2

ARCHITECTURE <结构体名> OF <实体名> IS

Co

[ 结构体说明部分 ];

BEGIN

<并行处理语句> ; END <结构体名> ;

ARCHITECTURE rtl OF half_adder IS SIGNAL tmp1,tmp2 : std_logic; BEGIN tmp1 <= A OR B; tmp2 <= A NAND B; Co <= NOT tmp2; S <= tmp1 AND tmp2; END rtl;

USE ieee.std_logic_1164.all ; ENTITY example1 IS PORT ( x1, x2, x3 f END example1 ; 库 每个部分通过关 键字引导出来

引用库中程序包

: IN BIT ; : OUT BIT ) ;

实体

ARCHITECTURE LogicFunc OF example1 IS BEGIN f <= (x1 AND x2) OR (NOT x2 AND x3) ; END LogicFunc ; 描述逻辑功能

实体说明格式 端口说明部分

ENTITY <实体名> IS [ 类属参数说明 ]; [ 端口说明部分 ]; [ 实体说明部分 ]; END <实体名>; ENTITY half_adder IS PORT ( A,B : IN std_logic; Co : OUT std_logic; S : OUT std_logic); END half_adder;

结构体

x1 x2

f

x3

VHDL语言结构

存放已编译的实体、 结构体、程序包和 配置

存放各种设计模块 能共享的数据类型、 常数、程序等

库

描述所设计硬件系 统的外部接口信号

程序包

实体 结构体

描述所设计硬 件系统的内部 结构和功能

用来从库中选取 所需单元来组成 新系统

配置 VHDL结构

VHDL语言结构组成