Lab 2 二与非门电路原理图设计

二输入端与非门设计.ppt

(6) 引入输入和输出脚:按步骤 (5) 选出2个输入脚

和1个输出脚。

第5章

组合逻辑电路设计

(7) 更 改 输 入 和 输 出 脚 的 脚 位 名 称 : 在 PIN_NAME 处双击鼠标左键,进行更名,输入脚为A、 B,输出脚为C。

Edit画面,2输入端与非门的电路符号如图5-2所示。

第5章

组合逻辑电路设计

(14) 创建电路包含文件:选取窗口菜单 File→Create Default Include File,产生用来代表目前所 设计电路的nand2.inc文件,供其他VHDL编译时使用, 如图5-3所示。 (15) 时间分析:选取窗口菜单Utilities→Analyze

(2) 保存:选取窗口菜单 File→Save ,出现对话框,

键入文件名nand2.gdf,单击OK按钮。

第5章

组合逻辑电路设计

(3) 指定项目名称,要求与文件名相同:选取窗口

菜单File→Project→Name,键入文件名nand2,单击OK 按钮。

(4) 确定对象的输入位置:在图形窗口内单击鼠标

电路的nand2 .inc文件,供其他VHDL编译时使用。 (11) 时间分析:选取窗口菜单Utilities→Analyze

第5章

组合逻辑电路设计

(6) 保存并查错:选取窗口菜单

File→Project→Save&Check,即可针对电路文件进行检查。 (7) 修改错误:针对Massage-Compiler窗口所提供的 信息修改电路文件,直到没有错误为止。 (8) 保存并编译:选取窗口菜单 File→Project→Save&Compile,即可进行编译,产生 nand2.sof烧写文件。

lab_二阶电路的响应实验课件

8

À谢谢收看

9

1. 绘出有关的实验接线图,并说明实验原 理。 2. 绘出 u (t ) 、u (t )、i (t ) 在过阻尼和欠阻尼情 况下的波形。

s

c

L

3. 绘出过阻尼和欠阻尼情况下的状态轨 迹。 七、思考题

7

1. 二阶RLC串联电路阻尼系数α和固有 频率ωo与激励源有无关系? 2.从方波响应来看,当RLC串联电路处 于过阻尼情况时,若减少回路电阻, 衰减到零的时间变短还是变长?当电 路处于欠阻尼情况时,若增加回路电 阻,震荡幅度衰减变快还是变慢?为 什么?

R L + C

1

S

2

+

Y1

iL

R L C +

us

ur (t ) +

r

uc

uc

Y2

uc(0−)= U 0 , iL (0− ) = I 0

RLC串联电路零输入响应

二阶RLC电路的方波响应

4

实验内容与要求

1. 观察 RLC 串联电路的零输入响应和阶跃 响应。按图接线。改变R,观察两种响应 的过阻尼、欠阻尼和临界阻尼情况,描 u (t ) i (t ) 绘出 和 的波形。注意此时回路电阻 R、 和r。 应包括R

1

电路测试技术

二阶电路的响应

实验目的

1.加深对二阶RLC串联电路暂态响应的形式 与元件参数关系的了解。 2.学习测量 RLC串联电路的状态轨迹。 3.学习用示波器测量二阶电路衰减震荡的 角频率和阻尼系数。

2

实验仪器设备

1.双踪示波器 一台

2.函数发生器

一台

3.动态电路实验板

一块

3

实验原理图

iL

与非门版图设计

目录1绪论 (2)1.1 设计背景 (2)1.2设计目标 (2)2与门电路设计 (3)2.1电路原理 (3)2.2电路结构 (3)2.3与门电路仿真波形 (4)2.4与门电路的版图绘制及DRC验证 (5)2.5与门电路版图仿真 (6)2.6 LVS检查匹配 (6)总结 (8)参考文献 (9)附录一版图网表: (10)附录二电路图网表 (12)1绪论1.1 设计背景Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。

L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

1.2设计目标1.用MOS场效应管实现二输入与门电路。

2.用tanner软件中的原理图编辑器S-Edit编辑反相器电路原理图。

3.用tanner软件中的W-Edit对反相器电路进行仿真,并观察波形。

4.用tanner软件中的L-Edit绘制反相器版图,并进行DRC验证。

cadence详细教程(模拟电路)

cadence详细教程(模拟电路)⽬录1.Cadence系统编辑环境 (2)实验1:Cadence系统编辑环境设置与基本操作 (2)2.电路图设计⼯具-Schematic (8)实验2:⼆与⾮门电路原理图设计 (8)实验3:数、模混合集成电路原理图设计 (14)3.电路仿真⼯具-ADE (18)实验4:ADE环境设置 (18)实验5:差分放⼤器电路仿真 (23)4.版图设计⼯具-Layout Editor (30)实验6:Layout Editor环境设置 (30)实验7:MOS管版图设计 (35)实验8:BJT管版图设计 (38)实验9:CMOS反相器版图设计 (42)实验10:Pcells版图设计 (46)实验11:pk44chip芯⽚版图综合设计 (53)5.版图验证⼯具-Diva (57)实验12:版图验证 (57)实验13:版图识别 (66)实验14:版图改错 (71)6.设计性实验 (73)实验15:RS触发器设计 (73)实验16:静态存储器设计 (76)实验17:三态与⾮门设计 (79)实验18:基准电压源设计 (81)实验19:CMOS放⼤器设计 (83)实验20:异或门设计 (84)Lab 1 Cadence系统环境设置与基本操作1.实验⽬的熟悉Cadence系统环境了解CIW窗⼝的功能掌握基本操作⽅法2.实验原理系统启动Cadence系统包含有许多⼯具(或模块),不同⼯具在启动时所需的License 不同,故⽽启动⽅法各异。

⼀般情况下涉及到的启动⽅式主要有以下⼏种,本实验系统所⽤到的有icms、icfb、layoutPlus等。

①前端启动命令:表1.1 前端启动命令命令规模功能icde s 基本数字模拟设计输⼊icds s icde以及数字设计环境icms s 前端模拟、混合、微波设计icca xl 前端设计加布局规划②版图⼯具启动命令表1.2 版图⼯具启动命令命令规模功能Layout s 基本版图设计(具有交互DRC功能)layoutPlus m 版图设计(具有⾃动化设计⼯具和交互验证功能)③系统级启动命令表1.3 系统级启动命令命令规模功能swb s PCB设计msfb l 混合型号IC设计icfb xl 前端到后端⼤多数⼯具CIW窗⼝Cadence系统启动后,⾃动弹出“what’s New…”窗⼝和命令解释窗⼝CIW (Command Interpreter Window)。

与非门、或非门和异或门的版图设计

实验四:与非门和或非门的版图设计、异或门的后仿真一、实验目的1、使用virtuoso layout XL工具创建或非门(NOR)和与非门(NAND)的电路原理图和版图;2、利用已创建好的或非门、与非门和反相器设计异或门(XOR)的电路原理图;3、对异或门提取的参数进行模拟仿真。

二、实验要求1、打印出由或非门、与非门和反相器设计成的异或门的仿真结果;2、打印出异或门的电路原理图和版图。

三、实验工具Virtuoso四、实验内容1、或非门的设计;2、与非门的设计;3、异或门的设计;4、异或门的仿真。

1、或非门的设计step1:创建或非门的电路原理图,其中,NMOS的宽度120nm为PMOS的宽度为480nm.图1 或非门的电路原理图step2:验证或非门是否可以正常工作,即创建SPICE netlist.图2 验证或非门图3验证成功产生的报告step3:创建一个layout view,并选择菜单栏上Tools->Lyaout XL,此时刚刚保存的电路原理图会自动弹出来,接着选择菜单栏上的Connectivity->Updata->Components and Nets,在弹出得对话框中修改参数,修改完成后点击OK,将会出现如下图所示布局。

图4 利用virtuoso XL工具生成的布局step4:参照前面的实验,在矩形边框内画上电源轨道和NWELL,并创建M1_PSUB 和MI_NWELL,将vdd!、gnd!移至电源轨道上,再将其他原件也移至矩形边框内。

对照电路原理图将NMOS、PMOS、电源、地、以及输入输出端口连接起来,在连线时,注意观察电路原理图,确保不会出现短路情况,连接好的版图如下图所示。

图5 连接好的或非门版图step5:对画好的版图进行DRC,成功后验证提取参数并做LVS验证,再生成网表文件。

图6 或非门版图的DRC验证图7 或非门的参数提取视图图8 或非门的LVS验证图9 或非门的网表文件2、与非门的设计与或非门的设计类似,在此不再赘述,直接给出与非门的电路原理图、版图以及DRC、LVS验证。

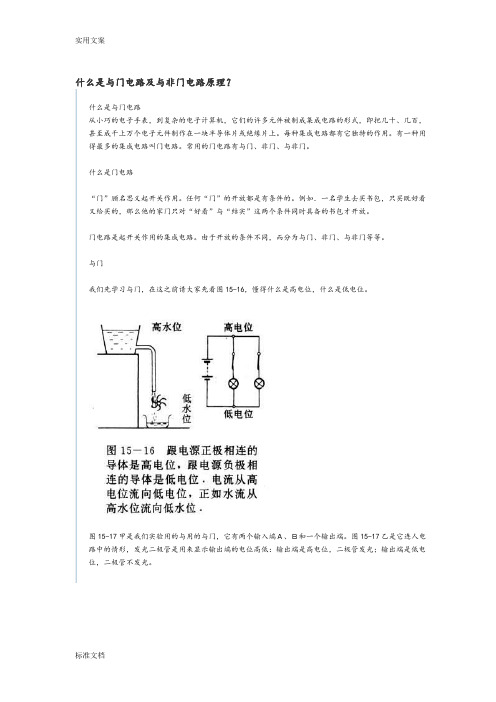

与门电路和与非门电路原理

什么是与门电路及与非门电路原理?什么是与门电路从小巧的电子手表,到复杂的电子计算机,它们的许多元件被制成集成电路的形式,即把几十、几百,甚至成干上万个电子元件制作在一块半导体片或绝缘片上。

每种集成电路都有它独特的作用。

有一种用得最多的集成电路叫门电路。

常用的门电路有与门、非门、与非门。

什么是门电路“门”顾名思义起开关作用。

任何“门”的开放都是有条件的。

例如.一名学生去买书包,只买既好看又给买的,那么他的家门只对“好看”与“结实”这两个条件同时具备的书包才开放。

门电路是起开关作用的集成电路。

由于开放的条件不同,而分为与门、非门、与非门等等。

与门我们先学习与门,在这之前请大家先看图15-16,懂得什么是高电位,什么是低电位。

图15-17甲是我们实验用的与用的与门,它有两个输入端A、B和一个输出端。

图15-17乙是它连人电路中的情形,发光二极管是用来显示输出端的电位高低:输出端是高电位,二极管发光;输出端是低电位,二极管不发光。

实验照图15-18甲、乙、丙、丁的顺序做实验。

图中由A、B引出的带箭头的弧线,表示把输入端接到高电位或低电位的导线。

每次实验根据二极管是否发光,判定输出端电位的高低。

输入端着时,它的电位是高电位,照图15-18戊那样,让两输人端都空着,则输出瑞的电位是高电位,二极管发光。

可见,与门只在输入端A与输入端B都是高电位时,输出端才是高电位;输入端A、B只要有一个是低电位,或者两个都是低电位时,输出端也是低电位。

输人端空着时,输出端是高电位。

与门的应用图15-19是应用与门的基本电路,只有两个输入端A、B同低电位间的开关同时断开,A与B才同时是高电位,输出端也因而是高电位,用电器开始工作。

实验照图15-20连接电路。

图中输入端与低电位间连接的是常闭按钮开关,按压时断开,不压时接通。

观察电动机在什么情况下转动。

如果图15-20的两个常闭按钮开关分别装在汽车的前后门,图中的电动机是启动汽车内燃机的电动机,当车间关紧时常闭按钮开关才能被压开,那么这个电路可以保证只有两个车门都关紧时汽车才能开动。

Lab2a集成电路设计

根据GBW和CL计算输入管的gm, 再根据Vdsat计算输入管的电流 和W/L 计算其它管子的W、L 一些建议:

需要匹配的管子一般取相同的 W和L,通过改变m实现电流比 MN2的L和Vdsat通常取比较大, 以提高CMRR PMOS负载管的L和Vdsat通常 取比较大,以降低噪声

Institute of Microelectronics, Peking University Copyright © 2014-2015 集成电路设计实习-单元实验二 模拟单元电路设计 Page 5

创建放大器的symbol和仿真电路

symbol用于调用关系 左下图用于dc/ac/noise仿真 右下图用于dc/tran仿真

Institute of Microelectronics, Peking University Copyright © 2014-2015

集成电路设计实习-单元实验二 模拟单元电路设计

Page 8

Results: MOSFET的直流工作点

Results Print DC Operating Points 鼠标点击元件弹出对 话框

集成电路设计实习-单元实验二 模拟单元电路设计

Page 18

DC/AC仿真小结

DC仿真是第一步,是否所有管子都处于预想的状态?

若不在正常工作状态,ac/tran等仿真结果无意义 放大管、负载管等都应处于饱和区,通常要求Vds比Vdsat大至少100mV (经验值) Vdsat大小是否合适?

实验内容:

设计差分放大器 对电路进行直流、交流、瞬态、噪声分析

实验目的:

掌握模拟集成电路单元模块的设计分析方法

时间安排:

非门,与非门,或非门的电路结构与仿真剖析

实验二非门、与非门、或非门的电路结构与仿真班级xxxx 姓名xx 学号xxxxxxxx 指导老师一、实验目的1、掌握基本组合逻辑电路结构及相关特性;2、进一步熟练Hspice等工具;二、实验内容及要求1、设计反相器电路;2、设计出2输入与非门、或非门并仿真;实验结果及要求:(1)、确定反相器电路每个晶体管尺寸;(2)、绘制出反相器电压传输特性;(3)、确定与非门、或非门各个管子的尺寸;三、实验原理1.反相器:(1)组成:一个增强型NMOS管和一个增强型PMOS管相连接而组成的;下方的NMOS 管的衬底(P型硅)都接地,而PMOS管衬底(N型硅)都接Vdd,这种对衬底的偏置方式可以避免源,漏区和衬底形成的PN结正偏,防止寄生效应。

(2)结构:CMOS反相器中输入端直接连接在NMOS管和PMOS管的栅极上,输入端引入的输入电平会直接影响NMOS管和PMOS管的工作状态。

而NMOS管和PMOS管的漏极则相互连接起来,构成了输出端,对外提供输出电平(Vout).注意:反相器的输出端并不是孤立的节点,而是连接有负载电容。

( 3 )在CMOS反相器中,NMOS管和PMOS管的栅源电压和漏源电压与输入,输出电平的关系为:V(GSN)= V(in);V(DSN)=V(out)V(GSP)=V(in)-V(DD);V(DSP)=V(out)-V(DD);备注:G为栅极,S为源极,D为漏极。

(5)反相器的工作原理:静态工作的CMOS反相器,当输入为逻辑值“0”时(V(in)= 0V),NMOS管的接地端为源极,NMOS管上的栅源电压为0V,而PMOS管接V(DD)的是源极,PMOS管的栅源电压为-V(DD).这就使得NMOS管处于截止状态而PMOS管处于导通状态;通过导通的PMOS管,在电源电压V(DD)与输出端连接的负载电容之间建立起了导电通路。

可以将负载电容充电到V(DD),使得输出的逻辑值变为“1”;当输入为逻辑值“1”时(此时的输入电平为V(DD),即V(in)=V(DD)),由于PMOS管的栅源电压为0V,而NMOS管的栅源电压为V(DD),使得PMOS管处于截止状态而NMOS管处于导通状态,这样就在负载电容与地电极之间通过NMOS管建立起了导电通路,使得负载电容被放电到0V,这就使输出逻辑值变为“0”。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Lab 2 二与非门电路原理图设计1.实验目的1.1了解Schematic设计环境1.2掌握二与非门电路原理图输入方法1.3掌握逻辑符号创建方法2.实验原理2.1Schematic设计环境启动Schematic Editor后,在命令解释窗口CIW中,打开任意库与单元中的Schematic视图,浏览Schematic Editing窗口如图2.1所示,顶部为菜单栏(Menu),左侧为图标栏(Icon Bar),具体介绍如下:图2.1 Schematic Editing窗口2.1.1菜单栏菜单栏中可选菜单有Tool、Design、Window、Edit、Add、Check、Sheet、Options等项。

其中常用菜单有:Tool菜单提供设计工具以及辅助命令。

比如,lab4、lab5所使用的仿真工具ADE,就在Tool下拉菜单中。

Window菜单中的各选项有调整窗口的辅助功能。

比如,Zoom选项对窗口放大(Zoom in)与缩小(Zoom out),fit选项将窗口调整为居中,redraw选项为刷新。

Edit菜单实现具体的编辑功能,主要有取消操作(Undo)、重复操作(Redo)、拉伸(Stretch)、拷贝(copy)、移动(Move)、删除(Delete)、旋转(Rotate)、属性(Properties)、选择(Select)、查找(Search)等子菜单,在以下实验中将大量应用。

Add菜单用于添加编辑所需要的各种素材,比如元件(Instance)或输入输出端点(pin)等。

2.1.2图标栏图标栏内的所有命令都可以在菜单栏实现,图标栏提供使用频率较高的一些菜单为快捷方式,旨在提高设计效率。

从上至下的图标共有:检查错误并存档(Check and Save)、放大(Zoom in)、缩小(Zoom out)、图形拉伸(Stretch)、拷贝(copy)、删除(Delete)、重复操作(Redo)、属性(Properties)、添加元件(Add Instance)、细连线(Wire Narrow)、粗连线(Wire Wide)、连线命名(Wire Label)、添加输入输出端点(Add pin)、命令选择(Command Options)等。

2.1.3盲键在设计过程中,除了可以使用图标快捷方式外,还有盲键(Bindkey)快捷方式。

比如添加元件,可以在Add菜单下选择Instance来弹出Add Instance窗口,也可以点击图标Add Instance来弹出Add Instance窗口,盲键快捷方式则为直接在键盘上按“i”键即可。

对比三种方式,盲键最为方便快捷。

Cadence系统安装过程中已经设置了通用的盲键,但用户可以根据自己的需要自行设置,在CIW窗口中,选择Options→Bindkeys,可以对所有设置的盲键自定义。

常用盲键在Edit和Add等菜单中都有定义,点击选择Edit,下拉菜单中的Stretch选项的盲键为[m],而Move选项的盲键为[M],Select选项中的Filter 则为[^r]。

用[ ]来表示盲键是Cadence系统自带的习惯,本实验系统中予以保留。

三种盲键分别表示为:[m]:直接在键盘按键m[M]:表示大写的M,同时按键Shift和m[^r]:同时按键Ctrl和r2.1.4鼠标Cadence系统支持3D鼠标,左、中、右分别定义为LMB、MMB、RMB。

LMB用于点击和选择之用,MMB用于辅助编辑,比如拷贝、粘贴、删除等,RMB与LMB配合使用,在调查元件属性,局域放大,元件旋转等方面都有应用,在具体实验过程中有详细说明。

电路原理图编辑环境,除了以上的菜单、图标、盲键、鼠标之外,尚有许多需要注意的地方,只能在设计过程中具体处理。

2.2 元件定义二与非门电路比较简单,读者可以自行解决。

需要注意的是,在所有元件的添加中,必须定义元件的属性。

比如nmos与nmos4,前者表示普通的nmos,默认为具有源、漏、栅极的三端器件;后者表示四端器件,在源、漏、栅三极之外,还有衬底作为一极,其具体偏置由具体电路决定。

其次,每个元件必须有器件参数,比如mos管的宽长比,电阻的阻抗等。

最后,为了后续设计中执行仿真,每个元件必须具有物理模型(Model),在lab3中将有实例说明。

3.实验内容3.1电路原理图设计3.1.1创建库与视图lab1中创建的库与视图如果仍存在,则没有必要再行创建,直接调用即可。

在CIW中选择File→open,在弹出窗口中选择如下:Library Name:mylibCell Name:nand2View Name:Schematic点击OK,打开Schematic Editing的空白窗口。

以下步骤为创建库与视图的过程。

①在命令解释窗口CIW中,依次选择File→New→Library,打开New Library窗口。

②在New Library窗口中,Name栏输入库文件名mylib(可以自定义),右侧工艺文件(Technology File)栏中,选择最下方的Don’t need a techfile,点击窗口左上角的OK。

③在CIW中,选择file→new→cellview,打开Create New File窗口。

④在Create New File窗口中,Library Name选取为mylib(与刚才定义一致),Cell Name设置为nand2,View Name选取为Schematic,Tool栏选取为Composer-Schematic,点击OK,弹出Schematic Editing的空白窗口。

3.1.2添加元件(电路如图2.2所示)图2.2 二与非门电路原理图1在Schematic Editing窗口中,选择Add→Instance,打开instance窗口如图2.3所示,在窗口中点击右侧Browse按钮,弹出Library Browser窗口如图2.4所示,在Library栏中选择analogLib,Cell选择nmos4,Cellview选择为symbol。

图2.3 instance窗口图2.4 Library Browser窗口注意:添加元件的方法方法一:选择Add→instance,弹出instance窗口;方法二:选择Tool bar图标栏中的instance图标,可弹出instance窗口;方法三:在键盘上按键“i”也可以弹出instance窗口(盲键的使用)。

2在Instance form中输入nmos4的参数如下:model name trnmoswidth 2.0ulength 0.5u3移动LMB(鼠标左键)到schematic窗口,刚才选择的nmos4元件以高亮度(黄色)出现,点击LMB完成添加过程。

4选择Add→Instance,在Library column中选择analogLib,再选择pomos4,在视图中选择symbol,参数设置为:model name:trpmoswidth: 2.5ulength:0.5u5添加完4个元件后,按ESC键(退出当前操作状态,此后均同)。

3.1.3添加Pins①在左侧Tool bar图标栏中选择pin icon图标,出现Add form窗口如图2.5所示,在Pin names栏中输入如下(注意Pin names之间有空格):Pin names INA INB OUT设置Direction为input设置Usage为schematic图2.5 Add form窗口图2.6 Add Wire Name窗口②点击Rotate(或鼠标右键RMB),可完成逆时钟旋转90度的操作。

③移动LMB到Schematic窗口,点击LMB可完成Pins的添加。

④依次完成INA ,INB ,OUT 三个pin的添加。

最后按ESC键。

3.1.4添加Sources和Ground①按盲键[i],激活Add instance form窗口。

②和选择nmos4方法相同,选择Add→Instance,在Library column中选择analogLib,再选择Vdd并添加到schematic中。

③同上方法,完成gnd的添加,按ESC键。

3.1.5连线①点击tool bar栏中的wire(narrow)图标。

②移动LMB到Schematic窗口,将需要连接的两个端点依次点击LMB,可完成连线。

③将poms4的衬底与Vdd相连,nmos4的衬底与gnd 相连。

衬底为栅极所对应的右侧的那条短线。

3.1.6连线命名①点击Wire Name图标,弹出窗口如图2.6所示,在窗口中输入ndrain,其它不变。

②将命名移至上面一个nmos4的源端(source),点击LMB。

③strench(拉伸)移动过的线至合适位置并点击它,完成以上操作后,按键Esc。

④点击tool bar栏中的check and save 图标,检查电路图无误后存档。

注意:Virtuoso Schematic Editor环境下,电路布线时,因为存在两条不相交的走线“过桥”问题,不相交的走线间没有节点,故而,Cadence系统默认所有的两条走线在形成十字时,都是没有节点的过桥问题。

在应当有节点的时候,只能形成丁字形式的节点,而不能形成十字形式的节点,否则,在check and save时提示为Warning。

注意到图2.2中,输出Y pin的连线没有直接与pmos4的源端相交在同一节点,而是在M1与M2连线之间形成了两个节点。

3.2创建符号3.2.1生成符号①在CIW窗口中,依次选择Tools→library manager→mylib→nand2,如图2.7所示。

双击view column中的schematic选项,在schematic中,依次选择:design→create cellview→From cellview。

图2.7 cellview From cellview②各项选择如下:Library name mylibCell name nand2From view name schematicTo view name symbolTool/Data type: Composer-symbol选择完成后点击OK,弹出Symbol Generation Options窗口,如图2.8所示。

图2.8 Symbol Generation Options③在Symbol Generation Options窗口中,请确定:Lift pins INA INBRight pins OUT点亮Load/Save按钮,点击OK(在窗口顶端),自动生成nand2 symbol,如图2.9所示。

图2.9 二与非门逻辑符号草图3.2.2编辑符号①用LMB选择红色的边框box,按键“m”移动边框box至上一格(移动一格)。