飞思卡尔寄存器整理

飞思卡尔16位单片机寄存器总结

一、输入输出端口寄存器I/O接口包括PORTA、B、E、K、T、S、M、P、H、J、AD。

其中PORTA、B、E、K属于复用扩展总线接口,单片机在扩展方式下工作时,作为总线信号。

1、PORTT、S、M、P、H、JI/O寄存器PTx如果对应位数据方向寄存器DDRx为“0”,输入,读取该寄存器返回引脚值;“1”,输出,读取该寄存器返回I/O寄存器的内容。

数据方向寄存器DDRx决定对应引脚为输出还是输入,“0”为输入,“1”为输出,复位后,默认为输入。

上拉/下拉使能寄存器PERx选择使用内置上拉/下拉器件,“1”允许,“0”禁用。

中断使能寄存器PIExPORTP、H、J三个端口具有中断功能。

“1”对应引脚允许中断,“0”禁止,复位后,所有端口中断关闭。

中断标志寄存器PIFxPORTP、H、J三个端口具有中断功能。

“1”对应引脚允许中断,“0”禁止,复位后,所有端口中断关闭。

2、PORTA、B、E、KI/O寄存器Px若某端口的引脚被定义为输出,写入I/O寄存器中的数值会从对应引脚输出;输入,通过I/O寄存器读取对应引脚电平。

数据方向寄存器DDRx决定对应引脚为输出还是输入,“0”为输入,“1”为输出,复位后,默认为输入。

PORTE最低两位只能为输入。

上拉电阻控制寄存器PERx第7、4、1、0位分别控制K、E、B、A端口,“1”允许使用对应端口的上拉电阻,“0”禁止,复位后,PK、PE端口使能,PB、PA禁止。

二、中断系统中断控制寄存器INTCR第7位IRQE,中断电平/边沿有效选择,0为低电平有效,1为下降沿有效;第6位IRQEN,外部中断IRQ中断请求使能,0关闭,1允许。

三、PWM模块PWM允许寄存器PWME对应每一位PWMEx,1启动输出,0停止输出,读写任意时刻。

PWM预分频时钟选择寄存器PWMPRCLK为Clock A和B选择独立的预分频因子,读写任意时刻。

Clock B对应6、5、4三位,Clock A对应2、1、0三位,分别可以实现2、4、8、16、32、64、128分频。

飞思卡尔S12系列寄存器和中断讲解

S12的输入/输入端口(I/O口)I/O端口功能可设置为通用I/O口、驱动、内部上拉/下拉、中断输入等功能。

设置I/O口工作方式的寄存器有:DDR、IO、RDR、PE、IE和PS。

DDR:设定I/O口的数据方向。

IO :设定输出电平的高低。

RDR:选择I/O口的驱动能力。

PE:选择上拉/下拉。

IE:允许或禁止端口中断。

PS:1、中断允许位置位时,选择上升沿/下降沿触发中断;2、中断禁止时且PE有效时,用于选择上拉还是下拉。

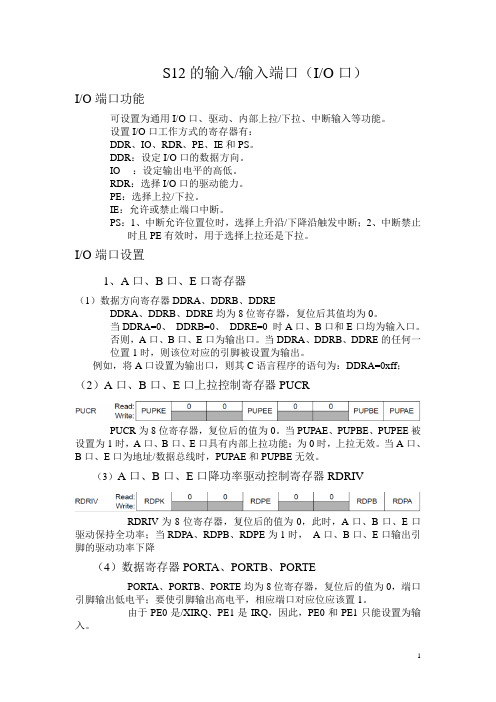

I/O端口设置1、A口、B口、E口寄存器(1)数据方向寄存器DDRA、DDRB、DDREDDRA、DDRB、DDRE均为8位寄存器,复位后其值均为0。

当DDRA=0、DDRB=0、DDRE=0 时A口、B口和E口均为输入口。

否则,A口、B口、E口为输出口。

当DDRA、DDRB、DDRE的任何一位置1时,则该位对应的引脚被设置为输出。

例如,将A口设置为输出口,则其C语言程序的语句为:DDRA=0xff;(2)A口、B口、E口上拉控制寄存器PUCRPUCR为8位寄存器,复位后的值为0。

当PUPAE、PUPBE、PUPEE被设置为1时,A口、B口、E口具有内部上拉功能;为0时,上拉无效。

当A口、B口、E口为地址/数据总线时,PUPAE和PUPBE无效。

(3)A口、B口、E口降功率驱动控制寄存器RDRIVRDRIV为8位寄存器,复位后的值为0,此时,A口、B口、E口驱动保持全功率;当RDPA、RDPB、RDPE为1时,A口、B口、E口输出引脚的驱动功率下降(4)数据寄存器PORTA、PORTB、PORTEPORTA、PORTB、PORTE均为8位寄存器,复位后的值为0,端口引脚输出低电平;要使引脚输出高电平,相应端口对应位应该置1。

由于PE0是/XIRQ、PE1是IRQ,因此,PE0和PE1只能设置为输入。

2、H口寄存器(1)H口I/O寄存器PTH任意时间读/写。

当某一引脚对就的数据方向位设置为1时,读操作返回的是这个端口寄存器的值;否则,读的是引脚的值。

飞思卡尔单片机 第1节-CPU寄存器

CPU寄存器

CPU寄存器

累加器 (A) 累加器A是一个通用8位寄存器。经常用于暂存一个输入到算 术逻辑单元(ALU)的操作数,并且用于存放(ALU)的计算结果。 复位对累加器A的内容没有影响。 索引寄存器(H:X) 这个16位寄存器实际上分为两个8位寄存器(H和X),它们作为 一个16位的地址指针一起工作,H存放一个地址的高位字节 和X存放地址的低位字节。所有索引寻址模式指令利用H:X中 全部16位值作为一个索引参考指针;然后,为了与早先 M68HC05家族兼容,一些指令只在低8位(X)中运行,并且H在 复位过程中强制为0x00。复位对X的内容没有影响。

HCS08 CPU的特点包括:

▪目标代码完全向上兼容M68HC05和M68HC08家族 ▪所有寄存器和存储器映射在单块64 Kbyte地址空间 ▪16位堆栈指针SP(64 Kbyte地址空间中的任意大小堆栈) ▪16位索引寄存器(H:X)的强大的寻址索引模式 ▪多种寻址模式 ▪8位累加器(A) ▪支持存储器到存储器的数据传送 ▪高效的位操作指令 ▪快速的8位乘8位和16位除以 8位指令 ▪STOP和WAIT指令唤醒低功耗运行状态

条件代码寄存器(CCR) 条件代码寄存器 8位条件代码寄存器存放中断屏蔽位(I)和5个指出刚执行指令 结果的标志。第5和第6位永远设置为1。如图:

I 位是中断屏蔽控制位,与其他位不同的是它在CCR 中不是处 理器状况位。在CCR的六个可执行位中,I 位也是复位后唯一可 被初始化的位。I 位复位后置为1,这使得中断被屏蔽直到堆栈 指针被初始化。其他五个状态位(V、H、N、Z 和C)在复位后是 未知的,只有在执行一个指令后才能知道。复位后无须强制这 些位为特定的值,因为直到执行了一个影响它们的指令后,与 这些位相关的条件转移才有意义。 这五个状态位标志了运算和其他指令的结果。条件转移指令 根据CCR 内状态位的值来决定是直接转移到一个新的程序地址, 还是继续执行下一个指令。简单的条件转移指令(BCC、BCS、 BNE、BEQ、BHCC、BHCS、BMC、BMS、BPL 和BMI)所导 致的转移取决于单一的CCR 位状态,而其他转移指令则被两三 个更复杂的CCR 位控制。例如,若布尔表达式[(Z) | (N⊕V)]真, 则将产生小于等于转移(BLE).

飞思卡尔16位单片机的资源配置

以MC9S12XS128MAL为例,其实DG128之类的类似。

如图一,128代表的是单片机中的FLASH大小为128K Byte,同理64代表的是单片机中的FLASH大小为64 K Byte,256代表的是单片机中的FLASH大小为256 K Byte。

但是S12(X)所使用的内核CPU12(X)的地址总线为16位,寻址范围最大为2^16 =64K Byte,而这64K Byte的寻址空间还包括寄存器、EEPROM (利用Data Flash模拟)、RAM等,因此不是所有的64K Byte都是用来寻址FLASH。

所以在S12(X)系列单片机中,很多资源是以分页的形式出现的,其中包括EEPROM、RAM、FLASH。

EEPROM的每页大小为1K Byte,RAM的每页大小为4K Byte,FLASH的每页大小为16K Byte。

因此XS128中EEPROM的页数为8K/1K = 8页,RAM的页数为8K/4K = 2页,Flash的页数为128K/16K = 8页。

图一图二在单片普通模式中,复位后,所有内存资源的映射如图二所示,其中从0x0000-0x07FF 的2K范围内映射为寄存器区,如I/O端口寄存器等,当然寄存器没有那么多,后面的一部分其实没有使用;从0x0800-0x0BFF,共1K的空间,映射为EEPROM区,由上面的分析,XS128中共有8页的共8K的EEPROM,所以这8页的EEPROM都是以分页的形式出现的,可以通过设置寄存器EPAGE选择不同的页并进行访问;从0x0C00到0x0FFF的1K空间为保留区(其实这里面也有学问,以后探讨);从0x1000到0x3FFF的12K空间为RAM区,分为三页,但是和前面所说的EEPROM不同,这三页中有2页(对于XS128和XS256)或一页(对于XS64)为固定页,位于12K空间的后一部分,以XS128为例,其内部的RAM资源为8K,所以其三页中的最后两页(0x2000-0x3FFF)为固定页,第一页(0x1000-0x1FFF)为窗口区,通过设置寄存器RPAGE来映射其他分页的RAM,当然在单片普通模式下,XS128内部已经没有其他的RAM了,所以这一页其实也没有用。

飞思卡尔之ATD模块

飞思卡尔之ATD模块今天看了ATD的模块,⼿头上有dg系列的资料,⽽⽤到的开发板是XS系列的。

在⽹上很难找到有关S12XS系列的中⽂资料,所以只能对着datasheet看,再加上⽹上搜集到的⼀些资料,有关此模块的⼀些⼩总结:S12XS系列MCU的ATD模块有27个寄存器,六个转换控制寄存器,两个转换状态寄存器,⼀个⽐较使能寄存器,⼀个⽐较⽅式寄存器和16个转换结果寄存器,附上⼀段例程void ATD_init(void){ATD0CTL1=0x0f; //选择8位转换精度ATD0CTL2=0x40; //打开CCF快速清零位,关闭外部触发输⼊,关闭中断ATD0CTL3=0x08; //数据左对齐,non-fifo,转换序列长度为1ATD0CTL4=0xE3; //采样时间为24个ATD时钟期, ATDCLK=8MB/8=1MHz}⼀般常⽤到的也就是这段例程中⽤到的⼏个寄存器。

//-----------------------------------------------------------////功能说明:MC9S12XS128--ATD例程//使⽤说明:由通道ATD0进⾏多通道A/D转换,转换值在B⼝显⽰//程序设计:DEMOK⼯作室()//设计时间:2010.03.12//------------------------------------------------------------//#include <hidef.h>#include "derivative.h"word AD_wValue;//AD转换结果//--------------初始化函数----------------////-----时钟初始化程序--------//void PLL_Init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1){ //锁相环时钟=2*16*(2+1)/(1+1)=48MHzREFDV=1; //总线时钟=48/2=24MHzSYNR=2;while(!(CRGFLG&0x08));CLKSEL=0x80;}//-----ATD初始化程序--------//void AD_Init(void){ATD0CTL1=0x00; //选择AD通道为外部触发,8位精度,采样前不放电ATD0CTL2=0x40; //标志位⾃动清零,禁⽌外部触发, 禁⽌中断ATD0CTL3=0xa0; //右对齐⽆符号,每次转换4个序列, No FIFO, Freeze模式下继续转ATD0CTL4=0x01; //采样时间为4个AD时钟周期,PRS=1,ATDClock=6MHzATD0CTL5=0x30; //特殊通道禁⽌,连续转换 ,多通道转换,起始通道为0转换4个通道ATD0DIEN=0x00; //禁⽌数字输⼊}//-----读取AD转换结果--------//void AD_GetValue(word *AD_wValue){*AD_wValue=ATD0DR0; //读取结果寄存器的值}//-----主函数--------//void main(void){PLL_Init();AD_Init();DDRB=0xFF;PORTB=0x00;EnableInterrupts;for(;;){while(!ATD0STAT2_CCF0); // 等待转换结束while(ATDOSTAT2_CCF0==1) AD_GetValue(&AD_wValue); // 读取转换结果PORTB = (byte)AD_wValue; // 在B⼝显⽰转换值}}。

飞思卡尔单片机_DG128_Timer寄存器说明

Bit15 Bit14 Bit13 Bit12 Bit7 Bit6 Bit5 Bit4

TC5 寄存器偏移量:$001A-$001B Bit15 Bit14 Bit13 Bit12 Bit7 Bit6 Bit5 Bit4

TC6 寄存器偏移量:$001C-$001D Bit15 Bit14 Bit13 Bit12 Bit7 Bit6 Bit5 Bit4

TC7 寄存器偏移量:$001E-$001F Bit15 Bit14 Bit13 Bit12 Bit7 Bit6 Bit5 Bit4

Bit11 Bit3

Bit11 Bit3

Bit8 Bit0

Bit8 Bit0

Bit8 Bit0

Bit8 Bit0

Bit8 Bit0

Bit8 Bit0

8、定时器核心寄存器(TCNT) 寄存器偏移量:$0004-$0005

Bit15 Bit14 Bit13 Bit12 Bit11 Bit10 Bit9 Bit8

Bit7 Bit6

Bit5

Bit4

所示的 TFLG1、TFLG2 为中断标志寄存器,其中 TFLG1 对应 8 个 IC/OC 通道,当某 CnF=1 时说明对应的 IC/OC 通道有动作,表明该通道有中断事 件发生。TFLG2 只有一个标志位 TOF,作为核心计数器的中断请求标志。当 TOF=1 时说明核心计数器溢出。要清除某个标志位,只需向该位写 1,向某位 写 0 不影响该位的状态。当 TSCR 中的 TFFCA 位置位时,读 IC 通道或写 OC 通道 ($10-$1F)将自动清除该通道标志 CnF,对 TCNT 的任何访问将自动清 除 TFLG2。

飞思卡尔单片机教程

注 : A/D模块的时钟频率要在500KHz和2MHz之间, 所以在选择分频因子时一定要注意。

采样时间选择

SMP [1 :0]

采样时间

00

2个 A/D时钟周期

01

4个A/D时钟周期

ATDclock= ( (BusClock) / (PRS+1) ) /2

10

8个A/D时钟周期

11

16个A/D时钟周期

设CCBCA = 000,转换序列从通道

0开始;ATD0DR0,

ATD0DR1,ATD0DR2存放转换结果

设CCBCA = 0 10,转换序列从通道 2开始。 仍然是ATD0DR0,

ATD0DR1,ATD0DR2存放转换结果

S8C 、S4C 、S2C 、S1C:定义转换队列的长度 。默认长度为4。 FIFO: 结果寄存器先进先出模式 。1=FIFO模式 ,转换结果是连续 存放的;0=非FIFO模式 ,转换结果放在对应的寄存器中。 FRZ1、FRZ0:背景调试冻结模式允许 。这两个控制位就决定了,

{ while (ATD1STAT0_SCF ==0) ;

ad_value [0] = ATD1DR0; ad_value [4] = ATD1DR4;//使用 PORTB= (byte) ad_value [4] ;

}}

void ATDInit(void)

{ATD1CTL2=0xC0;//AD模块上电,快速清零,无等待模式,禁止外部触发, 中断禁止 // ADPU AFFC AWAI ETRIGLE --- ETRIGP ETRIGE ASCIE ASCIF

PRS=3

ATD1CTL5=0xA4; //右对齐无符号 ,单通道采样 ,通道0

飞思卡尔单片机 DG128 SCI寄存器说明

SCI寄存器说明1、波特率控制寄存器(SCIBDH、SCIBDL)IREN:红外调制模式使能位1 使能0 禁止TNP[0..1]:窄脉冲发射位SBR[0..12]:波特率设置位When IREN = 0 then,SCI baud rate = SCI bus clock / (16 x SBR[12:0])When IREN = 1 then,SCI baud rate = SCI bus clock / (32 x SBR[12:1])【说明】波特率发生器在复位后是禁止的,在设置TE、RE(在SCICR2寄存器中)后才会工作。

当(SBR[12:0] = 0 and IREN = 0) 或者(SBR[12:1] = 0 andIREN = 1),波特率发生器不工作。

【注意】在未写入SCIBDL,写SCIBDH没有反应。

一般地,设置IREN=0,SR=52(总线频率8MHz),波特率为9600。

2、数据寄存器(SCIDRH、SCIDRL)SCI 内部分别设有发送和接收两个数据寄存器,其低位都通过SCIDRL 访问,读操作返回接收数据寄存器RDR 的内容,写操作数据置入发送数据寄存器。

TDR。

当M=1 即运行在9 位数据模式时,SCIDRL 和SCIDRH 形成9 位的SCI数据字,这时必须先写入SCIDRH,以便与低位字节(SCIDRL)一起进入发送移位器。

如果M=0 即SCI 只用于7 位或8 位的数据传送,可以只访问SCIDRL。

当PE=1 即奇偶校验允许时,奇偶校验位由硬件负责,无需软件干预。

R8:接收到的位8,该位写操作无效。

当SCI 设置成9 位数据运行模式时,该位是从串行数据流中接收到的第9 位。

T8:发送位8,任何时候可写。

当SCI 设置成9 位数据模式时,该位是送到串行数据流的第9 位。

该位不必为每个数据重新设置,每次发送可重复使用。

R[0..7]T[0..7]:收/发数据位7-0,读操作返回只读寄存器RDR 的内容,写操作写入只写寄存器TDR。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

S12的输入/输入端口(I/O口)I/O端口功能可设置为通用I/O口、驱动、内部上拉/下拉、中断输入等功能。

设置I/O口工作方式的寄存器有:DDR、IO、RDR、PE、IE和PS。

DDR:设定I/O口的数据方向。

IO :设定输出电平的高低。

RDR:选择I/O口的驱动能力。

PE:选择上拉/下拉。

IE:允许或禁止端口中断。

PS:1、中断允许位置位时,选择上升沿/下降沿触发中断;2、中断禁止时且PE有效时,用于选择上拉还是下拉。

I/O端口设置1、A口、B口、E口寄存器(1)数据方向寄存器DDRA、DDRB、DDREDDRA、DDRB、DDRE均为8位寄存器,复位后其值均为0。

当DDRA=0、 DDRB=0、 DDRE=0 时A口、B口和E口均为输入口。

否则,A口、B口、E口为输出口。

当DDRA、DDRB、DDRE的任何一位置1时,则该位对应的引脚被设置为输出。

例如,将A口设置为输出口,则其C语言程序的语句为:DDRA=0xff;(2)A口、B口、E口上拉控制寄存器PUCRPUCR为8位寄存器,复位后的值为0。

当PUPAE、PUPBE、PUPEE被设置为1时,A口、B口、E口具有内部上拉功能;为0时,上拉无效。

当A口、B 口、E口为地址/数据总线时,PUPAE和PUPBE无效。

(3)A口、B口、E口降功率驱动控制寄存器RDRIVRDRIV为8位寄存器,复位后的值为0,此时,A口、B口、E口驱动保持全功率;当RDPA、RDPB、RDPE为1时, A口、B口、E口输出引脚的驱动功率下降(4)数据寄存器PORTA、PORTB、PORTEPORTA、PORTB、PORTE均为8位寄存器,复位后的值为0,端口引脚输出低电平;要使引脚输出高电平,相应端口对应位应该置1。

由于PE0是/XIRQ、PE1是IRQ,因此,PE0和PE1只能设置为输入。

2、H口寄存器(1)H口I/O寄存器PTH任意时间读/写。

当某一引脚对就的数据方向位设置为1时,读操作返回的是这个端口寄存器的值;否则,读的是引脚的值。

(2)端口H输入寄存器PTIH只可读,不可写。

读该寄存器返回的是引脚状态。

该寄存器可检测相应引脚的输出是否过载或短路。

(3)数据方向寄存器DDRH(4)端口H降功率驱动寄存器RDRH(5)端口H拉动装置使能寄存器PERH任意时间读/写。

如果端口H是输入口,该寄存器将配置被激活的上拉或下拉装置。

当PERH某一位为1时,对应装备上拉或下拉使能。

当PERH某一位为0时,对应装备上拉或下拉禁止。

(6)端口H极性选择寄存器PPSH任意时间读/写。

该寄存器有两个作用:选择激活的中断边沿的极性;选择上拉或下拉。

当PPSH某一位为1时,H口对应引脚信号上升沿将使PIFH寄存器中相应位置位;当PERH对应位置1且端口定义为输入口时,引脚和下拉装置连接。

当PPSH某一位为0时,H口对应引脚信号下降沿将使PIFH寄存器中相应位置位;当PERH对应位置1且端口定义为输入口时,引脚和上拉装置连接。

(7)H口中断使能寄存器PIEH任意时间读/写。

PIEH寄存器可设置端口H相应引脚的外部中断边沿使能或禁止。

PIEH某一位置1时,对应引脚的中断使能。

PIEH某一位置0时,对应引脚的中断禁止。

(8)口中断标志寄存器PIFH任意时间读/写。

当对应引脚出现活动的边沿时,PIFH相应位被置1。

是上升沿或下降沿,由PPSH寄存器相应位的状态决定。

为了清除标志位,向PIFH对应位写“1”。

写“0”无效。

3、J口寄存器(1)J口I/O寄存器PTJ任意时间读/写。

当数据方向寄存器对应位置1时,读PTJ将返回PTJ中的值;否则读返回对应引脚的值。

(2)J口输入寄存器PTIJ只读不写。

读该寄存器将返回引脚的值。

该寄存器可检测相应引脚的输出是否过载或短路。

(3)J口数据方向寄存器DDRJ(4)J口降功率驱动寄存器RDRJ(5)J口拉动装备使能寄存器PERJ(6)J口极性选择寄存器PPSJ任意时间读/写。

该寄存器有两个作用:选择激活的中断边沿的极性;选择上拉或下拉。

当PPSJ某一位为1时,J口对应引脚信号上升沿将使PIFJ寄存器中相应位置位;当PERJ对应位置1且端口定义为输入口时,引脚和下拉装置连接。

当PPSJ某一位为0时,J口对应引脚信号下降沿将使PIFJ寄存器中相应位置位;当PERJ对应位置1且端口定义为输入口时,引脚和上拉装置连接。

(7)J口中断使能寄存器PIEJ任意时间读/写。

PIEJ寄存器可设置端口J相应引脚的外部中断边沿使能或禁止。

PIEJ某一位置1时,对应引脚的中断使能。

PIEJ某一位置0时,对应引脚的中断禁止.任意时间读/写。

当对应引脚出现活动的边沿时,PIFJ相应位被置1。

是上升沿或下降沿,由PPSJ寄存器相应位的状态决定。

为了清除标志位,向PIFJ对应位写“1”。

写“0”无效。

4、M口寄存器(1)M口I/O寄存器PTM任意时间读/写。

当数据方向寄存器对应位置1时,读PTM将返回PTM中的值;否则读PTM 将返回对应引脚的值。

(2)M口输入寄存器PTIM只读不写。

读该寄存器将返回引脚的值。

该寄存器可检测相应引脚的输出是否过载或短路。

Byteflight/CAN/BDLC强制将与其输出对应的引脚置为输出状态;同时,将与其输入对应的引脚置为输入状态。

(4)M口降功率驱动寄存器RDRM(5)M口拉动装备使能寄存器PERM任意时间读/写。

如果端口用于输入或“线或”输出,该寄存器配置被激活的上拉或下拉装置。

当端口用于推挽输出时,相应位无效。

(6)M口极性选择寄存器PPSM任意时间读/写。

当PPSM的某一位被置为1时,如果PERM对应位使能,并且端口用于通用或BDLC输入,则一个下拉装备被连接到M口对应引脚上。

当PPSM的某一位被清0时,如果PERM对应位使能,并且端口用于通用、Byteflight或RXCAN输入,则一个上拉装备被连接到M口对应引脚上。

该寄存器配置输出引脚为线或。

如果应用于Byteflight、CAN和BDLC 输出且许多几种串行模式的多点连接,则该寄存器的某一位对于用于输入的相应引脚无影响。

当WOMM某一位置为1时,输出缓冲器工作在开漏输出状态。

当WOMM某一位清为0时,输出缓冲器工作在推挽输出状态。

5、P口寄存器(1)P口I/O寄存器PTP任意时间读/写。

如果PWM通道使能,则PWM功能优先于通用I/O功能。

如果相应通道使能,通道6~0只能输出;如果停机特性使能,则通道7可作为PWM输出与输入。

SPI功能也优先于通用I/O功能。

(2)P口输入寄存器PTIP如果PWM对应通道或SPI模式使能,则该寄存器对引脚无效。

(4)P口降功率驱动寄存器RDRP(5)P口拉动装置使能寄存器PERP(6)P口极性选择寄存器PPSP任意时间读/写。

该寄存器有两个作用:选择激活的中断边沿的极性;选择上拉或下拉。

当PPSP某一位为1时,P口对应引脚信号上升沿将使PIFP寄存器中相应位置位;当PERP对应位置1且端口定义为输入口时,引脚和下拉装置连接。

当PPSP某一位为0时,P口对应引脚信号下降沿将使PIFP寄存器中相应位置位;当PERP对应位置1且端口定义为输入口时,引脚和上拉装置连接。

任意时间读/写。

PIEP寄存器可设置端口P相应引脚的外部中断边沿使能或禁止。

PIEP某一位置1时,对应引脚的中断使能。

PIEP某一位置0时,对应引脚的中断禁止。

(8)P口中断标志寄存器PIFP任意时间读/写。

当对应引脚出现活动的边沿时,PIFP相应位被置1。

是上升沿或下降沿,由PPSP寄存器相应位的状态决定。

为了清除标志位,向PIFP对应位写“1”。

写“0”无效。

6、S口寄存器(1)S口I/O寄存器PTS(2)S口输入寄存器PTIP(4)S口降功率驱动寄存器RDRS(5)S口拉动装置使能寄存器PERS(6)S口极性选择寄存器PPSS任意时间读/写。

该寄存器有两个作用:选择激活的中断边沿的极性;选择上拉或下拉。

当PPSP某一位为,PERP对应位置1且端口定义为输入口时,引脚和下拉装置连接。

当PPSP某一位为0,PERP对应位置1且端口定义为线或输出口时,引脚和上拉装置连接。

该寄存器配置输出引脚为线或。

如果应用于SPI和SCI输出且许多几种串行模式的多点连接,则该寄存器的某一位对于用于输入的相应引脚无影响。

当WOMM某一位置为1时,输出缓冲器工作在开漏输出状态。

当WOMM某一位清为0时,输出缓冲器工作在推挽输出状态。

S12微控制器中断模块中断源:中断请求信号的来源。

S12微控制器的中断源:特殊中断源、外部中断源、端口中断源、定时中断源、通信中断源、A/D中断源等。

中断过程①外部或内部中断源提出中断请求,如果存在中断标志位,则硬件置相应中断标志位。

②如果开放了CPU对相应中断源的中断请求的响应,CPU将暂停当前程序段的执行,I清0,即关中断,将断点地址与相关寄存器的值压入堆栈保护起来。

③跳转到中断入口地址执行指令,进而执行中断服务程序。

中断服务程序中清标志位。

④将压入堆栈的数据放回相关寄存器,断点地址放回PC。

⑤返回暂停的程序段继续执行。

1、不可屏蔽中断XIRQ中断入口地址:$fff4、$fff5。

C语言中断号:5。

(1)中断允许位X将CCR中的X位清0,就开放了CPU对XIRQ中断请求的响应。

C语言程序中,使用如下指令可开放XIRQ的中断:ASM LDAA #$10;ASM TAP;(2)中断请求信号低电平有效。

(3)实验①实验要求在main()中顺序点亮8支发光管,每次点亮1支。

在XIRQ的中断服务程序中反向点亮8支发光管,每次点亮2支。

②电路连接发光管由A口驱动;将E口与B口连接,由PB0为XIRQ提供中断请求信号。

2、可屏蔽中断IRQ中断入口地址:$fff2、$fff3。

C语言中断号:6。

(1)中断允许总控制位I将CCR中的I位清0,就开放了CPU对可屏蔽中断源的中断请求的响应。

(2)IRQ控制寄存器IRQCR程序中,IRQCR使用符号INTCR代替。

①IRQ中断触发方式选择位IRQE当IRQE=1时,IRQ引脚下降沿触发中断。

当IRQE=0时,IRQ引脚低电平沿触发中断。

②IRQ中断允许控制位IRQEN当IRQEN=1时,IRQ引脚与中断逻辑连接,IRQ中断允许。

当IRQEN=0时,IRQ引脚与中断逻辑断开,IRQ中断禁止。

(3)实验①实验要求在main()中顺序点亮8支发光管,每次点亮1支。

在IRQ的中断服务程序中反向点亮8支发光管,每次点亮2支。

②电路连接发光管由A口驱动;将E口与B口连接,由PB1为IRQ提供中断请求信号。

3、H口中断中断入口地址:$ffcc、$ffcd。

C语言中断号:25。

(1)中断允许总控制位I将CCR中的I位清0,就开放了CPU对可屏蔽中断源的中断请求的响应。