集成电路制造工艺流程图

《集成电路制造工艺》课件

CMOS工艺

适用广泛,消耗低功率,集成 度高

光刻和电子束刻蚀工 艺

芯片制造中影响巨大,直接决 定芯片精度和质量

IC封装技术

通过引线焊接连接芯片与外部 电路

集成电路制造工艺的未来发展方向

量子计算机

利用量子位的并行性,比传统计 算机更快速、更准确

纳米技术

更加精细的芯片制造和量子效应 的应用

3D打印

高质量、低成本的芯片制造和量 产

1 革命性

集成电路是现代科技的基础。无集成电路,无现代智能设备。

2 市场需求

集成电路产业是信息产业的核心,随着通讯和计算机的快速发展,需求量将节节攀升

集成电路制造工艺的发展历程

1

早期阶段

简单的扩散工艺和光刻工艺,可制造简单

集成度提高

2

的逻辑门和模拟器件

计算机辅助设计、离子注入、金属蒸镀等

新技术的应用,集成度不断提高

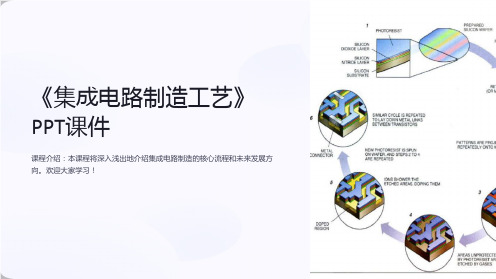

《集成电路制造工艺》 PPT课件

课程介绍:本课程将深入浅出地介绍集成电路制造的核心流程和未来发展方 向。欢迎大家学习!

什么是集成电路?

定义

集成电路是由数百万个微小电子元器件组成的电子 电路系统,它可以完成特定的功能。

历史

集成电路的起源可以追溯到20世纪60年代,它是计 算机和通讯技术的重要基础。

为什么集成电路制造工艺如此重要?

3

现代集成电路工艺

光刻、浸没/化学机械抛光、等离子刻蚀 等高级技术的应用,如今我们拥有极复杂 的芯片设计和制造工艺。

集成电路制造工艺的工作流程

芯片设计

设计加工工艺,布图加工

芯片构造

渗透、离子注入、扩散、腐蚀

芯片掩膜制作制作掩Fra bibliotek板、晶圆复制封装测试

集成电路制造工艺流程

P N+ N-P+

23

1.1.1 工艺流程(续5) 蒸镀金属 反刻金属

P P+ N+ N- P+

P-Sub

2021/1/7 韩良

P N+ N-P+

24

1.1.1 工艺流程(续6) 钝化 光刻钝化窗口后工序

P P+ N+ N- P+

P-Sub

2021/1/7 韩良

P N+ N-P+

25

1.1.2 光刻掩膜版汇总

N–-epi

钝化层

SiO2

P+

P-Sub 2021/1/7 韩良

N+埋层 27

EB C

N+ P

N+

N–-epi

P+

1.1.4 埋层的作用

1.减小串联电阻(集成电路中的各个电极均从 上表面引出,外延层电阻率较大且路径较长。 2.减小寄生pnp晶体管的影响(第二章介绍)

光P+刻胶

SiO2

EB C

N+ P

计公司。

2021/1/7

2

韩良

引言

2. 代客户加工(代工)方式

➢ 芯片设计单位和工艺制造单位的分离,即芯片设计单位可以不拥有生产线而存在和发 展,而芯片制造单位致力于工艺实现,即代客户加工(简称代工)方式。

➢ 代工方式已成为集成电路技术发展的一个重要特征。

2021/1/7

3

韩良

引言

3. PDK文件

2021/1/7

5

韩良

引言

5. 掩模与流片

➢ 代工单位根据设计单位提供的GDS-Ⅱ格式的版图 数据,首先制作掩模(Mask),将版图数据定义 的图形固化到铬板等材料的一套掩模上。

集成电路制造工艺流程

集成电路制造工艺流程概述集成电路(Integrated Circuit, IC)是由几千个甚至是数十亿个离散电子元件,如晶体管、电容、电阻等构成的电路,在特定的芯片上进行集成制造。

IC制造工艺流程主要包括晶圆制备、晶圆加工、芯片制造、封装测试等几个环节,是一个非常严谨、复杂的过程。

晶圆制备晶圆制备是IC制造的第一步。

晶圆是用硅单晶或其他半导体材料制成的薄片,作为IC芯片的基础材料。

以下是晶圆制备的流程:1.单晶生长:使用气态物质的沉积和结晶方法,使单晶硅的原料在加热、冷却的过程中逐渐成为一整块的单晶硅材料。

2.切片:将生长好的单晶硅棒利用切割机械进行切片,制成形状规整的圆片,称为晶圆。

3.抛光:将晶圆表面进行机械研磨和高温氧化处理,使表面达到极高的光滑度。

4.清洗:用去离子水等高纯度溶剂进行清洗,清除晶圆表面的污染物,确保晶圆的纯度和光洁度。

晶圆加工晶圆加工是IC制造的关键环节之一,也是最为复杂的过程。

在晶圆加工过程中,需要通过一系列的步骤将原始的晶圆加工为完成的IC芯片。

以下为晶圆加工的流程:1.光刻:通过光刻机将芯片图案转移到光刻胶上,然后使用酸洗、去除光刻胶,暴露出芯片的表面。

2.蚀刻:利用化学蚀刻技术,在IC芯片表面形成电路图案。

3.离子注入:向芯片进行掺杂,改变材料的电学性质。

4.热处理:对芯片进行高温、低温处理,使其达到设计要求的电学性能。

5.金属沉积:在芯片表面沉积一层金属,用于连接芯片各个元件。

芯片制造芯片制造是最为核心的IC制造环节,主要将晶圆加工后的芯片进行裁剪、测试、绑定等操作,使其具备实际的电学性能。

以下是IC芯片制造的流程:1.芯片测试:对芯片的性能进行测试,找出不合格的芯片并予以淘汰。

2.芯片切割:将晶圆上的芯片根据需求进行切割。

3.接线:在芯片表面安装金线,用于连接各个器件。

4.包装:将芯片放入封装盒中,并与引线焊接,形成成品IC芯片。

封装测试封装测试是IC制造的最后一步。

集成电路设计与制造的主要流程图

否 否

否

3

引言

半导体器件物理基础:包括PN结的物理机制、双极管、 MOS管的工作原理等

器件

小规模电路

大规模电路

超大规模电路

甚大规模电路

电路的制备工艺:光刻、刻蚀、氧化、离子注入、扩散、 化学气相淀积、金属蒸发或溅射、封装等工序

集成电路设计:另一重要环节,最能反映人的能动性

✓ 高度复杂电路系统的要求 ✓ 什么是分层分级设计? 将一个复杂的集成电路系统的设计问题分解为复杂性较低的设 计级别,这个级别可以再分解到复杂性更低的设计级别;这样 的分解一直继续到使最终的设计级别的复杂性足够低,也就是 说,能相当容易地由这一级设计出的单元逐级组织起复杂的系 统。一般来说,级别越高,抽象程度越高;级别越低,细节越 具体

集成电路 设计与制造的主要流程

1

集成电路设计与制造的主要流程框架

系 统 需 求 设计

掩膜版

芯片制造 过程

芯片检测

封装 测试

单晶、外 延材料

2

集成电路的设计过程:

设计创意 +

仿真验证

功能要求 行为设计(VHDL)

行为仿真 是

综合、优化——网表

时序仿真 是

布局布线——版图

—设计业—

后仿真 是

Sing off

没有单元库支持:对各单元进行电路设计,通过电

路模拟与分析,预测电路的直流、交流、瞬态等特性, 之后再根据模拟结果反复修改器件参数,直到获得满 意的结果。由此可形成用户自己的单元库

21

单元库:一组单元电路的集合

经过优化设计、并通过设计规则检查和反复工艺验证, 能正确反映所需的逻辑和电路功能以及性能,适合于工 艺制备,可达到最大的成品率。

集成电路制造工艺(微电子)..

接触与互连

Al是目前集成电路工艺中最常用的金 属互连材料 但Al连线也存在一些比较严重的问题

电迁移严重、电阻率偏高、浅结穿透等

Cu连线工艺有望从根本上解决该问题

IBM、Motorola等已经开发成功

形成横向氧化物隔离区

去掉光刻胶,把硅片放入氧化炉氧化,形成 厚的场氧化层隔离区 去掉氮化硅层

形成基区

光刻3#版(基区版),利用光刻胶将收集区遮挡 住,暴露出基区 基区离子注入硼

形成接触孔:

光刻4#版(基区接触孔版) 进行大剂量硼离子注入 刻蚀掉接触孔中的氧化层

形成发射区

合金 形成钝化层

测试、封装,完成集成电路的制造工艺

在低温条件下(小于300℃)淀积氮化硅 光刻钝化版 刻蚀氮化硅,形成钝化图形

CMOS集成电路一般采用(100)晶向的硅材料

双极集成电路 制造工艺

双极集成电路工艺

制作埋层

初始氧化,热生长厚度约为500~1000nm的氧化层 光刻1#版(埋层版),利用反应离子刻蚀技术将光刻窗 口中的氧化层刻蚀掉,并去掉光刻胶 进行大剂量As+注入并退火,形成n+埋层

集成电路工艺小结

后工序

划片 封装 测试 老化 筛选

集成电路工艺小结

辅助工序

超净厂房技术 超纯水、高纯气体制备技术 光刻掩膜版制备技术 材料准备技术

作

业

设计制备NMOSFET的 工艺,并画出流程图

形成场隔离区

生长一层薄氧化层 淀积一层氮化硅 光刻场隔离区,非隔离 区被光刻胶保护起来 反应离子刻蚀氮化硅 场区离子注入 热生长厚的场氧化层 去掉氮化硅层

集成电路生产工艺流程(一)

集成电路生产工艺流程(一)集成电路生产工艺概述集成电路生产工艺是指将所有电子元件集成在单一芯片上的生产过程。

它被广泛应用于电子设备制造业,如计算机、手机、电视等。

制造流程1.设计–集成电路设计师设计电路–使用EDA软件进行仿真与验证2.掩膜制造–制造掩膜–通过光刻技术将图案转移到硅片上3.投影光刻–使用掩膜将图案投影在硅片上–制造电路的输送4.融合–在高温下将掩膜和硅片融合–形成晶体管5.化学处理–使用化学液体进行蚀刻–将不需要的硅层去除6.金属化–在硅片表面蒸镀金属–形成线路和电极7.包装测试–切割硅片–用陶瓷或塑料封装芯片–测试芯片性能制造技术1.CMOS–基础工艺–低功耗和低噪音2.BJT–晶体管工艺–高频率和高速率3.BCD–模拟与数字工艺结合–适用于汽车、医疗和航空等领域4.MEMS–微电子机械系统–功能丰富的微型机械装置制造挑战1.芯片尺寸缩小–越来越小的芯片尺寸–需要更精密的光刻技术和更高的抗干扰能力2.成本控制–竞争日益激烈–芯片制造成本需要持续降低3.故障排除–单个芯片上有上亿个晶体管–如何排查其中的问题是一个挑战结论集成电路生产工艺是一个非常复杂的过程,需要各个流程相互合作,使用最新的技术和设备。

随着时间的推移,它将继续进化和改进,以满足越来越高的市场需求和更严格的质量控制。

制造趋势1.三维IC制造技术–将多个芯片堆叠在一起,以提高芯片效率和成本效益2.全球晶圆制造技术–分布式制造技术可帮助降低成本–全球晶圆制造可促进产业链的全球化3.自动化技术–机器学习和人工智能将推动制造工艺的自动化–减少人为干扰和错误应用领域1.通信–集成电路的高速率和低功耗等特点十分适合通信应用2.计算机–处理器、内存、存储等都需要集成电路–集成电路的不断进步也推动了计算机性能的提升3.汽车–外部环境复杂,需要集成电路来实现各种功能–集成电路技术适合于汽车电子系统的小型化和高度集成化4.医疗–集成电路技术在医疗成像、生物传感器和仿生器件等方面有广泛应用–提升了医疗设备的精度和可靠性结语随着各种工业领域的发展和需要,集成电路生产工艺将继续前进和改进。

集成电路制造工艺流程图

在集成电路制造过程中,该公司面临生产效率低下、产品质 量不稳定等问题,需要进行工艺流程优化。

优化动机

为了提高生产效率、降低成本、提升产品质量,该公司决定 开展集成电路制造工艺流程优化实践。

工艺流程优化措施与实践

措施一

引入自动化设备与智能检测系统

具体实践

引入先进的自动化生产线和智能检测设备,实现生产过程的自动化和智能化。

集成电路制造的定义

集成电路制造是指将多个电子元件集 成在一块衬底上,通过微细加工技术 实现电路功能的过程。

集成电路制造涉及多个工艺步骤,包 括光刻、刻蚀、掺杂、薄膜淀积等, 以实现电路的设计要求。

集成电路制造的重要性

集成电路制造是现代电子工业的基础 ,广泛应用于通信、计算机、消费电 子等领域。

集成电路制造技术的发展对于提高电 子产品的性能、降低成本、促进产业 升级具有重要意义。

Hale Waihona Puke 详细描述新型封装技术如倒装焊、晶圆级封装等不断 涌现,能够实现更小体积、更高集成度的封 装形式。同时,测试技术也在向自动化、高 精度方向发展,以提高测试效率和准确性。 这些技术的发展为集成电路的性能提升和应 用拓展提供了有力支持。

04

集成电路制造的设备与材料

集成电路制造的设备

晶圆制备设备

用于制造集成电路的晶 圆制备设备,包括切割 机、研磨机、清洗机等

。

光刻设备

用于将电路图形转移到 晶圆表面的光刻设备, 包括曝光机和掩膜对准

器等。

刻蚀设备

用于在晶圆表面刻蚀出 电路图形的刻蚀设备, 包括等离子刻蚀机和湿

法刻蚀机等。

集成电路制造的材料

半导体材料

用于制造集成电路的半导体材料,如硅和锗等 。

集成电路制造工艺流程

集成电路制造工艺流程1.晶圆制造( 晶体生长-切片-边缘研磨-抛光-包裹-运输 )晶体生长(Crystal Growth)晶体生长需要高精度的自动化拉晶系统。

将石英矿石经由电弧炉提炼,盐酸氯化,并经蒸馏后,制成了高纯度的多晶硅,其纯度高达0.99999999999。

采用精炼石英矿而获得的多晶硅,加入少量的电活性“掺杂剂”,如砷、硼、磷或锑,一同放入位于高温炉中融解。

多晶硅块及掺杂剂融化以后,用一根长晶线缆作为籽晶,插入到融化的多晶硅中直至底部。

然后,旋转线缆并慢慢拉出,最后,再将其冷却结晶,就形成圆柱状的单晶硅晶棒,即硅棒。

此过程称为“长晶”。

硅棒一般长3英尺,直径有6英寸、8英寸、12英寸等不同尺寸。

硅晶棒再经过研磨、抛光和切片后,即成为制造集成电路的基本原料——晶圆。

切片(Slicing) /边缘研磨(Edge Grinding)/抛光(Surface Polishing)切片是利用特殊的内圆刀片,将硅棒切成具有精确几何尺寸的薄晶圆。

然后,对晶圆表面和边缘进行抛光、研磨并清洗,将刚切割的晶圆的锐利边缘整成圆弧形,去除粗糙的划痕和杂质,就获得近乎完美的硅晶圆。

包裹(Wrapping)/运输(Shipping)晶圆制造完成以后,还需要专业的设备对这些近乎完美的硅晶圆进行包裹和运输。

晶圆输送载体可为半导体制造商提供快速一致和可靠的晶圆取放,并提高生产力。

2.沉积外延沉积 Epitaxial Deposition在晶圆使用过程中,外延层是在半导体晶圆上沉积的第一层。

现代大多数外延生长沉积是在硅底层上利用低压化学气相沉积(LPCVD)方法生长硅薄膜。

外延层由超纯硅形成,是作为缓冲层阻止有害杂质进入硅衬底的。

过去一般是双极工艺需要使用外延层,CMOS技术不使用。

由于外延层可能会使有少量缺陷的晶圆能够被使用,所以今后可能会在300mm晶圆上更多采用。

9.晶圆检查Wafer Inspection (Particles)在晶圆制造过程中很多步骤需要进行晶圆的污染微粒检查。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2020/8/12

韩良

3

集成电路设计原理

国际微电子中心

引言

3. PDK文件

➢ 首先,代工单位将经过前期开发确定的一套工艺 设计文件PDK(Pocess Design Kits)通过因特网传 送给设计单位。

PDK文件包括:工艺电路模拟用的器件的SPICE

宏力 8英寸晶圆0.25/0.18 mCMOS工艺 华虹 NEC 8英寸晶圆0.25mCMOS工艺 台积电(TSMC) 在松江筹建 8英寸晶圆0.18

mCMOS工艺 联华(UMC) 在苏州筹建 8英寸晶圆0.18

mCMOS工艺等等。

2020/8/12

韩良

8

集成电路设计原理

7.境外代工厂家一览表

➢ 在一张张掩模的参与下,工艺工程师完成芯片的 流水式加工,将版图数据定义的图形最终有序的 固化到芯片上。这一过程通常简称为“流片”。

2020/8/12

韩良

6

集成电路设计原理

国际微电子中心

引言

6. 代工工艺

代工(Foundry)厂家很多,如:

无锡上华(0.6/0.5 mCOS和4 mBiCMOS 工艺)

国际微电子中心

思考题

1.需要几块光刻掩膜版(mask)? 2.每块掩膜版的作用是什么? 3.器件之间是如何隔离的? 4.器件的电极是如何引出的? 5.埋层的作用?

2020/8/12

韩良

16

集成电路设计原理

国际微电子中心

双极集成电路的基本制造工艺,可以粗

略的分为两类:一类为在元器件间要做隔离 区。隔离的方法有多种,如PN结隔离,全介 质隔离及PN结-介质混合隔离等。另一类为 器件间的自然隔离。

2020/8/12

韩良

10

集成电路设计原理

国际微电子中心

Relation of F&F(无生产线与代工的关系)

8. 芯片工程与多项目晶圆计划

2020/8/12

韩良

11

集成电路设计原理

国际微电子中心

引言

8. 芯片工程与多项目晶圆计划

多项目晶圆MPW(multi-project wafer)技术服 务是一种国际科研和大学计划的流行方式。

通过因特网传送到代工单位。

2020/8/12

韩良

5

集成电路设计原理

国际微电子中心

引言

5. 掩模与流片

➢ 代工单位根据设计单位提供的GDS-Ⅱ格式的版图 数据,首先制作掩模(Mask),将版图数据定义 的图形固化到铬板等材料的一套掩模上。

➢ 一张掩模一方面对应于版图设计中的一层的图形, 另一方面对应于芯片制作中的一道或多道工艺。

国际微电子中心Βιβλιοθήκη 2020/8/12韩良

9

集成电路设计原理

国际微电子中心

引言

8. 芯片工程与多项目晶圆计划

F&F(Fabless and Foundry)模式

工业发达国家通过组织无生产线IC设计的芯片 计划来促进集成电路设计的专业发展、人才培 养、技术研究和中小企业产品开发,而取得成 效。

这种芯片工程通常由大学或研究所作为龙头单 位负责人员培训、技术指导、版图汇总、组织 芯片的工艺实现,性能测试和封装。大学教师、 研究生、研究机构、中小企业作为工程受益群 体,自愿参加,并付一定费用。

集成电路设计原理

国际微电子中心

引言

4. 电路设计和电路仿真

➢ 设计单位根据研究项目提出的技术指标,在自己 掌握的电路与系统知识的基础上,利用PDK提供 的工艺数据和CAD/EDA工具,进行电路设计、电 路仿真(或称模拟)和优化、版图设计、设计规 则检查DRC、参数提取和版图电路图对照LVS, 最终生成通常称之为GDS-Ⅱ格式的版图文件。再

MPW技术把几到几十种工艺上兼容的芯片拼装 到一个宏芯片(Macro-Chip)上然后以步进的 方式排列到一到多个晶圆上,制版和硅片加工 费用由几十种芯片分担,极大地降低芯片研制 成本,在一个晶圆上可以通过变换版图数据交 替布置多种宏芯片。

2020/8/12

韩良

12

集成电路设计原理

代工单位与其他单位关系图

➢ 设计工作由有生产线集成电路设计到无生 产线集成电路设计的发展过程。

➢ 无生产线(Fabless)集成电路设计公司。 如美国有200多家、台湾有100多家这样的 设计公司。

2020/8/12

韩良

2

集成电路设计原理

国际微电子中心

引言

2. 代客户加工(代工)方式

➢ 芯片设计单位和工艺制造单位的分离,即 芯片设计单位可以不拥有生产线而存在和 发展,而芯片制造单位致力于工艺实现, 即代客户加工(简称代工)方式。

上海先进半导体公司(1 mCOS工艺) 首钢NEC(1.2/0.18 mCOS工艺) 上海华虹NEC(0.35 mCOS工艺) 上海中芯国际(8英寸晶圆0.25/0.18 mCOS

工艺)

2020/8/12

韩良

7

集成电路设计原理

国际微电子中心

引言

6. 代工工艺

代工(Foundry)厂家很多,如:

国际微电子中心

2020/8/12

韩良

13

集成电路设计原理

国际微电子中心

集成电路制造工艺分类

1. 双极型工艺(bipolar) 2. MOS工艺 3. BiMOS工艺

2020/8/12

韩良

14

集成电路设计原理

国际微电子中心

§1-1 双极集成电路典型的 PN结隔离工艺

2020/8/12

韩良

15

集成电路设计原理

(Simulation Program with IC Emphasis)参

数,版图设计用的层次定义,设计规则,晶体管 、电阻、电容等元件和通孔(VIA)、焊盘等基 本结构的版图,与设计工具关联的设计规则检查 (DRC)、参数提取(EXT)和版图电路对照( LVS)用的文件。

2020/8/12

韩良

4

集成电路设计原理

国际微电子中心

第一章 集成电路制造工艺流程

集成电路(Integrated Circuit) 制造工艺是集成电路实现的手段, 也是集成电路设计的基础。

2020/8/12

韩良

1

集成电路设计原理

国际微电子中心

引言

1.无生产线集成电路设计技术

➢ 随着集成电路发展的过程,其发展的总趋 势是革新工艺、提高集成度和速度。

典型PN结隔离工艺是实现集成电路制 造的最原始工艺,迄今为止产生的各种双极 型集成电路制造工艺都是在此工艺基础上改 进而来的。

2020/8/12

韩良

17

集成电路设计原理

1.1.1典型PN结隔离工艺流程

国际微电子中心

衬底准 氧 埋层光 埋层扩 生长外 氧 隔离光