第3章 工艺基础及版图的层

集成电路工艺基础及版图设计

氧化环境中使硅表面发生氧化, 生成SiO2 薄膜。

滤气 球 O2

流量 控制

二通

温度 控制

硅片 氧化 炉

石英 管 温度 控制

图2 - 1 热氧化示意图

❖

根据氧化环境的不同, 又可把热

氧化分为干氧法和湿氧法两种。 如果氧

化环境是纯氧气, 这种生成SiO2薄膜的 方法就称为干氧法。 干氧法生成SiO2薄 膜的机理是: 氧气与硅表面的硅原子在

(2 -4)

SiH4+2O2→SiO2↓+2H2O

❖ 2.2.2 掺杂工艺

❖

集成电路生产过程中要对半导体

基片的一定区域掺入一定浓度的杂质元

素, 形成不同类型的半导体层, 来制作

各种器件, 这就是掺杂工艺。 由此可见,

掺杂工艺也是一种非常重要的基础工艺。

掺杂工艺主要有两种: 扩散工艺和离子

注入工艺。

间测试之前的所有工序。 前工序结束时,

半导体器件的核心部分——管芯就形成了。

前工序中包括以下三类工艺:

❖

(1) 薄膜制备工艺: 包括氧化、工艺: 包括离子注入和

扩散。

❖

(3) 图形加工技术: 包括制版和

❖

2) 后工序

❖

后工序包括从中间测试开始到器

❖

1. 扩散工艺

❖

物质的微粒总是时刻不停地处于

❖

扩散的机理有两种: 替位扩散和

填隙扩散。 在高温的情况下, 单晶固体

中的晶格原子围绕其平衡位置振动, 偶

然也可能会获得足够的能量离开原来的

位置而形成填隙原子, 原来的位置就形

成空位, 而邻近的杂质原子向空位迁移,

这就是杂质的替位扩散方式。 杂质原子

模拟集成电路版图基础

模拟集成电路版图基础

Lab3-1 CMOS 无源器件结构与版图 • 知识单元: • 1、电阻 • 2、电容 • 3、电阻和电容画法实例

模拟集成电路版图基础

一、电阻:1、方块电阻

• 方块电阻测量方法: – 用poly 来做一个电阻,先做一个正方形,长,宽相等。通过在其两端加 电压,测量电流的方法,可以得到它的阻值。

• 电阻并联: – 会达到什么结果呢?200ohms。把四个200ohms 的方块组合成一 个更大的方块,可以同样得到200ohms 的电阻值。可以把这个方 块越做越大,但最终测得电阻值将始终为200ohms。

• 对于不同大小的方块来说,阻值是一样的。由此可以用每方块多少电 阻来讨论电阻大小(200ohms/squares)。只考虑方块数,所有相同 材料的方块有相同的电阻值。

模拟集成电路版图基础

3.其他类型电阻

• N+电阻:

– 无需增添任何新的掩模版或层,只是用原先已有的其 他层来替代poly,就可以获得很多种电阻类型。

• P+电阻:

– 一般来说是做在nwell 中,因此必须增加第三个的端点 连接nwell,而且必须连接到最正的电平,一般来说是 vdd。这样可以防止寄生PN 结的影响。

模拟集成电路版图基础

扩散电阻与Poly电阻对比

• 使用工艺中已有的层来做电阻,做一些较小的修 改就可以得到所需要的方块电阻。扩散电阻和 Poly 电阻的一样,也要考虑delta 效应的影响。 扩散电阻是做在衬底上的,因此在边缘变化比较 大,工艺上不那么好控制。而且在做的时候必须 注意第三个端点的连接。

模拟集成电路版图基础

直接nwell电阻

• 直接nwell电阻: – 只不过需要2 个N+作为电阻头。 – 对于较大的阻值的电阻可用nwell 来做。 – Nwell 掺杂低,经过光照,电阻值会降低,呈现不稳定 的现象。 • 处理方法:在nwell 上覆盖金属,并将其电位接到电 源电压上,若无法接到电源电压时,可将其接到电 阻两端较高电位端。 • 在nwell 电阻四周加电源电压,以降低电压系数。当 well 电阻要接到pad,则必须于外围环绕pseudo collector,电位接到地,以防止其对其他的电路造 成latch-up。

第三章 集成电路版图设计基础

§3-1 版图设计规则

设计规则与厂家的技术水平和设备条 件密切相关,它不是正确与不正确实现集 成电路的严格界限,但是由于它包含了一 定的工艺容差,遵循它进行版图设计可以 保证集成电路高概率地正确实现。

2021/3/30

韩良

2

集成电路设计原理

电子科学与技术

3.1.1 工艺层

数据保存和处理时与图形的直观性

活划分多个N阱,避免同类器件过于集中影响布线。

•其它类型器件是否需要设立独立的阱,可以参照电隔 离原则确定。

2021/3/30

韩良

22

集成电路设计原理

3.2.3 压焊点的排布

电子科学与技术

(1)排布形状:压焊点是芯片与封装管腿相连接用 的输入/输出端口(I/O),一般分布在芯片四周。

•I/O较少时通常采用嵌入式 (embed)

3.1.2 几何设计规则

(2)几何图形的最小宽度

宽度是指一个封闭几何图形 自身内边与边之间的距离。

电子科学与技术

最小宽度是指在保证质量的前提下工艺所能加工出的 图形最小宽度。

例如:发射区扩散最小宽度 隔离扩散区的最小宽度

N阱最小宽度

N+有源区最小宽度

引线孔最小宽度

金属最小宽度等。

2021/3/30

韩良

地址寄存存器储阵译控列码制

些 按信主息次进 关行 系每 进个 行单布元的内码部 其它控制电路 加法

布 局局设。计。

控制

寄存器组 地址加法器

•最后从最小的子单元开始设计,这就是自上而下分

层布局-自下而上版图设计的设计方法。

2021/3/30

韩良

27

集成电路设计原理

3.2.5 布线层

模拟集成电路版图设计基础

集成电路工艺基础

以上每道工序都是需要掩膜 版的,那掩膜版的大小怎么

定呢?如何精确呢?

P-Si N+ (e)

P-Si

N+

(f)

SiO2 (5) 淀积SiO2, 将整个结构用SiO2覆盖起来, 刻

淀积SiO2

出与源区和漏区相连的接触孔。 (6) 把铝或其它金属蒸上去, 刻出电极及互连线

铝电极引出 SiO2 (场氧)

七、如何绘制版图

1.需要的软件工具

七、如何绘制版图

2.需要做的准备

七、如何绘制版图

2.需要做的准备

七、如何绘制版图

3.打开软件

七、如何绘制版图

3.打开软件

七、如何绘制版图

3.打开软件

七、如何绘制版图

4.相关设置

七、如何绘制版图

4.相关设置

七、如何绘制版图

4.相关设置

七、如何绘制版图

划分时需考虑的因素:模块的大小,模块的数目、模块之间的连 线数。

四、版图设计的过程

2.布图规划和布局:布图规划是根据模块所包含的器件数估计其面 积,再根据该模块与其他模块的连接关系以及上一层模块或芯片的 形状估计该模块的形状和相对位置。 3.布局的任务是确定模块在芯片上的精确位置,其目标是保证在布 通的前提下使芯片面积尽可能小。 4.布线:百分之百的完成模块之间的互连,在完成布线的前提下进 一步优化布线结果,如:提高电性能、减少通孔数。

✓ PMOS管,做在N阱中,沟 道为N型,源漏为P型

2) 包括层次:

✓ NWELL,N阱 ✓ PIMP,P+注入 ✓ DIFF,有源区 ✓ Poly,栅 ✓ M1,金属 ✓ CONT,过孔

3) MOS管的宽长确定

PMOS版图

理解版图的层

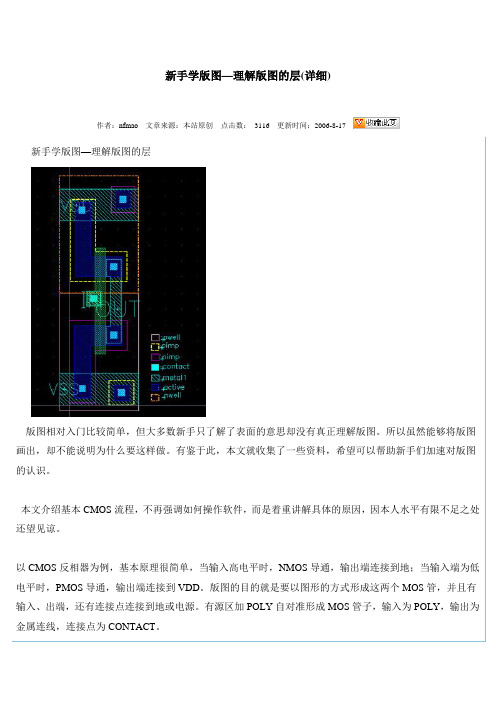

新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP 的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

用版图N-well层定位N-well区域,离子植入P+/600KeV/2x10^13cm^-2。

IC版图设计 入门培训材料

现在就可以使用提取的网表通过SPICE仿真确定 电路的实际性能。

2. 设计规则

如果仿真出的电路性能(如瞬态响应时间 或功耗)与期望值不相符,就必须对版图 进行修改并重复上面的过程。版图修改主 要是对晶体管尺寸中的宽长比进行修改。 这是因为管子的宽长比决定器件的跨导和 寄生源极和漏极电容。

应用Leff、Weff、 Weff/ Leff 不要用L、W、W/L

3. 基本工艺层版图

有源区接触

有源区接触(Active Contact):硅与互连金属的接触

3. 基本工艺层版图 金属层:与有源区接触

信号互连线 金属层1(Metal1) 电源线、地线

Metal1至有源区 接触的最小间距

Metal1线的 最小宽度

宽度指封闭几何图形的内边之间的距离

最小宽度 最大宽度

2. 设计规则 间距规则(Separation rule)(1)

间距指各几何图形外边界之间的距离

同一工艺层的间距 (spacing)

不同工艺层的间距 (separation)

2. 设计规则 交叠规则(Overlap rule)(1)

交叠有两种形式:

为了减小寄生效应,设计者也必须考虑对 电路结构进行局部甚至全部的修改。

掩膜版图设计流程

2. 设计规则

CMOS反相器版图设计

通过对CMOS反相器掩膜版图的设计来逐步讲解版图设 计规则的应用。

首先,我们要根据设计规则生成每个晶体管。

假设我们要设计一个具有最小晶体管尺寸的反相器。

集成电路版图设计与验证课件

5 常用工艺之二:光刻

❖ 目的:按照集成电路的设计要求,在SiO2或 金属层上面刻蚀出与光刻掩膜版完全相对应 的几何图形,以实现选择性扩散或金属布线 的目的。

5 常用工艺之二:光刻

❖ 主要步骤 ❖ (1)在晶圆上涂一层光刻胶,并将掩膜版

放在其上。 ❖ (2)曝光。正胶感光部分易溶解,负胶则

相反。 ❖ (3)显影、刻蚀。 ❖ (4)去除光刻胶

3.3 工艺集成

❖ 1 制作流程 ❖ 2 无源器件 ❖ 3 双极集成电路制造流程 ❖ CMOS工艺

1 制作流程

1 制作流程

2 无源器件

❖ 1、电阻 ❖ (1)淀积:淀积电阻层,然后光刻刻蚀 ❖ (2)扩散或离子注入:在硅衬底上热生长的

氧化层上开出一个窗口,注入或扩散与衬底 类型相反的杂质。

电阻

❖ (3)掺杂工艺:包括扩散工艺和离子注入工 艺。

3 工艺流程

❖ 以上工艺重复、组合使用,就形成集成电路 的完整制造工艺。

❖ 光刻掩模版(mask):版图完成后要交付给 代工厂,将版图图形转移到晶圆上,就需要 经过一个重要的中间环节——制版,即制造 一套分层的光刻掩膜版。

3 工艺流程

❖ 制版——光刻掩膜版就是讲电路版图的各个 层分别转移到一种涂有感光材料的优质玻璃 上,为将来再转移到晶圆做准备,这就是制 版。

❖ 每层版图都有相对应的掩膜版,并对应于不 同的工艺。

4 常用工艺之一:外延生长

❖ 半导体器件通常不是直接做在衬底上的, 而是先在沉底上生长一层外延层,然后将 器件做在外延层上。外延层可以与沉底同 一种材料,也可以不同。

❖ 在双极型集成电路中:可以解决原件间的 隔离;减小集电极串联电阻。

❖ 在CMOS集成电路中:可以有效避免闩锁 效应。

新手学版图—理解版图的层

新手学版图—理解版图的层(详细)作者:nfmao 文章来源:本站原创 点击数: 3116 更新时间:2006-8-17新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS 流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS 反相器为例,基本原理很简单,当输入高电平时,NMOS 导通,输出端连接到地;当输入端为低电平时,PMOS 导通,输出端连接到VDD 。

版图的目的就是要以图形的方式形成这两个MOS 管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY 自对准形成MOS 管子,输入为POLY ,输出为金属连线,连接点为CONTACT 。

阻,光照射的区域可溶化,以此定位出开孔区域。

孔内金属是以MOCVD(金属有机化学气相沉积CVD)形式沉积金属W(钨),再以CMP方式打磨多余的金属。

濺射第一层金属,并以版图metal1层,刻画出金属连线。

覆盖CMP(介电层),以同样的方式开孔(版图via 1层),刻画第二层金属(版图metal2层)。

如果是完整的项目还要使用版图pass层开出PAD的位置,并进行钝化处理以PECVD(介质等离子体增强化学气相沉积)沉积氮化硅,以达到保护芯片的目的。

现在各层的作用已经有了说明,接下来将利用实际的作用来举例说明,层与层之间的关系。

1,版图P-well层,N-wel l层在衬底形成各自的阱区,它们之间的关系应该不能相互重叠。

2,因为器件形成在阱中,所以器件的图形必须被阱所覆盖,要么在P-well中,要么在N-well中。

3,P-well与P-well,N-well与N-well是否可以相连,取决于特性是否一致,比如相同的电位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第三章 集成电路工艺基础及版图设计

同一加工工艺上,如果两个晶体管宽度相同,而 长度不同,则栅长度短的晶体管必会产生更大的电流。 晶体管的宽度,可想象为一系列平行的沟道,电 流通过这些沟道从源极流向漏极。

如果两晶体管长度相同,宽度更宽的晶体管有更 多的有效沟道,更多的沟道则意味着更大的电流。 更大的电流在概念上则意味着更快的性能。

第三章 集成电路工艺基础及版图设计

3.3.3 反相器版图

第三章 集成电路工艺基础及版图设计

无论在电路图中还是在版图中,PMOS晶体管都与VDD 相连接; 在电路图和版图中,NMOS晶体管都与VSS相连接; 在电路图和版图中,NMOS晶体管和PMOS晶体管的栅 极有相同的IN信号,而其漏极有相同的OUT信号; 两种晶体管的宽度不同——在此例中,PMOS晶体管的 宽度是NMOS晶体管的两倍。 两种晶体管的长度看似相同,但却不同,我们很难辨别 它们的差异; 对于N阱来说,N+区域实际上是与VDD相连接的,而 电路图中没有显示这一连接关系; 对于衬底来说,P+区域实际上是与VSS相连接的。而电 路图中没有显示这一连接关系。

第三章 集成电路工艺基础及版图设计

第三章 CMOS集成电路工艺基础及版图设计

3.1 CMOS集成电路制造工艺简介 3.2 版图设计技术 3.3 九天软件进行版图设计

第三章 集成电路工艺基础及版图设计

3.1 CMOS集成电路制造工艺简介

集成电路的制造工艺包括衬底外延生长、掩膜制版、 光刻、掺杂、绝缘层、金属层形成等等。 CMOS工艺技术是当代VLSI工艺的主流工艺技术。 它是在PMOS和NMOS工艺基础上发展起来的。其特点 是将NMOS器件和PMOS器件制作在同一硅衬底上,一 般可分为三类,P阱CMOS工艺、N阱CMOS工艺和双 阱CMOS工艺。

形成了MOS管的源区和漏区; 同时多晶硅也被掺杂, 减小了多

晶硅的电阻率。 (5) 淀积SiO2, 将整个结构用SiO2覆盖起来, 刻出与源区和漏区

相连的接触孔。

(6) 把铝或其它金属蒸上去, 刻出电极及互连线

第三章 集成电路工艺基础及版图设计

3.1.2 P阱CMOS工艺简介

P 阱 CMOS 工艺通常是在中度掺杂的 N 型硅衬底上

型衬底通过一个 N+ 区和接触孔内的金属与 UDD 相连;

P阱通过一个P+区和接触孔内的金属与USS相连。

第三章 集成电路工艺基础及版图设计

金属(UD D) 多晶硅(Uin ) P+区 金属(USS)

P阱 接触 孔

(a )

薄氧化层 ( P管有源区)

金属(Uou t)

薄氧化层 ( N管有源区)

图3 - 6 反向器版图及结构剖面图 (a) 版图; (b) 结构剖面图

第三章 集成电路工艺基础及版图设计

3.4工艺设计规则

用特定工艺制造电路的物理掩膜版图都必须遵循 一系列几何图形排列的故则,这些规则称为版图设计 规则。 通过适度的图形排列可以得到较高的成品率,通 过将芯片上不同的器件进行高密度放置能得到更高的 面积利用率,但这两者常常是相互矛盾的。

一个特定制造工艺的版图设计规则通常指出了成 品率和密度之间的一个最优的平衡点。

第三章 集成电路工艺基础及版图设计

3.3.4器件尺寸设计

栅和有源区的重叠确定了器件的尺寸,重叠区之外的区 域对器件的尺寸没有影响。 如何根据电路性能要求设计器件的尺寸?要设计多大的 重叠区?

第三章 集成电路工艺基础及版图设计

两个重要的尺寸参数——晶体管的长度和宽度

就版图而言,晶体管的长度是源极和漏极之间的距 离;就晶体管性能而言,晶体管的长度是电子所必须 移动的距离;就制造而言,晶体管的长度是多晶硅 (多晶)能够可靠制造的最窄可能长度。

隔离层:用于隔离的层,它在垂直方向和水平方向上 将各个导电层互相隔离开来。无论是在垂直方向还是 在水平方向上都需要进行隔离,以此来避免在个别电 气节点之间产生“短路”现象。

接触和通孔:用于确定绝缘层上的切口(cut)。绝缘 层用于分隔导体层,并且允许上下层通过切口或“接 触”孔进行连接,像金属通孔或接触孔就是这类例子。 在钝化层上为绑定pad开孔则是接触层的另一种情况。

第三章 集成电路工艺基础及版图设计

SiO2 淀积SiO2 P- Si (e) 铝电 极引出 P- Si (f)

图3 - 3 硅栅MOS管的制造工序 (a) 场氧化、 光刻有源区; (b) 栅氧化; (c) 淀积多晶硅、 刻多晶硅;(d) N+注入; (e) 淀积SiO2, 刻接触孔; (f) 蒸铝、 刻铝电极和互连

第三章 集成电路工艺基础及版图设计

3.1.1 硅栅MOS工艺简介

硅除了以单晶的形式存在外, 还以多晶的形式存在, 称为多晶硅(见图 3 - 1)。 多晶硅从小的局部区域去看, 原 子结构排列整齐; 但从整体上看却并不整齐。

图3 - 1 多晶硅

第三章 集成电路工艺基础及版图设计

图 3 -2 是硅栅NMOS管的剖面结构, 多晶硅栅极

N+

N+

SiO2 ( 场氧)

第三章 集成电路工艺基础及版图设计 (1)对P型硅片进行氧化, 生成较薄的一层Si3N4, 然后进行光 刻, 刻出有源区后进行场氧化。 (2) 进行氧化(栅氧化), 在暴露的硅表面生成一层严格控制的

薄SiO2层。

(3) 淀积多晶硅, 刻蚀多晶硅以形成栅极及互连线图形。 (4) 将磷或砷离子注入, 多晶硅成为离子注入的掩膜(自对准),

第三章 集成电路工艺基础及版图设计

注入层:这些层并不明确地规定一个新的分层或者接触, 而是去定制或改变已经存在的导体层的性质。

绘图层:制版工艺所要求的最小数目的层 掩模层:生成光学掩膜

隔离层:隐含于掩模层之中

绘制的图形的方式——“多边形”(polygon)和“线形” (path)

第三章 集成电路工艺基础及版图设计

第三章 集成电路工艺基础及版图设计

定义线形时,它的顶点规定了其中心线(或边界

线),再用一个附加的变量来规定其宽度,同样能够

按90度角、45度角或手绘角度等方式来绘制。 用多个线形生成版图是线形的一种有效应用方式。 只要确定了所要求的形状,就可以将线形展平开来, 由此得到多边形。

第三章 集成电路工艺基础及版图设计

确定晶体管的基底区域

形成并绘制多晶硅栅的图案

确定有源区

为接触孔开孔(对每个互连层都如此操作)

确定互连层(对每个互连层都如此操作)

用钝化层覆盖芯片

为连线绑定形成钝化层开孔

第三章 集成电路工艺基础及版图设计

第三章 集成电路工艺基础及版图设计

3.2分层和连接

导体:这些层是导电层,因为它们能够传送信号电压。 扩散层、金属层、多晶层以及阱层都属于此类。

第三章 集成电路工艺基础及版图设计

金属(USS) 场氧化层 (b ) P+ N- Si 多晶硅(Uin )

金属(Uou t) 金属(UDD )

N+

P阱

薄 氧 化 层 (栅 氧 化 层 )

图3 - 6 反向器版图及结构剖面图 (a) 版图; (b) 结构剖面图

第三章 集成电路工艺基础及版图设计

硅晶圆

掩膜版1: 用来规定P阱的形状、 大小及位置。 掩膜版2: 用于确定薄氧化层。 掩膜版3: 用来刻蚀多晶硅, 形成多晶硅栅极及 多晶硅互连线。 掩膜版4: 确定需要进行离子注入形成P+的区域。

第三章 集成电路工艺基础及版图设计

掩膜版5: 用来确定需要进行掺杂的N+区域, 由 图3 -4(e)可看出它实际上是P+掩膜版的负版, 即凡 不是P+的区域都进行N+掺杂, 包括NMOS管的栅区、 源区和漏区(实际上还应包括N型衬底的欧姆接触, 但图中并未画出)。 掺杂之后在硅片表面覆盖一层

的下面是很薄的一层 SiO2 , 称为栅氧, 两边较厚的

SiO2层称为场氧化层, 主要起隔离作用。 下面就以硅栅 NMOS 为例, 简要介绍硅栅 MOS 管

制造的基本工序(参照图3 -3)。

第三章 集成电路工艺基础及版图设计

源极金属引出

多晶硅栅极

漏极金属引出

N+ 场氧 源扩散区

栅氧

N+ 场氧 漏扩散区

第三章 集成电路工艺基础及版图设计

为了是SPICE能够精确地预测电路的复杂工 作过程,我们不仅需要设计规范和初始原理图, 还必须建立相关电路元件的数学描述。

第三章 集成电路工艺基础及版图设计

CMOS反相器的设计

在一定的工艺条件下,反相器的设计,关键是对晶体管的

尺寸(W/L)的设计,并由确定的沟道长度,获得沟道宽度

3.3晶体管版图简介

第三章 集成电路工艺基础及版图设计

3.3.1基底连接

第三章 集成电路工艺基础及版图设计

第三章 集成电路工艺基础及版图设计

3.3.2导体和接触孔

在业界,接触孔(contact)特指最低层金属孔,用于将 最低层金属和多晶硅或者扩散层连接起来;通孔(via)则是 指允许更高层金属进行相互连接的孔。

图3 - 4 CMOS工艺流程

第三章 集成电路工艺基础及版图设计

掩膜版 4

P+ (d ) 掩膜版 5

P+

N+

(e) 接触孔 掩膜版 6

N-Si (f) 金属电极 掩膜版 7

(g )

图3 - 4 CMOS工艺流程

第三章 集成电路工艺基础及版图设计

图3 - 4 中, 右边一列画出的是左边各主要步骤用

SiO2。

掩膜版6: 确定接触孔, 将这些位置处的SiO2刻 蚀掉。

掩膜版7: 用于刻蚀金属电极和金属连线。

第三章 集成电路工艺基础及版图设计

图3 -4(a)是反向器的版图, 图3 -6(b)是反向 器的剖面图。 需要说明的是: 为了防止闩锁效应的发 生, P阱必须接地, 衬底要接到UDD, 这只需在上面 掩膜版4、 掩膜版5、 掩膜版6中将括号内说明的未画 出的部分添加上去就可以了。 最后得到的结果是, N