第四章 习题解答

第4章 习题解答

第4章 习题与答案4-1作简谐振动的物体,每次通过同一位置时,不一定相同的量是 [ ] (A) 位移 ; (B) 速度 ; (C) 加速度; (D) 能量。

[答案:B ]4-2 把单摆摆球从平衡位置向位移正方向拉开,使摆线与竖直方向成一微小角度θ ,然后由静止放手任其振动,从放手时开始计时。

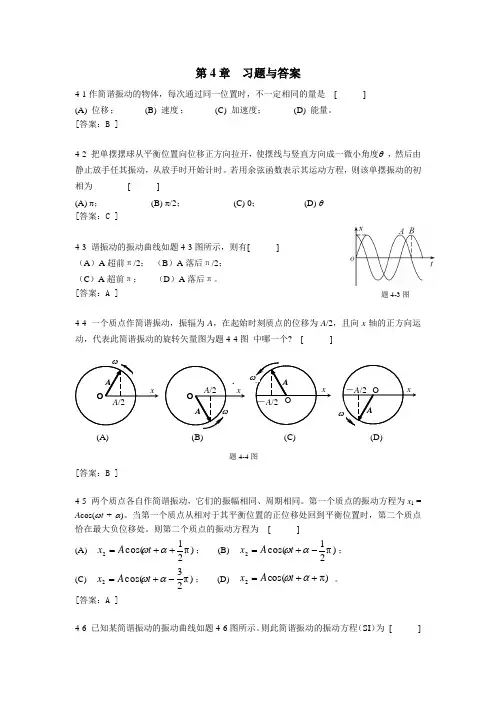

若用余弦函数表示其运动方程,则该单摆振动的初相为 [ ](A) π; (B) π/2; (C) 0; (D) θ [答案:C ]4-3 谐振动的振动曲线如题4-3图所示,则有[ ] (A )A 超前π/2; (B )A 落后π/2; (C )A 超前π; (D )A 落后π。

[答案:A ]4-4 一个质点作简谐振动,振辐为A ,在起始时刻质点的位移为A /2,且向x 轴的正方向运动,代表此简谐振动的旋转矢量图为题4-4图 中哪一个? [ ][答案:B ]4-5 两个质点各自作简谐振动,它们的振幅相同、周期相同。

第一个质点的振动方程为x 1 = A cos(ωt + α)。

当第一个质点从相对于其平衡位置的正位移处回到平衡位置时,第二个质点恰在最大负位移处。

则第二个质点的振动方程为 [ ] (A) )π21cos(2++=αωt A x ; (B) )π21cos(2-+=αωt A x ; (C) )π23cos(2-+=αωt A x ; (D) )cos(2π++=αωt A x 。

[答案:A ]4-6 已知某简谐振动的振动曲线如题4-6图所示。

则此简谐振动的振动方程(SI )为 [ ](A) 题4-4图题4-3图(A )220.02cos()33x t =π+π;(B )220.02cos()33x t =π-π;(C )420.02cos()33x t =π+π;(D )420.02cos()33x t =π-π。

[答案:C ]4-7 弹簧振子作简谐振动,先后以相同的速度依次通过A 、B 两点,历时1秒,质点通过B 点后再经过1秒又第二次通过B 点,在这2秒内质点通过的总路程为12cm ,则质点的振动周期和振幅分别为 [ ](A )3s 、12cm ; (B )4s 、6cm ; (C )4s 、9cm ; (D )2s 、8cm 。

原子物理学第四章习题解答

第四章习题解答4-1 一束电子进入1.2T 的均匀磁场时,试问电子的自旋平行于和反平行于磁场的电子的能量差为多大?解:∵磁矩为μu r 的磁矩,在磁场B u r中的能量为:U = -μu r ·B u r= -sz μ B电子自旋磁矩 sz μ=±B μ∴电子自旋平行于和反平行于磁场的能量差u =B μ B – (-B μB) =2B μ B ∴u = 2B μ B =2 ×0.5788×410-eV ·1T -× 1.2 T = 1.39 ×410- eV4-2 试计算原子处于23/2D 状态的磁矩μ及投影μz 的可能值. 解:由23/2D 可知 S=12 J=32L=2 ∴j g =32+12(1)(1)(1)S S L L J J +-++=32+121323223522⨯-⨯⨯=45又j μ=j g Bμ45B μ =1.55 B μ∴μ=1.55 B μ又,j z j j B m g μμ= 又3113,,,2222j m =--∴,142×255j z B B μμμ=±=±或,346×255j z B B μμμ=±=±即,6226(,,,)5555j z B μμ=--4-3 试证实:原子在63/2G 状态的磁矩等于零,并根据原子矢量模型对这一事实作出解释.解:由63/2G 可知:S =52 J = 32L = 4∴5745 31(1)(1)3122··03522(1)22×22JS S L LgJ J⨯-⨯+-+=+=+=+∴(1)0J j Bj j gμμ=+=即原子在63/2G状态的磁矩等于零。

解释:∵原子的总角动量为J L S=+u r u r u r,而处于63/2G态原子各角动量为:(1)4(41)20 4.47L L L=+=+==h h h h5535(1)(1) 2.9622S S S=+=+==h h h h3315(1)(1) 1.94222J J J=+=+==h h h h则它们的矢量关系如图示:Lu r和Su r同时绕Ju r旋进,相对取项保持不变由三角形余弦定理可知:22222211()[(1)(1)(1)]22L J L J S L L J J S S⋅=+-+++-+u r u rh h h=22355715[45]222222=⨯+⨯-⨯=hh而222221573515()(45)2222224S J S J L⋅=+-=⨯+⨯-⨯=-u r u r hh∴相应的磁矩2B BS Sg S Sμμμ=-=-u r u r u rh hB B Lg L L μμμ∆=-=-u ru r u r hhS L μμμ=+u r u ru r由于磁矩μu r 随着角动量绕J u r 旋进,因而对外发生效果的是μu r在J u r 方向上的分量。

功和能习题解答

第四章 功和能一 选择题1. 一辆汽车从静止出发,在平直公路上加速前进时,若发动机功率恒定,则正确的结论为:( )A. 加速度不变B. 加速度随时间减小C. 加速度与速度成正比D. 速度与路径成正比 解:答案是B 。

简要提示:在平直公路上,汽车所受阻力恒定,设为F f 。

发动机功率恒定,则P =F v ,其中F 为牵引力。

由牛顿运动定律得a m F F =-f ,即:f F P/m -v a =。

所以,汽车从静止开始加速,速度增加,加速度减小。

2. 下列叙述中正确的是: ( ) A. 物体的动量不变,动能也不变. B. 物体的动能不变,动量也不变. C. 物体的动量变化,动能也一定变化. D. 物体的动能变化,动量却不一定变化. 解:答案是A 。

3. 一颗卫星沿椭圆轨道绕地球旋转,若卫星在远地点A 和近地点B 的角动量与动能分别为L A 、E k A 和L B 、E k B ,则有:( )A. L B > L A , E k B > E k AB. L B > L A , E k B = E k AC. L B = L A , E k B > E k A地球BA选择题3图D. L B = L A , E k B = E k A 解:答案是C 。

简要提示:由角动量守恒,得v B > v A ,故E k B > E k A 。

4. 对功的概念有以下几种说法:(1) 保守力作正功时,系统内相应的势能增加. (2) 质点运动经一闭合路径,保守力对质点作的功为零.(3) 作用力和反作用力大小相等、方向相反,所以两者所作功的代数和必为零. 在上述说法中: ( )A. (1)、(2)是正确的;B. (2)、(3)是正确的;C. 只有(2)是正确的;D. 只有(3)是正确的. 解:答案是C 。

5. 如图所示,足够长的木条A 置于光滑水平面上,另一木块B 在A 的粗糙平面上滑动,则A 、B 组成的系统的总动能:( )A. 不变B. 增加到一定值C. 减少到零D. 减小到一定值后不变 解:答案是D 。

弹性力学(徐芝纶)第四章习题答案

第四章 习题解答4-14-2、解:本题为轴对称应力问题,相应的径向位移为: ()()()()()θ+θ+⎥⎦⎤⎢⎣⎡υ-+υ-+-υ-+υ+-=sin cos ln K I Cr 12Br 311r Br 12r A 1E 1u r (1) 轴对称应力通式为()()02ln 232ln 2122=+++-=+++=θθτσσr r C r B rAC r B r A由应力边界条件()()()()0,00,===-=====b r r b r r a r r a r r q θθτστσ并结合位移单值条件可知B=0,求得:22222222ab qa C a b qb a A -=--= 因半径的改变与刚体位移I ,K 无关,且为平面应变问题,将A 、B 、C 代入(1)式,并将υυυυ-→-→1,12EE 得:内半径的改变:()()()⎪⎪⎭⎫⎝⎛-+-+-=⎥⎦⎤⎢⎣⎡-⎪⎭⎫ ⎝⎛--+-⎪⎭⎫ ⎝⎛-+-=∆=υυυυυυυυ11*111112222222222222a b a b Eqa a a b qa a a b q b a E u ar r外半径的改变:()()()2222222222221*11111a b ab E qa b a b qa b a b q b a Eu br r --=⎥⎦⎤⎢⎣⎡-⎪⎭⎫ ⎝⎛--+-⎪⎭⎫ ⎝⎛-+-=∆=υυυυυυ 圆筒厚度的改变:()()()⎪⎪⎭⎫⎝⎛-++---=∆-∆=∆==υυυ112a b a b E qa u u R ar r b r r4-2另解:半径为r 的圆筒周长为r π2,受载后周长则为 ()θθεπεππ+=+1222r r r , 于是半径为 ()θε+1r ,半径的改变量则为:⎥⎦⎤⎢⎣⎡⎪⎭⎫ ⎝⎛+--⎪⎭⎫ ⎝⎛+--=⎪⎭⎫⎝⎛---=C r A C rA r E E r r r 212111*2222υυυσυυσυεθθ将对应的A 、C 及r=a,b 分别代入,可求出内外半径的改变及圆筒厚度的改变。

(解答)《随机过程》第四章习题

第四章 二阶矩过程、平稳过程和随机分析 习题解答1、 设∑=-=Nk k k kn U n X 1)cos(2ασ,其中k σ和k α为正常数,)2,0(~πU U k ,且相互独立,N k ,,2,1 =,试计算},1,0,{ ±=n X n 的均值函数和相关函数,并说明其是否是平稳过程。

解:计算均值函数和相关函数如下0)}{cos(2)cos(2}{)(11=-=⎭⎬⎫⎩⎨⎧-==∑∑==Nk k k k N k k k k n X U n E U n E X E n ασασμ∑∑∑∑∑∑======-=--=--=⎪⎭⎪⎬⎫⎪⎩⎪⎨⎧⎥⎦⎤⎢⎣⎡-⋅⎥⎦⎤⎢⎣⎡-=Ni i i N i i i i i i Ni Nj j j i i j i N j j j j N i i i i X m n U m U n E U m U n E U m U n E m n R 12121111)](cos[)}cos(){cos(2)}cos(){cos(2)cos(2)cos(2),(ασαασαασσασασ因此可知,},1,0,{ ±=n X n 是平稳随机过程。

2、 设有随机过程))(cos()(t t A t X πηω+=,其中0>ω为常数,}0),({≥t t η是泊松过程,A 是与)(t η独立的随机变量,且2/1}1{}1{===-=A P A P 。

(1) 试画出此过程的样本函数,并问样本函数是否连续? (2) 试求此过程的相关函数,并问该过程是否均方连续? 解:(1)样本函数不连续。

(2)令:012≥>t t ,下面求相关函数:)(221)(212210)(1212211212121211212212122112221122121121212cos cos )]}(cos[)]({cos[21!)]([)]}(cos[)]({cos[)1(21))]}()(()(cos[))]()(()(2)({cos[21))]}()(()(cos[))]()(()({cos[21))}(cos())({cos(}{))}(cos())(cos({)}()({),(t t t t k t t k kX e t t e t t t t e k t t t t t t t t t t t t t t t E t t t t t t t t E t t t t E A E t t t t A E t X t X E t t R ----∞=--⋅=⋅-++=⋅-⋅-++-=-+-+-+++=-+-++++=++⋅=++==∑λλλωωωωλωωηηπωηηππηωηηπωηηπωπηωπηωπηωπηω因为:t t t R ωξ2cos ),(=因此该过程是均方连续的随机过程。

第4章 习题解答

第4章 周期信号的频域分析习题详解4-1 试比较题4-1图所示的四种周期方波信号,说明每种信号的对称特性并写出Fourier 级数展开式。

tt(b)tt-A(c) (d)题4-1图【解】 (a))(14/4/04/4/000T jn T jn tjn T T n eejnT A dt AeTc ωωωω----==⎰)2/(Sa )2/()2/sin(πππn A n n A ==所以 tjn n a e n A t f 0)2/(Sa )2/()(ωπ∑∞-∞==000211/2cos()cos(3)cos(5)35A A t t t ωωωπ⎛⎫=+-+- ⎪⎝⎭)(t f a 实偶对称,Fourier 级数展开式中只含有直流分量与余弦分量。

)(t f a 减去直流分量后为半波镜像信号,Fourier 级数展开式中只有奇次谐波。

(b) 从图形观察:)4/()(T t f t f a b -=所以 )(t f b )2/(0)2/(Sa )2/(πωπn t n j n en A -∞-∞=∑=000211/2sin()sin(3)sin(5)35A A t t t ωωωπ⎛⎫=++++ ⎪⎝⎭)(t f b 减去直流分量实奇对称,Fourier 级数展开式中只含有直流分量与正弦分量。

)(t f b 减去直流分量后为半波镜像信号,Fourier 级数展开式中只有奇次谐波。

(c) 从图形观察:A t f t f a c -=)(2)(第4章 周期信号的频域分析 83所以 tjn n n c en A t f 0)2/(Sa )(0,ωπ∑∞≠-∞==000411c o s ()c o s (3)c o s (5)35A t t t ωωωπ⎛⎫=-+- ⎪⎝⎭)(t f c 实偶对称,且是半波镜像信号,Fourier 级数展开式中只含有奇次谐波的余弦分量。

(d) 从图形观察:)4/()(T t f t f c d -=所以 )2/(0,0)2/(Sa )(πωπn t n j n n d en A t f -∞≠-∞=∑=000411sin()sin(3)sin(5)35A t t t ωωωπ⎛⎫=++- ⎪⎝⎭)(t f d 实奇对称,且是半波镜像信号,Fourier 级数展开式中只含有奇次谐波的正弦分量。

大学电路习题第4章

第四章(电路定律)习题解答一、选择题1.受控源是不同于独立源的一类电源,它一种激励。

A.是; b.不是2.下列电路定理、定律中,仅能用于线性电路的有。

A.KVL 和KCL ; B.叠加定理;C.替代定理; D.戴维南定理和诺顿定理3.甲乙两同学对图4—1所示电路应用替代定理求电流I 。

甲画了图4—2(a )电路,乙画了图4—2(b )电路,后来他们认为图是不可行的,其理由是。

A.不满足“置换前后电路应具有唯一解”这一条件;B.电路中不存在电阻;C.电流等于零了;D.电流等于无限大了4.图4—3所示电路的诺顿等效电路如图4—4,则s I 、eq G 分别为。

a.S 403A 1,;b.S 340A 1,;c.S 403A 2,;d.S 103A 2,5.图4—5(a )所示电路的端口特性如图4—5(b ),其戴维南等效电路如图4—5(c ),则oc u 、i R 分别为。

A.Ω-20V 20,;B.Ω20V 20,;C.Ω-20V 20,; C.Ω10V 10,二、填空题1.线性一端口电路N 如图4—6所示。

当0=R 时,A 5=i ;当∞→R 时V 10=u 。

如果Ω=5R ,则=u ,=i 。

2.图4—7所示电路中,N 为线性电路,且Ω=10R 。

当0=s u ,0=s i 时,V 5=u ;当A 2=s i ,0=s u 时,V 8=u ;当0=s i ,V 10=s u 时,V 6=u 。

那么,当A 6=s i ,V 4=s u 时,=i 。

3.图4—8(a )所示电路的戴维南等效电路如图4—8(b ),那么=s U ,=eq R 。

4.图4—9(a )所示电路的戴维南等效电路如图4—9(b ),则=s U ,=eq R 。

5.在图4—10(a )所示的电路中,i u 1024-=(i 的单位用安培时,u 的单位为伏特),其戴维南等效电路如图4—10(b ),则=s u ,=0R 。

三、计算题1.用叠加定理计算图4—11所示电路中的u 。

计算机系统结构 第四章(习题解答)

1. 假设一条指令的执行过程分为“取指令”、“分析”和“执行”三段,每一段的时间分别是△t 、2△t 和3△t 。

在下列各种情况下,分别写出连续执行n 条指令所需要的时间表达式。

⑴ 顺序执行方式。

⑵ 仅“取指令”和“执行”重叠。

⑶ “取指令”、“分析”和“执行”重叠。

答:⑴ 顺序执行方式12 ......1 2 12T =∑=++n1i i i i )t t t (执行分析取址=n(△t +2△t +3△t)=6n △t⑵ 仅“取指令”和“执行”重叠12 ......1 212T =6△t +∑=+1-n 1i i i )t t (执行分析=6△t +(n-1)(2△t +3△t)=(5n +1)△t⑶ “取指令”、“分析”和“执行”重叠12 34 ......1 2 3 41234△t2△t3△t△t2△t3△t△t2△t3△tT =6△t +∑=1-n 1i i )t (执行=6△t +(n-1)(3△t)=(3n +3)△t2. 一条线性流水线有4个功能段组成,每个功能段的延迟时间都相等,都为△t 。

开始5个任务,每间隔一个△t 向流水线输入一个任务,然后停顿2个△t ,如此重复。

求流水线的实际吞吐率、加速比和效率。

答:1 2 3 4 5 6 7 8 9 10 11 12 13 14 15...1 2 3 4 5 6 7 8 9 10 11 12 13 14 151 2 3 4 5 6 7 8 9 10 11 12 13 14 15 1 2 3 4 56 7 8 9 10 11 12 13 14 151 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23我们可以看出,在(7n+1)Δt 的时间内,可以输出5n 个结果,如果指令的序列足够长(n →∞),并且指令间不存在相关,那么,吞吐率可以认为满足:)n (t75t )n /17(5t )1n 7(n 5TP ∞→∆=∆+=∆+=加速比为:)n (720n /17201n 7n 20t )1n 7(t 4n 5S ∞→=+=+=∆+∆⨯=从上面的时空图很容易看出,效率为:)n (75n /1751n 7n 5t )1n 7(4t 4n 5E ∞→=+=+=∆+⨯∆⨯=3. 用一条5个功能段的浮点加法器流水线计算∑==101i i A F 。

概率论与数理统计统计课后习题答案-总主编-邹庭荣-主编-程述汉-舒兴明-第四章

概率论与数理统计统计课后习题答案-总主编-邹庭荣-主编- 程述汉-舒兴明-第四章第四章习题解答11 •设随机变量X〜B (30,-),则E (X)=( D ).6A.-;D.5.1E (X) = np = 30 562 •已知随机变量X和Y相互独立,且它们分别在区间[-1 , 3]和[2, 4]上服从均匀分布,则E(XY)=( A ).A. 3;B. 6;C. 10;D. 12.E(X) =1 E(Y) =3因为随机变量X和Y相互独立所以E(XY) = E(X)E(Y) = 33.设X表示10次独立重复射击命中目标的次数,每次射中目标的概率为0.4,贝U X2的数学期望E(X 2) = 1&4 .X LI B(10,0.4) E(X) =4 D(X) =2.42 2E(X ) =(E(X)) D(X) =18.44.某射手有3发子弹,射一次命中的概率为-,如果命中了就停止射击,3否则一直射到子弹用尽.设表示X耗用的子弹数.求E (X).解:X123P2/32/91/92 2 1 13E(X)=—十—:2 +3 9 9 95 .设X的概率密度函数为x, 0ExE1f (x) - x, 1 :: x 乞2[0, 其它求 E(X) , E(X2).解: E(X) = J xf(x)dx = J x2dx + J x(2-x)dx =1,0 ' 11 32 27f (x)dx x dx 亠 i x (2「x)dx .- -bo -E(X 2)「;x 2求 E(X) , E(Y),E(XY).解:X-12P 0.650.35E(X)二「0.65 0.35 2 =0.05 .Y-112P0.40.250.35E(Y) = -0.4 0.25 1 0.35 2 =0.55E(XY)=(-1) (-1) 0.25 (-1) 1 0.1 (-1) 2 0.32 (-1) 0.15 2 1 0.15 2 2 0.05 =-0.257 •设二维随机向量(X, Y)的联合概率密度为求(1)E(X Y); (2) E(XY).E(XY) = _;.;(xy)f(x,y)dxdy=讥(广(xy)「dy)dx = 38.设随机变量X与Y相互独立,且D(X)=1, D(Y)=2 , J则D(X-Y)= 3 .D(X _Y) = D(X) D(Y) =39.设正方形的边长在区间]0, 2]服从均匀分布,则正方形面积A=X2的f(x,y)二e0,1°,0 :x y其它解: y) dxdy( x x y )e y d y dx 3方差为64/45 _________ .4 1E(X)=1, D(X) ,12 3X的密度函数f(x)= 102,0乞x乞26 •设随机向量(X, Y)的联合分布律为:E(X Y)=二y)求 D(X ),D(Y ),D(X-Y ).解:由本章习题5知E(X)=1 , E(X 2)=7,于是有62 21D(X)二 E(X )-(E(X)).6221 4E (XTE (X)「D (X)n 〒.4"be 42E(X )= x f(x)dx = 01 4 16x dx =2 5D(X 2) =E(X 4)—[E(X 2)]210•设随机变量X 的分布律为X -1 0 1 2P1/5 1/2 1/5 1/10求 D(X).解:D(X) = E(X 2) -(E(X))2, E(X2 21 2 1 2E(X ) =(-1) -01- 2 551 19 224D(X)=E (X 2)-(E(X))2=5 25 2511•设随机变量X 的概率密度函数为f(x)亠1,求 D(X ).::1I解:E(X) xf (x) dxxe*dx=0, 2E(X 2)x 2f(x)dx=2 x 2e^dx = 2 ,0 212•设随机变量X , Y 相互独立,其概率密度函数分别为x,f x (x)二 2 -x,0 _x _1 1 :: x _ 2y_ 0其它16 564 45由Y LI E(1)知 E(X) =D(X) =1.由于随机变量X , Y 相互独立,所以D(X -Y)二 D(X) D(Y) =7.613•设 D(X)=1,D(Y)=4,相关系数 P XY =0.5,则 cov(X,Y)=_1 __________ covX,Y)= » D(X)D(Y) =114•设二维随机变量(X, Y )的联合密度函数为求 cov(X,Y ), ?XY •DJI nI 22。

模电第四章答案

第四章习题解答4-1如题4-1图所示MOSFE转移特性曲线,说明各属于何种沟道?若是增强型,开启电压等于多少?若是耗尽型,夹断电压等于多少?答:(a)P-EMOSFET,开启电压V GSM2V(b)P-DMOSFET,夹断电压V Gsoff (或统称为开启电压V GS Q 2V(c)P-EMOSFET,开启电压V Gsth 4V(d)N-DMOSFET,夹断电压V GS Off (或也称为开启电压V GS Q4V4-2 4个FET的转移特性分别如题4-2图(a)、(b)、(c)、(d)所示。

设漏极电流i D的实际方向为正,试问它们各属于哪些类型的FET?分别指出i D的实际方向是流进还是流出?答:(a)P-JFET,i D的实际方向为从漏极流出。

(b)N-DMOSFET,i°的实际方向为从漏极流进。

(c)P-DMOSFET,i D的实际方向为从漏极流出。

(d)N-EMOSFET, i D的实际方向为从漏极流进。

4-3 已知N 沟道EMOSFET 的卩n C ox=100y A/V2,V GS(th)=0.8V, W/L=10,求下列情况下的漏极电流:(a)V GS=5V,V DS=1V ; (b)V GS=2V,V DS=1.2V ;(c)V GS=5V,V DS=0.2V; (d)V GS=V DS=5V。

解:已知N-EMOSFET 的n C ox 100 A/V2, V GSth 0.8V W L 10(a)当V GS 5V,V DS 1V 时,MOSFET 处于非饱和状态V°s V GS V GS thI D /2V GS V Gsth V DS V2DS今0.1mA V2 102 5 0.8 1 12 3.7mA(b)当V GS2V,V DS 1.2V 时,J S V GS th 1-2V V DS,MOSFET 处于临界饱和I D i n C ox ¥V GS V GS th 弓0.1叫 2 10 2 0.8 20.72mA(c)当V GS5V,V DS0.2V 时,% V GS th 4.2V V DS,MOSFET 处于I D ; nC oxWL 2V GSV GS th J SV DS4 0.1mA V 2 1025 0.80.2 0.220.82mA(d )当 V GSV DS5V 时,V DSV GSV GS th,MOSFET 处于饱和状态1nC oxWV GS V GS th20.1mA v 2 105 0.8 2 8.82mA4-4 N 沟道 EMOSFET 的 V GS(th)=1V ,卩 n C ox (W/L ) =0.05mA/V 2,V GS =3V 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第四章习题解答

1.计算机存储系统由哪几部分构成,各有什么特点?

解答:3级存储器结构,即高速缓冲存储器(Cache)、内存储器和辅助存储器。

用Cache临时存放CPU最近一直在使用的指令和数据,以提高信息的处理速度。

与CPU 速度相当的静态随机存储器(SRAM)芯片组成,和内存相比,它存取速度快,但价格高,故容量较小。

内存用来存放计算机运行期间的大量程序和数据,多由MOS动态随机存储器(DRAM)芯片组成。

辅存是计算机最常用的输入输出设备,通常用来存放系统程序、大型文件及数据库等。

2.针对某intel 32位CPU,若其存储地址空间为0x00000~0x1ffff,那么该CPU访问地址为

0x03ff3的字型数据以及地址为0x03456的半字数据,分别需要多少个总线周期?

解答:intel 32位CPU存储地址空间分为4块,总线低2位地址信号无效。

0x03FF3对应bank3(低两位地址为11),则对该地址进行字类型数据访问需要2个总线周期:地址0x03ff0一次,此时BE3有效,得到字型数据的最低字节;地址0x03ff4一次,此时BE0,BE1,BE2有效,得到字型数据的高3个字节。

由0x3FF3,0x3FF4,0x3FF5,0x3FF6地址处的4个字节构成一个字

0x03456对应bank2(低两位地址为10),则对该地址进行半字类型数据访问只需要1个总线周期,即地址为0x03454时,BE2,BE3有效,一个总线周期得到半字数据。

3.在intel cpu的实地址模式下,假设程序代码段地址为0x0234,代码段中的某个标号偏移

地址为0x23,请问该标号的物理地址为多少?

解答:实地址模式物理地址的行程过程:

因此该标号的物理地址为:0x02340+0x23=0x02363

4.已知某32位intel微处理器的段描述符为0x3453002312890103,试指出该段描述符对应

的段的起始地址与结束地址。

解答:

段描述的构成结构如:

字节7字节5字节3字节1

字节0

字节2字节4字节6

段起始地址由字节7,字节4,字节3,字节2构成,因此为:0x34231289 段结束地址=段起始地址+段界限*段界限粒度-1

段界限为由字节6的低4位,字节,字节0构成,为0x30103 G=0,因此段界限粒度为1B ,由此可得到段的结束地址为: 0x34231289+0x30103-1=0x3426138C

5. 采用分段方式描述一个从

0x30000000开始到0x5fffffff 结束的段,试指出该段描述符的

段地址,界限以及G 分别为多少? 解答:段地址为0x3000 0000

段长度为:0x5FFF FFFF-0x3000 0000+1=0x3000 0000

段描述符的段界限为20位,段界限即取段长度的高20位,因此为:0x30000,由于此时段长度还剩余低12位,由此可知段界限描述的粒度为4KB ,因此G=1

6. 如果微处理器将逻辑地址0x00200000按分页机制处理,则会访问哪个页目录项以及哪

个页表项?

解答:

0x00200000的高10位为0,因此访问第0个页目录项(页表描述符);中间10位为0x200,

因此访问第512个页表项(页描述符)

7. 页目录中可以存放多少个32位地址?

解答:逻辑地址仅给出10位作为页目录的索引,因此仅可以存放210=1K 个32位地址

8. 页目录中每一项可把一个多大的线性存储空间转换为物理存储器空间?

解答:每一个页目录项指示一个页表的首地址,而一个页表可存储1K 个页描述符,每个页描述符可访问4KB 的地址空间,因此页目录中每一项可把一个4MB 的线性存储空间转换为物理存储器空间。

9. 高速缓存有哪几种映射策略,它们分别具有什么优缺点?

解答:

地址映象方法有:直接映像(Direct Mapped )、全相联(Full Associative )与组相联(Set Associative)。

直接映射:由于主存中某页的一块存入缓存时只能存入缓存中块号相同的位置,因此当访问主存时,可以直接根据cache 块索引,检查页号是否相等即可,因而可以得到比较快的访问速度,硬件设备简单。

但当对多个不同的页中处于同样块位置的数据访问比较频繁时就存在一个问题:需要不停的更换同一个cache 行的内容,因此cache 替换操作频繁,命中率比较低。

全相联映射:由于可以实现任意映像,因此其优点是cache块的利用率高,块冲突的概率低,命中率高。

但是当CPU访问内存时,每次都要与cache中的全部标志比较,使得访问速度低,硬件成本高。

组相联映像:cache的访问部分采用地址直接映像——根据内存地址中的组号可以直接获得对应到cache中的组,再结合比较高位地址标志,从而使得这种查找仅限定在相应的组内,相比全相联映像方式加快了cache的访问速度。

但是仍然需要进行查找,因此实现难度比直接映像要高,但是块的利用率、命中率要比直接映像高。

10. 采用直接映射方式为一个1GB的内存空间设计一个高速缓存,要求高速缓存的每一块可以存储128个字节,共具有64块,试写出该高速缓存每一块的结构,并计算系统分别需要多少位地址线寻址高速缓存块内字节、块索引以及块匹配?

解答:系统地址总线位数:1GB的内存空间共需要30位地址信号才能访问到各个字节地址字节索引:高速缓存每块128字节,则需要7位地址信号才能访问到该块的各个字节,因此寻址块内字节需7位地址线

块索引:高速缓存共64块,则需要6位地址信号才能进行块索引

块匹配:30位地址除去块内字节索引,块索引地址信号剩余的地址信号即为块匹配的地址信号,因此为30-7-6=17位

11. 已知某cache 具有16 块,每块存储32 个字节数据(8 个字),试说明在直接映射,4路组相联,全相联映射方式下CPU 访问以下连续内存地址空间时:0,23,48,34,86,389,786,1024,789. 各种cache 未命中的次数。

并说明cache 的填充过程。

解答:直接映射内存地址由三部分构成:

都是6次未命中。