基于Quartus II的带计时器功能的秒表系统设计

根据QuartusII软件的数字时钟设计

full:out std_logic);

end component;

component scan6----------------------------------------------------------------元器件4

Port(clr,clk:in std_logic;

one :buffer std_logic_vector(3 downto 0);

ten :buffer std_logic_vector(3 downto 0);

full:out std_logic;

dout:buffer std_logic_vector(7 downto 0));

3.2.2 count60组件

由此提供分(秒)计数值,当分计数器计数到59再来一个脉冲信号秒计数器清零从新开始计数,而进位则作为小时计数器的计数脉冲,使小时计数器计数加1,同时分计数器在分设置时钟信号的响应下设置分计数器的数值。在count60组件中,个位(one)和十位(ten)分别计数,都设为二进制四位矢量形式,当个位从0计到9时,在下一个clk上升沿来临后,十位进1,个位变0,十位从0到5计数,在十位为5,个位9的时候,下一个上升沿来临后,十位个位都变0,进位full加1。因此在程序设计中需要两个进程process来分别完成计数,秒计数以1Hz的输入为触发信号,分计数以秒的full信号为触发信号。具体的count60的组件代码如下:

component div40M------------------------------------------------------------------元器件1

基于Quartus的数字秒表设计

EDA技术课程大作业设计题目:数字秒表设计姓名:学号:姓名:学号:姓名:学号:专业班级:级通信工程2013年1月2日数字秒表设计1. 设计背景和设计方案要求1.1设计背景经过一个学期对《EDA 技术实用教程》的学习,已经初步掌握了一些较为简单的EDA 应用实例。

本次实验我小组选择的课题是《数字秒表设计》。

1.1.1任务安排1.2设计原理和结构1.2.1秒表功能秒表的显示范围是00:00:00-59:59:99,显示精度为1ms ,其拥有可控的自动报警功能(可通过蜂鸣器控制模块的clk 端选择计数一小时后报时或者不报时,如想要报时则接通clk 端,反之clk 端断开,选择报时则计数达到一小时后蜂鸣器会响一声,否则蜂鸣器不响,)、可控的启动功能(通过计数器的start 端口来控制计数器的启动,也即控制数字秒表的启动)及数字秒表清零功能(通过控制计数器清零端来实现,当清零端为高电平时,计数器清零,也即数字秒表清零,否则秒表正常计数)。

1.2.2秒表结构秒表的物理结构比较简单,它主要由十进制计数器、六进制计数器、数据选择器、显示译码器蜂鸣器等组成。

此外,秒表还需有一个启动信号、清零信号及报时信号,以便实现对秒表的控制和有效应用(启动和清零信号及报时信号由使用者给出,设计时主要任务是将此外界信号的功能准确的通过数字秒表体现出来,也即,当使用者给出启动信号时数字秒表能够正常启动,上面已经给出,启动和清零的功能是通过将此信号送给计数器来实现的)。

1.2.3设计思路十进制计数器clk 端接石英晶体振荡器,选择振荡频率为1000HZ 。

则振荡一秒钟之后,十进制计数器进位输出端输出100个高电平信号,每个高电平信号表示1001s,也即10ms 。

然后将10ms 的信号接到下一个十进制计数器的clk 端,则10个此信号之后,输出一个高电平信号,也即每个高电平信号表示10 10=100ms 。

依此类推,通过选择不同的计数器,在进位输出端可分别得到10ms 、100ms 、1s 、10s 等进位信号。

基于QuartusII的同步计数器设计

基于QuartusII的同步计数器设计精心整理精心整理精心整理1.1软件介绍:Quartus II是Altera公司在21 世纪初推出的FPGA/CPLD开发环境,是Altera前一代FPGA/CPLD集成开发环境MAX+PLUS II的更新换代产品,其优点是功能强大、界面友好、使用便捷。

它支持原理图、VHDL、VerilogHDL以及AHDL等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

Quartus II支持Altera的IP内核,包含了LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性,加精心整理快了设计速度。

此外,Quartus II通过和DSP Builder工具与Matlab/Simulink的相结合,可以方便的实现各种DSP应用系统;支持Altera的片上可编程系统开发,集系统设计、嵌入式软件开发。

可编程逻辑设计于一体,是一个综合性的开发平台。

Quartus II有严格的设计流程,分为设计输入与约束、分析和综合、布局布线、仿真及编程与配置等。

本次仿真设计所用到的版本为Quartus II 9.0,其用户界面如下图所示:1.2 Verilog HDL语言概述:Verilog HDL即Verilog硬件描述语言,它主要应用于数字电路和系统设计、数字电路和系统仿真等,即利用计算机和相关软件对用Verilog HDL等硬件语言建模的复杂数字逻辑电路设计进行仿真验证,再利用综合软件将设计的数字电路自动综合,以得到符合功能需求并且在相应的硬件电路结构上可以映射实现的数字逻辑网表,然后布局布线,根据网表和选定的实现器件工艺特性自动生成具体电路,同时软件生成选定器件的延时模型,经过仿真验证确定无误后写入器件中,精心整理最终实现电路设计。

Verilog HDL语言不仅定义了语法而且对每个语法结构都定义了清晰的模拟、仿真语义。

基于FPGA的数字电子钟的设计与实现

基于FPGA的数字电⼦钟的设计与实现背景:本实验所有结果基于Quartus II 13.1 (64-bit)实现,实验过程采⽤⾃下⽽上⽬录⼀、基本功能设计与思路基本功能:能实现秒、分钟、⼩时的计数,计数结果清晰稳定的显⽰在 6 位数码管上。

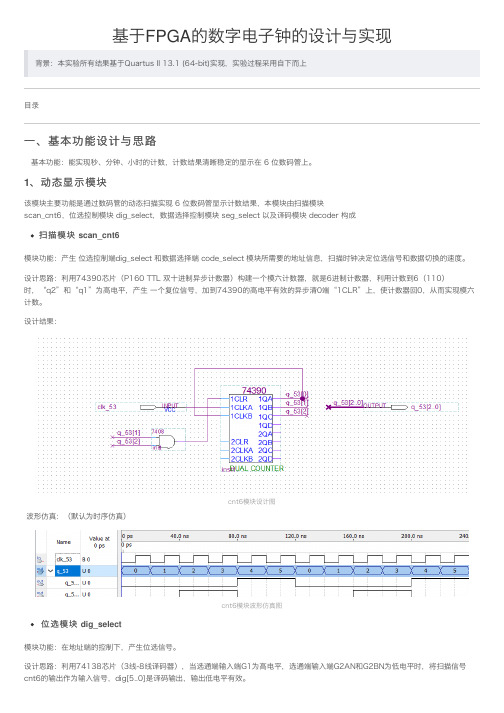

1、动态显⽰模块该模块主要功能是通过数码管的动态扫描实现 6 位数码管显⽰计数结果,本模块由扫描模块scan_cnt6,位选控制模块 dig_select,数据选择控制模块 seg_select 以及译码模块 decoder 构成扫描模块 scan_cnt6模块功能:产⽣ 位选控制端dig_select 和数据选择端 code_select 模块所需要的地址信息,扫描时钟决定位选信号和数据切换的速度。

设计思路:利⽤74390芯⽚(P160 TTL 双⼗进制异步计数器)构建⼀个模六计数器,就是6进制计数器,利⽤计数到6(110)时,“q2”和“q1”为⾼电平,产⽣ ⼀个复位信号,加到74390的⾼电平有效的异步清0端“1CLR”上,使计数器回0,从⽽实现模六计数。

设计结果:cnt6模块设计图波形仿真:(默认为时序仿真)cnt6模块波形仿真图位选模块 dig_select模块功能:在地址端的控制下,产⽣位选信号。

设计思路:利⽤74138芯⽚(3线-8线译码器),当选通端输⼊端G1为⾼电平,选通端输⼊端G2AN和G2BN为低电平时,将扫描信号cnt6的输出作为输⼊信号,dig[5..0]是译码输出,输出低电平有效。

设计结果:dig_select模块设计图波形仿真:dig_select模块波形仿真图数据选择模块 seg_select模块功能:输⼊ 6 组数据,每组数据 4bit,本模块完成在地址端的控制下从6 组数据当中选择 1 组输出。

设计思路:利⽤74151芯⽚(P91 8选1数据选择器),在控制输⼊端GN为低电平时,将扫描信号的选择下,分别选中D[5..0]对应的输⼊信号输出为Y。

基于QuartusII以及74ls192为核心的简易数字时钟设计

基于QuartusII以及74ls192为核心的简易数字时钟设计版权信息:重庆文理学院电子电气工程学院作者:电子信息科学与技术学生廖智星该项目是利用QuartusII软件设计一个数字钟,进行试验设计和仿真调试,实现了计时,校时,校分,保持和整点报时功能,并下载到FPGA实验系统中进行调试和验证。

此外还添加了显示星期,使得设计的数字钟的功能更加完善。

关键字:QuartusII EDA FPGA 数字钟 74ls192This experiment is to design a digital clock using QuartusII software, debugging test design and simulation, to achieve timing, timing, school hours, maintain and the whole point timekeeping function, and download the debugging and verification of FPGA experimental system. In addition also added that week, making digital clock design features more perfect.Keywords: QuartusII EDA FPGA 74LS192 digital clock目录1.设计要求 (1)2.工作原理 (1)3.各模块设计的说明 (2)4.实物效果 (7)5、总结 (11)一、设计要求1.设计一个数字计时器,可以完成00:00:00到23:59:59的计时功能,并在控制电路的作用下具有保持、调时的基本功能。

2.具体要求如下:1)能进行正常的时、分、秒计时功能,最大计时显示23小时59分59秒。

2)分别由7个数码管显示,前面6个进行时分秒的计时显示,最后一个。

基于QuartusⅡ的带计时器功能的秒表系统设计

基于QuartusⅡ的带计时器功能的秒表系统设计

郑亚民;许敏

【期刊名称】《电子工程师》

【年(卷),期】2005(31)1

【摘要】电子设计自动化(EDA)技术使得设计者可以利用硬件描述语言和EDA技术的工具软件实现系统硬件功能。

QuartusⅡ4.0是Altera公司推出的适用于不同设计对象的最新的EDA开发环境。

文中以QuartusⅡ4.0为设计平台,以现场可编程门阵列(FPGA)器件为核心,设计了一个具体数字系统即带计时器功能的秒表系统,使用QuartusⅡ4.0的综合器和仿真器对系统进行了编译和仿真,得出了正确的仿真结果。

【总页数】4页(P59-61)

【关键词】电子设计自动化(EDA);QuartusⅡ4.0;计时器;秒表系统

【作者】郑亚民;许敏

【作者单位】山东大学威海分校

【正文语种】中文

【中图分类】TP274

【相关文献】

1.基于EDA软件QuartusⅡ的数字秒表设计 [J], 钱虹凌

2.基于Quartus的16QAM调制系统设计 [J], 易阳;陈安;何雨东;宋晋

3.基于Quartus的16QAM调制系统设计 [J], 易阳;陈安;何雨东;宋晋;

4.基于Quartus Ⅱ的电子线束系统设计 [J], 王海霞

5.基于STC89C52单片机时间秒表计时器制作 [J], 杨盛兴;

因版权原因,仅展示原文概要,查看原文内容请购买。

基于-Quartus多功能数字钟设计

基于Quartus的多功能数字钟设计该实验是利用QuartusII软件设计一个数字钟,进展试验设计和仿真调试,实现了计时,校时,校分,清零,保持和整点报时等多种根本功能,并下载到SmartSOPC实验系统中进展调试和验证。

此外还添加了显示星期,闹钟设定,秒表和彩铃等附加功能,使得设计的数字钟的功能更加完善。

一、设计要求1.设计一个数字计时器,可以完成00:00:00到23:59:59的计时功能,并在控制电路的作用下具有保持、清零、快速校时、快速校分、整点报时等根本功能。

2.具体要求如下:1)能进展正常的时、分、秒计时功能,最大计时显示23小时59分59秒。

2)分别由六个数码管显示时分秒的计时。

3)K1是系统的使能开关,K1=0正常工作,K1=1时钟保持不变。

4)K2是系统的清零开关,K2=0正常工作,K2=1时钟的分、秒全清零。

5)在数字钟正常工作时可以对数字钟进展快速校时和校分。

K3是系统的校分开关,K3=0正常工作K3=1时可以快速校分;K4是系统的校时开关,K4=0正常工作,K4=1时可以快速校时。

3.设计提高局部要求1)时钟具有整点报时功能,当时钟计到59’51〞时开场报时,在59’51〞,59’53〞, 59’55〞,59’57〞时报时频率为512Hz,59’59〞时报时频率为1KHz。

2)星期显示:星期显示功能是在数字钟界面显示星期,到计时到24小时时,星期上显示的数据进一位。

3)闹表设定:通过开关切换显示至闹钟界面,利用闹钟校时和校分开关对闹钟时间进展设定,且不影响数字钟计时。

当计时到闹钟设定时间蜂鸣器鸣叫,并响起彩铃。

4)秒表计时:通过开关切换显示至秒表界面,分秒局部是100进制的,即当值为99时向秒位进位。

4.仿真与验证用Quartus软件对设计电路进展功能仿真,并下载到实验板上对其功能进展验证。

二、工作原理数字计时器是由计时电路、译码显示电路、脉冲发生电路和控制电路等几局部组成的,控制电路按要求可由校分校时电路、清零电路和保持电路组成。

根据QuartusII软件的数字时钟设计

根据QuartusII软件的数字时钟设计实验名称:数字时钟设计姓名:杨龙成班级:电子与通信工程学号: 3120302012 成绩:一、实验目的1.掌握各类计数器及它们相连的设计方法;2.掌握多个数码管显示的原理与方法;3.掌握模块化设计方式;4.掌握用VHDL语言的设计思想以及整个数字系统的设计。

二、实验内容1. 设计要求1)具有时、分、秒计数显示功能,在数码管显示00:00:00~23:59:59,以24小时循环计时。

2)完成可以计时的数字时钟时钟计数显示时有LED灯的花样显示。

3)具有调节小时、分钟及清零的功能。

4)具有整点报时功能。

2. 性能指标及功能设计1)时钟计数:完成时、分、秒的正确计时并且显示所计的数字;对秒、分60进制计数,时钟—24进制计数,并且在数码管上显示数值。

2)时间设置:手动调节分钟、小时,可以对所设计的时钟任意调时间。

可以通过实验板上的键7和键4进行任意的调整,因为时钟信号均是1HZ的,所以LED灯每变化一次就来一个脉冲,即计数一次。

3)清零功能:reset为复位键,低电平时实现清零功能,高电平时正常计数。

4)蜂鸣器在整点时有报时信号产生,产生“滴答.滴答”的报警声音。

5)根据进位情况,LED灯在时钟显示时有花样显示信号产生。

3. 系统方框图三、设计原理和过程3.1 硬件设计本设计使用VHDL硬件开发板,可编程逻辑器件EMP1270T144C5系列。

设计过程中用到的外围电路的设计有电源部分,可编程器件EMP1270T144C5,CPLD –JTAG接口,晶振和蜂鸣器,LED数码管显示,DIP开关与按键输入(具体电路见附录)3.2 软件设计3.2..1 程序包my_pkg的设计说明为了简化程序设计增加可读性,系统采用模块化的设计方法,重复使用的组件以元件(component)的形式存在,以便相关块的调用。

下面列出my_pkg组件包的代码。

library ieee;use ieee.std_logic_1164.all;package my_pkg iscomponent div40M------------------------------------------------------------------元器件1 Port( clk: in std_logic;f1hz : out std_logic);end component;component count60-----------------------------------------------------------------元器件2 Port(clr,clk:in std_logic;one :buffer std_logic_vector(3 downto 0);ten :buffer std_logic_vector(3 downto 0);full:out std_logic;dout:buffer std_logic_vector(7 downto 0));end component;component count24-----------------------------------------------------------------元器件3 Port(clr,clk:in std_logic;one :buffer std_logic_vector(3 downto 0);ten :buffer std_logic_vector(3 downto 0);full:out std_logic);end component;component scan6----------------------------------------------------------------元器件4 port (clr,clk : in STD_LOGIC;h_ten,h_one,m_ten,m_one,s_ten,s_one: in STD_LOGIC_vector(3 downto 0);cs: out STD_LOGIC_vector(5 downto 0);mux_out: out STD_LOGIC_vector(3 downto 0));end component;component bin2led---------------------------------------------------------------元器件5 port (bin : in std_logic_vector (3 downto 0);led : out std_logic_vector (7 downto 0) );end component;component sh1k ----------------------------------------------------------------------元器件6 Port( clk: in std_logic;--from system clock(40MHz)f1hz : out std_logic);-- 1Hz output signalend component;component alarm_set------------------------------------------------------------------元器件7 Port(rst,hz1: in std_logic;--system clock 1Hzalarm,ok: in std_logic;--keep pushing to declare alarm setsec_tune: in std_logic;sec_one,sec_ten:out std_logic_vector(3 downto 0));end component;end my_pkg;3.2.2 count60组件由此提供分(秒)计数值,当分计数器计数到59再来一个脉冲信号秒计数器清零从新开始计数,而进位则作为小时计数器的计数脉冲,使小时计数器计数加1,同时分计数器在分设置时钟信号的响应下设置分计数器的数值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于Quartus II的带计时器功能的秒表系统设计Quartus II是Altera 公司单芯片可编程系统(SOPC) 设计的综合性环境,也是适合SOPC的最全面的设计环境。

它拥有现场可编程门阵列(FPGA) 和复杂可编程逻辑器件(CPLD) 设计的所有阶段的解决方案。

与原来的Max + plus II相比,Quartus II 在界面和功能上都发生了不少变化,除承接了原来Max + plusII的全部设计功能和器件对象外,还增加了许多新功能,如支持Max + plusII界面,支持RTLView 等,还增加了新的FPGA 器件系列,包括一些适用于SOPC开发的大规模器件。

本文以Quartus II 4.0 为设计平台,以FPGA 为核心,设计了一个具体数字系统即带计时器功能的秒表系统,使用Quartus II 4.0 的综合器和仿真器对系统进行了编译和仿真,得出了正确的仿真结果。

1 秒表系统总体结构要设计一个带计时器功能的秒表,计时范围为0.01 s~1 h ,计时器初值以min 为单位,最长计时时间为59 min。

总体结构包括以下几个组成部分:a) 显示屏,由6 个七段数码管组成,用于显示计时时间。

b) 输入数字键,用于设置计时器的计时时间(以min 为单位,不超过1 h) 。

c) START 键,用于启动秒表计时。

d) RESET 键,用于计时清零(复位) 。

e) ALARM 键,用于启动秒表的计时器功能。

f) 扬声器,在计时器计时结束时发声报警。

设计的总体结构图如图1 所示,主要显示了内部连接关系。

1.1 秒表系统控制器控制器外部端口如图1 所示。

各端口的功能如下:a) CLK为外部时钟信号,RESET 为复位信号。

b) 当KEY为高电平( KEY= 1) 时,表示用户按下数字输入键。

c) 当START-DOWN 为高电平时,表示用户按下“START”键。

d) 当ALARM-DOWN 为高电平时,表示用户按下“ALARM”键。

e) ALARM-END 为计数器送来的计时完成信号,为高电平时表示计时结束。

f) CLR 为提供给计数器的复位信号。

g) 当CLOCK-START 输出为高电平时,控制时钟计数器开始计时。

h) 当LOAD-NEW-TIME 输出为高电平时,控制寄存器下载新的计时时间。

i) 当SHOW-NEW-TIME 输出为高电平时,控制显示电路显示新的时间值。

控制器的功能可以通过有限状态自动机( FSM)的方式来实现。

根据设计要求及端口设置,需要4 个状态来实现:a) S0 :电路初态即等待状态。

b) S1 :秒表工作状态即正常计时状态。

完成上述端口功能a 的工作,在状态S1 时用户按下START 键后进入此状态。

c) S2 :接收键盘输入状态。

在状态S0 或状态S1时用户按下数字输入键后进入此状态,此时将接收到的键盘输入信息在七段数码管上显示。

d) S3 :计时器工作状态。

在状态S2 时用户按下ALARM键后进入此状态,当计时完成后返回状态S0。

相应的状态转换及控制如表1 所示。

1.2 秒表系统时间计数器根据设计需要,要设计一个计时范围为0.01s~1 h 的秒表,命名为CLOCK。

首先需要获得一个比较精确的计时基准信号,这里是周期为1/100 s 的计时脉冲。

其次,除了对每一计数器需设置清零信号CLR输入外,还需在6 个计数器设置时钟使能信号,即计时允许信号ENA ,以便作为秒表的计时启停控制开关。

另外,为了完成计时器功能,需要一个控制减法计数功能的计时使能信号SET-TIME ,以作为计时器的启停控制开关。

因此,秒表可由1 个分频器(用来提供计时基准信号) 、4 个十进制计数器(1/100 s ,1/10 s ,1 s ,1min) 以及2 个六进制计数器(10 s ,10 min) 组成。

各部分组装完成后的时间计数器的外部端口如图1 所示。

各端口的功能如下:a) CLR 为复位信号,CLK 为外部输入的时钟信号。

b) CLOCK-START 为高电平时,启动秒表计时。

c) LOAD-NEW-TIME 为高电平时,表示启动计时器计时。

d) SET-TIME 为接收到的计时初始时间。

e) OUT-CLOCK为输出给其他器件的时钟信号,时钟周期为1/100 s。

f) DOUTL 为输出给显示驱动器的低16 位信号。

g) DOUTH 为输出给显示驱动器的高8 位信号。

1.3 接收键盘输入的缓冲器缓冲器命名为KEYPAD。

计时时间的输入利用两个按键分别代表1 min、10 min ,每按动一次,设置值加1 (相当于一个计数器,其最大值分别为9 、5) 。

其外部端口如图1 所示。

各端口的功能如下:a) SCLR 为复位信号。

b) KEY1 、KEY2 为接收到的键盘输入信号,只有高电平和低电平两种状态。

当输入一个上升沿时,计数加1 。

c) KEY为高电平时,表示有按键按下。

d) NEW-TIME 为转换后的计时时间。

1.4 显示驱动器本模块的功能是:当SHOW-NEW-TIME 端口输入信号有效(高电平) 时,根据NEW-TIME 端口输入信号(时间数据) 在DISPLAY 端口输出该信号。

当SHOW-NEW-TIME 端口输入信号无效(低电平) 时,根据TIME 端口的输入信号判断输出。

其外部端口如图1 中所示。

各端口的功能如下:a) CLR 为复位信号。

b) SHOW-NEW-TIME 为显示控制信号,为高电平时DISPLAY 的高8 位输出由端口NEW-TIME 引入的信号,为低电平时输出由TIME 引入的信号。

c) TIMEL 为由时间计数器引入的低16 位信号。

d) SOUND-ALARM 为高电平时,表示在计时器状态下计时结束。

1.5 计时时间寄存器本模块的功能是在时钟上升沿同步下, 根据LOAD-NEW-TIME 端口的输入信号控制TIME 端口的输出,当控制信号有效(高电平) 时,把NEW- TIME端口输入的信号值输出。

其外部端口如图1 所示。

各端口的功能如下:a) CLR 为复位信号,对TIME 端口的输出进行异步清零复位。

b) LOAD-NEW-TIME 为输出控制信号,为高电平时,TIME 端口将输出由端口NEW- TIME 引入的信号(时间数据) 。

c) TIME 为输出端口,输出时间数据。

1.6 整体组装前面已经完成了秒表系统各个组成部分的设计,下面把这些部分组装起来,形成完整的总体设计。

命名为TIMES ,其外部端口如图2 所示。

图2 秒表系统的外部端口各个输入输出端口的功能如下:a) CLK为外部时钟信号,CLR 为复位信号。

b) START 为高电平时,表示用户按下START键,秒表计时启动。

c) ALARM 为高电平时,表示用户按下ALARM键,用于确定新的计时器时间设置。

d) SET-KEY1 和SET-KEY2 ,用于接收用户输入的时间数据。

e) DISPLAY 实际上表示了6 个七段数码显示管,用于显示时间。

f) SOUND-ALARM-OUT 为高电平时,驱动扬声器发声,表示计时结束。

2 Quartus II4.0 的秒表系统整体仿真以上完成了秒表系统的VHDL 设计。

下面使用Quartus II4.0 对本设计进行编译和仿真。

首先创建工程,使用文本编辑器输入本设计的所有模块的源程序,把TIMES.VHD 设为顶层文件。

把本设计中的所有设计文件添加进工程后,先对每个模块进行编译纠错,然后进行全程编译,通过之后就可以进行仿真。

每一部分的仿真从略,下面只说明系统的整体仿真波形。

系统工作在秒表功能时的仿真波形如图3 所示。

图3 系统秒表功能的仿真波形图中,START 为高电平时,表示用户按下了START键,秒表开始计时。

这里把输出的DISPLAY 信号分成了6 组,每组代表秒表上的1 位。

由于DISPLAY0代表的是最低位,也就是百分之一秒,所以显示不清晰。

当接收到一个RESET 信号的高电平后时间清零,RESET 恢复低电平后,由于START 信号仍然为高电平,秒表重新开始计时。

系统工作在计时器功能时的仿真波形见图4 。

图4 系统计时器功能时的仿真波形图SET-KEY1 ,SET-KEY2 脉冲代表用户按下了数字输入键,有几个正脉冲就显示数字几。

开始时START先变为高电平,系统开始秒表计时;图中所示0.21 s后SET-KEY1 来了正脉冲,秒表由显示驱动器驱动显示正在设置的计时时间。

之后,ALARM 键变为高电平,计时器开始工作。

由图中可看出,用户设置的计时时间为43 min ,按下ALARM 键后,系统开始倒计时。

3 结束语我们根据秒表系统的设计要求,把整个系统分成了几个模块来进行设计,并通过VHDL 语言完成了具体程序的编写,使用Quartus II 4.0 对系统进行了分析、综合,编译、仿真等工作,通过整体仿真,可以看出完成后的系统满足设计要求。

整个设计充分利用了Quartus II4.0 的设计优势,简洁灵活,便于修改。