Lecture07_Single_Stub_Shunt_Tuning

W9812G2GB-6I中文资料

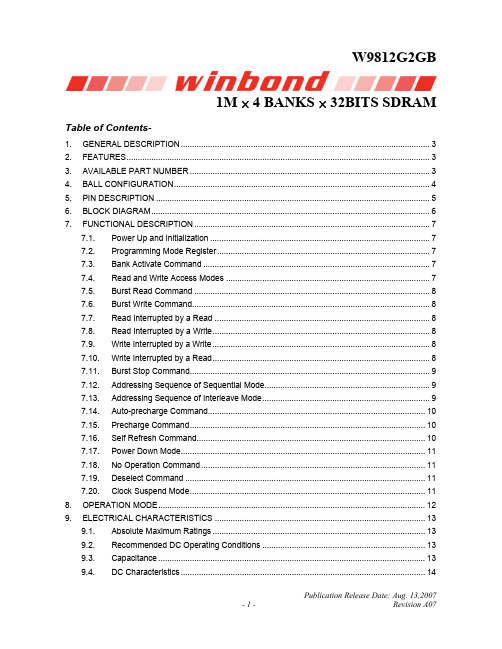

1M × 4 BANKS × 32BITS SDRAM Table of Contents-1.GENERAL DESCRIPTION (3)2.FEATURES (3)3.AVAILABLE PART NUMBER (3)4.BALL CONFIGURATION (4)5.PIN DESCRIPTION (5)6.BLOCK DIAGRAM (6)7.FUNCTIONAL DESCRIPTION (7)7.1.Power Up and Initialization (7)7.2.Programming Mode Register (7)7.3.Bank Activate Command (7)7.4.Read and Write Access Modes (7)7.5.Burst Read Command (8)7.6.Burst Write Command (8)7.7.Read Interrupted by a Read (8)7.8.Read Interrupted by a Write (8)7.9.Write Interrupted by a Write (8)7.10.Write Interrupted by a Read (8)7.11.Burst Stop Command (9)7.12.Addressing Sequence of Sequential Mode (9)7.13.Addressing Sequence of Interleave Mode (9)7.14.Auto-precharge Command (10)7.15.Precharge Command (10)7.16.Self Refresh Command (10)7.17.Power Down Mode (11)7.18.No Operation Command (11)7.19.Deselect Command (11)7.20.Clock Suspend Mode (11)8.OPERATION MODE (12)9.ELECTRICAL CHARACTERISTICS (13)9.1.Absolute Maximum Ratings (13)9.2.Recommended DC Operating Conditions (13)9.3.Capacitance (13)9.4.DC Characteristics (14)9.5.AC Characteristics and Operating Condition (15)10.TIMING WAVEFORMS (17)mand Input Timing (17)10.2.Read Timing (18)10.3.Control Timing of Input/Output Data (19)10.4.Mode Register Set Cycle (20)11.OPERATING TIMING EXAMPLE (21)11.1.Interleaved Bank Read (Burst Length = 4, CAS Latency = 3) (21)11.2.Interleaved Bank Read (Burst Length = 4, CAS Latency = 3, Auto-precharge) (22)11.3.Interleaved Bank Read (Burst Length = 8, CAS Latency = 3) (23)11.4.Interleaved Bank Read (Burst Length = 8, CAS Latency = 3, Auto-precharge) (24)11.5.Interleaved Bank Write (Burst Length = 8) (25)11.6.Interleaved Bank Write (Burst Length = 8, Auto-precharge) (26)11.7.Page Mode Read (Burst Length = 4, CAS Latency = 3) (27)11.8.Page Mode Read / Write (Burst Length = 8, CAS Latency = 3) (28)11.9.Auto-precharge Read (Burst Length = 4, CAS Latency = 3) (29)11.10.Auto-precharge Write (Burst Length = 4) (30)11.11.Auto Refresh Cycle (31)11.12.Self Refresh Cycle (32)11.13.Burst Read and Single Write (Burst Length = 4, CAS Latency = 3) (33)11.14.Power Down Mode (34)11.15.Auto-precharge Timing (Read Cycle) (35)11.16.Auto-precharge Timing (Write Cycle) (36)11.17.Timing Chart of Read to Write Cycle (37)11.18.Timing Chart of Write to Read Cycle (37)11.19.Timing Chart of Burst Stop Cycle (Burst Stop Command) (38)11.20.Timing Chart of Burst Stop Cycle (Precharge Command) (38)11.21.CKE/DQM Input Timing (Write Cycle) (39)11.22.CKE/DQM Input Timing (Read Cycle) (40)12.PACKAGE SPECIFICATION (41)12.1.TFBGA 90 Balls pitch=0.8mm (41)13.REVISION HISTORY (42)1. GENERAL DESCRIPTIONW9812G2GB is a high-speed synchronous dynamic random access memory (SDRAM), organized as 1,048,576 words × 4 banks × 32 bits. Using pipelined architecture and 0.11 µm process technology, W9812G2GB delivers a data bandwidth of up to 166MHz words per second (-6). For different application, W9812G2GB is sorted into two speed grades: -6/-6I and -75. The –6 is compliant to the 166MHz/CL3 specification (the -6I grade which is guaranteed to support -40°C ~ 85°C). The -75 is compliant to the 133MHz/CL3 specification.Accesses to the SDRAM are burst oriented. Consecutive memory location in one page can be accessed at a burst length of 1, 2, 4, 8 or full page when a bank and row is selected by an ACTIVE command. Column addresses are automatically generated by the SDRAM internal counter in burst operation. Random column read is also possible by providing its address at each clock cycle. The multiple bank nature enables interleaving among internal banks to hide the precharging time.By having a programmable Mode Register, the system can change burst length, latency cycle, interleave or sequential burst to maximize its performance. W9812G2GB is ideal for main memory in high performance applications.2. FEATURES• 3.3V ± 0.3V Power Supply•Up to 166 MHz Clock Frequency• 1,048,576 Words × 4 banks × 32 bits organization• Self Refresh Mode•CAS Latency: 2 and 3•Burst Length: 1, 2, 4, 8 and full page•Burst Read, Single Writes Mode•Byte Data Controlled by DQM•Auto-precharge and Controlled Precharge•4K Refresh cycles / 64 mS• Interface: LVTTL•Packaged in TFBGA 90 Ball•W9812G2GB is using lead free materials with RoHS compliant3. AVAILABLE PART NUMBERPART NUMBER SPEEDMAXIMUM SELFREFRESH CURRENTOPERATINGTEMPERATUREW9812G2GB-6 166MHz/CL3 2mA 0°C ~ 70°C W9812G2GB-6I 166MHz/CL3 2mA -40°C ~ 85°C W9812G2GB-75 133MHZ/CL3 2mA 0°C ~ 70°C4. BALL CONFIGURATION5. PIN DESCRIPTION6. BLOCK DIAGRAM7. FUNCTIONAL DESCRIPTION7.1. Power Up and InitializationThe default power up state of the mode register is unspecified. The following power up and initialization sequence need to be followed to guarantee the device being preconditioned to each user specific needs.During power up, all V DD and V DDQ pins must be ramp up simultaneously to the specified voltage when the input signals are held in the “NOP” state. The power up voltage must not exceed V DD +0.3V on any of the input pins or V DD supplies. After power up, an initial pause of 200 µS is required followed by a precharge of all banks using the precharge command. To prevent data contention on the DQ bus during power up, it is required that the DQM and CKE pins be held high during the initial pause period. Once all banks have been precharged, the Mode Register Set Command must be issued to initialize the Mode Register. An additional eight Auto Refresh cycles (CBR) are also required before or after programming the Mode Register to ensure proper subsequent operation.7.2. Programming Mode RegisterAfter initial power up, the Mode Register Set Command must be issued for proper device operation. All banks must be in a precharged state and CKE must be high at least one cycle before the Mode Register Set Command can be issued. The Mode Register Set Command is activated by the low signals of RA,S CAS, CS and WE at the positive edge of the clock. The address input data during this cycle defines the parameters to be set as shown in the Mode Register Operation table. A new command may be issued following the mode register set command once a delay equal to t RSC has elapsed. Please refer to the next page for Mode Register Set Cycle and Operation Table.7.3. Bank Activate CommandThe Bank Activate command must be applied before any Read or Write operation can be executed. The operation is similar to RAS activate in EDO DRAM. The delay from when the Bank Activate command is applied to when the first read or write operation can begin must not be less than the RAS to CAS delay time (t RCD). Once a bank has been activated it must be precharged before another Bank Activate command can be issued to the same bank. The minimum time interval between successive Bank Activate commands to the same bank is determined by the RAS cycle time of the device (t RC). The minimum time interval between interleaved Bank Activate commands (Bank A to Bank B and vice versa) is the Bank to Bank delay time (t RRD). The maximum time that each bank can be held active is specified as t RAS (max).7.4. Read and Write Access ModesAfter a bank has been activated, a read or write cycle can be followed. This is accomplished by setting S RCD delay. WE pin voltage level RAS high and CA low at the clock rising edge after minimum of tdefines whether the access cycle is a read operation (WE high), or a write operation (WE low). The address inputs determine the starting column address.Reading or writing to a different row within an activated bank requires the bank be precharged and a new Bank Activate command be issued. When more than one bank is activated, interleaved bank Read or Write operations are possible. By using the programmed burst length and alternating the access and precharge operations between multiple banks, seamless data access operation amongmany different pages can be realized. Read or Write Commands can also be issued to the same bank or between active banks on every clock cycle.7.5. Burst Read CommandThe Burst Read command is initiated by applying logic low level to CS and CAS while holding RAS and WE high at the rising edge of the clock. The address inputs determine the starting column address for the burst. The Mode Register sets type of burst (sequential or interleave) and the burst length (1, 2, 4, 8 and full page) during the Mode Register Set Up cycle. Table 2 and 3 in the next page explain the address sequence of interleave mode and sequential mode.7.6. Burst Write CommandThe Burst Write command is initiated by applying logic low level to CS, CAS and WE while holding RAS high at the rising edge of the clock. The address inputs determine the starting column address. Data for the first burst write cycle must be applied on the DQ pins on the same clock cycle that the Write Command is issued. The remaining data inputs must be supplied on each subsequent rising clock edge until the burst length is completed. Data supplied to the DQ pins after burst finishes will be ignored.7.7. Read Interrupted by a ReadA Burst Read may be interrupted by another Read Command. When the previous burst is interrupted, the remaining addresses are overridden by the new read address with the full burst length. The data from the first Read Command continues to appear on the outputs until the CAS Latency from the interrupting Read Command the is satisfied.7.8. Read Interrupted by a WriteTo interrupt a burst read with a Write Command, DQM may be needed to place the DQs (output drivers) in a high impedance state to avoid data contention on the DQ bus. If a Read Command will issue data on the first and second clocks cycles of the write operation, DQM is needed to insure the DQs are tri-stated. After that point the Write Command will have control of the DQ bus and DQM masking is no longer needed.7.9. Write Interrupted by a WriteA burst write may be interrupted before completion of the burst by another Write Command. When the previous burst is interrupted, the remaining addresses are overridden by the new address and data will be written into the device until the programmed burst length is satisfied.7.10. Write Interrupted by a ReadA Read Command will interrupt a burst write operation on the same clock cycle that the Read Command is activated. The DQs must be in the high impedance state at least one cycle before the new read data appears on the outputs to avoid data contention. When the Read Command is activated, any residual data from the burst write cycle will be ignored.7.11. Burst Stop CommandA Burst Stop Command may be used to terminate the existing burst operation but leave the bank open for future Read or Write Commands to the same page of the active bank, if the burst length is full page. Use of the Burst Stop Command during other burst length operations is illegal. The Burst Stop Command is defined by having RAS and CAS high with CS and WE low at the rising edge of the clock. The data DQs go to a high impedance state after a delay which is equal to the CAS Latency in a burst read cycle interrupted by Burst Stop.7.12. Addressing Sequence of Sequential ModeA column access is performed by increasing the address from the column address which is input to the device. The disturb address is varied by the Burst Length as shown in Table 2.Table 2 Address Sequence of Sequential Mode7.13. Addressing Sequence of Interleave ModeA column access is started in the input column address and is performed by inverting the address bit in the sequence shown in Table 3.Table 3 Address Sequence of Interleave Mode7.14. Auto-precharge CommandIf A10 is set to high when the Read or Write Command is issued, then the auto-precharge function is entered. During auto-precharge, a Read Command will execute as normal with the exception that the active bank will begin to precharge automatically before all burst read cycles have been completed. Regardless of burst length, it will begin a certain number of clocks prior to the end of the scheduled burst cycle. The number of clocks is determined by CAS Latency.A Read or Write Command with auto-precharge can not be interrupted before the entire burst operation is completed. Therefore, use of a Read, Write or Precharge Command is prohibited during a read or write cycle with auto-precharge. Once the precharge operation has started, the bank cannot be reactivated until the Precharge time (t RP) has been satisfied. Issue of Auto-precharge command is illegal if the burst is set to full page length. If A10 is high when a Write Command is issued, the Write with Auto-precharge function is initiated. The SDRAM automatically enters the precharge operation two clocks delay from the last burst write cycle. This delay is referred to as Write t WR. The bank undergoing auto-precharge can not be reactivated until t WR and t RP are satisfied. This is referred to as t DAL, Data-in to Active delay (t DAL = t WR + t RP). When using the Auto-precharge Command, the interval between the Bank Activate Command and the beginning of the internal precharge operation must satisfy t RAS (min).7.15. Precharge CommandThe Precharge Command is used to precharge or close a bank that has been activated. The Precharge Command is entered when CS, RAS and WE are low and CAS is high at the rising edge of the clock. The Precharge Command can be used to precharge each bank separately or all banks simultaneously. Three address bits, A10, BS0, and BS1, are used to define which bank(s) is to be precharged when the command is issued. After the Precharge Command is issued, the precharged bank must be reactivated before a new read or write access can be executed. The delay between the Precharge Command and the Activate Command must be greater than or equal to the Precharge time (t RP).7.16. Self Refresh CommandThe Self Refresh Command is defined by having CS, RAS, CAS and CKE held low with WE high at the rising edge of the clock. All banks must be idle prior to issuing the Self Refresh Command. Once the command is registered, CKE must be held low to keep the device in Self Refresh mode. When the SDRAM has entered Self Refresh mode all of the external control signals, except CKE, are disabled. The clock is internally disabled during Self Refresh Operation to save power. The device will exit Self Refresh operation after CKE is returned high. A minimum delay time is required when the device exits Self Refresh Operation and before the next command can be issued. This delay is equal to the t AC cycle time plus the Self Refresh exit time.If, during normal operation, AUTO REFRESH cycles are issued in bursts (as opposed to being evenly distributed), a burst of 4,096 AUTO REFRESH cycles should be completed just prior to entering and just after exiting the self refresh mode. The period between the Auto Refresh command and the next command is specified by t RC.7.17. Power Down ModeThe Power Down mode is initiated by holding CKE low. All of the receiver circuits except CKE are gated off to reduce the power. The Power Down mode does not perform any refresh operations, therefore the device can not remain in Power Down mode longer than the Refresh period (t REF) of the device.The Power Down mode is exited by bringing CKE high. When CKE goes high, a No Operation Command is required on the next rising clock edge, depending on t CK. The input buffers need to be enabled with CKE held high for a period equal to t CKS (min) + t CK (min).7.18. No Operation CommandThe No Operation Command should be used in cases when the SDRAM is in a idle or a wait state to prevent the SDRAM from registering any unwanted commands between operations. A No Operation Command is registered when CS is low with RAS, CAS, and WE held high at the rising edge of the clock. A No Operation Command will not terminate a previous operation that is still executing, such as a burst read or write cycle.7.19. Deselect CommandThe Deselect Command performs the same function as a No Operation Command. Deselect Command occurs when CS is brought high, the RAS, CAS, and WE signals become don’t cares.7.20. Clock Suspend ModeDuring normal access mode, CKE must be held high enabling the clock. When CKE is registered low while at least one of the banks is active, Clock Suspend Mode is entered. The Clock Suspend mode deactivates the internal clock and suspends any clocked operation that was currently being executed. There is a one clock delay between the registration of CKE low and the time at which the SDRAM operation suspends. While in Clock Suspend mode, the SDRAM ignores any new commands that are issued. The Clock Suspend mode is exited by bringing CKE high. There is a one clock cycle delay from when CKE returns high to when Clock Suspend mode is exited.8. OPERATION MODEFully synchronous operations are performed to latch the commands at the positive edges of CLK. Table 1 shows the truth table for the operation commands.Table 1 Truth Table (Note (1), (2))Notes:(1) v =valid x =Don’t care L =Low Level H =High Level(2) CKEn signal is input level when commands are provided.CKEn-1 signal is the input level one clock cycle before the command is issued.(3) These are state of bank designated by BS0, BS1 signals.(4) Device state is full page burst operation.(5) Power Down Mode can not be entered in the burst cycle.When this command asserts in the burst cycle, device state is clock suspend mode.9. ELECTRICAL CHARACTERISTICS9.1. Absolute Maximum RatingsRATINGUNIT PARAMETER SYMBOLInput/Output Voltage V IN, V OUT -0.3 ~ V DD +0.3 VPower Supply Voltage V DD, V DDQ-0.3 ~ 4.6 VOperating Temperature (-6/-75) T OPR0 ~ 70 °C°C85Operating Temperature (-6I) T OPR -40~°C150Storage Temperature T STG -55~Soldering Temperature (10s) T SOLDER 260 °CW Power Dissipation P D 1mA Short Circuit Output Current I OUT 50Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.9.2. Recommended DC Operating Conditions(Ta = 0 to 70°C for -6/-75, Ta= -40 to 85°C for -6I)UNIT PARAMETER SYMBOL MIN.MAX.TYP.Power Supply Voltage V DD 3.0 3.3 3.6 VPower Supply VoltageV DDQ 3.0 3.3 3.6 V(for I/O Buffer)V DD +0.3 VInput High Voltage V IH 2.0 -Input Low Voltage V IL -0.3 - 0.8 VNote: V IH(max) = V DD/ V DDQ+1.2V for pulse width < 5 nSV IL(min) = V SS/ V SSQ-1.2V for pulse width < 5 nS9.3. Capacitance(V DD= 3.3V, f = 1 MHz, Ta 25°C)Note: These parameters are periodically sampled and not 100% tested.9.4. DC Characteristics(VDD =3.3V± 0.3V, Ta = 0 to 70°C for-6/-75, Ta= -40 to 85°C for -6I)NOTESUNIT PARAMETER SYMBOL MIN.MAX.Input Leakage CurrentI I(L) -5 5 µA (0V ≤V IN≤ V DD, all other pins not under test = 0V)Output Leakage CurrentI O(L) -5 5 µA (Output disable , 0V ≤ V OUT≤ V DDQ)LVTTL Output ″H″ Level VoltageV OH 2.4 - V(I OUT = -2 mA )LVTTL Output ″L″ Level VoltageV OL - 0.4 V(I OUT = 2 mA )9.5. AC Characteristics and Operating Condition(VDD =3.3V ± 0.3V, Ta = 0 to 70°C for -6/-75, Ta= -40 to 85°C for -6I, Notes: 5, 6, 7, 8, 9, 10)-6/-6I -75PARAMETER SYM.MIN. MAX. MIN. MAX.UNIT NOTESRef/Active to Ref/Active Command Period t RC 60 65 Active to precharge Command Period t RAS 42 10000045 100000 nSActive to Read/Write Command Delay Timet RCD 18 20 Read/Write(a) to Read/Write(b) Command Periodt CCD 1 1 t CKPrecharge to Active Command Period t RP 18 20 Active(a) to Active(b) Command Period t RRD 12 15 nS CL* = 2 22 t CKWrite Recovery Time CL* = 3 t WR 22CL* = 2 101000101000CLK Cycle TimeCL* = 3t CK6 1000 7.5 1000CLK High Level widtht CH 2 2.5 9 CLK Low Level widtht CL 2 2.59CL* = 2 6 6 Access Time from CLKCL* = 3t AC 5 5.4 10 Output Data Hold Timet OH 3 3 10 Output Data High Impedance Time t HZ 3 6 3 7.5 8 Output Data Low Impedance Time t LZ 0 0 10 Power Down Mode Entry Time t SB 0 6 0 7.5Transition Time of CLK (Rise and Fall) t T 0.1 1 0.1 1 7 Data-in Set-up Time t DS 1.5 1.5 9 Data-in Hold Time t DH 1.0 1.0 9 Address Set-up Time t AS 1.5 1.5 9 Address Hold Time t AH 1.0 1.0 9 CKE Set-up Time t CKS 1.5 1.5 9 CKE Hold Time t CKH 1.0 1.0 9 Command Set-up Time t CMS 1.5 1.5 9 Command Hold Time t CMH 1.0 1.0nS9Refresh Timet REF 64 64 mS Mode register Set Cycle Time t RSC 12 15 nS Exit self refresh to ACTIVE commandt XSR72 75 nS*CL = CAS LatencyNotes:1. Operation exceeds “Absolute Maximum Ratings” may cause permanent damage to the devices.2. All voltages are referenced to V SS3. These parameters depend on the cycle rate and listed values are measured at a cycle rate with the minimum values of t CK and t RC .4. These parameters depend on the output loading conditions. Specified values are obtained with output open.5. Power up sequence is further described in the “Functional Description” section.6. AC Testing ConditionsPARAMETER CONDITIONSOutput Reference Level1.4VOutput LoadSee diagram belowInput Signal Levels (V IH /V IL ) 2.4V/0.4VTransition Time (t T : tr/tf) of Input Signal 1/1 nS Input Reference Level 1.4V7. Transition times are measured between V IH and V IL .8. t HZ defines the time at which the outputs achieve the open circuit condition and is not referenced to output level.9. Assumed input transition Time (t T ) = 1nS.If tr & tf is longer than 1nS, transient time compensation should be considered, i.e., [(tr + tf)/2-1]nS should be added to the parameter(The t T maximum can’t be more than 10nS for low frequency application.)10. If clock rising time (t T ) is longer than 1nS, (t T /2-0.5)nS should be added to the parameter.10. TIMING WAVEFORMS 10.1. Command Input Timing10.2. Read Timing10.3. Control Timing of Input/Output Data10.4. Mode Register Set Cycle11. OPERATING TIMING EXAMPLE11.1. Interleaved Bank Read (Burst Length = 4, CAS Latency = 3)11.2. Interleaved Bank Read (Burst Length = 4, CAS Latency = 3, Auto-precharge)11.3. Interleaved Bank Read (Burst Length = 8, CAS Latency = 3)11.4. Interleaved Bank Read (Burst Length = 8, CAS Latency = 3, Auto-precharge)11.5. Interleaved Bank Write (Burst Length = 8)11.6. Interleaved Bank Write (Burst Length = 8, Auto-precharge)11.7. Page Mode Read (Burst Length = 4, CAS Latency = 3)11.8. Page Mode Read / Write (Burst Length = 8, CAS Latency = 3)11.9. Auto-precharge Read (Burst Length = 4, CAS Latency = 3)11.10. Auto-precharge Write (Burst Length = 4)11.11. Auto Refresh Cycle11.12. Self Refresh Cycle11.13. Burst Read and Single Write (Burst Length = 4, CAS Latency = 3)11.14. Power Down Mode11.15. Auto-precharge Timing (Read Cycle)11.17. Timing Chart of Read to Write Cycle11.18. Timing Chart of Write to Read Cycle11.19. Timing Chart of Burst Stop Cycle (Burst Stop Command)11.20. Timing Chart of Burst Stop Cycle (Precharge Command)11.21. CKE/DQM Input Timing (Write Cycle)11.22. CKE/DQM Input Timing (Read Cycle)12. PACKAGE SPECIFICATION12.1. TFBGA 90 Balls pitch=0.8mmPublication Release Date:Aug. 13,2007- 41 - Revision A07Publication Release Date: Aug. 13,2007- 42 - Revision A0713. REVISION HISTORYVERSION DATEPAGEDESCRIPTIONA01 Mar. 24, 2006 All Create new datasheet A02 Jul. 05, 2006 8 Burst Stop commandA03 Sep. 08, 2006 10 Exit Auto refresh to next command is specified by t RC A04 Sep. 27, 200615,16Modify Characteristics Notes 9 and add Notes 10 (t T ) A05 Apr. 12, 2007 15,32,34,41Add t XSR timing specification and package dimension ball openingA06 Jun. 21, 2007 3,13,14,15Add -6I gradeA07 Aug. 13, 200716Revise transient time t T AC test condition and calculate formula for compensation consideration in Notes 6, 9 of AC Characteristics and Operating ConditionImportant NoticeWinbond products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Further more, Winbond products are not intended for applications wherein failure of Winbond products could result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.。

《操作系统导论》ostep_homework(Chapter26283031)

Chapter26首先查看相关汇编指令的含义:选项含义:26.1答:首先查看loop.s文件内容如下:运行以上命令,得到以下结果:使用“-c”选项运行命令查看答案,结果和上图一致,说明分析正确。

26.2答:分析以上命令可知“-t2”表示指定两个线程,“-i100”表示中断间隔为100,“-a dx=3,dx=3”表示指定线程0和线程1的dx均初始化为3,运行以上命令得以下运行结果:使用“-c”选项运行命令查看答案,结果和上图一致,说明分析正确。

26.3答:分析以上命令可知,相对第二题,该命令只是将中断间隔由原来的100改为3,运行以上命令得到以下运行结果:(此结果为-s为0)使用“-c”选项运行命令查看答案,结果和上图一致,说明分析正确。

再对“-s”的值进行改变和运行,查看结果可知不同的种子情况下运行结果一致。

由本实验可知中断频率会改变程序的行为。

26.4答:首先查看并分析looping-race-nolock.s文件的内容如下图:运行以上命令得到以下结果:使用“-c”选项运行命令查看答案,结果和上图一致,说明分析正确。

Chapter28首先查看选项明确含义,大多数的选项与Chapter26的相同,主要有以下新选项:28.1答:首先查看flag.s文件内容:运行命令得以下结果:由上图可知,首先是线程0获得锁,直到执行结束释放锁之后线程1才获得锁并执行。

由此可分析以上汇编代码是想通过用一个变量来标志锁是否被某些线程占用。

第一个线程到达时首先会检查标志是否为0,如果是0则设置标志为1表示已经获得锁,其他线程到达时如果第一个线程仍未执行结束则一直检查标志是否为0,直到第一个线程执行结束释放锁(将标志设置为0)才会被其他线程获取。

28.2答:有第一题可得,使用默认值运行时,flag.s可按预期工作。

可以产生正确的结果,并且可以预测代码运行时最终的flag标志会被置0,因为线程1执行结束后锁会被释放。

使用-M和-R对相应的地址内存和寄存器进行跟踪,运行一下命令“./x86.py-p flag.s-R ax,bx-M flag,count-c”,运行结果如下图:28.3答:在第二题的命令的基础上加上-a选项“-a bx=2,bx=2”再次运行,结果如下。

[RCUstall]RCUstall分析,RCUstall内核文档翻译

![[RCUstall]RCUstall分析,RCUstall内核文档翻译](https://img.taocdn.com/s3/m/5fb4650fc4da50e2524de518964bcf84b9d52da2.png)

[RCUstall]RCUstall分析,RCUstall内核⽂档翻译使⽤RCU的CPU失速检测器本⽂档⾸先讨论RCU的CPU停顿检测器可以定位哪些问题,然后讨论可⽤于微调检测器操作的内核参数和Kconfig选项。

最后,本⽂解释了失速检测器的“splat”格式。

是什么导致RCU CPU停顿警告?是因为您的内核会打印RCU CPU停⽌警告。

下⼀个问题是“是什么原因引起的?” 以下问题可能导致RCU CPU停顿:警告:o RCU read-side 关键部分中出现CPU循环。

o 禁⽤中断时出现CPU循环。

o 禁⽤抢占时出现CPU循环。

这种情况可能会导致RCU调度的停顿,并且,如果使⽤kso??ftirqd,则会导致RCU-bh停顿。

o 下半部禁⽤时出现CPU循环。

这种情况可能导致RCU调度和RCU-bh停顿。

o 对于!CONFIG_PREEMPT内核,CPU可以在内核中的任何位置循环,⽽⽆需调⽤schedule()。

如果确实确实希望在内核中循环,这是您期望的⾏为,则可能需要向cond_resched()添加⼀些调⽤。

o 使⽤太慢的控制台连接来引导Linux,以致⽆法跟上引导时控制台消息的速率。

例如,115Kbaud串⾏控制台的速度可能太慢⽽⽆法跟上启动时消息的速率,经常会导致RCU CPU停顿警告消息。

特别是如果您添加了printk()调试代码。

o 阻⽌RCU宽限期kthread运⾏的任何措施。

这可能会导致“All QSes seen”控制台⽇志消息。

此消息将包含有关kthread上次运⾏的时间以及应该运⾏的频率的信息。

它还可能导致控制台⽇志消息“ rcu _.*kthread starved for”,其中将包含其他调试信息。

O CONFIG_PREEMPT内核中的CPU绑定的实时任务,这可能恰好抢占了RCU读取侧关键部分中间的低优先级任务。

如果不允许该低优先级任务在任何其他CPU上运⾏,则这尤其有害,在这种情况下,下⼀个RCU宽限期将永远⽆法完成,最终将导致系统内存不⾜并挂起。

Lecture0.Introdnction

Camera:

• Light & photograph

Robot arm:

• Movement & motor speed

Introduction: Smart Phone with Camera, GPS etc. iPhone

From /tw/

Feng-LiLian Lian© ©2013 2011 Feng-Li NTUEE-SS0-Intro-13

Introduction: Modulation & Demodulation in Communication

Feng-LiLian Lian© ©2012 2011 Feng-Li NTUEE-SS0-Intro-8

Signal Frequency Characteristics:

f (Hz) 10 20K 100M 300M 40G 2.4G 300G

Introduction: Digital Signal Processing

Feng-LiLian Lian© ©2013 2011 Feng-Li NTUEE-SS0-Intro-10

Signals and Systems

Feng-LiLian Lian© ©2013 2011 Feng-Li NTUEE-SS0-Intro-11

LTI & Convolution

(Chap 2)

Course Flowchart

Signals & Systems

(Chap 1)

Feng-LiLian Lian© ©2013 2011 Feng-Li NTUEE-SS0-Intro-18

LTI & Convolution

gostub函数打桩 -回复

gostub函数打桩-回复如何使用gostub函数进行打桩。

标题:使用gostub函数进行打桩:完美解决单元测试中的外部依赖问题引言:在软件开发过程中,我们经常面临一个共同的问题:如何在单元测试中处理对外部依赖的调用,以确保测试的可靠性和可重复性。

传统的方法往往是使用模拟对象或者模拟框架,但是这些方法要么过于复杂,要么效率低下。

幸运的是,在Go语言中,我们有一个简单而高效的解决方案——gostub函数。

第一步:了解gostub函数的基本概念gostub函数是一个基于反射的库,专门用于在单元测试中处理外部依赖。

它的原理是通过打桩(stubbing)的方式,将被测试函数中的外部依赖替换为自定义的实现,以便进行测试。

具体来说,gostub函数通过修改函数的符号表,来劫持外部函数的调用,从而实现打桩的效果。

第二步:安装gostub函数库在开始使用gostub函数之前,我们首先需要将它添加到我们的Go项目中。

打开终端,使用以下命令安装gostub函数库:bashgo get github/prashantv/gostub这个命令将会自动从GitHub上下载最新版本的gostub函数库,并将它安装到你的GOPATH目录下。

第三步:创建一个需要进行测试的函数在我们使用gostub函数之前,我们需要先创建一个带有外部依赖的函数,作为我们将要进行测试的对象。

这个函数可以是一个已经存在的函数,也可以是一个你自己定义的函数。

以下是一个简单的示例:gopackage mathimport "strconv"func Add(a, b int) (int, error) {sum := a + bstr, err := externalService(strconv.Itoa(sum)) if err != nil {return 0, err}result, err := strconv.Atoi(str)if err != nil {return 0, err}return result, nil}上面的示例函数中,我们使用了一个外部的服务externalService,这个服务接受一个整型参数,并返回一个字符串。

南京Oracle认证培训 TimesTen学习之安装篇讲课讲稿

南京O r a c l e认证培训T i m e s T e n学习之安装篇南京Oracle认证培训 TimesTen学习之安装篇一.Linux平台安装准备工作。

1.大页设置1).修改HugePage配置值:echo 32 > /proc/sys/vm/nr_hugepages2).查看HugePage值:[root@ttdb ~]# cat /proc/meminfo | grep HugeHugePages_Total: 28HugePages_Free: 28HugePages_Rsvd: 0Hugepagesize: 2048 kB2.信号量1).查看当前值:[root@ttdb ~]# /sbin/sysctl -a | grep semkernel.sem = 250 32000 32 1282).推荐值:kernel.sem = 400 32000 100 1283).使设置生效:/sbin/sysctl -p3.共享内存kernel.shmmax=2147483648(单位:字节byte)。

如果配置大于8GB,那么也应该增加shmall参数的值,这个值应该等于SHMMAX/PAGE_SIZE,在x86系统Page的大小通常为4K,在安腾平台通常为16K,例如,在安腾64GB的数据库,应该指定以下的参数值:kernel.shmmax=68719476736kernel.shmall=41943041).配置shmmax和shmall参数:在没有重启的情况下,执行以下的命令修改共享内存的值:/sbin/sysctl -w kernel.shmmax=2147483648也可以通过以下命令修改这个值:echo 2147483648 > /proc/sys/kernel/shmmax这个命令与执行sysctl命令有相同的效果。

2).查看共享内存值:cat /proc/sys/kernel/shmmax注意:如果操作系统使用的是Redhat,从Redhat Enterprise 5.4开始,shmmax和shmall 这两个值已经足够的大,默认不需要修改。

uC_OS-II实验指导书

MVTS基本使用说明

MVTS安装使用说明(适用310 312)第一节,安装操作系统要求:310 运行在LINUX AS3或ES3 以下的版本312运行在LINUX Radhat 9.0以上版本,(不包括LINUX9.0)建议硬件配置:CPU:P4 2.0以上内存:2G以上硬盘:30G以上安装步骤:安装linux完成后,将MVTS的manager.tar.gz和MVTS-310-Linux.tar.gz两个安装包上传到/usr/local 目录下.使用SSH登陆LINUX,执行以下命令:cd /usr/loca 回车tar -zxvf MVTS-310-Linux.tar.gz 回车tar –zxvf manager.tar.gz 回车cd mvts 回车[root@localhost mvts]# sh setup.shMVTS installation:enter MVTS admin group id:0 输入0回车enter MVTS support group id:0 输入0回车enter MVTS billing group id:0 输入0回车updating ./cfg/meraproxy.cfg ...setting permissions to MVTS contents ...updating /etc/profile ...making startup script mvts ...moving startup script to /etc/rc.d/init.d ...adding links for start/stopcreate links:/etc/rc.d/init.d/mvts <- /etc/rc.d/rc5.d/S50mvts/etc/rc.d/init.d/mvts <- /etc/rc.d/rc0.d/K50mvtsinstallation successful这样MVTS就安装好了,这个时候还不能登陆,需要安装managercd ..回车cd manager 回车sh setupMVTS directory? [/usr/local/mvts]: /root/mvtsMVTS Manager directory? [/root/mvts/manager]: 回车MVTS admin group? [mvts]: 回车Group mvts does not exist. Create? [y/n]: yMVTS admin user (not root)? [mvts]: 回车User mvts does not exist. Create? [y/n]: yChanging password for user mvts.New password: 密码写入linux的密码BAD PASSWORD: it is too shortRetype new password: 密码写入linux的密码passwd: all authentication tokens updated successfully.MVTS Manager successfully installed.Please do following steps before using MVTS Manager:1. Edit file /root/mvts/cfg/meraproxy.cfg:[Console]console_port=1730admin_gid=5012. Reload MVTS configuration:/root/mvts/bin/mp_shell.x r c -d3. Start MVTS agent from root:/root/mvts/manager/bin/mvtsagntctl startor/etc/init.d/mvtsagnt startThank you for using MVTS Manager![root@localhost manager]# /etc/init.d/mvtsagnt startStarting MVTS Agent: [ OK ]Manager 安装最好装两次,也就是执行2次sh setup 确保能安装成功请注意以上的红色,那写请按上面的中文提示作相应操作,安装完成后先别急着启动请注意这段提示:1. Edit file /root/mvts/cfg/meraproxy.cfg:[Console]console_port=1730admin_gid=501这里也要做相应修改写入vi /root/mvts/cfg/meraproxy.cfg回车找到后面这个按A作相应修改:console_port=1730admin_gid=501修改好后按ESC退出编辑命令,再输入wq! 保存退出以下命令是用来启动和停止MVTS的起动MVTS: /etc/init.d/mvts start停止MVTS: /etc/init.d/mvts stop起动mvtsagnt: /etc/init.d/mvtsagnt start停止mvtsagnt: /etc/init.d/mvtsagnt stop安装完成后第二节:MVTS的登陆和相关功能按键介绍请在你的电脑上安装MVTS的管理软件MVTSmanager并运行manager软件看到以上窗口说明MVTSmanager成功运行了,这个时候我们要做登陆服务器的数据:点右边的Create 看到如下窗口:写入相关数据,MVTS刚安装的默认登陆端口是1730 帐号和密码是admin 都是小写,小提示:MVTS的数据里面不可以存在全角字符更不能有中文,不然是不能登陆的.写完后点OK就保存下来了,然后选中他双击或点右上解的OK,即可连接,连接的过程会有点慢,请耐心等待,出现如下窗口后即说明成功登陆了:本文重点介绍如何对接IP认证客户和、注册用户、和落地对接路由方式←落地对接和网关对接都是在这里←路由调度在这里←注册帐号类型Originators 是指用户的帐号品质报告Terminators 是指落地的品质报告Gteways 是指所有在Gateways的品质报告Dialpeers是指路由调度的品质报告Endpoints 这里显示RAS 注册帐号的在线状态Active Calls是指当前在线的活动呼叫CDR 显示最近100条目的是用来查线路的问题Edit Config 编辑模式,要作数据改动,必须进入此模式(同时只能一人在线)Cancel edit 撤消编辑并退出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IntroductionIn this simulation, we will be studying a matching technique know as single-stub tuning. The technique matches a network by connecting a single open or short circuited transmission line, known as the stub, in series or parallel with the load. The stub is tuned using two parameters, d –the distance from the load to the stub, and l – the length of the stub. Figure 1 illustrates an open-circuit single-stub shunt tuning circuit.Figure 1: Open-circuit single-stub shunt tuning circuitPre-lab I: Single-Stub TuningIn this section of the pre-lab, we will determine the single-stub matching parameters (d & l) needed to match a load of 60-j*80 Ω to a 50 Ω transmission line. Below are a set of formulas that you may find helpful.where,For a short circuit stub, l is defined as:And for an open circuit stub, l is defined as:where,Determine the both the short-circuit and open circuit matching network solutions. Your answer should be in terms of λ. Hint: If your calculations for the lengths turn up negative you can increase the distance by λ/2.Answer:Short Circuit:Pre-lab II: MicrostripTo construct our matching network, we are going using microstrip. In practice, Microstrip is a popular choice because it is easy to fabricate. Open ADS taskLecture07_Quarter_wave_Matching. Use the formulas that were provided in Part I: Calculating Width & Length of Microstrip Line and calculate the microstrip width, W, and signalwavelength,λ for the circuit operating at 2 GHz.Warning: In Lecture04_TL when W/t was calculated we substituted Zo = √(Zl * Zs), this is only done in Quarter-wave matching. For this task use the typical characteristic impedance, Zo = 50Ω.Answer:Pre-lab III: Single-Stub Microstrip TuningUsing the solutions from Pre-lab I & II . Find the lengths d and l, in millimeters, for thematching network.Short Circuit:Part I : Single-Stub Microstrip Tuning Simulation1.Login to your computer and start ADS.2.Open the project by selecting File—Open Project and then select “elec483_2005.prj” if it doesnot automatically open.3.In the schematic window, open the prepared schematic by selecting File—Open Design and thenselect “Stub_Matching.dsn”. The schematic should resemble the one shown in Figure 2.Figure 2 – Stub_Matching.dsn4.Fill in the parameters of the microstrip components using one of the two solutions from either theopen circuit stub or the short circuit stub. The microstrip components can be found underComponent Palette List->TL-Microstrip. There are only 4 components that are of interest to us:Mlin – Microstrip Line, MLSC – Short Circuit Stub, MLOC – OpenCircuit Stub, and MTEE – Microstrip T Junction.The parameters d and l are represented respectively by the “L” of MLIN and MLSC/MLOC Indicate which matching network was used by circling the appropriate choices bellow. Simulate.What is the value of S11 ?Short Circuit Open CircuitSolution 1Solution 2Part II : Single-Stub Shunt Microstrip Design GuideIn Part I, a lot of lengthy calculations were performed in order to develop a matching network. In this part, we will show you a quick way to develop a matching network using a Design Guide.1.Remove the matching network that was created in Part I.2.Select Component Palette List->Passive Circuit DG – Matching-> Single-Stub MatchSmartComponent and insert it in front of the load. The circuit should resemble Figure 3.Figure 3 – Stub_Matching with Single-Stub Match SmartComponent3.Adjust parameters F, Zload, and Stub Type in the SmartComponent. Select the stub type to bethe same as the one used in Part I. We will be comparing the results of the two parts later.4.Select DesignGuide -> Passive Circuit -> Microstrip Control Window...5.Go to the tab labeled “Design Assistant” and click “Design”. This should only take a coupleseconds. Once it has finished designing go back to the schematic and push into theSmartComponent and record the W, l, and d that ADS has calculated. The design guide only calculates one possible solution for the matching network. Compare the results found here with the one calculated in Part I. Were your values in Part I close? If not, explain why?Answer:6.Simulate and record the S11 value. Is this matching network better or worse than the one youcreated in Part I?。