利用VHDL语言设计一个8位8421码到8位格雷码的编码器

Verilog HDL 之 8-3编码器

Verilog HDL 之8-3编码器原理:在数字系统中,常常需要将某一信息(输入)变换为某一特定的代码(输出)。

把二进制码按一定的规律排列,例如8421码、格雷码等,使每组代码具有一特定的含义(代表某个数字或是控制信号)称为编码。

具有编码功能的逻辑电路称为编码器。

编码器有若干个输入,在某一时刻只有一个输入被转换为二进制码。

例如8线-3线编码器和10线-4线编码器分别有8输入、3位输出和10位输入、4位输出。

下面是8-3编码器的真值表。

实验环境:硬件:AR2000核心板、SOPC-MBoard板、PC 机、ByteBlaster II 下载电缆软件:ModelSim 、Altera Quartus II 7.2 集成开发环境。

实验步骤:1.打开Quartus II 7.2软件,选择File | New Project Wizard新建一个工程,在对话框中第一行选择工程路径,并为该工程新建一个文件夹。

本例中第二行输入工程名bm8_3;第三行是工程顶层设计文件名,该顶层设计文件名一定要与设计文件中模块名module一致,可以与工程名不同,但一般都和工程名一致。

如图1.1所示。

图1.1 在Quartus II中新建工程2.单击“Next”,此对话框是向工程中添加设计文件的。

现在还没有写设计文件,所以没有文件可以添加;直接单击“Next”,进入器件选择对话框。

在Family下拉菜单中选择Cyclone II 系列。

然后在Filters下的Package下拉菜单中选择封装形式FBGA,Pin count下拉菜单中选择管脚数672,Speed grade下拉菜单中选择速度级别8;然后在Available devices中选择EP2C35F672C8器件。

如图1.2所示。

图1.2 选择FPGA器件3.单击Finish,建立好工程。

向工程中添加设计文件,选择File | New ,在New对话框中选择Device Design Files下的Verilog HDL File,单击OK,完成新建设计文件。

VHDL八位数码管频率计课程设计

5、时钟源。

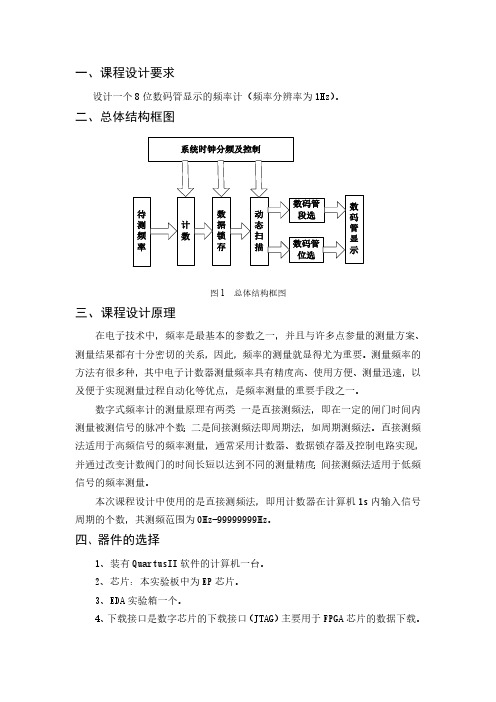

五、功能模块和信号仿真图以及源程序(1) 系统时钟分频及控制的功能模块图及其源程序图2 功能模块图作用:将试验箱上的50MHz的晶振分频,输出CLOCK为数码管提供1kHz的动态扫描频率。

CNT_EN输出为0.05s的信号,对频率计中的32位十进制计数器CNT10的ENA使能端进行同步控制,当TSTEN高电平时允许计数,低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要一个锁存信号LOAD的上跳沿将计数器在前一秒的计数值锁存进锁存器REG32B中,并由外部的十进制7段数码管显示计数值。

设置锁存器的好处是数据显示稳定,不会由于周期性的清零信号而不断闪烁。

锁存信号后,必须有一个清零信号RST_CNT对计数器进行清零,为下一秒的计数操作做准备。

该模块的信号仿真图如下:图3 仿真波形图源程序如下:--分频library ieee;use ieee.std_logic_1164.all;entity fdivwangzheng isport(clk0:in std_logic; --输入系统时钟clk1:out std_logic; --输出1hz时钟信号clk2:out std_logic); --输出显示扫描时钟信号end fdivwangzheng;architecture a of fdivwangzheng isbeginp1:process(clk0)variable cnt:integer range 0 to 49999999; --分频系数为24999999variable ff:std_logic;beginif clk0'event and clk0='1' thenif cnt<49999999 thencnt:=cnt+1;elsecnt:=0;ff:=not ff; --反向end if;end if;clk1<=ff;end process p1;p2:process(clk0)variable cnn:integer range 0 to 999; --分频系数为499variable dd:std_logic;beginif clk0'event and clk0='1' thenif cnn<999 thencnn:=cnn+1;elsecnn:=0;dd:=not dd; --反向end if;end if;clk2<=dd;end process p2;end a;--测频控制器(testctl.vhd)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TESTCTLwanzheng ISPORT ( CLKK : IN STD_LOGIC; -- 1HzCNT_EN,RST_CNT,LOAD : OUT STD_LOGIC);END TESTCTLwanzheng;ARCHITECTURE behav OF TESTCTLwanzheng ISSIGNAL DIV2CLK : STD_LOGIC;BEGINPROCESS( CLKK )BEGINIF CLKK'EVENT AND CLKK = '1' THEN DIV2CLK <= NOT DIV2CLK;END IF;END PROCESS;PROCESS (CLKK, DIV2CLK)BEGINIF CLKK='0' AND Div2CLK='0' THEN RST_CNT <= '1';ELSE RST_CNT <= '0'; END IF;END PROCESS;LOAD <= NOT DIV2CLK ; CNT_EN <= DIV2CLK;END behav;(2) 十进制计数器的功能模块图及其源程序图4 功能模块图作用:当使能端为高电平,清零端为低电平时,实现十进制计数功能。

编码器的VHDL设计

END coder83_2;

பைடு நூலகம்

ARCHITECTURE behave OF coder83_2 IS BEGIN Q2 <= D4 OR D5 OR D6 OR D7; Q2=D4+D5+D6+D7 Q1 <= D2 OR D3 OR D6 OR D7; Q1=D2+D3+D6+D7 Q0=D1+D3+D5+D7 Q0 <= D1 OR D3 OR D5 OR D7; END behave;

(3)条件选择值必须覆盖“表达式”的所有取值。 )条件选择值必须覆盖“表达式”的所有取值。 因此, 因此,在END CASE前的最后一条语句总是 前的最后一条语句总是 顺序语句” “WHEN OTHERS=>顺序语句”。 顺序语句 引导的条件选择值不能重叠。 (4)不同的“WHEN”引导的条件选择值不能重叠。 )不同的“ 引导的条件选择值不能重叠 5)CASE语句是顺序语句 必须在进程中使用。 语句是顺序语句, (5)CASE语句是顺序语句,必须在进程中使用。

二case语句case语句也是分支语句的一种case语句不同于if语句它是根据所满足的条件直接执行多项顺序语句中的一项没有优先级

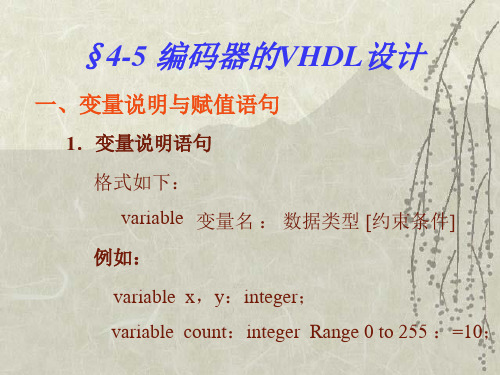

§4-5 编码器的VHDL设计

一、变量说明与赋值语句

1.变量说明语句 . 格式如下: variable 变量名 : 数据类型 [约束条件] 例如: 例如: variable x,y:integer; variable count:integer Range 0 to 255 :=10;

8路抢答器的VHDL语言

八路抢答器由抢答启动电路、抢答定时器及定时译码显示电路、抢中报警电路、选手编号译码显示电路、答题时间限制电路,答题时间剩余显示电路和答题结束报警电路组成。

优先编码电路、锁存器、译码电路将抢中选手的编号译码显示输出;主持人开关启动和选手抢中报警电路;答题限时时间显示电路,答题时间结束和答题完成报警电路。

基于FPGA,经过程序设计、调试、仿真、下载和软硬件联合调试等工作,实现了抢答功能(另设计提供限时答题功能)。

1.设计一个八路智力抢答器,同时供8个选手参赛,编号分别为1到8。

每位选手用一个答题按钮。

2.给主持人一个控制开关,实现系统的清零和抢答的开始。

3.具有数据锁存和显示功能。

抢答开始后,如果有选手按下了抢答按钮,其编号立即锁存并显示在LED数码管上,同是扬声器报警。

此外,禁止其他选手再次抢答。

选手的编号一直保存直到主持人清除。

扩展功能:1.具有定时抢答功能,可由主持人设定抢答时间。

当抢答开始后。

定时其开始倒计时,并显示在LED上,同时扬声器发声提醒、2.选手在规定时间内抢答有效,停止倒计时,并讲倒计时时间显示在LED上,同时报警3.在规定时间内,无人抢答时,电路报警提醒主持人,此后的抢答按键无效。

4.选手抢中后,开始答题。

规定答题时间为:10s,在规定的时间内,选手答完题,手动报警。

若在规定时间内,未完成答题,报警提示。

答题时,显示答题剩余时间。

5.报警时间定为:100ms1.2.系统顶层文件顶层文件原理图:VHDL程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;-- Uncomment the following lines to use the declarations that are -- provided for instantiating Xilinx primitive components.--library UNISIM;--use UNISIM.VComponents.all;entity myproject isport( clk : in std_logic; --时钟信号clear : in std_logic; --清零信号player : in std_logic_vector(7 downto 0); --八个抢答选手输入settime1 : in std_logic_vector(3 downto 0);--答题时间设置led_10s : out std_logic_vector(6 downto 0); --10s抢答计时已进行的时间显示selector : out std_logic_vector(6 downto 0); --抢中选手编码输出a udio : out std_logic; --喇叭响,低有效.endanswer : in std_logic; --答题完成led_left1 : out std_logic_vector(6 downto 0));end myproject;architecture Behavioral of myproject isc omponent qiangdap ort(set_start : in std_logic;a : in std_logic_vector(7 downto 0);clk : in std_logic;led : out std_logic_vector(6 downto 0);selector : out std_logic_vector(6 downto 0);selected : out std_logic;alarm : out std_logic);e nd component;c omponent dingshiqip ort(selected : in std_logic;clk : in std_logic;settime1: in std_logic_vector(3 downto 0);endanswer : in std_logic;alarm : out std_logic;led : out std_logic_vector(6 downto 0));e nd component;c omponent baojingp ort(clk : in std_logic;alarm1 : in std_logic;alarm2 : in std_logic;alarm3 : in std_logic;audioer : out std_logic);e nd component;s ignal selected1 : std_logic;s ignal start : std_logic:='0';s ignal alarm1 : std_logic:='0';s ignal alarm2 : std_logic;beginstartall : process(clear)beginif clear'event and clear='1' thenstart<=not start;end if;e nd process;u1: qiangda port map(start,player,clk,led_10s,selector,selected1,alarm1);u2: dingshiqi port map(selected1,clk,settime1,endanswer,alarm2,led_left1);u3: baojing port map(clk,start,alarm1,alarm2,audio);end Behavioral;系统仿真图:2、抢答模块VHDL程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;-- Uncomment the following lines to use the declarations that are-- provided for instantiating Xilinx primitive components.--library UNISIM;--use UNISIM.VComponents.all;entity qiangda isport(set_start : in std_logic; --开始抢答信号(主持人按)否则一直有效,a : in std_logic_vector(7 downto 0); --八个抢答选手输入clk : in std_logic;led : out std_logic_vector(6 downto 0); --10s抢答计时已进行的时间显示selector : out std_logic_vector(6 downto 0); --抢中选手编码输出selected : out std_logic;alarm : out std_logic);end qiangda;architecture Behavioral of qiangda issignal deny1 : std_logic:='0'; --作为选中后标志signal deny2 : std_logic:='0'; --作为抢答计时结束标志signal timeon : integer range 0 to 15 :=0;signal cnt1 : integer range 0 to 32000000;beginalarm<=deny1 or deny2;selected<=deny1;select1 : process(set_start,deny2,a)beginif set_start='0' thendeny1<='0';selector<="0110000";elsif(deny1='0' and deny2='0' ) thencase a iswhen "10000000"=> selector<="1001111"; deny1<='1';when "01000000"=> selector<="0010010"; deny1<='1';when "00100000"=> selector<="0000110"; deny1<='1';when "00010000"=> selector<="1001100"; deny1<='1';when "00001000"=> selector<="0100100"; deny1<='1';when "00000100"=> selector<="0100000"; deny1<='1';when "00000010"=> selector<="0001111"; deny1<='1';when "00000001"=> selector<="0000000"; deny1<='1';when others => selector<="1111111"; --all unlaw states!!!end case;end if;end process;time10s : process(clk,deny1,set_start)beginif (clk'event and clk='1') thenif set_start='0' thendeny2<='0';timeon<=10;cnt1<=0;elsif deny1='1' thentimeon<=timeon;elsif timeon/=0 thenif cnt1/=32000000 thencnt1<=cnt1+1;elsetimeon<=timeon-1;cnt1<=0;end if;elsedeny2<='1';end if;end if;end process;ledshow : process(timeon)begincase timeon iswhen 0=> led<="0000001"; --0when 1=> led<="1001111"; --1when 2=> led<="0010010"; --2when 3=> led<="0000110"; --3when 4=> led<="1001100"; --4when 5=> led<="0100100"; --5when 6=> led<="0100000"; --6when 7=> led<="0001111"; --7when 8=> led<="0000000"; --8when 9=> led<="0000100"; --9when others => led<="1111111"; --未选中的状态,不显示end case;end process;end Behavioral;抢答电路仿真图:3.答题模块VHDL程序:(定时)library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;-- Uncomment the following lines to use the declarations that are-- provided for instantiating Xilinx primitive components.--library UNISIM;--use UNISIM.VComponents.all;entity dingshiqi is--设置答题时间,并计数,显示剩余时间,并将计数剩余时间转换为LED码输出。

实验二 基于VHDL格雷码编码器的设计

实验二基于VHDL格雷码编码器的设计一、实验目的1、了解格雷码变换的原理。

2、进一步熟悉QUARTUSII软件的使用方法和VHDL输入的全过程。

3、进一步掌握实验系统的使用。

二、实验原理格雷(Gray)码是一种可靠性编码,在数字系统中有着广泛的应用。

其特点是任意两个相邻的代码中仅有一位二进制数不同,因而在数码的递增和递减运算过程中不易出现差错。

但是格雷码是一种无权码,要想正确而简单的和二进制码进行转换,必须找出其规律。

根据组合逻辑电路的分析方法,先列出其真值表再通过卡诺图化简,可以很快的找出格雷码与二进制码之间的逻辑关系。

其转换规律为:高位同,从高到低看异同,异出‘1’,同出‘0’。

也就是将二进制码转换成格雷码时,高位是完全相同的,下一位格雷码是‘1’还是‘0’,完全是相邻两位二进制码的“异”还是“同”来决定。

下面举一个简单的例子加以说明。

假如要把二进制码10110110转换成格雷码,则可以通过下面的方法来完成,方法如图2-1。

图2-1 格雷码变换示意图因此,变换出来的格雷码为11101101。

三、实验内容本实验要求完成的任务是变换12位二进制码到12位的格雷码。

实验中用12位拨动开关模块的K1~K12表示8位二进制输入,用LED模块的LED1~LED12来表示转换的实验结果十二位格雷码。

实验LED亮表示对应的位为‘1’,LED灭表示对应的位为‘0’。

通过输入不同的值来观察输入的结果与实验原理中的转换规则是否一致。

实验箱中的拨动开关、与FPGA的接口电路,LED灯与FPGA的接口电路以及拨动开关、LED与FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。

四、实验步骤1、 打开QUARTUSII 软件,新建一个工程。

2、建完工程之后,再新建一个VHDL File 。

新建一个VHDL 文件的过程如下: 1)选择QUARTUSII 软件中的File>New 命令,出现New 对话框。

如图2-2所示。

分别使用原理图和VHDL语言输入方法设计8位全加器

大庆石油学院课程设计2006年 9 月 12 日大庆石油学院课程设计任务书课程硬件课程设计题目分别使用原理图和VHDL语言输入方法设计8位全加器专业计算机科学与技术姓名孟庆军学号040702140408主要内容、基本要求、主要参考资料等一、主要内容:利用EDA-V型实验系统、微机和Maxplus-II软件系统,分别使用原理图和VHDL语言输入方法设计8位全加器。

要求利用层次设计方法,首先设计1位半加器,仿真和测试成功后把它保存到元件库中去;之后以1位半加器为底层元件设计1位全加器,仿真和测试成功后把它也保存到元件库中去;最后以1位全加器为基本元件,设计8位全加器的顶层文件,进行仿真和测试。

二、基本要求:1、熟练掌握EDA软硬件系统的使用方法。

2、设计出8位全加器,精通原理图输入方法,初步学会使用VHDL语言输入方法。

3、学会功能仿真和时序仿真。

4、按照规范写出论文,要求字数在4000字以上,并进行答辩。

论文内容包括概述(学习、调研、分析、设计的内容摘要)、EDA技术的现状和发展趋势、对EDA_V型实验系统和MaxplusII软件的掌握程度、8位全加器设计过程(包括原理图或程序设计、编译、仿真分析、硬件测试的全过程),论文中含有原理图、程序、仿真波形图及其分析报告。

三、主要参考资料:[1] 潘松.EDA技术实用教程[M].北京:科学出版社, 2003.11-13.[2] 杨恒.FPGA/CPLD最新实用技术指南[M].北京:清华大学出版社, 2005.20-22.[3] EDA先锋工作室.Altera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社2005.32-33.[4] 求是科技.CPLD/FPGA应用开发技术与工程实践[M].北京:人民邮电出版社2005. 55-58.[5] 潘松.SOPC技术实用教程[M] .清华大学出版社.2005.1-15.完成期限第28周指导教师专业负责人年月日大庆石油学院课程设计成绩评价表指导教师:年月日摘要本文介绍了利用EDA-V硬件系统和微机上的MaxPlus-II等软件系统,分别使用原理图和VHDL语言输入方法设计8位全加器。

8位CPU的设计-VHDL语言-综合性实验实验报告

综合性实验报告计算机组成原理年级专业班级:10级软工R3班小组号: 5完成日期:2012-06-06【分工包括:、、执行(ALU相关)、通用寄存器组、存储器等】(一)实验类型:验证性+设计性(二)实验类别:综合性专业基础实验(三)实验学时数:8学时(四)实验目的理解和验证参考代码,并在其基础上,通过适当改造,尝试设计一个简单的CPU,并测试其结果。

(五)实验内容设计一个能验证计算机CPU工作原理的实验系统,包括取指部分、指令译码部分、执行部分、通用寄存器组以及存储器,并测试其结果。

(六)实验要求根本目标:缩小到8位的数据通路,也即是4位OP和4位的地址码。

(参考代码是16位数据通路,也即8位OP和8位的地址码)(参见实践报告.doc中的9-11页的指令系统总体说明)学生按照实验要求,在实验平台上实现具有存储与运算功能的计算机系统,并能通过测试,以验证其正确性。

具体要求如下:(1)取指及调试(组长兼任)。

熟悉指令取指过程,并把16位的部分改为8位。

使用DebugController和系统中的调试模块(reg_testa.vhd,reg_test.vhd)。

(2)熟悉电原理图的连接,以通用寄存器组部分为例。

实现上,用实验4所用的简单通用寄存器组(4个寄存器+1个2-4译码器+2个4选1多路开关)设计方法,替代参考代码中的通用寄存器组部分。

(3)学习和掌握控制逻辑。

设计一套指令集(可在原参考代码指令集的基础上做删减,从中选取16条基本的指令),并修改控制器中指令集的译码部分。

(4)执行部件,ALU的改造。

可在原参考代码的基础上,改变某些运算功能的实现方式,比如加、减、增1、减1等算术运算。

实现上,原参考代码采用了最少编码量的“+”、“-”号实现。

可以改用通过port map语句调用系统自带的加法器,也可以进一步自己编写加法器,然后用port map语句调用。

(5)存储器部分的加入。

原参考代码采用的带外部存储器的模式。

EDA实验_设计一个8位加法器

XXXX大学计算机科学学院实验/上机报告一、实验目的设计一个8位加法器。

二、实验环境Quartus II 7.0 开发系统三、实验内容利用全加器,设计一个8位加法器。

四、实验过程设计思想:8位二进制加法器可以由8个全加器通过级联的方式构成。

根据全加器级联的原理,用VHDL设计一个8位二进制数的加法器,可以先设计一个一位全加器,然后利用一位全加器采用元件例化的方式实现加法器。

实验步骤:1、设计一个全加器新建工程,建立源文件,输入VHDL设计文件,如下图所示:完成设计文件输入后,保存文件,对文件进行编译、仿真,以下是仿真结果,如图所示:由图可知仿真结果正确。

2、元件例化把VHDL设计文件转为原理图中使用的元件。

在文件菜单File中选择Creat/Update选项,单击Create Symbol File for Current File 选项,系统自动生成相应的元件标号。

重复新建文件的操作,选择Block Diagram/Schmatic File 选项,新建一个原理图文件,在添加元件列表中可以看到自动生成的元件,选择full_adder这个元件添加到原理图中,如下图所示:3、完成顶层图的设计用生成的元件标号,完成顶层图的设计。

这里有两种方法,一种是直接用原理图设计,根据原理图设计工具的使用方法,完成顶层文件的设计,这个方法比较复杂,所以这里选择另一种方法,通过VHDL设计文件。

继续建立源文件,输入VHDL设计文件,如下图所示:依照上述步骤,保存文件,对文件进行编译、仿真,以下是仿真结果,如图所示:五、实验总结本次实验的目的是设计一个8位二进制加法器,而8位二进制加法器可以由8个全加器通过级联的方式构成。

根据全加器级联的原理,用VHDL设计一个8位二进制数的加法器,可以先设计一个一位全加器,然后利用一位全加器采用元件例化的方式实现加法器。

根据实验设计思路,我先用VHDL设计了一个全加器full_adder.vhd,编译、仿真成功后,通过元件例化的方式,采用原理图设计了一个8位的加法器adder8.bdf,但是在这个过程中出现了很多问题,即由于我是把这个8位的加法器的每个全加器元件输入输出引脚分开的,因此一开始就设计了17个输入引脚,这使得我在给输入引脚添加信号时不知道添加什么信号,才能够起到验证仿真结果是否正确的目的。