Verilog期末复习题[优质文档]

Verilog期末复习题

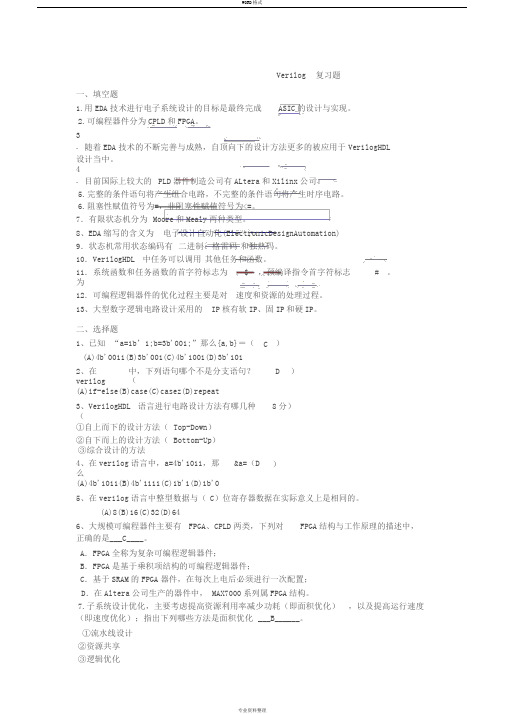

Verilog 复习题一、填空题1.用EDA技术进行电子系统设计的目标是最终完成ASIC的设计与实现。

2.可编程器件分为CPLD和FPGA。

3. 随着EDA技术的不断完善与成熟,自顶向下的设计方法更多的被应用于VerilogHDL 设计当中。

4. 目前国际上较大的PLD器件制造公司有ALtera和Xilinx公司。

5.完整的条件语句将产生组合电路,不完整的条件语句将产生时序电路。

6.阻塞性赋值符号为=,非阻塞性赋值符号为<=。

7.有限状态机分为Moore和Mealy两种类型。

8、EDA缩写的含义为电子设计自动化(ElectronicDesignAutomation)9.状态机常用状态编码有二进制、格雷码和独热码。

10.VerilogHDL 中任务可以调用其他任务和函数。

11.系统函数和任务函数的首字符标志为$ ,预编译指令首字符标志为12.可编程逻辑器件的优化过程主要是对速度和资源的处理过程。

13、大型数字逻辑电路设计采用的IP核有软IP、固IP和硬IP。

# 。

二、选择题1、已知“a=1b’1;b=3b'001;”那么{a,b}=( C )(A)4b'0011(B)3b'001(C)4b'1001(D)3b'1012、在verilog 中,下列语句哪个不是分支语句?(D )(A)if-else(B)case(C)casez(D)repeat3、VerilogHDL 语言进行电路设计方法有哪几种(①自上而下的设计方法( Top-Down)②自下而上的设计方法( Bottom-Up)8分)③综合设计的方法4、在verilog语言中,a=4b'1011,那么&a=(D )(A)4b'1011(B)4b'1111(C)1b'1(D)1b'05、在verilog语言中整型数据与(C)位寄存器数据在实际意义上是相同的。

(完整版)Verilog期末复习题

(完整版)Verilog期末复习题Verilog复习题一、填空题1. 用EDA技术进行电子系统设计的目标是最终完成2. 可编程器件分为CPLD和FPGA。

3. 随着EDA技术的不断完善与成熟,自顶向下的设计方法更多的被应用于Verilog HDL设计当中。

4. 目前国际上较大的PLD器件制造公司有ALtera和Xilinx公司。

5. 完整的条件语句将产生组合电路,不完整的条件语句将产生时序电路。

6. 阻塞性赋值符号为=,非阻塞性赋值符号为<= 。

78、EDA9.状态机常用状态编码有二进制、格雷码和独热码。

10.V erilog HDL中任务可以调用其他任务和函数。

11.系统函数和任务函数的首字符标志为$,预编译指令首字符标志为#。

12.可编程逻辑器件的优化过程主要是对速度和资源的处理过程。

13、大型数字逻辑电路设计采用的IP核有软IP、固IP和硬IP。

二、选择题1、已知“a =1b’1; b=3b'001;”那么{a,b}=(C )(A) 4b'0011 (B) 3b'001 (C) 4b'1001 (D) 3b'1012、在verilog中,下列语句哪个不是分支语句?( D )(A) if-else (B) case (C) casez (D) repeat3、Verilog HDL语言进行电路设计方法有哪几种(8分)①自上而下的设计方法(Top-Down)②自下而上的设计方法(Bottom-Up)③综合设计的方法4、在verilog语言中,a=4b'1011,那么 &a=(D )(A) 4b'1011 (B) 4b'1111 (C) 1b'1 (D) 1b'05、在verilog语言中整型数据与(C)位寄存器数据在实际意义上是相同的。

(A) 8 (B) 16 (C) 32 (D) 646、大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA 结构与工作原理的描述中,正确的是___C____ 。

verilog复习卷

end

else

dout=din;//若符号位不为1,即为0,正数,补码为其本身

end

endmodule六、编程( Nhomakorabea4分)编程实现一个并行加载串行输出的程序,输入是一个8位的二进制数。

module test12 (clk, en, d_in, s_out);

input clk;

input en;

input[9:0] d_in;

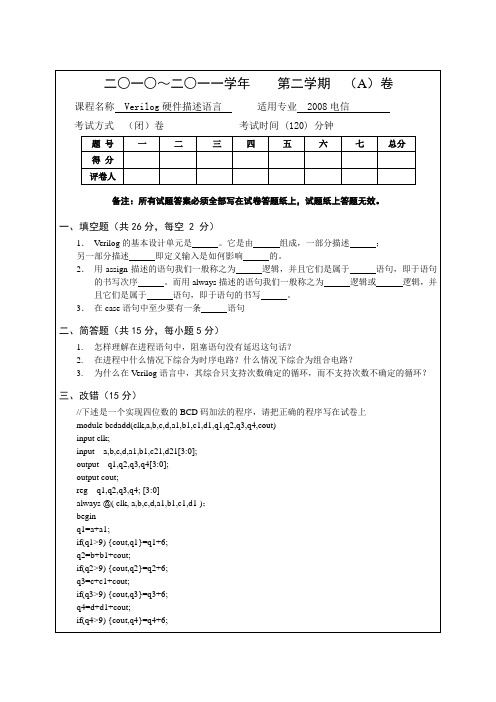

一、填空题(共10分,每空2分)

1.已知x=4’b1001,y=4’b0110,则x的4位补码为,而y的4位的补码为。

2.在case语句中至少要有一条语句。

3.两个进程之间是语句。而在Always中的语句则是语句。

二、简答题(共20分,每小题5分)

1.进程语句的启动条件是怎样?

2.为什么在Verilog语言中,其综合只支持次数确定的循环,而不支持次数不确定的循环?

3.为什么在Verilog语言中,其综合只支持次数确定的循环,而不支持次数不确定的循环?

答:这是因为,在Verilog语言中,它是为电路设计而设计的一门语言,它如高级语言不同,若循环的次数不确定,则会带来不确定的延迟,而这在电路中是不允许存在的,故综合只支持次数确定的循环,即对于一个具体的芯片,其延迟是一个定值。

4'b0111: data<= 8'b11100000;

4'b1000: data<= 8'b11111110;

4'b1001: data<= 8'b11110110;

(完整word版)EDA-VerilogHDL期末复习题总结必过

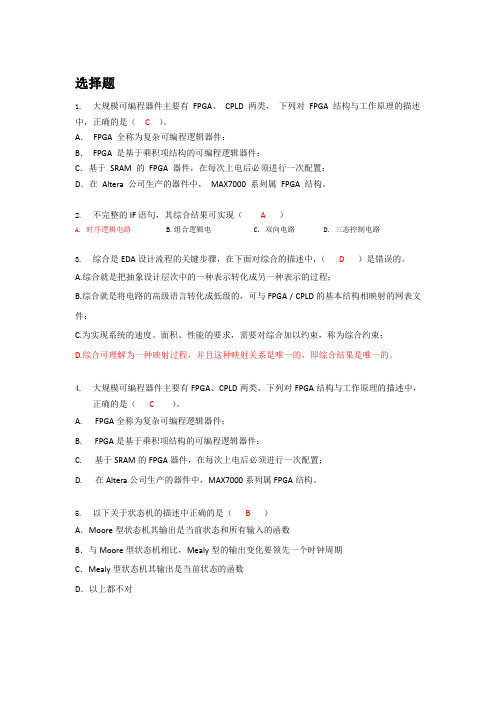

选择题1.大规模可编程器件主要有FPGA、CPLD 两类,下列对FPGA 结构与工作原理的描述中,正确的是(C)。

A.FPGA 全称为复杂可编程逻辑器件;B.FPGA 是基于乘积项结构的可编程逻辑器件;C.基于SRAM 的FPGA 器件,在每次上电后必须进行一次配置;D.在Altera 公司生产的器件中,MAX7000 系列属FPGA 结构。

2.不完整的IF语句,其综合结果可实现(A)A. 时序逻辑电路B.组合逻辑电C. 双向电路D. 三态控制电路3.综合是EDA设计流程的关键步骤,在下面对综合的描述中,(D)是错误的。

A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

4.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是( C )。

A.FPGA全称为复杂可编程逻辑器件;B.FPGA是基于乘积项结构的可编程逻辑器件;C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

5.以下关于状态机的描述中正确的是(B)A.Moore型状态机其输出是当前状态和所有输入的函数B.与Moore型状态机相比,Mealy型的输出变化要领先一个时钟周期C.Mealy型状态机其输出是当前状态的函数D.以上都不对6.目前应用最广泛的硬件描述语言是(B)。

A. VHDLB. Verilog HDLC. 汇编语言D. C语言7.一模块的I/O 端口说明:“input [7:0] a;”,则关于该端口说法正确的是( A )。

A. 输入端口,位宽为8B. 输出端口,位宽为8C. 输入端口,位宽为7D. 输出端口,位宽为78.基于EDA 软件的FPGA / CPLD 设计流程为:原理图/HDL 文本输入→综合→___ __→→适配→编程下载→硬件测试。

verilog复习题

verilog复习题Verilog复习题Verilog是一种硬件描述语言,广泛应用于数字电路设计和验证。

它的语法简洁明了,能够精确描述电路的行为和结构。

在进行Verilog的学习和实践过程中,复习题是非常有用的工具。

下面将介绍一些常见的Verilog复习题,帮助大家巩固知识和提高技能。

一、基础题1. 请用Verilog描述一个4位全加器。

module full_adder(input a, b, cin, output sum, cout);assign sum = a ^ b ^ cin;assign cout = (a & b) | (cin & (a ^ b));endmodule2. 如何用Verilog实现一个4位比较器?module comparator(input [3:0] a, b, output eq, gt, lt);assign eq = (a == b);assign gt = (a > b);assign lt = (a < b);endmodule3. 请用Verilog实现一个4位移位寄存器。

module shift_register(input [3:0] in, input shift, output [3:0] out);reg [3:0] reg_out;always @(posedge shift)if (shift)reg_out <= {reg_out[2:0], in[0]};elsereg_out <= reg_out;assign out = reg_out;endmodule二、中级题1. 如何用Verilog实现一个4位加法器?module adder(input [3:0] a, b, output [3:0] sum);reg [3:0] reg_sum;always @(a, b)reg_sum = a + b;assign sum = reg_sum;endmodule2. 请用Verilog实现一个4位乘法器。

Verilog的期末题目

评价方案

1. 逐人验收,email提交代码。

2. 验收时间:2013年6月10日(星期二)开始

3. 验收时,学生需要展示代码、运行仿真程序、展示在Quartus中综合生成的电路图,对代码做出口头解释,并回答教师随机提出的问题。

4. 先做完的可先验收。

越早验收越能得高分,越晚的分越低。

验收顺序通过到教师处预约确定。

若预约好而验收时却还未做好的,酌情减分。

5. 通过email提交的代码主要作为备案之用,以及评分的后期辅助参考。

最主要的评分将于验收时给出。

6. 所有程序都需要单独写出测试程序。

1.编码器

利用verilog语言设计HDB3码编码器

2.译码器

利用verilog语言设计HDB3码译码器

3.序列检测器

利用状态机设计一个序列检测器,使之能检测111000011序列,并进行仿真

4.排序

设计一个模块,通过任务完成3 个8 位2 进制输入数据的冒泡排序。

要求:时钟触发任务的执行,每个时钟周期完成一次数据交换的操作。

5. 分频器

分别设计占空比为50%的奇数分频、偶数分频。

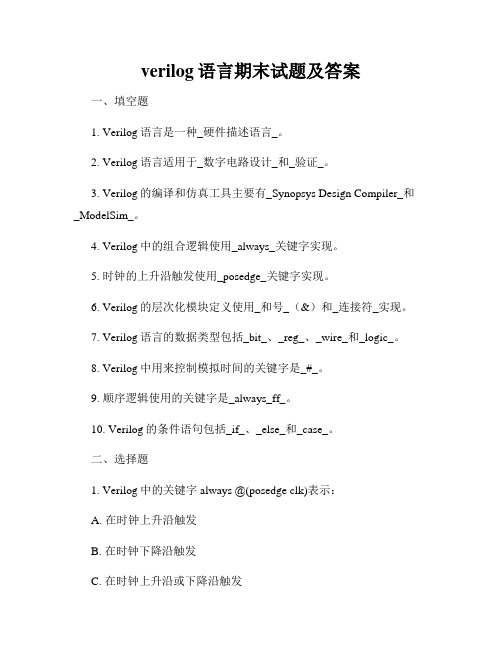

verilog语言期末试题及答案

verilog语言期末试题及答案一、填空题1. Verilog语言是一种_硬件描述语言_。

2. Verilog语言适用于_数字电路设计_和_验证_。

3. Verilog的编译和仿真工具主要有_Synopsys Design Compiler_和_ModelSim_。

4. Verilog中的组合逻辑使用_always_关键字实现。

5. 时钟的上升沿触发使用_posedge_关键字实现。

6. Verilog的层次化模块定义使用_和号_(&)和_连接符_实现。

7. Verilog语言的数据类型包括_bit_、_reg_、_wire_和_logic_。

8. Verilog中用来控制模拟时间的关键字是_#_。

9. 顺序逻辑使用的关键字是_always_ff_。

10. Verilog的条件语句包括_if_、_else_和_case_。

二、选择题1. Verilog中的关键字always @(posedge clk)表示:A. 在时钟上升沿触发B. 在时钟下降沿触发C. 在时钟上升沿或下降沿触发D. 无关键字触发答案:A2. Verilog中用来定义模块的关键字是:A. alwaysB. moduleC. caseD. reg答案:B3. 下列哪个关键字用于在连续赋值中实现多路选择:A. ifB. elseC. caseD. always_ff答案:C4. Verilog中用来延时模拟时间的关键字是:A. #B. @C. $D. %答案:A5. Verilog中的数据类型wire和reg的区别在于:A. wire用于内部信号连接,reg用于存储数据B. wire只能传输数字信号,reg可以传输任意信号C. wire用于组合逻辑,reg用于时序逻辑D. wire在连续赋值中使用,reg在时序赋值中使用答案:A三、编程题请使用Verilog语言描述一个4位全加器模块,并画出其电路原理图。

```verilogmodule full_adder(input a, b, cin, output sum, cout);assign sum = a ^ b ^ cin;assign cout = (a & b) | (a & cin) | (b & cin);endmodule```四、简答题1. 请简述Verilog语言的优点及应用领域。

verilog期末考试试题

verilog期末考试试题一、选择题(每题2分,共20分)1. 在Verilog中,以下哪个关键字用于定义一个模块?A. moduleB. endmoduleC. inputD. output2. 以下哪个操作符用于Verilog中的按位与操作?A. &B. &&C. |D. ||3. Verilog中,一个时钟信号通常与哪个信号属性关联?A. regB. wireC. clkD. none of the above4. 在Verilog中,非阻塞赋值使用哪个操作符?A. =B. <=C. <=D. <=>5. 以下哪个是Verilog中定义参数的正确语法?A. parameter int a;B. parameter a = 10;C. parameter int a = 10;D. parameter a = 10 int;6. 以下哪个是Verilog中定义信号的初始值的正确方式?A. reg [7:0] data = 8'b1;B. reg [7:0] data = 8'b00000001;C. reg [7:0] data = 8'b10101010;D. reg [7:0] data = 8'b1;7. 在Verilog中,一个信号的宽度可以是任意的吗?A. 是的,可以是任意宽度B. 不是的,必须在1到32位之间C. 不是的,必须在1到64位之间D. 不是的,必须在1到1024位之间8. 以下哪个是Verilog中生成时钟信号的常用方法?A. 使用always块和非阻塞赋值B. 使用initial块和阻塞赋值C. 使用initial块和非阻塞赋值D. 使用always块和阻塞赋值9. 在Verilog中,case语句的每个分支后面应该使用哪个关键字?A. endB. endcaseC. caseD. default10. 以下哪个是Verilog中定义一个4位二进制计数器的正确方式?A. reg [3:0] counter;B. reg [4:1] counter;C. reg [0:3] counter;D. reg [4:0] counter;二、简答题(每题5分,共20分)1. 解释Verilog中的阻塞赋值和非阻塞赋值的区别。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Verilog复习题一、填空题1. 用EDA技术进行电子系统设计的目标是最终完成2. 可编程器件分为CPLD和FPGA。

3. 随着EDA技术的不断完善与成熟,自顶向下的设计方法更多的被应用于Verilog HDL设计当中。

4. 目前国际上较大的PLD器件制造公司有ALtera和Xilinx公司。

5. 完整的条件语句将产生组合电路,不完整的条件语句将产生时序电路。

6. 阻塞性赋值符号为=,非阻塞性赋值符号为<= 。

7.有限状态机分为Moore和Mealy两种类型。

8、EDA9.状态机常用状态编码有二进制、格雷码和独热码。

10.V erilog HDL中任务可以调用其他任务和函数。

11.系统函数和任务函数的首字符标志为$,预编译指令首字符标志为#。

12.可编程逻辑器件的优化过程主要是对速度和资源的处理过程。

13、大型数字逻辑电路设计采用的IP核有软IP、固IP和硬IP。

二、选择题1、已知“a =1b’1; b=3b'001;”那么{a,b}=(C )(A) 4b'0011 (B) 3b'001 (C) 4b'1001 (D) 3b'1012、在verilog中,下列语句哪个不是分支语句?( D )(A) if-else (B) case (C) casez (D) repeat3、Verilog HDL语言进行电路设计方法有哪几种(8分)①自上而下的设计方法(Top-Down)②自下而上的设计方法(Bottom-Up)③综合设计的方法4、在verilog语言中,a=4b'1011,那么 &a=(D )(A) 4b'1011 (B) 4b'1111 (C) 1b'1 (D) 1b'05、在verilog语言中整型数据与(C)位寄存器数据在实际意义上是相同的。

(A) 8 (B) 16 (C) 32 (D) 646、大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是___C____ 。

A.FPGA全称为复杂可编程逻辑器件;B.FPGA是基于乘积项结构的可编程逻辑器件;C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

7. 子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化___B______。

①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法A.①③⑤ B.②③④ C.②⑤⑥ D.①④⑥8、下列标识符中,_____A_____是不合法的标识符。

A.9moon B.State0 C. Not_Ack_0 D. signall9、下列语句中,不属于并行语句的是:____D___A. 过程语句 B.assign语句 C.元件例化语句 D.case语句10、P,Q,R都是4bit的输入矢量,下面哪一种表达形式是正确的5)1)input P[3:0],Q,R;2)input P,Q,R[3:0];3)input P[3:0],Q[3:0],R[3:0];4)input [3:0] P,[3:0]Q,[0:3]R;5)input [3:0] P,Q,R;11、请根据以下两条语句的执行,最后变量A中的值是___①___。

reg [7:0] A;A=2'hFF;① 8'b0000_0011 ② 8'h03 ③ 8'b1111_1111 ④ 8'b1111111112. 基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→综合→___ __→→适配→编程下载→硬件测试。

正确的是 B 。

①功能仿真②时序仿真③逻辑综合④配置⑤分配管脚A.③①B.①⑤ C.④⑤D.④②三、EDA名词解释(10分)ASIC 专用集成电路RTL 寄存器传输级FPGA 现场可编程门阵列 SOPC 可编程片上系统CPLD 复杂可编程逻辑器件 LPM 参数可定制宏模块库EDA 电子设计自动化IEEE 电子电气工程师协会IP 知识产权核 ISP 在线系统可编程三、简答题1、简要说明仿真时阻塞赋值与非阻塞赋值的区别非阻塞(non-blocking)赋值方式( b<= a):b的值被赋成新值a的操作, 并不是立刻完成的,而是在块结束时才完成;块内的多条赋值语句在块结束时同时赋值;硬件有对应的电路。

阻塞(blocking)赋值方式( b = a):b的值立刻被赋成新值a;完成该赋值语句后才能执行下一句的操作;硬件没有对应的电路,因而综合结果未知。

阻塞赋值是在该语句结束是立即完成赋值操作;非阻塞赋值是在整个过程块结束是才完成赋值操作。

2、简述有限状态机FSM分为哪两类?有何区别?有限状态机的状态编码风格主要有哪三种?根据内部结构不同可分为摩尔型状态机和米里型状态机两种。

摩尔型状态机的输出只由当前状态决定,而次态由输入和现态共同决定;米里型状态机的输出由输入和现态共同决定,而次态也由输入和现态决定。

状态编码主要有三种:连续二进制编码、格雷码和独热码。

3、简述基于数字系统设计流程包括哪些步骤?包括五个步骤:⑴、设计输入:将设计的结构和功能通过原理图或硬件描述语言进行设计或编程,进行语法或逻辑检查,通过表示输入完成,否则反复检查直到无任何错误。

⑵、逻辑综合:将较高层的设计描述自动转化为较低层次描述的过程,包括行为综合,逻辑综合和版图综合或结构综合,最后生成电路逻辑网表的过程。

⑶、布局布线:将综合生成的电路网表映射到具体的目标器件中,并产生最终可下载文件的过程。

⑷、仿真:就是按照逻辑功能的算法和仿真库对设计进行模拟,以验证设计并排除错误的过程,包括功能仿真和时序仿真。

⑸、编程配置:将适配后生成的编程文件装入到PLD器件的过程,根据不同器件实现编程或配置。

4、简述Verilog HDL编程语言中函数与任务运用有什么特点?函数和任务都能独立完成相应电路功能,通过在同一模块中的调用实现相应逻辑电路功能。

但它们又有以下不同:⑴、函数中不能包含时序控制语句,对函数的调用,必须在同一仿真时刻返回。

而任务可以包含时序控制语句,任务的返回时间和调用时间可以不同。

⑵、在函数中不能调用任务,而任务中可以调用其它任务和函数。

但在函数中可以调用其它函数或函数自身。

⑶、函数必须包含至少一个端口,且在函数中只能定义input端口。

任务可以包含0个或任何多个端口,且可以定义input、output和inout端口。

⑷、函数必须返回一个值,而任务不能返回值,只能通过output 或inout端口来传递执行结果。

5、简述FPGA与CPLD两种器件应用特点。

CPLD与FPGA都是通用可编程逻辑器件,均可在EDA仿真平台上进行数字逻辑电路设计,它们不同体现在以下几方面:⑴FPGA集成度和复杂度高于CPLD,所以FPGA可实现复杂逻辑电路设计,而CPLD 适合简单和低成本的逻辑电路设计。

⑵、FPGA内主要由LUT和寄存器组成,倾向实现复杂时序逻辑电路设计,而CPLD 内主要由乘积项逻辑组成,倾向实现组合逻辑电路设计。

⑶、FPGA工艺多为SRAM、flash等工艺,掉电后内信息消失,所以该类型需外配存储器,而CPLD工艺多为EEPROM等工艺,掉电后信息不消失,所以不用外配存储器。

⑷、FPGA相对CPLD成本高,但都可以在内都镶嵌硬核和软核,实现片上系统功能。

2、简述有限状态机FSM分为哪两类?有何区别?有限状态机的状态编码风格主要有哪三种?FSM的三段式描述风格中,三段分别描述什么?(本题6分)答:Mearly型,Moore型;前者与输入与当前状态有关,而后者只和当前状态有关;Binary,Gray,One-Hot编码;分别为状态保存,状态切换,输出;四、计算题1、利用有限状态机,以格雷码编译方式设计一个从输出信号序列中检测出101信号的电路图,其方块图、状态图和状态表如图表示。

module melay(clk,Din,reset,Qout);input clk,reset;input Din;output Qout;reg Qout;parameter[1:0] S0=2'b00,S1=2'b01,S2=2'b11; reg[1:0] CS;reg[1:0] NS;always @(posedge clk or posedge reset) beginif(reset==1'b01)CS=S0;else CS=NS;endalways @(CS or Din)begincase(CS)S0:beignif(Din==1'b0)beginNS=S0;Qout=1'b0;endelsebeginNS=S1;Qout=1'b0;endendS1:beginif(Din==1'b0)beginNS=S2;Qout=1'b0;endelsebeginNS=S1;Qout=1'b0;endendS2:beignif(Din==1'b0)beginNS=S0;Qout=1'b0;endelsebeginNS=S1;Qout=1'b0;endendendcaseendendmodule4、下面是通过case语句实现四选一电路部分程序,将横线上的语句补上,使程序形成完整功能。