Verilog试题 A答案

Verilog HDL试卷及答案教学提纲

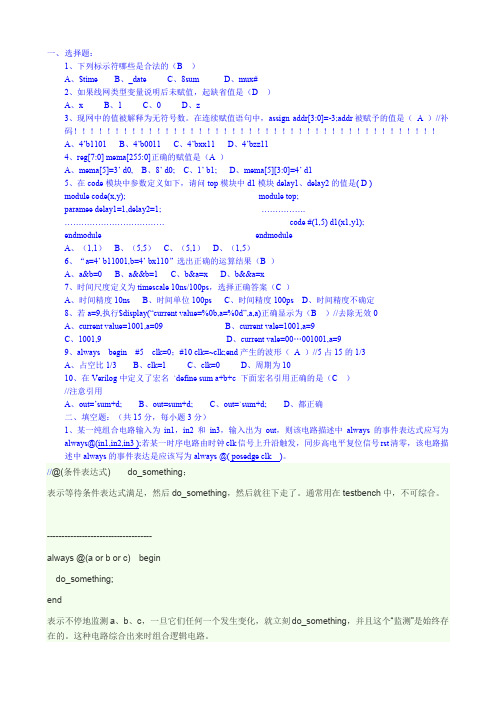

V e r i l o g H D L试卷及答案河北大学课程考核试卷2008——2009学年第一学期 2006级电气类专业(类)考核科目EDA技术课程类别必修考核类型考查考核方式闭卷类别 A一、选择题:1、下列标示符哪些是合法的(B )A、$timeB、_dateC、8sumD、mux#2、如果线网类型变量说明后未赋值,起缺省值是(D )A、xB、1C、0D、z3、现网中的值被解释为无符号数。

在连续赋值语句中,assign addr[3:0]=-3;addr被赋予的值是( A )A、4’b1101B、4’b0011C、4’bxx11D、4’bzz114、reg[7:0] mema[255:0]正确的赋值是(A )A、mema[5]=3’ d0,B、8’ d0;C、1’ b1;D、mema[5][3:0]=4’ d15、在code模块中参数定义如下,请问top模块中d1模块delay1、delay2的值是( D )module code(x,y); module top;paramee delay1=1,delay2=1; …………….……………………………… code #(1,5) d1(x1,y1);endmodule endmoduleA、(1,1)B、(5,5)C、(5,1)D、(1,5)6、“a=4’ b11001,b=4’ bx110”选出正确的运算结果(B )A、a&b=0B、a&&b=1C、b&a=xD、b&&a=x7、时间尺度定义为timescale 10ns/100ps,选择正确答案(C )A、时间精度10nsB、时间单位100psC、时间精度100psD、时间精度不确定8、若a=9,执行$display(“current value=%0b,a=%0d”,a,a)正确显示为(B )A、current value=1001,a=09B、current vale=1001,a=9C、1001,9D、current vale=00…001001,a=99、aways begin #5 clk=0;#10 clk=~clk;end产生的波形( A )A、占空比1/3B、clk=1C、clk=0D、周期为1010、在Verilog中定义了宏名 `define sum a+b+c 下面宏名引用正确的是(C )A、out=’sum+d;B、out=sum+d;C、out=`sum+d;D、都正确二、填空题:(共15分,每小题3分)1、某一纯组合电路输入为in1,in2和in3,输入出为out,则该电路描述中always的事件表达式应写为always@(in1,in2,in3 );若某一时序电路由时钟clk信号上升沿触发,同步高电平复位信号rst清零,该电路描述中always的事件表达是应该写为always @( posedge clk )。

最新Verilog-HDL考核试卷一及答案资料

河北大学课程考核试卷2008 —— 2009学年第一学期2006级电气类专业(类)考核科目EDA技术课程类别必修考核类型考查考核方式闭卷类别A 选择题:1、下列标示符哪些是合法的(B )A、$timeB、_dateC、8sumD、mux#2、如果线网类型变量说明后未赋值,起缺省值是(D )A、xB、1C、0D、z3、现网中的值被解释为无符号数。

在连续赋值语句中,assign addr[3:0]=-3;addr被赋予的值是(A)A、4'1101B、4'0011C、4'bxx11D、4'bzz114、r eg[7:0] mema[255:0]正确的赋值是(A)A、mema[5]=3 'd0,B、8'd0; C 1'b1; D、mema[5][3:0]=4 'd15、在code模块中参数定义如下,请问top模块中d1模块delay1、delay2的值是(D )module code(x,y); module top;paramee delay1=1,delay2=1; ............ ......................................... code #(1,5) d1(x1,y1);en dmodule en dmoduleA、(1,1)B、(5,5) C (5,1)D、(1,5)6、“a=4‘ b11001,b=4 ' bx110”选出正确的运算结果(B )A、a&b=0B、a&&b=1C、b&a=xD、b&&a=x7、时间尺度定义为timescale 10ns/100ps,选择正确答案(C )A、时间精度10nsB、时间单位100psC、时间精度100psD、时间精度不确定8、若a=9,执行$display(“urrent value=%0b,a=%0d ",a,a)正确显示为(B )A、current value=1001,a=09B、current vale=1001,a=9C 1001,9 D、current vale=00 …001001,a=99、aways begin #5 clk=0; #10 clk=~clk;end 产生的波形(A )A、占空比1/3 B clk=1 C、clk=0 D、周期为1010、在Verilog中定义了宏名'define sum a+b+c下面宏名引用正确的是( C )A、out= 'um+d;B、out=sum+d;C、out='sum+d;D、都正确二、填空题:(共15分,每小题3分)1、某一纯组合电路输入为in1, in2和in3,输入出为out,则该电路描述中always的事件表达式应写为always@(in1,in2,in3 );若某一时序电路由时钟clk信号上升沿触发,同步高电平复位信号rst 清零,该电路描述中always的事件表达是应该写为always@( posedge clk )。

VerilogHDL试卷及答案

一、选择题:1、下列标示符哪些是合法的(B )A、$timeB、_dateC、8sumD、mux#2、如果线网类型变量说明后未赋值,起缺省值是(D )A、xB、1C、0D、z3、现网中的值被解释为无符号数。

在连续赋值语句中,assign addr[3:0]=-3;addr被赋予的值是(A )//补码!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!A、4’b1101B、4’b0011C、4’bxx11D、4’bzz114、reg[7:0] mema[255:0]正确的赋值是(A )A、mema[5]=3’ d0,B、8’ d0;C、1’ b1;D、mema[5][3:0]=4’ d15、在code模块中参数定义如下,请问top模块中d1模块delay1、delay2的值是( D )module code(x,y); module top;paramee delay1=1,delay2=1; …………….………………………………code #(1,5) d1(x1,y1);endmodule endmoduleA、(1,1)B、(5,5)C、(5,1)D、(1,5)6、“a=4’ b11001,b=4’ bx110”选出正确的运算结果(B )A、a&b=0B、a&&b=1C、b&a=xD、b&&a=x7、时间尺度定义为timescale 10ns/100ps,选择正确答案(C )A、时间精度10nsB、时间单位100psC、时间精度100psD、时间精度不确定8、若a=9,执行$display(“current value=%0b,a=%0d”,a,a)正确显示为(B )//去除无效0A、current value=1001,a=09B、current vale=1001,a=9C、1001,9D、current vale=00…001001,a=99、always begin #5 clk=0;#10 clk=~clk;end产生的波形(A )//5占15的1/3A、占空比1/3B、clk=1C、clk=0D、周期为1010、在Verilog中定义了宏名`define sum a+b+c 下面宏名引用正确的是(C )//注意引用A、out=’sum+d;B、out=sum+d;C、out=`sum+d;D、都正确二、填空题:(共15分,每小题3分)1、某一纯组合电路输入为in1,in2和in3,输入出为out,则该电路描述中always的事件表达式应写为always@(in1,in2,in3 );若某一时序电路由时钟clk信号上升沿触发,同步高电平复位信号rst清零,该电路描述中always的事件表达是应该写为always @( posedge clk )。

最新Verilog-HDL试卷及答案

河北大学课程考核试卷2008 —— 2009学年第一学期2006级电气类专业(类)考核科目EDA技术课程类别必修考核类型考查考核方式闭卷类别A 选择题:1、下列标示符哪些是合法的(B )A、$timeB、_dateC、8sumD、mux#2、如果线网类型变量说明后未赋值,起缺省值是(D )A、xB、1C、0D、z3、现网中的值被解释为无符号数。

在连续赋值语句中,assign addr[3:0]=-3;addr被赋予的值是(A)A、4'1101B、4'0011C、4'bxx11D、4'bzz114、r eg[7:0] mema[255:0]正确的赋值是(A)A、mema[5]=3 'd0,B、8'd0; C 1'b1; D、mema[5][3:0]=4 'd15、在code模块中参数定义如下,请问top模块中d1模块delay1、delay2的值是(D )module code(x,y); module top;paramee delay1=1,delay2=1; ........... ......................................... code #(1,5) d1(x1,y1);en dmodule en dmoduleA、(1,1)B、(5,5) C (5,1)D、(1,5)6、“a=4‘ b11001,b=4 ' bx110”选出正确的运算结果(B )A、a&b=0B、a&&b=1C、b&a=xD、b&&a=x7、时间尺度定义为timescale 10ns/100ps,选择正确答案(C )A、时间精度10nsB、时间单位100psC、时间精度100psD、时间精度不确定8、若a=9,执行$display(“urrent value=%0b,a=%0d ",a,a)正确显示为(B )A、current value=1001,a=09B、current vale=1001,a=9C 1001,9 D、current vale=00 …001001,a=99、a ways begin #5 clk=0; #10 clk=~clk;end 产生的波形(A )A、占空比1/3 B clk=1 C、clk=0 D、周期为1010、在Verilog中定义了宏名'define sum a+b+c下面宏名引用正确的是( C )A、out= 'um+d;B、out=sum+d;C、out='sum+d;D、都正确二、填空题:(共15分,每小题3分)1、某一纯组合电路输入为in1, in2和in3,输入出为out,则该电路描述中always的事件表达式应写为always@(in1,in2,in3 );若某一时序电路由时钟clk信号上升沿触发,同步高电平复位信号rst 清零,该电路描述中always的事件表达是应该写为always@( posedge clk )。

Verilog试题 A答案

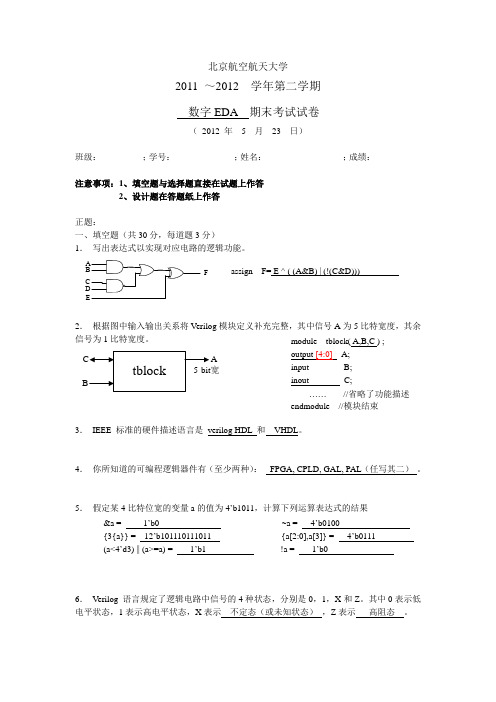

北京航空航天大学2011 ~2012 学年第二学期 数字EDA 期末考试试卷( 2012 年 5 月 23 日)班级:__________;学号:______________;姓名:__________________;成绩:___________注意事项:1、填空题与选择题直接在试题上作答2、设计题在答题纸上作答正题:一、填空题(共30分,每道题3分)1. 写出表达式以实现对应电路的逻辑功能。

F2. 根据图中输入输出关系将Verilog模块定义补充完整,其中信号A 为5比特宽度,其余信号为1比特宽度。

A 宽3. IEEE 标准的硬件描述语言是 verilog HDL 和 VHDL 。

4. 你所知道的可编程逻辑器件有(至少两种): FPGA, CPLD, GAL, PAL (任写其二) 。

5. 假定某4比特位宽的变量a 的值为4’b1011,计算下列运算表达式的结果6. Verilog 语言规定了逻辑电路中信号的4种状态,分别是0,1,X 和Z 。

其中0表示低电平状态,1表示高电平状态,X 表示 不定态(或未知状态) ,Z 表示 高阻态 。

assign F= E ^ ( (A&B) | (!(C&D)))module tblock( A,B,C ) ; output [4:0] A;input B;inout C; …… //省略了功能描述endmodule //模块结束 &a = 1’b0 ~a = 4’b0100 {3{a}} = 12’b101110111011 {a[2:0],a[3]} = 4’b0111 (a<4’d3) || (a>=a) = 1’b1 !a = 1’b07. 下面两段代码中信号in ,q1,q2和q3的初值分别为0,1,2和3,那么经过1个时钟周期后,左侧程序中q3的值变成 0 ,右侧程序中q3的值变成 2 。

8. Verilog 语言规定的两种主要的数据类型分别是 wire(或net) 和 reg 。

(完整)Verilog_HDL试卷及答案,推荐文档.doc

河北大学课程考核试卷2008 —— 2009 学年第一学期2006 级电气类专业(类)考核科目 EDA 技术课程类别必修考核类型考查考核方式闭卷类别 A一、选择题:1、下列标示符哪些是合法的( B )A、 $timeB、 _dateC、 8sumD、 mux#2、如果线网类型变量说明后未赋值,起缺省值是( D )A、 xB、 1C、 0D、 z3、现网中的值被解释为无符号数。

在连续赋值语句中,assign addr[3:0]=-3;addr 被赋予的值是( A )A、 4’b1101B、 4’b0011C、 4’bxx11D、 4’bzz114、 reg[7:0] mema[255:0] 正确的赋值是( A )A、 mema[5]=3 ’d0,B、 8’d0;C、 1’b1;D、 mema[5][3:0]=4 ’d15、在 code 模块中参数定义如下,请问top 模块中 d1 模块 delay1、 delay2 的值是 ( D )module code(x,y); module top;paramee delay1=1,delay2=1; .code #(1,5) d1(x1,y1);endmodule endmoduleA、( 1,1)B、(5,5)C、( 5,1)D、( 1,5)6、“ a=4’b11001,b=4 ’bx110”选出正确的运算结果( B )A、 a&b=0B、a&&b=1C、b&a=xD、 b&&a=x7、时间尺度定义为timescale 10ns/100ps ,选择正确答案( C )A、时间精度 10nsB、时间单位 100psC、时间精度 100psD、时间精度不确定8、若 a=9,执行 $display( “current value=%0b,a=%0d ”,a,a)正确显示为( B )A、 current value=1001,a=09B、current vale=1001,a=9C、 1001,9D、 current vale=00 001001,a=99、 aways begin #5 clk=0; #10 clk=~clk;end 产生的波形( A )A、占空比 1/3B、 clk=1C、 clk=0D、周期为 1010、在 Verilog 中定义了宏名`define sum a+b+c 下面宏名引用正确的是( C )A、 out= ’sum+d;B、 out=sum+d;C、 out=`sum+d;D、都正确二、填空题:(共 15 分,每小题 3 分)1、某一纯组合电路输入为in1,in2 和 in3,输入出为 out ,则该电路描述中always 的事件表达式应写为always@(in1,in2,in3 ); 若某一时序电路由时钟clk 信号上升沿触发,同步高电平复位信号rst 清零,该电路描述中always 的事件表达是应该写为always @( posedge clk )。

verilog考试题

verilog考试题西安电⼦科技⼤学考试时间分钟试题1.考试形式:闭(开)卷;2.本试卷共四⼤题,满分100分。

班级学号姓名任课教师⼀、选择题(每题2分,共18分)1. 下⾯哪个是可以⽤verilog语⾔进⾏描述,⽽不能⽤VHDL语⾔进⾏描述的级别?( A )(A) 开关级 (B)门电路级 (C) 体系结构级 (D) 寄存器传输级2.在verilog中,下列语句哪个不是分⽀语句?( D )(A) if-else (B) case (C) casez (D) repeat3.下列哪些Verilog的基本门级元件是多输出( D )(A) nand (B) nor (C) and (D) not4.Verilog连线类型的驱动强度说明被省略时,则默认的输出驱动强度为( B )(A) supply (B) strong (C) pull (D) weak5.元件实例语句“notif1 #(1:3:4,2:3:4,1:2:4) U1(out,in,ctrl);”中截⾄延迟的典型值为( B )(A) 1 (B) 2 (C) 3 (D) 46.已知“a =1b’1; b=3b'001;”那么{a,b}=( C )(A) 4b'0011 (B) 3b'001 (C) 4b'1001 (D) 3b'1017.根据调⽤⼦模块的不同抽象级别,模块的结构描述可以分为(ABC )(A) 模块级 (B)门级 (C) 开关级 (D) 寄存器级8.在verilog语⾔中,a=4b'1011,那么 &a=(D )(A) 4b'1011 (B) 4b'1111 (C) 1b'1 (D) 1b'09.在verilog语⾔中整型数据与( C )位寄存器数据在实际意义上是相同的。

(A) 8 (B) 16 (C) 32 (D) 64⼆、简答题(2题,共16分)1.Verilog HDL语⾔进⾏电路设计⽅法有哪⼏种(8分)1、⾃上⽽下的设计⽅法(Top-Down)2、⾃下⽽上的设计⽅法(Bottom-Up)3、综合设计的⽅法2.specparam语句和parameter语句在参数说明⽅⾯不同之处是什么(8分)。

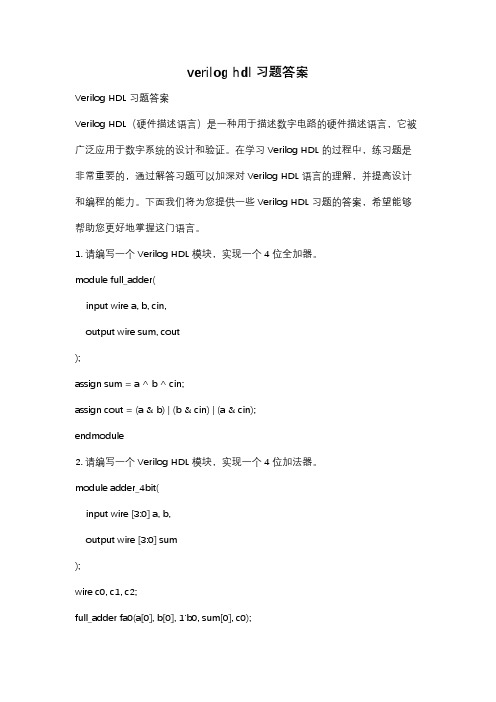

verilog hdl 习题答案

verilog hdl 习题答案Verilog HDL 习题答案Verilog HDL(硬件描述语言)是一种用于描述数字电路的硬件描述语言,它被广泛应用于数字系统的设计和验证。

在学习Verilog HDL的过程中,练习题是非常重要的,通过解答习题可以加深对Verilog HDL语言的理解,并提高设计和编程的能力。

下面我们将为您提供一些Verilog HDL习题的答案,希望能够帮助您更好地掌握这门语言。

1. 请编写一个Verilog HDL模块,实现一个4位全加器。

module full_adder(input wire a, b, cin,output wire sum, cout);assign sum = a ^ b ^ cin;assign cout = (a & b) | (b & cin) | (a & cin);endmodule2. 请编写一个Verilog HDL模块,实现一个4位加法器。

module adder_4bit(input wire [3:0] a, b,output wire [3:0] sum);wire c0, c1, c2;full_adder fa0(a[0], b[0], 1'b0, sum[0], c0);full_adder fa1(a[1], b[1], c0, sum[1], c1);full_adder fa2(a[2], b[2], c1, sum[2], c2);full_adder fa3(a[3], b[3], c2, sum[3], );endmodule3. 请编写一个Verilog HDL模块,实现一个4位移位寄存器。

module shift_register(input wire clk, rst, shift,input wire [3:0] in,output wire [3:0] out);reg [3:0] reg_data;always @(posedge clk or posedge rst) beginif(rst)reg_data <= 4'b0;else if(shift)reg_data <= {reg_data[2:0], in[0]};elsereg_data <= in;endassign out = reg_data;endmodule以上是一些常见的Verilog HDL习题的答案,通过这些习题的练习,相信您对Verilog HDL语言的掌握会更加深入。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

北京航空航天大学2011 ~2012 学年第二学期 数字EDA 期末考试试卷( 2012 年 5 月 23 日)班级:__________;学号:______________;姓名:__________________;成绩:___________注意事项:1、填空题与选择题直接在试题上作答2、设计题在答题纸上作答正题:一、填空题(共30分,每道题3分)1. 写出表达式以实现对应电路的逻辑功能。

F2. 根据图中输入输出关系将Verilog模块定义补充完整,其中信号A 为5比特宽度,其余信号为1比特宽度。

A 宽3. IEEE 标准的硬件描述语言是 verilog HDL 和 VHDL 。

4. 你所知道的可编程逻辑器件有(至少两种): FPGA, CPLD, GAL, PAL (任写其二) 。

5. 假定某4比特位宽的变量a 的值为4’b1011,计算下列运算表达式的结果6. Verilog 语言规定了逻辑电路中信号的4种状态,分别是0,1,X 和Z 。

其中0表示低电平状态,1表示高电平状态,X 表示 不定态(或未知状态) ,Z 表示 高阻态 。

assign F= E ^ ( (A&B) | (!(C&D)))module tblock( A,B,C ) ; output [4:0] A;input B;inout C; …… //省略了功能描述endmodule //模块结束 &a = 1’b0 ~a = 4’b0100 {3{a}} = 12’b101110111011 {a[2:0],a[3]} = 4’b0111 (a<4’d3) || (a>=a) = 1’b1 !a = 1’b07. 下面两段代码中信号in ,q1,q2和q3的初值分别为0,1,2和3,那么经过1个时钟周期后,左侧程序中q3的值变成 0 ,右侧程序中q3的值变成 2 。

8. Verilog 语言规定的两种主要的数据类型分别是 wire(或net) 和 reg 。

程序模块中输入,输出信号的缺省类型为 wire(或net) 。

9. 一个大型的组合电路总延时为100ns ,采用流水线将它分为两个较小的组合电路,理论上电路最高工作频率可达 20 MHz 。

10. 块语句有两种,一种是begin-end 语句,通常用来标志 顺序 执行的语句;一种是fork-join 语句,通常用来标志 并行 执行的语句。

二、选择填空题 (共30分,每道题3分)。

1. inout 端口可以定义成下列哪种数据类型 ( B )。

A 、reg 类型B 、net 类型C 、reg 或net 类型D 、整数类型2. 下列数组描述中不正确的代码是( D )。

A 、integer cou [7:0] ; B 、reg bool [16:0] ; C 、integer mat [4:0][0:127] ; D 、reg [8*8:1] carray_value;3. 下列描述中采用时钟正沿触发且reset 异步下降沿复位的代码描述是 ( C ) A 、always @(posedge clk, negedge reset) if(reset)B 、always@(posedge clk, reset) if (!reset)C 、always @(posedge clk, negedge reset) if(!reset)D 、always @(negedge clk, posedge reset) if (reset)4. 下列代码描述中,不能产生时序逻辑的( A ) A 、always (*) begain if (a&b) rega=c; else rega=0; endB 、always (*) begainalways @(posedge clk) begin q1 = in; q2 = q1; q3 = q2; end always @(posedge clk) begin q1 <= in; q2 <= q1; q3 <= q2; endif (a&b) rega=c;y=rega;endC、always @(a)begainCase(a)2’b00: out=4’b0001;2’b01: out=4’b0010;2’b10: out=4’b0100;endcaseend5.在高速系统设计中,下列哪种优化方案的目的不是为了提高系统的工作频率(D )A、流水线 B、树型结构 C、迟置信号后移 D、资源共享6.状态机的编码风格包括一段式、两段式和三段式,下列描述正确的是(C )A、一段式寄存器输出,易产生毛刺,不利于时序约束;B、二段式组合逻辑输出,不产生毛刺,有利于时序约束;C、三段式寄存器输出,不产生毛刺,有利于时序约束;D、所有描述风格都是寄存器输出,易产生毛刺,有利于时序约束。

7.下列描述代码可综合的是(C )A、fork… joinB、assign/deassignC、if…else和caseD、repeat 和forever8.关于过程块以及过程赋值描述中,下列正确的是(A )A、在过程赋值语句中表达式左边的信号一定是寄存器类型;B、过程块中的语句一定是可综合的;C、在过程块中,使用过程赋值语句给wire赋值不会产生错误;D、过程块中时序控制的种类有简单延迟、边沿敏感和电平敏感。

9.关于函数的描述下列说法不正确的是(B )A、函数定义中不能包含任何时序控制语句;B、函数至少有一个输入,包含任何输出或双向端口;C、函数只返回一个数据,其缺省为reg类型;D、函数不能调用任务,但任务可以调用函数。

10.Verilog语言与C语言的区别,不正确的描述是(C )A、Verilog语言可实现并行计算,C语言只是串行计算;B、Verilog语言可以描述电路结构,C语言仅仅描述算法;C、Verilog语言源于C语言,包括它的逻辑和延迟;D、Verilog语言可以编写测试向量进行仿真和测试。

三、(10分)试设计一个3/8译码器,规定模块定义为module Decoder(Out,In,En),其中Out 为译码器输出,In为译码器输入,En为译码使能输入。

要求:写出3/8译码器Verilog HDL设计程序并注释;标准答案1:module decoder(Out,In,En); (2分)output [7:0] out;input [2:0] in;input en; //IO定义(3分)assign out = (en==0)?0:1’b1<<In; /*若En为高电平,3/8译码,否则输出无效电平*/(5分)endmodule标准答案2:module decoder(Out,In,En); (2分)output [7:0] out;input [2:0] in;input en; //IO定义(3分)reg [7:0] out;always @ (In or En)beginif(En == 0) //若En为低电平,3输出无效电平(2分)Out = 8’b0;else //若En为高电平,3/8译码(3分)case(in)3’b000: Out = 8’b00000001; //03’b001: Out = 8’b00000010; //13’b010: Out = 8’b00000100; //23’b011: Out = 8’b00001000; //33’b100: Out = 8’b00010000; //43’b101: Out = 8’b00100000; //53’b110: Out = 8’b01000000; //63’b111: Out = 8’b10000000; //7endcaseend四、(20分)试使用Verilog HDL设计一个10进制计数器,规定模块定义为module count10(out,clr,clk),其中clk为时钟输入,clr为同步清零输入,低电平有效,out为计数器输出。

要求(1)写出10进制计数器Verilog HDL设计程序并注释;(2)写出10进制计数器Verilog HDL测试文件并注释;标准答案(1)module counter10(out,clr,clk);input clr,clk; //IO端口定义output out;reg [3:0] cnt; //计数always @ (posedge clk)if(!clr)cnt <= 1’b0;else if(cnt == 4’d9)cnt <= 1’b0;elsecnt <= cnt + 1’b1;assign out = (cnt == 4’d9); //计数结果输出endmodule(2)module counter10_test;reg clk, rst;wire out;initial //赋初值beginrst = 1’b0;clk = 1’b0;#100rst = 1’b1;endalways #10 clk = ~clk; //产生时钟信号counter10 u0(.out(out),.clr(rst),.clk(clk)); //调用设计模型endmodule五、根据下列Verilog代码给出电路结构图,针对资源共享的思想分析电路的问题点并提出改进方法,用Verilog语言描写并给出电路结构图。

(五题和六题任选一题)源代码描述如下:for(i=0,i<=3,i=i+1)beginif (enable[i] ==1)vsum = vsum+ offset[i];elsevsum = vsum;end原代码对应的电路如下所示:for (i=0;i<=3;i=i+1) begin if (enable[i] ==1) offset_1= offset_1+ offset[i]; else vsum = vsum; endvsum = vsum+offset_1;评分标准:画出原代码对应的电路,并分析出资源特点得4分 画出优化后的电路,并分析出资源特点得4分 写出了优化后的源代码得2分。

六、(10分)使用状态机设计一个“11011”序列检测器,序列输入为s_in ,检测结果输出为p_out ,高电平表示发现指定序列,低电平表示没有发现指令序列。

请对状态进行定义,并画出状态转移图。

(10分)(五题和六题任选一题)0/0状态定义:IDLE :3’b000 未检出有效比特 A : 3’b001 检出有效比特1 B : 3’b010 检出有效比特11 C : 3’b011 检出有效比特110 D : 3’b100 检出有效比特1101 E : 3’b101 检出有效比特11011图中使用了4个选择器以及4个4位加法器。