verilog语言设计-同步清零计数器

verilog统计出现次数最优写法

在Verilog中,统计某个信号出现次数的最优写法可能会因具体的应用场景和需求而异。

以下是一种常见的方法,使用一个计数器来统计信号出现的次数:

```verilog

module counter (

input clk,

input rst,

input signal,

output reg [31:0] count

);

always @(posedge clk or posedge rst) begin

if (rst) begin

count <= 32'b0;

end else if (signal) begin

count <= count + 1;

end

end

endmodule

```

上述代码中,`counter`模块具有以下输入输出:

* `clk`:时钟输入,用于触发计数器操作。

* `rst`:重置输入,用于将计数器归零。

* `signal`:待统计的信号输入。

* `count`:32位寄存器,用于存储信号出现的次数。

在上述代码中,使用了一个`always`块来对信号进行计数。

当时钟上升沿到来时,如果`signal`信号为高电平,则将计数器加1。

当复位信号`rst`为高电平时,将计数器归零。

这样就可以统计`signal`信号出现的次数了。

需要注意的是,上述代码仅提供了一种常见的实现方式,并不一定是最佳的解决方案。

在实际应用中,需要根据具体的需求和场景进行优化和调整。

verilog 复位赋值

verilog 复位赋值【原创实用版】目录1.Verilog 基础知识2.复位赋值的概念3.复位赋值的实现方法4.复位赋值的应用实例5.总结正文一、Verilog 基础知识Verilog 是一种硬件描述语言,主要用于数字电路和模拟混合信号电路的描述。

它具有简洁、直观、易于理解的特点,广泛应用于集成电路设计领域。

Verilog 中的基本元件包括线(wire)、寄存器(reg)、输入输出端口(input、output)等。

二、复位赋值的概念在 Verilog 中,复位赋值是一种特殊的赋值方式,用于将某个信号或寄存器的值在某个时刻恢复为初始状态。

复位赋值在数字电路设计中具有重要意义,例如在时序电路的初始状态设定、同步电路的复位控制等方面。

三、复位赋值的实现方法在 Verilog 中,可以使用连续赋值(assign)和过程赋值(always)两种方法实现复位赋值。

1.连续赋值(assign)连续赋值是一种简单的赋值方法,将一个表达式的值直接赋给一个信号或寄存器。

当驱动源(如时钟信号)发生变化时,被赋值的信号或寄存器的值会立即更新。

例如:```verilogwire clk;wire reset;reg [7:0] count;assign count = 0; // 复位赋值,将 count 的值设定为 0```2.过程赋值(always)过程赋值是一种更加灵活的赋值方法,它包含一个敏感信号条件表和一段执行语句。

当敏感信号条件表中的信号发生变化时,执行语句会被触发,从而实现复位赋值。

例如:```verilogreg [7:0] count;always @(posedge clk or posedge reset)count <= 0; // 复位赋值,当时钟信号上升沿或复位信号上升沿出现时,将 count 的值设定为 0```四、复位赋值的应用实例以下是一个简单的计数器电路,使用复位赋值实现清零功能:```verilogmodule counter (input clk,input reset,output reg [7:0] count);reg [7:0] count_temp;always @(posedge clk or posedge reset)if (reset) begincount_temp <= 0; // 复位赋值,将 count_temp 的值设定为 0end else begincount_temp <= count_temp + 1; // 计数器逻辑endassign count = count_temp; // 将 count_temp 的值赋给输出信号countendmodule```五、总结复位赋值是 Verilog 中一种重要的赋值方式,它可以将信号或寄存器的值在某个时刻恢复为初始状态。

数控技术4.2同步计数器74x163的实现

4.1时钟同步状态机的设计 4.1.1时钟同步状态机及其设计流程4.1.2 时钟同步状态机设计方法构建序列发生器4.1.3 状态图直接描述法实现序列发生器4.2同步计数器74x163的实现4.3移位寄存器的实现和应用4.3.1 74x194的实现4.3.2 使用74x194IP 核实现11001序列发生器第四章时序逻辑电路FPGA 实现CLK CLR LD ENP ENTA B C DQAQBQCQDRCO 74x1632 1 9 7103 4 5 61413121115CLK CLR_L LD_L ENP ENT 工作状态0 ×××1 0 ××× 1 1 0 ×× 1 1 ×01 1 1 1同步清零同步置数保持保持,RCO=0计数74x163回顾74x163自由工作模式CLK CLR LD ENP ENTA B C DQA QB QC QDRCO74x163+5Vclk21971034561413121115QAQBQC QD RCORPU R自由模式时,QDQCQBQA 输出在每个时钟边沿变化,从0000开始计数,0000-0001-0010…1111-0000…完成从0到15的循环计数,当计数值为15时,RCO 有效,输出1。

1.module p74x163(clk,clr_l,ld_l,enp,ent,d,q,rco);2.input clk,clr_l,ld_l,enp,ent;3.input[3:0] d;4.output [3:0] q;5.output rco;6.reg[3:0] q=0;7.reg rco=0;8.always @ (posedge clk) begin9.if (clr_l==0) q<=0;10.else if (ld_l==0) q<=d;11.else if ((ent==1) && (ent==1)) q<=q+1;12.else q<=q;13.end14.always @ (q or ent) begin15.if ((ent==1) && (q==15)) rco=1;16.else rco=0;CLKCLRLDENPENTABCDQAQBQCQDRCO74x163219710345614131211151.`timescale 1ns / 1ps2.module sim1;3.reg clk=0;4.reg clr_l=1;5.reg ld_l=1;6.reg enp=1;7.reg ent=1;8.reg[3:0] d=0;9.reg[3:0] q=0; 10.wire rco;11.p74x163 uut(clk,clr_l,ld_l,enp,ent,d,q,rco);12.always # 10 clk=~clk; 13.endmodule1.module p74x163(clk,clr_l,ld_l,enp,ent,d,q,rco);2.input clk,clr_l,ld_l,enp,ent;3.input[3:0] d;4.output [3:0] q;5.output rco;CLKCLR LD ENP ENT A B C DQA QB QC QD RCO74x163219710345614131211151.ERROR: [USF-XSim-62] 'elaborate' step failed with error(s). Please check the Tcl console output or'E:/provivado/bppro/p_74x163/p_74x163.si m/sim_1/behav/elaborate.log' file for more information.Vivado Simulator 2015.3Copyright 1986-1999, 2001-2015 Xilinx, Inc. All Rights Reserved. Running: D:/xilinx/Vivado/2015.3/bin/unwrapped/win64.o/xelab.exe -wto bac9eefe3b0f4d5599d8113dcd71e272 --debug typical --relax --mt2 -L xil_defaultlib-L unisims_ver-L unimacro_ver-L secureip--snapshot sim1_behav xil_defaultlib.sim1 xil_defaultlib.glbl-log elaborate.logUsing 2 slave threads.Starting static elaborationERROR: [VRFC 10-529] concurrent assignment to a non-net q is not permitted[E:/provivado/bppro/p_74x163/p_74x163.srcs/sim_1/new/sim1.v:11] ERROR: [XSIM 43-3322] Static elaboration of top level Verilog design1.`timescale 1ns / 1ps2.module sim1;3.reg clk=0;4.reg clr_l=1;5.reg ld_l=1;6.reg enp=1;7.reg ent=1;8.reg[3:0] d=0;9.wire[3:0] q; 10.wire rco;11.p74x163 uut(clk,clr_l,ld_l,enp,ent,d,q,rco);12.always # 10 clk=~clk; 13.endmodule1.module p74x163(clk,clr_l,ld_l,enp,ent,d,q,rco);2.input clk,clr_l,ld_l,enp,ent;3.input[3:0] d;4.output [3:0] q;5.output rco;CLKCLR LD ENP ENT A B C DQA QB QC QD RCO74x16321971034561413121115有缘学习更多+谓ygd3076或关注桃报:奉献教育(店铺)接下来:移位寄存器的实现和应用。

同步计数器与异步计数器设计的比较与分析

同步计数器与异步计数器设计的比较与分析概述:计数器是现代电子电路常用的组件之一,广泛应用于各个领域中。

其中,同步计数器与异步计数器是最基本的两种设计方式。

本文将比较并分析这两种计数器的设计差异,探讨其优缺点及适用场景。

一、同步计数器的设计同步计数器是由触发器和逻辑门构成的组合逻辑电路。

其设计特点如下:1. 所有的触发器都由统一的时钟信号驱动,使得计数器在特定时刻同步更新,保证所有触发器的状态变化在同一时间发生。

2. 同步计数器的设计简单,可靠性高,稳定性好。

3. 连续触发器之间的输出相互连接,使得同步计数器的输出可以直接用于其他电路。

二、异步计数器的设计异步计数器的设计相对于同步计数器来说更为复杂,其主要特点如下:1. 每个触发器的时钟信号可独立控制,触发器的状态变化独立于其他触发器。

2. 异步计数器的设计灵活,可以实现较为复杂的计数逻辑。

3. 输出信号的稳定性较差,需要进一步处理才能应用到其他电路中。

三、同步计数器与异步计数器的比较与分析1. 设计复杂度:同步计数器的设计相对简单,触发器之间的连接简单直接。

而异步计数器的设计更加复杂,触发器之间需要进行更多的电路连接和逻辑控制。

2. 稳定性:由于同步计数器在特定时刻同步更新,所有触发器的状态变化在同一时间发生,因此具有较好的稳定性。

而异步计数器的输出信号在转换过程中可能会因为触发器的状态变化不同步而出现瞬态错误。

3. 应用范围:同步计数器适用于大部分计数场景,尤其在对计数稳定性要求较高的场合。

异步计数器则适用于对计数逻辑要求较为复杂的场合,可以灵活实现各种计数模式。

4. 同步性能:由于同步计数器需要等待整个时钟周期才能更新状态,因此其计数速度受到时钟频率的限制。

而异步计数器的状态更新可以在任意时刻发生,不受时钟频率的限制,计数速度更高。

5. 逻辑灵活性:异步计数器相对于同步计数器更具有逻辑灵活性,可以方便地实现复杂的计数逻辑。

同步计数器的设计较为简单,适用于大部分基本计数需求。

用74ls161实现计数器的同步级联,仿真图实现csdn

用74ls161实现计数器的同步级联,仿真图实现csdn

首先,确保你有足够的74LS161芯片。

每个芯片有4个同步可重置4位二进制计数器。

按照

将时钟输入(CLK)连接到每个芯片的时钟输入引脚(CLK)。

将清零信号(CLR)连接到每个芯片的同步清零输入引脚(CLR)。

将计数使能信号(CE)连接到每个芯片的计数使能输入引脚(CE)。

将数据输入(D0-D3)连接到第一个芯片的数据输入引脚(D0-D3)。

将Q0-Q3输出连接到下一个芯片的数据输入引脚(D0-D3)。

设置初始值:将每个芯片的清零信号(CLR)连接到高电平以清零计数器。

根据需要,可以将计数使能信号(CE)连接到高电平或低电平来控制计数器的启动和停止。

提供一个时钟信号(CLK)来触发计数器的计数操作。

使用仿真软件,如Proteus、Multisim等,在电路图中添加所连接的芯片并设置适当的输入信号。

运行仿真并观察计数器的输出。

你应该能够看到计数器按照设定的时钟脉冲进行计数。

如果你想进一步扩展计数器的位数,只需将上一个计数器的输出(Q0-Q3)连接到下一个计数器的数据输入引脚(D0-D3),并重复步骤2-7。

ISE 38译码器设计及VHDL八进制计数器

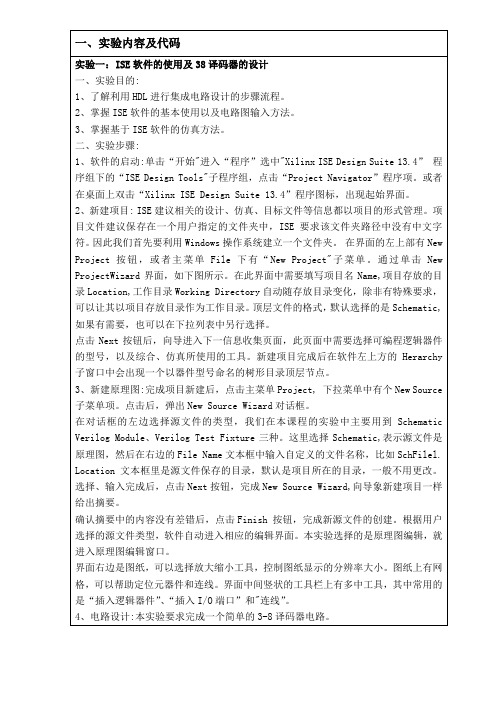

目文件建议保存在一个用户指定的文件夹中,ISE要求该文件夹路径中没有中文字符。因此我们首先要利用Windows操作系统建立一个文件夹。在界面的左上部有New Project按钮,或者主菜单File下有“New Project"子菜单。通过单击New ProjectWizard界面,如下图所示。在此界面中需要填写项目名Name,项目存放的目录Location,工作目录Working Directory自动随存放目录变化,除非有特殊要求,可以让其以项目存放目录作为工作目录。顶层文件的格式,默认选择的是Schematic,如果有需要,也可以在下拉列表中另行选择。

完成后点击Next按钮,出现摘要对话框,确认设计信息无误后,点击Finish按钮,完成Verilog源文件的建立。

3、Veriog程序设计:要求设计一一个同步置数、同步清零的8位二进制计数器。

根据功能要求,设计电路的输入、输出,根据逻辑关系确定输入、输出之间的逻辑关系,设计算法描述这种逻辑关系,用Verilog语言描述算法,得到如下的Verilog程序:

文件中每一行都代表一个管脚映射,#号表示注释。因此NET应该是表示网络名,后面跟程序里的端口名,示例中"atlys_ led[0]”是用户程序中的网络名。LOC= U18是指定芯片管脚,#tlys LDO是注释,表示U18连接的是一个编号为LD0的指示灯,这种对应关系是由硬件决定的。

对于8位二进制计数器而言,可以编辑出如下的用户约束文件:

一、实验内容及代码

实验一:ISE软件的使用及38译码器的设计

一、实验目的:

1、了解利用HDL进行集成电路设计的步骤流程。

2、掌握ISE软件的基本使用以及电路图输入方法。

计数器的设计

计数器的设计

计数器是一种电子数字电路,用于记录某个事件或进程的次数。

设计计数器的步骤如下:

1.确定计数器的位数:计数器的位数决定了它能够计数的最大值。

例如,一个

8位二进制计数器可以计数0到255之间的所有整数。

根据实际需求,选择适当的位数。

2.设计计数器的时钟输入电路:计数器的时钟输入决定了它何时进行计数。

通

常使用晶体振荡器或者其他时钟源来提供计数器的时钟信号。

3.选择计数器的计数模式:计数器可以分为同步计数器和异步计数器。

同步计

数器的各个位同时进行计数,而异步计数器的各个位独立进行计数。

根据具体需求选择合适的计数模式。

4.选择计数器的计数方式:计数器可以被设计为向上计数或向下计数。

向上计

数表示计数器的值递增,而向下计数表示计数器的值递减。

根据具体需求选择合适的计数方式。

5.设计计数器的清零电路:计数器需要在一些特定的时刻进行清零操作,以便

重新开始计数。

为此,需要设计清零电路,使计数器的值归零。

6.设计计数器的输出电路:计数器的输出电路将其计数器的值转换成数字形式

或者其他需要的形式,例如LED显示屏、七段数码管等。

7.选取适当的计数器芯片:根据具体需求选择合适的计数器芯片,例如74LS161、

74LS163等,这些芯片可以快速地实现基于上述设计步骤的计数器电路。

需要注意的是,在设计计数器时,应当根据实际情况进行仿真测试,确保其正常工作并满足设计要求。

同步与异步计数器的设计与分析

同步与异步计数器的设计与分析计数器是数字电路中常用的模块之一,用于计数和记录特定事件发生的次数。

其中,同步计数器和异步计数器是两种常见的设计方法。

本文将对同步与异步计数器的设计原理与分析进行介绍。

一、同步计数器的设计与分析同步计数器是一种基于时钟信号的计数器,它的输入和输出在时钟边沿进行同步。

以下是同步计数器的设计步骤:1. 确定计数器的位数和计数范围:根据实际需求确定所需计数器的位数和计数范围,例如一个4位二进制计数器可以计数0~15。

2. 设计计数器的状态转移表:根据计数器的位数和计数范围,设计计数器的状态转移表。

以4位二进制计数器为例,其状态转移表如下:当前状态(Q) 输入(D) 下一个状态(Q+1)0000 0 00010001 0 00100010 0 00110011 0 0100...1101 0 11101110 0 11111111 0 00003. 实现计数器的状态转移方程:根据状态转移表,可以得到计数器的状态转移方程。

以4位二进制计数器为例,其状态转移方程如下: Q0+ = Q0' + Q1' + Q2' + Q3'Q1+ = Q1' + Q2' + Q3'Q2+ = Q2' + Q3'Q3+ = Q3' + 1其中,Q0~Q3表示当前状态的各个位,Q0+~Q3+表示下一个状态的各个位。

4. 实现计数器的逻辑电路图:根据状态转移方程,可以设计计数器的逻辑电路图。

以4位二进制计数器为例,其逻辑电路图如下: Q0+ = Q0' + Q1' + Q2' + Q3'Q1+ = Q1' + Q2' + Q3'Q2+ = Q2' + Q3'Q3+ = Q3' + 15. 分析同步计数器的特性:对于同步计数器,由于输入和输出在时钟边沿同步,因此具有较低的时序延迟和较高的稳定性。

同步二进制计数器的电路

同步二进制计数器的电路1. 引言同步二进制计数器是一种常见的数字电路,用于计数和记录输入脉冲的数量。

它由多个触发器组成,通过时钟信号同步触发器的状态改变,从而实现计数功能。

本文将介绍同步二进制计数器的原理、设计方法以及应用场景。

2. 原理同步二进制计数器由多个触发器组成,其中每个触发器都有两个输入:时钟信号和清零信号。

当时钟信号上升沿到达时,触发器根据其输入状态改变输出状态。

当清零信号为高电平时,触发器将输出置为0。

在同步二进制计数器中,每个触发器都与前一个触发器相连,并且第一个触发器与外部输入信号相连。

当时钟信号上升沿到达时,第一个触发器会检测到外部输入脉冲,并将其传递给下一个触发器。

这样,在每个时钟周期内,每个触发器都会将前一个触发器的输出传递给下一个触发器。

3. 设计方法3.1 触发器选择在设计同步二进制计数器时,需要选择适当的触发器。

常见的触发器有D触发器、JK触发器和T触发器。

根据具体的需求,选择合适的触发器进行设计。

3.2 计数位数确定根据需要计数的范围,确定计数器需要多少位。

例如,如果需要计数0到15之间的数字,那么需要一个4位计数器。

3.3 连接触发器将选择好的触发器按照顺序连接起来,构成同步二进制计数器电路。

每个触发器都与前一个触发器相连,第一个触发器与外部输入信号相连。

3.4 添加清零功能为了能够在需要时将计数值清零,可以在每个触发器上添加清零信号输入,并通过逻辑门控制清零信号的传递。

4. 应用场景同步二进制计数器广泛应用于各种领域,包括但不限于以下几个方面:4.1 计时和测量同步二进制计数器可以用于计时和测量应用中。

通过连接合适数量的同步二进制计数器,可以实现高精度的时间测量和频率测量。

4.2 数据传输和通信同步二进制计数器可以用于数据传输和通信应用中。

通过将计数器的输出与其他电路相连,可以实现数据的同步传输和时序控制。

4.3 事件触发和触发控制同步二进制计数器可以用于事件触发和触发控制应用中。

verilog基本电路设计(包括:时钟域同步、无缝切换、异步fifo、去抖滤波))

Verilog基本电路设计(包括:时钟域同步、无缝切换、异步FIFO、去抖滤波))Verilog基本电路设计共包括四部分:单bit跨时钟域同步时钟无缝切换异步FIFO去抖滤波Verilog基本电路设计之一: 单bit跨时钟域同步(帖子链接:/thread-605419-1-1.html)看到坛子里不少朋友,对于基本数字电路存在这样那样的疑惑,本人决定开贴,介绍数字电路最常见的模块单元,希望给初学者带来帮助,也欢迎大佬们前来拍砖。

如果想要做数字设计,下面这些电路是一定会碰到的,也是所有大型IP,SOC设计必不可少的基础,主要包括异步信号的同步处理,同步FIFO,异步FIFO,时钟无缝切换,信号滤波debounce等等,后面会根据大家反馈情况再介绍新电路。

首先介绍异步信号的跨时钟域同步问题。

一般分为单bit的控制信号同步,以及多bit的数据信号同步。

多bit的信号同步会使用异步FIFO完成,而单bit的信号同步,又是时钟无缝切换电路以及异步FIFO电路的设计基础,这里先介绍单bit信号同步处理。

clka域下的信号signal_a,向异步的clkb域传递时,会产生亚稳态问题。

所有的亚稳态,归根结底就是setup/hold时间不满足导致。

在同一个时钟域下的信号,综合以及布线工具可以在data路径或者clock路径上插入buffer使得每一个DFF的setup/hold时间都满足;但是当signal_a在clkb域下使用时,由于clka与clkb异步,它们的相位关系不确定,那么在clkb的时钟沿到来时,无法确定signal_a此时是否处于稳定无变化状态,也即setup/hold时间无法确定,从而产生亚稳态。

这种异步信号在前后端流程里面是无法做时序分析的,也就是静态时序分析里常说的false_path。

消除亚稳态,就是采用多级DFF来采样来自另一个时钟域的信号,级数越多,同步过来的信号越稳定。

对于频率很高的设计,建议至少用三级DFF,而两级DFF同步则是所有异步信号处理的最基本要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电子技术基础可编程逻辑器件大作业106进制同步清零计数器

班级:0906101

学号:1090610106

姓名:康代涛

1.同步清零计数器

1.1设计目的与要求

利用Verilog HDL设计一个以自己学号后三位为模的计数器。

设计要求:1.编写源程序2.给出仿真电路图和仿真波形图。

1.2 Verilog HDL源代码

module counter_106(clk,reset,out);

input clk;

input reset;

output[6:0] out;

reg[6:0] out;

always@(posedge clk)

begin

if(reset==1) out<=0;

else if(out==105) out<=0;

else out<=out+1;

end

endmodule

1.3仿真原理图

同步清零计数器的仿真电路如下图所示:

1.4 仿真波形图

同步清零计数器仿真波形如下图所示:

2设计总结

本次设计需要利用Verilog HDL设计一个以自己学号后三位为模的计数器,而且要编写源程序并给出仿真电路图和仿真波形图。

通过本次设计,使自己初步了解了如何利用Quartus II 9.1 设计可编程逻辑器件,巩固了用Verilog HDL 语言编写硬件描述电路,以这样一种方式使自己复习并进一步熟悉了Verilog语言,对自己在数字电子技术方面的学习有很大作用。

参考文献:

[1]杨春玲,王淑娟,《数字电子技术基础》,高等教育出版社,2011.6

[2]王立欣,杨春玲,《电子技术实验与课程设计》,哈尔滨工业大学出版社,2009

[3]廉玉欣,《电子技术基础实验教程》,机械工业出版社,2010。