基于QuartusII的同步计数器设计

北京科技大学数电实验四 Quartus II集成计数器及移位寄存器应用

北京科技大学实验报告学院:高等工程师学院专业:自动化(卓越计划)班级:自E181姓名:杨威学号:41818074 实验日期:2020 年5月26日一、实验名称:集成计数器及其应用1、实验内容与要求(1)用74161和必要逻辑门设计一个带进位输出的10进制计数器,采用同步置数方法设计;(2)用两个74161和必要的逻辑门设计一个带进位输出的60进制秒计数器;2、实验相关知识与原理(1)74161是常用的同步集成计数器,4位2进制,同步预置,异步清零。

引脚图功能表其中X。

3、10进制计数器(1)实验设计1)确定输入/输出变量输入变量:时钟信号CLK、复位信号CLRN;输出变量:计数输出QD、QC、QB、QA,进位输出RCO,显示译码输出OA、OB、OC、OD、OE、OF、OG2)计数范围:0000-10013)预置数值:00004)置数控制端LDN:计数到1001时输出低电平5)进位输出RCO:计数到1001时输出高电平画出如下状态转换表:CP QDQCQBQA0 00001 00012 00103 00114 01005 01016 01107 01117 10009 100110 0000(2)原理图截图仿真波形如下功能验证表格CLRN QD QC QB QA RCO0 0 0 0 0 01 0 0 0 1 01 0 0 1 0 01 0 0 1 1 01 0 1 0 0 01 0 1 0 1 01 0 1 1 0 01 0 1 1 1 01 1 0 0 0 01 1 0 0 1 11 0 0 0 0 04、60进制秒计数器(1)实验设计1)确定输入/输出变量输入变量:时钟信号CLK、复位信号CLRN;输出变量:计数十位输出QD2、QC2、QB2、QA2和计数个位输出QD1、QC1、QB1、QA1,进位输出RCO2)计数范围:0000 0000-0101 10013)预置数值:0000 00004)置数控制端LDN1(个位):计数到0101 1001时输出低电平5)清零端CLRN2(十位):计数到0110时输出低电平6)ENT:个位计数到1001时输出高电平7)进位输出RCO:计数到1001时输出高电平画出如下状态转换表CP QD2QC2QB2QA2QD1QC1QB1QA1CPQD2QC2QB2QA2QD1QC1QB1QA1CPQD2QC2QB2QA2QD1QC1QB1QA10 0000 0000 20 0010 0000 40 0100 00001 0000 0001 21 0010 0001 41 0100 00012 0000 0010 22 0010 0010 42 0100 00103 0000 0011 23 0010 0011 43 0100 00114 0000 0100 24 0010 0100 44 0100 01005 0000 0101 25 0010 0101 45 0100 01016 0000 0110 26 0010 0110 46 0100 01107 0000 0111 27 0010 0111 47 0100 01118 0000 1000 28 0010 1000 48 0100 10009 0000 1001 29 0010 1001 49 0100 100110 0001 0000 30 0011 0000 50 0101 000011 0001 0001 31 0011 0001 51 0101 000112 0001 0010 32 0011 0010 52 0101 001013 0001 0011 33 0011 0011 53 0101 001114 0001 0100 34 0011 0100 54 0101 010015 0001 0101 35 0011 0101 55 0101 010116 0001 0110 36 0011 0110 56 0101 011017 0001 0111 37 0011 0111 57 0101 011118 0001 1000 38 0011 1000 58 0101 100019 0001 1001 39 0011 1001 59 0101 100160 0000 0000 (2)设计原理图截图(3)实验仿真仿真波形:仿真结果表:5、实验思考题:(1)总结任意模计数器的设计方法。

实验4:同步计数器及其应用实验报告

实验4:同步计数器及其应用实验报告

一、实验目的

1、了解可编程数字系统设计的流程

2、掌握Quartus II 软件的使用方法

3、掌握原理图输入方式设计数字系统的方法和流程

4、掌握74LS161同步16进制计数器的特点及其应用

二、实验设备

1、计算机:Quartus II 软件

2、Altera DE0 多媒体开发平台

3、集成电路:74LS10

4、集成电路:74LS161

三、实验内容

1、74LS161逻辑功能的测试

2、用74LS161实现12进制计数(异步清零)

3、用74LS161实现12进制计数(同步置数)

四、实验原理

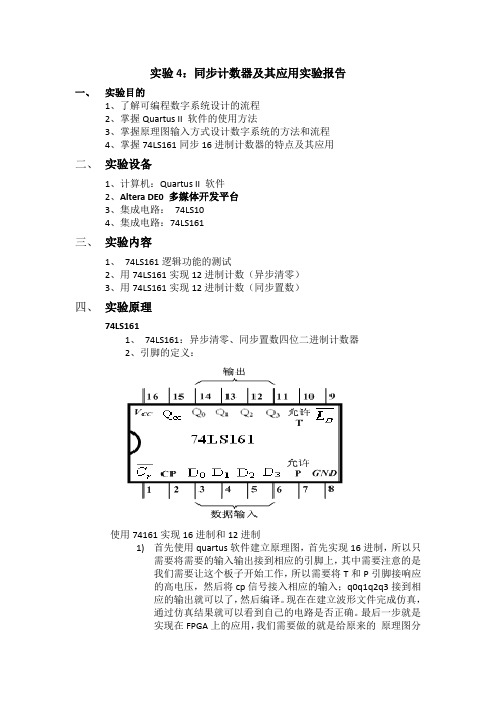

74LS161

1、74LS161:异步清零、同步置数四位二进制计数器

2、引脚的定义:

使用74161实现16进制和12进制

1)首先使用quartus软件建立原理图,首先实现16进制,所以只

需要将需要的输入输出接到相应的引脚上,其中需要注意的是

我们需要让这个板子开始工作,所以需要将T和P引脚接响应

的高电压,然后将cp信号接入相应的输入;q0q1q2q3接到相

应的输出就可以了,然后编译。

现在在建立波形文件完成仿真,

通过仿真结果就可以看到自己的电路是否正确。

最后一步就是

实现在FPGA上的应用,我们需要做的就是给原来的原理图分

配相应的引脚,然后重新编译后,插入线就可以看到仿真结果

了。

2)12进制可以采取两种方式,也就是同步置数和异步清零两种

方式,我使用的异步清零,从而只需要对q0q1q2q3在12的时

候执行清零的动作就可以了,也就是加一个而输入的与非门就

可以了。

五、实验结果。

基于quartusⅡ的通用运算器的设计与实现

在集成电路设计领域中,各类微处理器已经成为了整个芯片系统的核心。

运算器作为其核心部件,得到广泛的发展。

与此同时,为了增加电子产品产出效率,降低制造成本,诸如Quartus II9.0等电子仿真软件相继出现,为产品开发提供了良好的开发平台。

本文根据运算器具有物美价廉、使用方便、功能性强等特点,分别对半加器、全加器、乘法器、除法器进行了仿真设计。

首先本文介绍了课题的背景、意义、发展现状及未来走向,并对研究内容及设计方案进行了简单介绍。

其次对设计环境QuartusⅡ平台及VHDL做了介绍。

之后对半加器、全加器、乘法器、除法器的设计进行了详细描述,包括工作原理、真值表及流程图,还把乘法器分成各个模块,并对各个模块进行了详细的介绍与设计分析。

随后对半加器、全加器、乘法器、除法器进行了编程、仿真以及在QuartusⅡ平台上对仿真结果进行验证。

从而做到了从理论到实践,学以致用。

关键词:运算器;QuartusⅡ;VHDLIn the field of integrated circuit design, all kinds of microprocessors has become the core of the whole chip system. Unit as its core component, is widely development.At the same time, in order to increase the electronic products output efficiency, reduce manufacturing cost, such as the QuartusII 9.0 electronic simulation software appeared, such as for product development provides a good development platform.Based on the arithmetic unit has the good and inexpensive, easy to use, functional characteristics, respectively, half adder, full adder, multiplier and divider design has carried on the simulation. First this article introduces the topic background, significance, status quo and future development, and research contents and the design scheme of a simple introduction. Secondly on the design environment QuartusII platform and VHDL is presented. After full adder and full adder, multiplier and divider design are described in detail, including the working principle, the truth table and flow chart, also the multiplier is divided into various modules, and each module are analyzed in detail and design. Then half adder, full adder, multiplier and divider for programming, simulation, and in the QuartusII platform of simulation results to validate. Thus did it from theory to practice, to practice.Keywords: Arithmetic unit;VHDL;QuartusII1 引言 (1)1.1 课题背景及意义 (1)1.2 课题的现状与发展 (1)1.3 研究内容与设计方案 (1)2 开发环境 (3)2.1 Quartus II平台介绍 (3)2.1.1 Quartus II简介 (3)2.1.2 Quartus II总体设计 (4)2.1.3 Quartus II总体仿真 (8)2.2 VHDL语言介绍 (9)2.2.1 VHDL语言概述 (9)2.2.2 VHDL语言介绍 (10)2.2.3 VHDL应用开发介绍 (12)3 基于Quartus II的半加、全加器的设计与实现 (13)3.1 基于Quartus II的半加器运算 (13)3.1.1 半加器的原理与真值表 (13)3.1.2 半加器的设计与实现 (13)3.2 基于Quartus II的全加器运算 (22)3.2.1 全加器的原理、真值表和原理图 (22)3.2.2全加器的设计与实现 (24)4 基于Quartus II的乘法、除法器的设计与实现 (25)4.1 基于Quartus II的乘法器运算 (25)4.1.1 乘法器的原理和流程图 (25)4.1.2 四位二进制加法器模块 (28)4.1.3 八位二进制加法器模块 (29)4.1.4 一位乘法器模块 (31)4.1.5 8位右移寄存器模块 (33)4.1.6 乘法器的其他模块 (34)4.2 基于Quartus II的除法器运算 (39)4.2.1 除法器的原理与流程图 (39)4.2.2 除法器的设计与实现 (40)结论 (43)致谢 (44)参考文献 (45)附录A 英语原文 (46)附录B 汉语翻译 (56)1 引言1.1 课题背景及意义Quartus II具有界面友好、操作简单的特点,作为高效的EDA设计工具集合,与第三方软件扬长补短,使软件功能越来越强大,为用户提供了更加丰富的Quartus II平台。

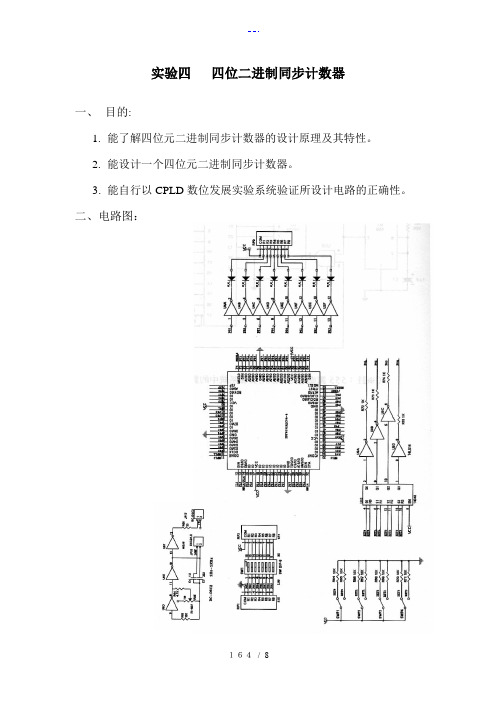

实验四四位二进制同步计数器

实验四四位二进制同步计数器一、目的:1.能了解四位元二进制同步计数器的设计原理及其特性。

2.能设计一个四位元二进制同步计数器。

3.能自行以CPLD数位发展实验系统验证所设计电路的正确性。

二、电路图:三、实验器配置图:四、实验步骤与画面:1.建立一个名为count16.vhd的新文件,并在QuartusⅡ文字编辑器中,以VHDL语言来设计程式,图为四位二进制计数器的VHDL代码。

其中clk为时钟端口,clk为异步清零端,Q为计数输出端口,co为进位输出端口。

2.存储、检查及编译。

3.创建元件符号。

4.创建波形文件,设定合适的端口信号,仿真元件的波形。

观察波形图可以看出当芯片可以实现16进制计数功能。

五、相关说明:1.同步计数器的意义是将所有正反器的时脉连接在一起,当时脉进来时,所有的正反器同时被触发而动作,因此传递延迟时间就可以大为缩短,计数的速度就会增快。

2.我们可以利用MAX+plusⅡ的Timing Analyzer来比较同步计数器与非同步计数器(单元十)的传递延迟状况,图U12-3(a)与图U12-3(b)为分析所得结果,从图中可以发现,同步计数器从时脉输入到各级的输出,其传递延迟时间皆相同,而非同步计数器则越到后级传递延迟时间越长。

3.图U12-2的程式设计方法,也可以改用D型正反器来设计,如图U12-4所示,您可以发现此种设计同步计数器的方法较简洁。

4.若要将图U12-4改成下数计数器,只要将叙述ff[].d=ff[].q+1;改成ff[].d=ff[].q-l;即可。

5.图U12-5为四位元含致能及清除的模10上下数计数器,其中的设计重点为:(1)为了能在高频计数电路应用,本电路的清除方式采同步清除式设计,并不利用正反器本身的elrn脚,而是当clr脚输入为鬲态时,令所有正反器的D输入脚为o,达到清除的目的。

(2)程式中使用了巢状的IF THEN叙述,须注意每一层的IF THEN、 ELSIF、ELSE及END IF的对应,不要弄乱了,否则会很麻烦。

简述基于QuartusⅡ设计的频率计

重庆师范大学期末考核提交材料课程名称: EDA原理及应用院系:物理与电子工程学院时间: 2012—2013学年度第2学期专业:电子信息科学与技术(职教师资)年级: 2011级培养层次:本科学生姓名:学号:成绩:基于QuartusⅡ设计的频率计摘要:计数器在数字电路中有着广泛的应用,现提出一种计数器设计穿插在电子电路设计的教学方法,使学生能够快速地根据现有的数字电路知识转化到EDA 的应用。

关键词频率计;电子设计自动化;Verilog0 引言:随着EDA技术的发展和应用领域的扩大,EDA技术在电子信息、通信、自动控制及计算机应用等领域的重要性日益突出。

同时,随着技术市场对EDA技术需求的不断提高,产品的市场效率和技术要求也必然会反映到数学和科研领域中来。

以最近的十届全国大学生电子设计竞赛为例,涉及EDA技术的赛题从未缺席过。

对诸如斯坦福大学、麻省理工学院等美国一些著名院校的电子与计算机实验室建设情况的调研表明,其EDA技术的教学与实践的内容也十分密集;在其本科和研究生教学中有两个明显的特点:其一,各专业中EDA教学实验课程的普及率和渗透率极高;其二,几乎所有实验项目都部分或全部地融入了EDA技术,其中包括数字电路、计算机组成与设计、计算机接口技术、数字通信技术、嵌入式系统、DSP等实验内容,并且更多地注重创新性实验。

这显然是科技发展和市场需求双重影响下自然产生的结果。

1.QuartusⅡ简介:QuartusⅡ是Altera提供的FPGA/CPLD开发集成环境,Altera是世界最大的可编程逻辑器件供应商之一。

QuartusⅡ在21世纪初推出,是Altera前一代FPGA/CPLD集成开发环境MAX+plusⅡ的更新换代产品,其界面友好,使用便捷。

2.计数器设计这里首先设计测频用的、含时钟使能控制的2位十进制计数器。

2.1:设计电路原理图。

频率计的核心元件之一是含有时钟使能及进位扩展输出的十进制计数器。

含异步清零和同步使能的加法计数器设计与仿真

实验二含异步清零和同步使能的加法计数器并用数码管显示一、实验目的1、了解二进制计数器的工作原理。

2、进一步熟悉QUARTUSII 软件的使用方法和VHDL 输入。

3、时钟在编程过程中的作用。

二、实验内容本实验要求完成的任务是在时钟信号的作用下,通过使能端和复位信号来完成加法计数器的计数。

实验中时钟信号使用数字时钟源模块的1HZ 信号,用一位en表示使能端信号,用复位开关rest 表示复位信号,用LED 模块的LED1~LED7 来表示计数的二进制结果。

实验LED亮表示对应的位为‘1’LED灭表示对应的位为‘0’。

通过输入不同的值模拟计数器的工作时序,观察计数的结果。

实验箱中的拨动开关、与FPGA 的接口电路,LED 灯与FPGA 的接口电路以及拨动开关、LED 与FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。

三实验步骤1、打开QUARTUSII 软件,新建一个工程。

2、建完工程之后,再新建一个VHDL File,打开VHDL 编辑器对话框。

3、在VHDL 编辑窗口编写VHDL 程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity exp4 isport( clk ,clr,en : in std_logic;co:out std_logic;key : in std_logic_vector(3 downto 0);ledag : out std_logic_vector(6 downto 0);del : out std_logic_vector(3 downto 0));end exp4;architecture whbkrc of exp4 issignal dount : std_logic_vector(3 downto 0);beginprocess(clk)beginif clk'event and clk='1' thenif clr='1'thendount<=(others=>'0');elsif en='1'thenif key="1111"thendount<="0000";co<='1';elsedount<=dount+'1';co<='0';end if;end if;end if;del<=dount;end process;process(key)begincase key iswhen "0000" => ledag <="0111111";when "0001" => ledag <="0000110";when "0010" => ledag <="1011011";when "0011" => ledag <="1001111";when "0100" => ledag <="1100110";when "0101" => ledag <="1101101";when "0110" => ledag <="1111101";when "0111" => ledag <="0000111";when "1000" => ledag <="1111111";when "1001" => ledag <="1101111";when "1010" => ledag <="1110111";when "1011" => ledag <="1111100";when "1100" => ledag <="0111001";when "1101" => ledag <="1011110";when "1110" => ledag <="1111001";when "1111" => ledag <="1110001";when others => null;end case;end process;end whbkrc;(4)分配管脚(5)功能仿真。

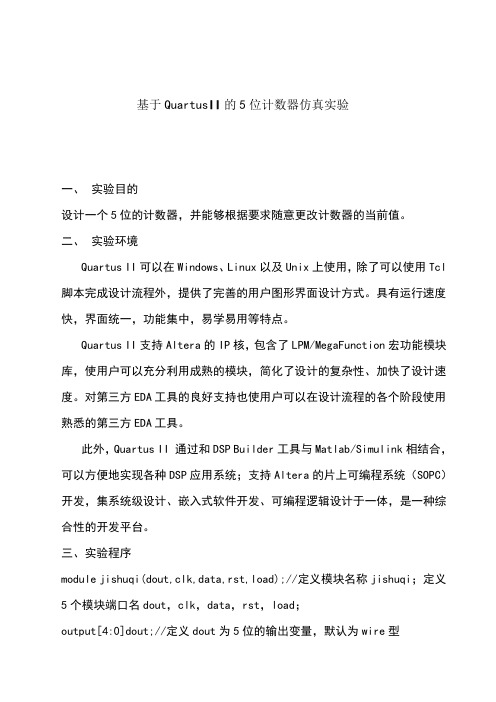

基于QuartusII的5位计数器仿真实验

基于Quartus II的5位计数器仿真实验一、实验目的设计一个5位的计数器,并能够根据要求随意更改计数器的当前值。

二、实验环境Quartus II可以在Windows、Linux以及Unix上使用,除了可以使用Tcl 脚本完成设计流程外,提供了完善的用户图形界面设计方式。

具有运行速度快,界面统一,功能集中,易学易用等特点。

Quartus II支持Altera的IP核,包含了LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性、加快了设计速度。

对第三方EDA工具的良好支持也使用户可以在设计流程的各个阶段使用熟悉的第三方EDA工具。

此外,Quartus II 通过和DSP Builder工具与Matlab/Simulink相结合,可以方便地实现各种DSP应用系统;支持Altera的片上可编程系统(SOPC)开发,集系统级设计、嵌入式软件开发、可编程逻辑设计于一体,是一种综合性的开发平台。

三、实验程序module jishuqi(dout,clk,data,rst,load);//定义模块名称jishuqi;定义5个模块端口名dout,clk,data,rst,load;output[4:0]dout;//定义dout为5位的输出变量,默认为wire型input[4:0]data;//定义data为5位的输入变量,默认为wire型input clk,rst,load;//定义clk,rst,laod为1为输出变量reg[4:0]dout;//将dout改为寄存器型变量always@(posedge rst or posedge clk)//敏感信号为clk和rst上升沿if(rst)dout=0;//如果rst=1,将data置为0else if(load)dout=data;//如果load=1,将data的值赋给doutelsedout=dout+1;其他情况下,dout自加1endmoduletestbench程序:`timescale 1 ps/ 1 ps//时间精度为1psmodule jishuqi_vlg_tst();reg eachvec;reg clk;reg [4:0] data;reg load;reg rst;wire [4:0] dout;`define period 10//定义周期为10 个时间单位jishuqi i1 (.clk(clk),.data(data),.dout(dout),.load(load),.rst(rst));initialclk=0; alwaysbegin//时钟信号加上激励#5 clk=1'b1;#5 clk=1'b0;endinitial//给各个信号加上激励begindata=5'h15;load=0;rst=1;#`period rst=0;#(`period*5)data=5'h1d;load=1;#`period load=0;#(`period*50)$finish;end endmodule三、实验结果及波形图从波形图上可以看出,当rst为0时没来一个上升沿,dout加1实现计数的效果。

根据QuartusII软件的数字时钟设计

根据QuartusII软件的数字时钟设计实验名称:数字时钟设计姓名:杨龙成班级:电子与通信工程学号: 3120302012 成绩:一、实验目的1.掌握各类计数器及它们相连的设计方法;2.掌握多个数码管显示的原理与方法;3.掌握模块化设计方式;4.掌握用VHDL语言的设计思想以及整个数字系统的设计。

二、实验内容1. 设计要求1)具有时、分、秒计数显示功能,在数码管显示00:00:00~23:59:59,以24小时循环计时。

2)完成可以计时的数字时钟时钟计数显示时有LED灯的花样显示。

3)具有调节小时、分钟及清零的功能。

4)具有整点报时功能。

2. 性能指标及功能设计1)时钟计数:完成时、分、秒的正确计时并且显示所计的数字;对秒、分60进制计数,时钟—24进制计数,并且在数码管上显示数值。

2)时间设置:手动调节分钟、小时,可以对所设计的时钟任意调时间。

可以通过实验板上的键7和键4进行任意的调整,因为时钟信号均是1HZ的,所以LED灯每变化一次就来一个脉冲,即计数一次。

3)清零功能:reset为复位键,低电平时实现清零功能,高电平时正常计数。

4)蜂鸣器在整点时有报时信号产生,产生“滴答.滴答”的报警声音。

5)根据进位情况,LED灯在时钟显示时有花样显示信号产生。

3. 系统方框图三、设计原理和过程3.1 硬件设计本设计使用VHDL硬件开发板,可编程逻辑器件EMP1270T144C5系列。

设计过程中用到的外围电路的设计有电源部分,可编程器件EMP1270T144C5,CPLD –JTAG接口,晶振和蜂鸣器,LED数码管显示,DIP开关与按键输入(具体电路见附录)3.2 软件设计3.2..1 程序包my_pkg的设计说明为了简化程序设计增加可读性,系统采用模块化的设计方法,重复使用的组件以元件(component)的形式存在,以便相关块的调用。

下面列出my_pkg组件包的代码。

library ieee;use ieee.std_logic_1164.all;package my_pkg iscomponent div40M------------------------------------------------------------------元器件1 Port( clk: in std_logic;f1hz : out std_logic);end component;component count60-----------------------------------------------------------------元器件2 Port(clr,clk:in std_logic;one :buffer std_logic_vector(3 downto 0);ten :buffer std_logic_vector(3 downto 0);full:out std_logic;dout:buffer std_logic_vector(7 downto 0));end component;component count24-----------------------------------------------------------------元器件3 Port(clr,clk:in std_logic;one :buffer std_logic_vector(3 downto 0);ten :buffer std_logic_vector(3 downto 0);full:out std_logic);end component;component scan6----------------------------------------------------------------元器件4 port (clr,clk : in STD_LOGIC;h_ten,h_one,m_ten,m_one,s_ten,s_one: in STD_LOGIC_vector(3 downto 0);cs: out STD_LOGIC_vector(5 downto 0);mux_out: out STD_LOGIC_vector(3 downto 0));end component;component bin2led---------------------------------------------------------------元器件5 port (bin : in std_logic_vector (3 downto 0);led : out std_logic_vector (7 downto 0) );end component;component sh1k ----------------------------------------------------------------------元器件6 Port( clk: in std_logic;--from system clock(40MHz)f1hz : out std_logic);-- 1Hz output signalend component;component alarm_set------------------------------------------------------------------元器件7 Port(rst,hz1: in std_logic;--system clock 1Hzalarm,ok: in std_logic;--keep pushing to declare alarm setsec_tune: in std_logic;sec_one,sec_ten:out std_logic_vector(3 downto 0));end component;end my_pkg;3.2.2 count60组件由此提供分(秒)计数值,当分计数器计数到59再来一个脉冲信号秒计数器清零从新开始计数,而进位则作为小时计数器的计数脉冲,使小时计数器计数加1,同时分计数器在分设置时钟信号的响应下设置分计数器的数值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于QuartusII的同步计数器设计

目录

一、软件及语言概述

二、实验设计

三、学习感悟

四、参考文献

一、软件及语言概述

1.1软件介绍:

Quartus II是Altera公司在21 世纪初推出的FPGA/CPLD开发环境,是Altera前一代FPGA/CPLD集成开发环境MAX+PLUS II的更新换代产品,其优点是功能强大、界面友好、使用便捷。

它支持原理图、VHDL、VerilogHDL以及AHDL 等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

Quartus II支持Altera的IP内核,包含了

LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性,加快了设计速度。

此外,Quartus II通过和DSP Builder工具与Matlab/Simulink的相结合,可以方便的实现各种DSP应用系统;支持Altera 的片上可编程系统开发,集系统设计、嵌入式软件开发。

可编程逻辑设计于一体,是一个综合性的开发平台。

Quartus II有严格的设计流程,分为设计输入与约束、分析和综合、布局布线、仿真及编程与配置等。

本次仿真设计所用到的版本为Quartus II 9.0,其用户界面如下图所示:

1.2 Verilog HDL语言概述:

Verilog HDL即Verilog硬件描述语言,它主要应用于数字电路和系统设计、数字电路和系统仿真等,即利用计算机和相关软件对用Verilog HDL等硬件语言建模的复杂数字逻辑电路设计进行仿真验证,再利用综合软件将设计的数字电路自动综合,以得到符合功能需求并且在相应的硬件电路结构上可以映射实现的数字逻辑网表,然后布局布线,根据网表和选定的实现器件工艺特性自动生成具体电路,同时软件生成选定器件的延时模型,经过仿真验证确定无误后写入器件中,最终实现电路设计。

Verilog HDL语言不仅定义了语法而且对每个语法结构都定义了清晰的模拟、仿真语义。

因此用这种语言编写的模型能够使用Verilog仿真

器进行验证。

语言从C编程语言中继承了多种操作符和结构。

Verilog HDL提供了扩展的建模能力其中许多扩展最初很难理解。

但是Verilog HDL语言的核心子集非常易于学习和使用这对大多数建模应用来说已经足够。

当然完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。

二、实验设计

计数器的逻辑功能是用于记录时钟脉冲的具体个数。

通常计数器最多能记忆时钟的最大数目m称为计数器的模2,即计数器的范围为0到m-1或m-1到0.其基本原理就是将几个触发器按照一定的顺序连接起来,然后根据触发器的组合状态,按照一定的技术规律随着时钟的变化来记忆时钟脉冲的个数。

计数器按照不同的分类方法可分为不同的类型,按照计数器中各个触发器时钟脉冲输入方式的不同分为同步计数器和异步计数器。

其中,同步计数器是指构成计数器的各个触发器的状态只在同一时钟信号的触发下才会发生变化的计数器。

在这里,我主要以同步4位二进制计数器为设计对象。

2.2设计步骤

在菜单栏中,选择File,新建一个工程,在根据工程向导设置相关内容。

所有选项设置好后就可以在文本编辑框中输入相应的程序了。

这里有个重要的点就是,保存时文件名必须和设计时所用的模块名保持一致。

采用文本编辑法,利用Verilog HDL语言来描述同步4位二进制计数器,代码如下:

module tongbu_cnt(co,q,clk,r,s,d,en);

output[3:0] q;

output co;

input clk,r,s,en;

input[3:0] d;

reg[3:0] q;

reg co;

always@(posedge clk)

begin

if(r)

begin q=d;end

else

if(s)

begin q=d;end

else

if(en)

begin q=q+1;

if(q==4'b1111)

begin co=1;end

else

begin co=0;end

end

else

begin q=q;end

end

endmodule

程序编写完成后再进行进行编译,根据编译后的结果提示,修改响应的错误,直到所有错误被修改完成。

编译成功后,如下图所示:

再新建波形仿真文件,弹出对话框如下图所示:

再选择需要添加的输入输出引脚的名字,如下图所示:

然后再对相应的信号进行初始设置,最后点击保存。

接下来就是进行仿真步骤,先进行功能仿真:

再进行时序仿真:

仿真结果:

同步4位二进制计数器的功能仿真结果如图1所示,时序仿真结果如图2所示。

其中,将q设置为buffer类型是为了方便计数。

图1 同步4位二进制计数器的功能仿真结果

图2 同步4位二进制计数器的时序仿真结果

三、学习感悟:

初次接触FPGA时,就感觉它功能很强大。

同时,我也了解到要想学好这门技术也并不容易,需要花大量的时间去专研,其相关的学习开发板也比较昂贵。

另外,对于编程语言来讲,我也是第一次听说Verilog HDL,它的一些编程语句和C语言很像。

在学习这门课程时,我也从中收获了许多。

从第一节课开始,老师推荐的几个学习网站,我觉得对我们技能的提升很有帮助。

除此之外,我觉得像电子发烧友网、电子工程网等,也是不错的学习平台,里面有许多有用的资料和最新的行业动态,这对我们电子信息类的学生来说很有帮助。

在上课过程中,我觉得还是有点更不上节奏,内容不仅多,大部分还是新知识。

基于此,我也到图书馆借阅了相关的书籍,主要是和编程语言相关的。

虽然,现在课程结束了,

但我仍然还是会继续学习下去,作为一门技能去掌握。

另一方面,老师在上课提到了半导体在今后发展趋势,为此我感到比较欣喜,因为我现在的学习内容和这个方向相关。

起初,我觉得作为传统制造业来说,它的发展优势并不明显,多年来一直不温不火,技术革新的地方也不多。

但是,现在随着人工智能的兴起,对于集成电路的要求也就越来越高,进而也就可能带动半导体行业的发展和进步。

除此之外,老师在课堂上提到的Python语言,我觉得在今后也大有用途,这也应该是我学习任务的一部分。

通过这次实例设计,我对Quartus ii软件和Verilog HDL语言有了更深一步的了解。

这次所用到的软件版本是在网上找的9.0版,我觉得软件的安装过程比较复杂。

结合网上的基础视频讲解和书本上的介绍,我对软件的基础使用有了一个大致的认识。

由于是第一次接触这方面的内容,这次的设计实验我也是选择了一个比较简单的同步4位计数器设计。

按照书上的例子,一步一步的去设置,编译,最后还是勉强实现了基本要求。

当然,在这个学习过程中,我也有遇到过许多问题。

从一开始的软件安装,到编译时的语句修改,再到最后的波形仿真,我都反复进行了许多次。

虽然,这次仅仅只是做了一个小的实验设计,涉及到的知识还不够多,难度也不算大,但是对于我来说收获却很多。

这其中也得到了老师和同学们的帮助,才使我更快的了解了相关的知识点。

借助这次实验设计,我在网上找到了学习视频和相关的学习资料,接下来就是准备买一快小的学习开发板,进行更加深入的学习研究。

同时,我也会关注相关行业的动态,了解更多新闻资讯。

四、参考文献:

[1]潘松.EDA技术实用教程.北京:科学出版社;

[2]周新.轻松学会FPGA设计与开发.北京:电子工业出版社;

[3]黄平.基于Quartus II的FPGA/CPLD数字系统设计与应用.北京:化学工

业出版社;。