PCI总线bus的测试规范

笔记本电脑MiniPCI总线测速功能说明

笔记本电脑MiniPCI总线测速功能说明在一块新的笔记本电脑上,使用其功能,可以方便的测试笔记本电脑的MiniPCI总线速度,即测即知;使用其功能,可以在购买笔记本电脑时,起到参考作用;也可使用其功能,将总线速度快的笔记本电脑卖出好价钱。

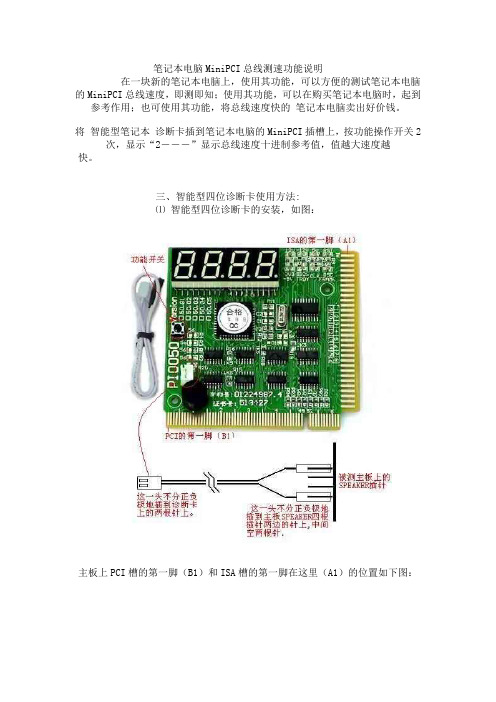

将智能型笔记本诊断卡插到笔记本电脑的MiniPCI插槽上,按功能操作开关2次,显示“2---”显示总线速度十进制参考值,值越大速度越快。

三、智能型四位诊断卡使用方法:⑪ 智能型四位诊断卡的安装,如图:主板上PCI槽的第一脚(B1)和ISA槽的第一脚在这里(A1)的位置如下图:⑫ 智能型诊断卡PI0050A使用方法流程图:⑬ 智能型诊断卡PI0050A数码管显示定义:智能型诊断卡 PI0050A 显示四位代码,前两位(即千位和百位)为被测计算机的检测故障代码;后两位(十位和个位)根据不同的操作,显示的代码意义不同。

当故障检测时,十位和个位显示的是千百位上故障代码的前一码;当使用代码翻查功能时,十位和个位显示的是千百位上故障代码的个数记数(PI0050卡总共能记忆48个代码,记数的序数号为00至47)。

故障检测时: 千百十个代码翻查时:千百十个位位位位位位位位故障代码前一码故障代码代码个数记数⑭ 智能型诊断卡PI0050A功能开关操作说明流程图:零速网络 » 个人电脑 » 电脑诊断卡使用方法‹‹ 上一主题 |下一主题 ››打印[其他]电脑诊断卡使用方法版主1# 大 中 小 发表于 2007-5-21 18:57 只看该作者 官方强烈推荐使用web 迅雷进行高速下载! 最新影视资源电脑诊断卡使用方法断卡使用方法 一、用户必读; 二、智能型笔记本电脑诊断卡使用方法;三、智能型四位诊断卡使用方法;四、智能型并口诊断卡L50使用方法.一、用户必读:⑪. 诊断卡也叫PC Analyzer 或POST ( Power On Self Test )卡,其工作原理是利用主板中 BIOS 内部自检程序的检测结果,通过代码一一 显示出来,结合本书的代码含义速查表就能很快地知道电脑故障所在。

PCI E硬件测试方法要点

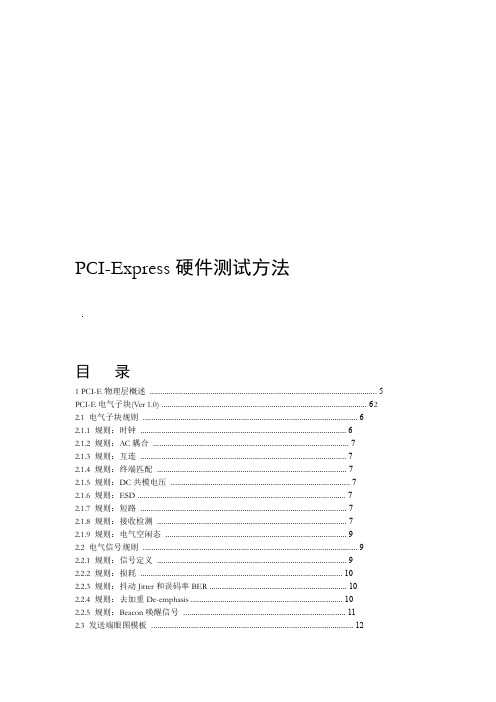

PCI-Express硬件测试方法目录1PCI-E物理层概述 (5)PCI-E电气子块(Ver 1.0) (62)2.1电气子块规则 (6)2.1.1规则:时钟 (6)2.1.2规则:AC耦合 (7)2.1.3规则:互连 (7)2.1.4规则:终端匹配 (7)2.1.5规则:DC共模电压 (7)2.1.6规则:ESD (7)2.1.7规则:短路 (7)2.1.8规则:接收检测 (7)2.1.9规则:电气空闲态 (9)2.2电气信号规则 (9)2.2.1规则:信号定义 (9)2.2.2规则:损耗 (10)2.2.3规则:抖动Jitter和误码率BER (10)2.2.4规则:去加重De-emphasis (10)2.2.5规则:Beacon唤醒信号 (11)2.3发送端眼图模板 (12)接收端眼图模板.2.4 (12)一致性测试负载................................................................................................. 2.5 13 PHY电气测试项目......................................................................................................... 3 13 3.1通用测试项目.. (14)发送端测试项目 3.2 (14)接收端测试项目. 3.3 (16)共页第2, 27页3.4母板测试项目 (17)插卡测试项目..................................................................................................... 13.5 7TEK测试方案简介.4 (18)4.1两个SMA通道连接 (18)一个带4.2SMA输入差分探头P7350SMA测试 (18)两个单端有源探头P72604.3测试 (19)一个差分探头P73xx测试................................................................................... 4.4 195PHY电气测试用例 (20)5.1符合性_PCI-E时钟精度测试 (20)符合性_SSC扩频时钟测试................................................................................ 25.2 0符合性_PCI-E一致性测试 5.3 (21)符合性_PCI-E5.4眼图测试 (23)符合性_PCI-E抖动测试 5.5 (25)符合性_PCI-E通道间偏斜测试......................................................................... 2 5.66符合性_PCI-E插卡功耗测试 5.7 (26)6参考文档......................................................................................... 错误!未定义书签。

PCI协议规范

PCI协议规范篇一:pci协议总结一. PCI 引脚必要的引脚在左边,任选的引脚在右边为了叙述方便,将PCI信号按数传方向及驱动特性划分为五种类型,各种类型的规定如下: in:输入信号。

out:输出驱动信号。

t/s:表示双向三态输入/输出驱动信号。

s/t/s:持续三态(Sustained Tri-State),表示持续的并且低电平有效的三态信号。

在某一时刻只能属于一个主设备并被其驱动。

这种信号从有效变为浮空(高阻状态)之前必须保证使其具有至少一个时钟周期的高电平状态。

另一主设备要想驱动它,至少要等到该信号的原有驱动者将其释放(变为三态)一个时钟周期之后才能开始。

同时,如果此信号处于持续的非驱动状态时,在有新的主设备驱动它之前应采取上拉措施,并且该措施必须由中央资源提供。

o/d:漏极开路(Open Drain)可作线或形势允许多个设备共同使用,二. 1.系统引线CLK in:时钟输入,为所有PCI上的接口传送提供时序。

其最高频率可达66MHz,最低频率一般为0(DC),这一频率也称为PCI的工作频率。

对于PCI的其他信号,除、、、之外,其余信号都在CLK的上升沿有效(或采样)RST in:复位,用来使PCI专用的特性寄存器和定时器相关的信号恢复规定的初始状况。

每当复位时, PCI的全部输出信号一般都应驱动到第三态。

2.地址和数据引线AD0~AD31 t/s:地址、数据多路复用的输入/输出信号。

在FRAME#有效时,是地址周期;在IRDY#和TRDY#同时有效时,是数据周期。

一个PCI总线的传输中包含了一个地址信号周期和一个(或多个)数据周期。

PCI总线支持突发方式的读写功能。

地址周期为一个时钟周期,在该周期中AD0~AD31线上含有一个32位的物理地址。

对于I/O操作,它是一个字节地址;若是存储器操作和配置操作,则是双字地址。

在数据周期,AD0~AD7为最低字节, AD24~AD31为最高字节。

当IRDY#有效时,表示写数据稳定有效,TRDY#有效表示读数据稳定有效C/BE0~3# t/s:总线命令和字节使能多路复用信号线。

PCIE 3.0简介及信号和协议测试方法

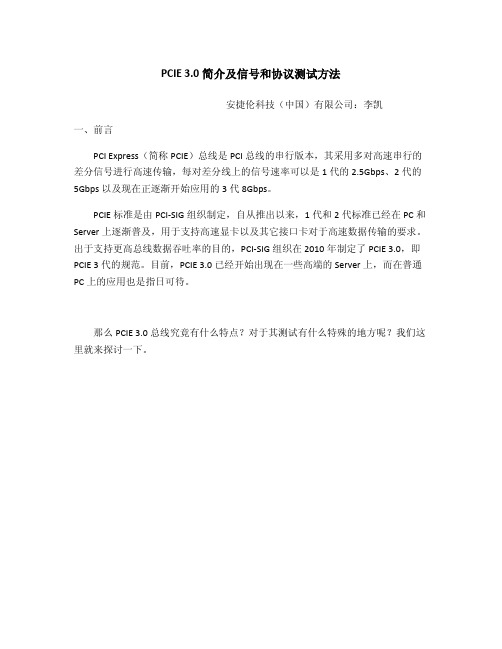

PCIE 3.0简介及信号和协议测试方法安捷伦科技(中国)有限公司:李凯一、前言PCI Express(简称PCIE)总线是PCI总线的串行版本,其采用多对高速串行的差分信号进行高速传输,每对差分线上的信号速率可以是1代的2.5Gbps、2代的5Gbps以及现在正逐渐开始应用的3代8Gbps。

PCIE标准是由PCI-SIG组织制定,自从推出以来,1代和2代标准已经在PC和Server上逐渐普及,用于支持高速显卡以及其它接口卡对于高速数据传输的要求。

出于支持更高总线数据吞吐率的目的,PCI-SIG组织在2010年制定了PCIE 3.0,即PCIE 3代的规范。

目前,PCIE 3.0已经开始出现在一些高端的Server上,而在普通PC上的应用也是指日可待。

那么PCIE 3.0总线究竟有什么特点?对于其测试有什么特殊的地方呢?我们这里就来探讨一下。

二、PCIE 3.0简介1、信号速率的变化首先我们看一下制定PCIE 3代规范的目的,其目的主要是要在现有的FR4板材和接插件的基础上提供比PCIE 2代高一倍的有效数据传输速率,同时保持和原有1代、2代设备的兼容。

别看这是个简单的目的,但实现起来可不容易。

我们知道,PCIE 2代在每对差分线上的数据传输速率是5Gbps,相对于1代提高了1倍;而3代要相对于2代把速率也提高一倍,理所当然的是把数据传输速率提高到10Gbps。

但是就是这个10Gbps把PCI-SIG给难住了,因为PC和Server上出于成本的考虑,普遍使用便宜的FR4的PCB板材以及廉价的接插件,无论采用什么技术都很难保证10Gbps的信号还能在原来的信号路径上可靠地传输很远的距离(典型距离是15~30cm)。

因此PCI-SIG最终决定把PCIE 3代的数据传输速率定在8Gbps。

但是8Gbps比着2代的5Gbps并没有高一倍,所以PCI-SIG决定在3代标准中把在1代和2代中使用的8b/10b编码去掉。

PCI实验说明书

PCI实验步骤说明书一实验之前的准备工作在做实验之前要把试验程序、VC6.0安装程序和pq8安装程序准备好,把它们全部复制到同一个位置。

对PCI卡实验程序文件夹里的文件名做一些有必要的介绍。

PCI卡实验程序文件夹下的Drivers文件夹是PCI驱动;Vfloppy文件夹是用来做虚拟DOS环境的;试验程序文件夹里的文件是实验所使用的程序,其中THS_2k文件是在Windows 2000以及XP系统下做DOS的PCI实验的程序,THS_9X文件是在Windows 98系统下做DOS的PCI实验的程序, THS_C文件是在C环境下做PCI实验的程序,THS_VC文件是在VC++环境下做PCI实验的程序。

最后的准备工作是将PCI的CPU板插到实验箱上,THS卡插入计算机的PCI 插槽,并将它们通过排线连接起来,然后启动计算机,发现新设备。

关闭新设备对话框,右击我的电脑,单击管理选项,再单击设备管理选项,找到其他设备里的其它PCI桥设备,右击该选项,更新其驱动程序。

该驱动程序就在刚刚介绍的Drivers文件夹。

成功装上驱动后显示达盛科技。

二 VC环境下的实验首先是安装VC6.0,在VC6.0文件夹里找到setup.exe,双击安装就行。

在安装过程中有两次重启计算机请不要惊讶。

在安装过程中会出现Install MSDN 对话框,把它前面的复选框中的勾去掉。

安装完毕后启动VC6.0,做PCI实验。

下面以8279显示器接口实验进行说明。

启动VC6.0后,单击File菜单下Open Workplace选项。

找到THS_VC文件夹下的E8279.dsw文件并打开,然后单击,软件编译会报错,提示找不到devintf.h文件。

接着单击Tools菜单下的Options选项,在弹出的对话框里找到Directions项,找到刚才提示的devintf.h文件的路径,然后单击OK,完了之后在单击进行编译,编译成功后,运行程序;出现如下对话框在上面的白框中输入两位16进制数,点击开始,数码管显示刚刚输入的数。

第二代PCI Express测试技巧

【設計論壇】第二代PCI Express測試技巧AgilentPCI Express (PCIe) 匯流排不再是所有資料都以固定速度傳遞的平行資料匯流排,而是序列、點對點、個別設定時脈的“波道”(lanes)組合,每個波道包含兩對差動資料線路,一對上傳資料,另一對下傳資料。

這些波道可以堆疊在一起,以提高I/O系統特定區域,如視訊卡插槽,的頻寬(詳見圖1)。

以第二代技術而言,每個波道在每個方向可達5 Gb/s的資料速率。

這項技術有一些顯而易見的優點,比如點對點電路可以大幅減少在主機板上繞遞的軌跡數量。

PCIe對桌上型PC市場所造成的最大衝擊就在於PCIe x16繪圖卡插槽,這項技術的實作取代了AGP 8x成為繪圖卡製造商的首選平台。

圖1:主機板結構PCIe實體層規格PCIe提升了資料傳輸效率與資料品質。

它使用8b/10b編碼,將時脈信號嵌入資料信號。

波道數最多可達16個。

第一代技術的資料速率是2.5 Gb/s [1],第二代的速度是第一代的兩倍,並且增加了更多信號完整性需求[2],以致對抖動測試產生新的要求。

再者它是為了擴頻時脈(SSC)而設計,能減少電磁干擾(EMI)的問題。

從規格可以瞭解測試邊限。

PCIe晶片組包含發射器(TX)和接收器(RX),它們各自擁有標準[1, 2] 所定義之不同實體參數。

圖2、3、4是第二代技術標準的複製[2]。

■特性描述TX資料流的速度為5 Gb/s,相當於200 ps的單位間隔(UI)。

資料速率的差異在±300 ppm之間,但不包括SSC,它會以30 kHz的速率增加一個-0.5%的三角形調變。

PCIe第二代規格定義了兩個電壓漂動位準:最大漂動與低漂動。

最大漂動信令使用解強調(de-emphasis),低漂動則否。

究竟發射器必須支援最大漂動、低漂動或同時支援此兩種模式,主要取決於它的使用方式。

通常低漂動適用於可接受較短通道的功率敏感(power sensitive)應用。

pci- e-指南规范标准

pci- e-指南规范标准英文回答:PCI-Express Standard.The PCI Express (PCIe) standard defines a high-speed serial computer expansion bus interface designed to replace the older PCI, PCI-X, and AGP bus standards. PCIe uses a point-to-point topology, with each device having its own dedicated link to the host controller. This allows for much higher data transfer rates than the shared bus architecture of the older standards.PCIe devices are typically connected to the host controller using a small, rectangular connector. The connector has a number of pins, which are used to transmit data, control signals, and power. The number of pins in the connector determines the number of lanes available for data transfer. Each lane can transfer data at a rate of up to 2.5 GT/s (gigatransfers per second).PCIe is a versatile standard that can be used for a variety of applications, including:Graphics cards.Network adapters.Storage devices.Sound cards.USB controllers.The PCIe standard is constantly evolving, with new versions being released regularly. The latest version of the standard, PCIe 6.0, was released in 2023. PCIe 6.0 supports data transfer rates of up to 64 GT/s, which is four times faster than PCIe 5.0.中文回答:PCIe 规范。

PCI插槽及测试点

PCI插槽及测试点

一、实物图

上图为主板上的PCI插槽实物图,左边三个是PCI插槽,中间最长的是PCI Express X16插槽,右边两个是PCI Express X1插槽

二、总线及测试点

PCI总线图及测试点(正面图)点击查看大图

PCI插槽背面图

说明:上图中深色显示的表格为PCI槽的关键测试点,包括4个供电、1个时钟、1个复位、8个信号测试点

+12V、-12V、+3.3V、+5V:是四个供电测试点

RESET#:是复位测试点,正常电压3.3V~0V,低电平复位,高电平正常工作,370主板大多由南桥提供,478主板大多由南桥通过门电路提供。

CLK:是时候测试点,频率为33MHZ,正常电压1.1V~1.6V,由时钟芯片提供。

8个信号测试点:

FRAME#:帧周期信号

TRDY#:从设备准备好

IRDY#:主设备准备好

DEVSEL#:设备选择信号

C/BE#(0)、C/BE#(1)、C/BE(2)、C/BE(3),是命令/字节允许信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCI总线测试指导规范目 录3410.1.5 CPCI 系统中系统板PCI 自动配置流程中的死锁现象.....................3410.1.4 MCP 卡在一台有SCSI 设备的工控机上,热启动后计算机有时会死机;.............................................................3410.1.3 C805MCP 卡在WINDOWS 下只分配到4Kbyte 的空间;...................3410.1.2 C805MCP 卡在联想微机(PII 400,VIA82C596芯片组)上配置失败............3310.1.1 配置程序因总线号搜索不全导致在Dell 计算机上不能配置APC 卡...........3310.1PCI 总线 配置案例..................................................3310案例分析..............................................................339常用仪器的使用操作......................................................338.3.2PCI-ISA (MPI )接口逻辑异常测试. (32)8.3.1PCI 总线信号异常测试 (32)8.3异常测试 (32)8.2.5PCI 卡兼容性测试 (32)8.2.4PCI 设备初始化测试 (31)8.2.3PCI 总线仲裁功能测试 (31)8.2.2PCI 读写功能测试 (31)8.2.1PCI 配置读及配置写功能测试 (31)8.2功能测试 (31)8.1.6PCI 中断信号测试 (30)8.1.5PCI 总线地址数据总线信号测试 (30)8.1.4PERR 、SERR 信号测试 (30)8.1.3PCI 控制信号测试 (30)8.1.2PCI 时钟信号相位测试 (29)8.1.1PCI 时钟信号测试 (29)8.1信号测试 (29)8测试项目、测试方法及注意事项.............................................287设计规范...............................................................266.3系统(母板)指标 (21)6.2PCI 元件指标 (20)6.1电气特性 (20)6性能指标...............................................................195.1.7PCI 总线配置空间 (18)5.1.6PCI 总线的访问延迟 (17)5.1.5 PCI 总线的仲裁机制 (13)5.1.4总线上的数据传输过程 (11)5.1.3 PCI 总线协议 (10)5.1.2总线命令 (8)5.1.1PCI 总线信号定义 (8)5工作原理................................................................74概述...................................................................73.2符号和缩略语.. (7)3.1定义 (7)3定义、术语、缩略语.......................................................72引用标准和规范..........................................................71适用范围................................................................4014.1附件一PCI 总线的驱动................................................4014附件.................................................................4013参考资料..............................................................4012修订记录..............................................................3911总结.................................................................3910.4PCI 总线异常案例...................................................3610.3信号质量案例......................................................3610.2插卡案例.........................................................PCI 总线测试指导书关键词:PCI 设计规范 测试用例摘要:本文首先介绍了PCI 总线的基本原理,然后给出了PCI 总线设计审查的注意点,并给出了基本测试用例,在文章最后总结了一些典型案例。

1适用范围适用于使用PCI 总线的各个产品,用于PCI 总线的了解熟悉,设计审查和测试。

2引用标准和规范PCI Local Bus Specification Revision 2.2 December 18,1998 无1名称编号序号3定义、术语、缩略语3.1定义无3.2符号和缩略语无4概述PCI (Peripheral Component Interconnect ,外围器件互连)总线,是一种高性能的32/64位地址数据多路复用标准工业总线,其支持5V/3.3V 两种信号电平和33MHz/66MHz 两种时钟频率,主要用于高集成外围控制器件、外围附加板及处理器/存储器系统。

特征与优点:1、高性能:PCI 总线的数据传输速率可从32位数据总线、33MHz 时钟(132MB/s )升级到64位总线、33MHz 时钟(264MB/s ),从32位数据总线、66MHz 时钟(264MB/s )升级到64位总线、66MHz 时钟(528MB/s ),即其可以支持四种工作状态,三种传输速率,同时可支持多组外围设备。

2、线性突发传输:PCI 可以支持突发读取及突发写入,当操作是从某个地址顺序进行时,就可以进行突发传输,地址自动增加,减少了无谓的地址操作,确保总线不断满载数据,更有效的利用总线的带宽传输数据。

3、极小的存取延误:当附属寄存器从总线上获得数据时,33MHz 写延误为60ns ,66MHz 写延误为30ns 。

4、采用总线主控和同步操作:总线主控是让任何一个具有处理能力的外围设备暂时接管总线,以加速执行高吞吐量、高优先级的任务。

PCI 总线的同步操作可以保证微处理器能够与这些总线主控同时操作,不必等待后者的完成。

5、不受处理器限制:PCI 总线独立于处理器的结构,形成一种独特的中间缓冲器设计方式,将中央处理器子系统与外围设备分开。

正是因为如此,PCI总线除了应用于X86系列CPU设计的系统外,还应用于其它多种CPU 设计的系统中。

6、适合与各种机型,兼容性强,预留有充足的发展空间,支持64位地址/数据多路复用,上下兼容33MHz和66MHz,而且成本低、效益高,是立足于未来的总线标准。

该总线在公司广泛用于各个产品,本文对PCI总线原理,设计审查,测试用例进行了总结和描述,以有利于刚刚接触PCI总线的同时尽快熟悉了解,同时对PCI总线的设计审查,测试项目和方法提供指导。

5工作原理PCI总线的数据传输采用突发分组机制,在地址期通过C/BE[3:0]上的命令类型确定是总线工作类型(如I/O读写,存储读写及其方式即多行读、单行读、普通读,配置读写,信息广播等),通过仲裁机构确定总线的所属权,然后在数据期根据总线协议完成数据传输。

具体如下:5.1.1PCI总线信号定义总线信号分为必备信号和可选信号,按功能分将这些信号表示如下图。

图1 PCI引脚图注:信号类型定义:IN:标准输入信号;OUT:标准输出信号;T/S:双向三态输入输出信号;S/T/S:低电平有效的三态信号,每次只能被1个设备驱动,并且在该设备释放之前必须驱动该信号至少1个时钟周期的高电平;O/D:开漏输出信号;系统信号CLK (IN):系统时钟信号。

对所有PCI设备来说都是输入信号,频率范围是0-33MHz,除RST#、INTA#、INTB#、INTC#、INTD#之外,所有信号都在CLK的上升沿有效(或采样)。

RST# (IN):PCI 复位信号。

用来使PCI专用的特性寄存器、定序器和相关的信号恢复到初始状态。

数据和地址信号AD[31::00] (T/S):数据/地址复用的输入/输出信号。

在地址期时,AD[31::00]上的数据为32位物理地址。

在数据期时,用于传送数据,AD[07::00]为最低字节,AD[31::24]为高字节。

C/BE[3::0]# (T/S):总线命令/字节使能复用信号。

地址期对应的是总线命令;数据期对应的是字节使能信号,表示在整个数据期中,AD[31::00]上那些字节为有效数据。

接口控制信号FRAME# (S/T/S):帧周期信号,由当前的主设备驱动,表示一次访问的开始和持续的时间,FRAME#无效后,是传输的最后一个数据期。

IRDY# (S/T/S):主设备准备好信号,该信号有效时表明发起本次传输的设备能够完成一个数据期。

与TRDY#配合使用,二者同时有效,数据才能完成传输。

TRDY# (S/T/S):目标设备准备好信号,有效时表示目标设备已作好进行当前数据传输的准备工作,可以进行相应的数据传输。

STOP# (S/T/S):停止数据传送信号。

有效时表示目标设备要求主设备终止当前的数据传送,该信号由目标设备发出。

LOCK# (S/T/S):锁定信号。

表示驱动它的设备所进行的操作可能需要多个传输才能完成。

LOCK#信号的控制是由PCI总线上发起数据传输的设备,根据它自己的约定并结合GNT#信号来完成的。

IDSEL (IN):初始化设备选择信号。

在配置空间读/写传输期间,用作片选信号。

计算机各插槽上的IDSEL信号是不同的;DEVSEL# (S/T/S):设备选择信号。

该信号有效时,表示驱动它的设备已经成为当前访问的目标设备。