第二章双极集成电路中的元件形成及寄生效应

双极寄生

1.1.6 肖特基晶体管中的寄生pnp管

最近发现的另一寄生pnp管是在肖特基箝位 晶体管中的寄生横向pnp管。如图1.1.6a显 示了典型肖特基箝位npn管的剖面。

22

肖特基晶体管中的寄生pnp管

肖特基二极管是这样形成的。通过延伸基区接触 窗口到外延上,并且在轻掺杂的外延区域接触处 引入铂硅化物。在一定的面积和电流密度下,肖 特基二极管比基区-外延二极管有更低的正向导通 压降,所以,当npn偏置到趋向于饱和时,肖特 基管开始导通,并且阻止了npn管基极电流的进 一步增加。同时,常规理论指出,电子注入到外 延,肖特基管将会导通,因此,在外延没有少子 (空穴)贮存。

18

合并的npn管

有种办法可以允许同一外延岛内的两个npn 管,为了这种逻辑应用而合并,那就是在 两个npn的基区之间放置一块p型区域。给 这个p型区域适当的偏置,使其收集任何一 个npn管基区发射的空穴,阻止寄生电流流 到另一个基区,偏置在这个额外的p型区域 的电位是衬底电位,这是IC中的最低电位, 这个结果显示在图1.1.4b的中。

17

合并的npn管

这是个普通的或非门电路。Q1和Q2管的集电极 短接在一起,很明显,通过用一个公共的外延区 做两个晶体管的集电极可以节约硅面积。当加信 号A或B是高电位(电位足够高,打开Q1或Q2并 且饱和),输出C是低电位。如果信号A为高,B 由高阻抗源驱动为低(被一个大电阻拉低),在 这种条件下,Q1将饱和,Q1的基区将注入空穴 到外延,Q2的基区作为集电区收集这些空穴,引 起B信号相对于其他逻辑门出高,正向电流将流 进Q3和其他任何连到B的npn管的基区。

30

横向pnp管中的寄生pnp管

图1.1.7d

31

横向pnp管中的寄生pnp管

第2章 集成电路中的晶体管及其寄生效应

2、次表面齐纳管

一般的齐纳管由于击穿发生在表面,因而输出噪声电压较大, 次表面齐纳管是设法把击穿由表面引入体内。可以用扩散法和 离子注入法来形成次表面齐纳管。 扩散法是在N+发射区内加一道深P+扩散,使击穿发生在N+ 与P+的接触圈上(称次表面)。

离子注入法掺杂可以精确控制掺杂的浓度和深度,利 用离子注入法来制造次表面齐纳管,可望得到较精确 的Vz值。离子注入次表面齐纳管的结构如图2.2l所示, 它是在P型基区扩散和N+发射区扩散后,增加一次硼 离子注入而成。

一、横向PNP管 1、横向PNP管的结构、特性及其寄生PNP管

2、多集电极横向PNP管

3、大电流增益的复合PNP管

二、衬底PNP管

三二极管 一、一般集成二极管 在集成电路中的二极管,多数是通过对集成晶体管 的不同接法而形成的,所以不增加新的工序,且可灵 活地采用不同的接法得到电参数不同的二极管,以满 足集成电路的不同要求。在集成电路中也可以利用单 独的一个硼扩散结形成的二极管。 各种集成二极管的特性比较如表2.2所示。二极管 接法的选择由电路对正向压降、动态电阻rd、电容、 存储时间tS和击穿电压的不同要求来决定,因为只要 工艺掌握得好,六种形式二极管的漏电流相差不多。

2.3 集成双极晶体管的无源寄生效应

因为衬底结始终反偏,在采取各种措施后,可使 α SF<0.0l,此时寄生PNP管的影响退化成一个势垒电 容Cjs,所以集成NPN管的等效电路如图2.4,称为 EM2模型。

一、集成NPN晶体管中 的寄生电阻 发射极串联电阻rES 集电极串联电阻rCS 基极串联电阻rB

2.6 肖特基势垒二极管(SBD)和肖特基箝位晶体管(SCT) 一、肖特基势垒二极管 由半导体物理的知识可知,铝和N型硅接触形成的肖 特基势垒具有类似于PN结的整流特性,其V-I关系为

第二章集成电路中的晶体管及其寄生效应详解

考虑无源寄生元件的集成NPN晶体管刨面图

无源寄生效应: 寄生电阻:

发射极串联电阻;集电极串联电阻,基区电阻

寄生电容:

与PN结有关的耗尽层势垒电容Cj; 与可动载流子在中性区的存储电荷有关的扩散电 容CD; 电极引线的延伸电极电容Cpad;

发射极串联电阻rES

由发射极金属和硅的接触电阻rE,C与发射区的体电阻rE,b, 组成.

10

4 3 有效范围:310 310

(a )

对于扩散的硅

P N 结二极管,在各种结深 xj 的情况下, 单位面积电容 C 相对总结电压V 除以本底浓度N BC 的关系

(b )

(2)查表 对于反偏pn结,作为一级近似,利用公式

ND N A C j (V ) ,VD VT ln 2 N i V 1 V D C jo

器件建模方法

一种是从元器件的电学工作特性出发,把元器件看成黑盒子,测量 其端口的电气特性,提取器件模型,而不涉及器件的工作原理,称 为行为级模型。这种模型的代表是IBIS模型和S参数。其优点是建模 和使用简单方便,节约资源,适用范围广泛,特别是在高频、非线 性、大功率的情况下行为级模型几乎是唯一的选择。缺点是精度较 差,一致性不能保证,受测试技术和精度的影响。

1、基区宽度调制等二级效应; 2、个别元件的分布性质

第二章 集成电路中的元器件及其寄生效应

Cj = Cc+ Ce

C p= C s

有寄生PNP管

P+

B E N P

+

C N

+

N–-epi P-Sub

P+

4. C开路,Ic=0击穿电压低于BC短接

VF=VBEF

BV=BVBE

Cj = Ce

Cp= Cc*Cs /(Cc+ Cs)

有寄生PNP管 P+ E B N P

+

齐纳二极管的特性要求

①动态电阻小 ②击穿电压稳定 ③噪声小

一般用BE结,缺点: 在表面处两侧浓度都 最高,且易受表面影 响 E B N P

+

VBO

I V

C N

+

P+

N–-epi P-Sub

P+

§2-6 肖特基二极管及肖特基晶体管

思考题

1.肖特基二极管的特点是什么? 2.肖特基晶体管的结构和工作原 理是什么? 3.设计肖特基二极管和肖特基晶 体管时应注意什么?

I2 = -F 1 -C B 1 SR

IES (eVBE/VT-1) B I VBC/VT-1) ICS (e B ISS (eVSC/VT-1)

VB

C

N P

C

IC IS

VSC

I

3

结电压 结电流 端电流

I A= 1 V I2 V

BE=0 SC=0

S

BE=0 BC=0

= -R = -F

I C= 2 V I3 V

从上面的分析可以看出,半导体的导电能力随外加电场强度的变化而变化, MOS管正是利用这种半导体的表面场效应原理而进行工作的。

双极集成电路中的元件形成及其寄生效应

I (X

n

2

In )

( X 3)

I (X

n

4

)

I P( X 1)

I I

rb

I

X3 X4

cbo

b

图 2.4 电流传输示意图

(1)发射结正向偏置--发射电子 由于发射结正向偏置,因而外加电场有利于多数载流子的扩散运动,高掺杂发射区 的多数载流子(电子)将向基区扩散(或注入);同时,基区中的多数载流子(空穴) 也向发射区扩散并与发射区中的部分电子复合。因此,发射极的正向电流 I e 是由两部分 电流组成的:一部分是注入基区的电子扩散电流 I n ( X 2 ) ,这股电流大部分能够传输到集 电极,成为集电极电流 I c 的主要部分;另一部分是注入发射区的空穴扩散电流 I p ( X 1 ) , 这股电流对集电极电流 I c 无贡献,且还是基极电流的 I B 一部分,所以有:

Ie = Ip ( X1) + In ( X 2 )

(2)载流子在基区的传输与复合

(2.1)

到达基区的一部分电子将与 P 型基区的多数载流子(空穴)复合。但是,由于低掺 杂基区的空穴浓度比较低。 而且基区很薄, 所以到达基区的电子与空穴复合的机会很少, 大多数电子在基区继续传输,到达靠近集电结的一侧。因此基极电流 I b 是由三部分电流 构成的:一部分是基区复合电流 I rb ,它代表进入基区的电子与空穴复合形成的电流;另 一部分是发射结正偏,由基区注入发射区的空穴扩散电流 I p ( X 1 ) ;还有一部分是集电结 反偏的反向饱和电流 I cbo ,所以有:

+

B

C

B

E

N E C

P

N+

B

C

B

《半导体集成电路》教学大纲

《半导体集成电路》教学大纲Semiconductor Integrated Circuits课程编码:12A30550 学分:4 课程类别:专业基础课计划学时:64 其中讲课:64 实验或实践:0 上机:0适用专业:集成电路设计与集成系统推荐教材:余宁梅,杨媛,潘银松,《半导体集成电路》,科学出版社,2011年参考书目:朱正涌,《半导体集成电路》(第2版),清华大学出版社,2009年廖裕评,陆瑞强,《Tanner Pro集成电路设计与布局实战指导》,科学出版社,2011年课程的教学目的与任务本课程的教学目的是通过本课程的学习,学生掌握掌握常用数字集成电路和模拟集成电路的类型、基本电路结构和设计方法,为设计复杂的集成电路结构奠定基础。

本课程的教学任务主要包括介绍常用数字集成电路和模拟集成电路的电路结构和工作原理以及设计方法,学生通过本课程的学习,可以对半导体集成电路的工艺基础和设计原理有全面和系统的掌握,为从事基础研究和应用研究打下基础。

课程的基本要求1、要求学生掌握双极晶体管的基本原理、制作工艺、寄生效应及典型电路;掌握CMOS数字集成电路的基本单元、实现工艺、基本逻辑单元构成及特性、系统构成等;2、掌握MOS型及双极型的模拟电路特性,掌握基本的模拟电路结构、工作原理和各自特点;掌握半导体存储器以及D/A、A/D转换器的结构和工作原理;3、能够采用静态电路设计方法、传输门逻辑方法和动态逻辑方法对数字集成电路进行设计;对带隙基准源电路、差分放大电路进行电路设计及功能仿真,提取并分析仿真参数,明确电路性能;能够根据所学知识设计高速低功耗的SRAM存储器以及基本类型的D/A及A/D转换器。

各章节授课内容、教学方法及学时分配建议(含课内实验)第1章绪论建议学时:2 [教学目的与要求] 了解半导体集成电路的基本概念、分类、发展动态、面临问题,明确学习目的。

[教学重点与难点] 深亚微米集成电路设计、性能与工艺面临问题与挑战[授课方法] 课堂教学[授课内容]第一节半导体集成电路的概念一、半导体集成电路的基本概念二、半导体集成电路的分类第二节半导体集成电路的发展过程第三节半导体集成电路的发展规律第四节半导体集成电路面临的问题一、深亚微米集成电路设计面临的问题与挑战二、深亚微米集成电路性能面临的问题与挑战三、深亚微米集成电路工艺面临的问题与挑战第2章双极型集成电路制造工艺及EM模型建议学时:4 [教学目的与要求] 1、掌握双极型晶体管(BJT管)的结构和工作原理;2、掌握BJT管的制造工艺;3、掌握BJT管理想的EM模型[教学重点与难点] 不同结构BJT管的EM模型。

集成电路中的晶体管及其寄生

电路的工作。 2. NPN工作于截止区或正向工作区——寄生PNP截止。

三、EM模型

如果令I3=0或ISS=0,就可得出三层二结结构NPN晶体管的EM 方程 :

集成双极晶体管的有源寄生效应

假定隔离结始终处于反偏,并取晶体管的参数如下;

在进行rC1的计算时,假定其图形是一个上下底为矩形且 相互平行的锥体,其上底为有效集电结面积S,即Sc.eff = SE(发射结面积),并作以下近似:

①上底、下底备为等位面; ②锥体内的ห้องสมุดไป่ตู้流只在垂直方 向流动; ③在上、下面上的电流分布 是均匀的。

这样结构的电阻可用公式求得:

公式的适用范围:

不能再认为电流再锥体内是垂

集成电路中的晶体管 及其寄生

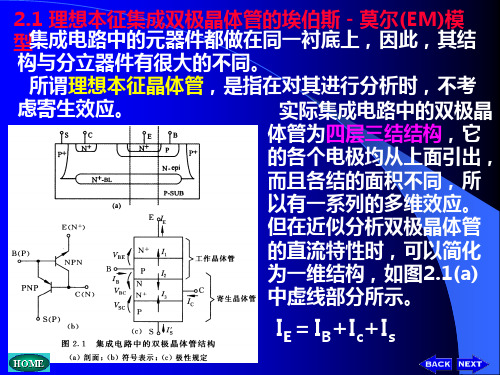

理想本征集成双极晶体管的埃伯斯-莫尔模型

一、要点

通过隔离把硅片分成一定数目的相互绝缘的隔 离区;

在各个隔离区制作晶体管,电阻等元件; 制作互连线,把各个元件按照一定功能连接起

来。 多维效应——集成电路中的双极晶体管为四层

三结结构,各电极均从上面引出,而且各结面 积不同。

对EM模型作简化:

① PN结正偏工作时, PN结反偏工作时,

V F 0 ,e V F /V t 1 e V F /V t

V R 0 ,e V R /V t 1 1

②在电流叠加时只计算exp ( V F / V t)项.即可以忽略反偏 电流,当全部结都反偏时,只考虑ISS项

③VSC总是小于零,所以

寄生PNP管的存在对NPN管的电流基本上没 有影响,只是增加了IB及IC中的反向漏 电.同时增加一项衬底漏电流IS’ 。

在模拟集成电路中,NPN管一般工作在正向 工作区,所以寄生PNP管的影响可以忽略。

集成电路——双极型晶体管

基极金属 和硅的接触电阻以及 基极接触孔下的基区电阻

B

E

发射区 扩散层下的

基区电阻

发射区扩散层 边缘到基极接触孔边缘的

外基区电阻

rB3 rB2 rB1

2021/4/22

集成双极晶体管的无源寄生效32 应

§2.5 MOSFET的单管结构及工作原理 • 单极器件:只有一种载流子参与导电

源极

n+

栅极

绝缘层(SiO2)

2021/4/22

理想本征集成双极晶体管的EM1模7 型

§2.3 集成双极晶体管的有源寄生效应

双极晶体管的四种工作状态

S

IS

E(n+)

VBC

p I3 n I2

IB p n I1

V3 B(p)

IC C pnp

V2

npn C(n)

V1

S(p)

反向工作区

(反偏)

截止区

(正偏)

饱和区 VBE

(正偏)

正向工作区

大部分被集电极反偏结收集:I

( 接近于1)

c

Ie

I c bo

Ie

I • 具有电流放大作用: c

Ib

2021/4/22

5

E

N

P

C N

B

当发射结正偏(VBE>0),集电结也正偏(VBC>0)时(但注意,VCE仍

大于0),为饱和工作区。

1. 发射结正偏,向基区注入电子,集电结也正偏,也向基区注入电 子(远小于发射区注入的电子浓度),基区电荷明显增加(存在

E C

rC3

L T

bL

rC 3

T

WL

ln( a b ) ab

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2.3

理想本征集成双极晶体管的EM模型

一结两层二极管(单结晶体管)

P-Si

N-Si

I V

I I s 0 (e 1)

V VT

IS0

Dn nP 0 DP Pn 0 热电压. I(mA) Aq( ) Ln LP T=300K,约为26mv

ISO

I I so (e VT 1)

则 I C I B I CEO

当 I C I CEO 时,I C I B

是另一个电流放大系数。同样,它也只与管

13

子的结构尺寸和掺杂浓度有关,与外加电压无关。 2013-9-11 >> 1 。 一般

正向工作区

• 发射结正偏,发射极发射电子,在基区中扩散前 进,大部分被集电极反偏结收集:c I e I cbo I e I ( 接近于1) • 具有电流放大作用: I c I b

IC >> ICBO

则有

I C I E

放大状态下BJT中载流子的传输过程

为电流放大系数。它只与

管子的结构尺寸和掺杂浓度有 关,与外加电压无关。一般 = 0.90.99 。 2013-9-11

12

又:把 IE=IB+ IC 代入 IC= IE+ ICBO 整理得:I C I B 1 I CBO 1 1 设 1 且令 ICEO= (1+ ) ICBO (穿透电流)

双极集成电路等效电路

• 1:衬底选择

确定衬底材料类型 确定衬底材料电阻率

确定衬底材料晶向

E P+

n+

n+-BL

P型硅(p-Si) ρ≈10Ω .cm (111)偏离2~50

B

C S

p

n+

P+

n-epi P-Si

2013-9-11

25

典型PN结隔离双极集成电路中元件的形成过程

• 2:第一次光刻----N+隐埋层扩散孔光刻

V2 VT

V3 VT

E

2013-9-11

理想本征集成双极晶体管的EM模型

45

三结四层结构(多结晶体管)

S

IS

p I3 n I2

IB

V3 IC V2 V1

I1 1 I2 R I 0 3

n+

P+

n-epi

P-Si

34

2013-9-11

典型PN结隔离双极集成电路中元件的形成过程

• 8:铝淀积

35

2013-9-11

典型PN结隔离双极集成电路中元件的形成过程

• 9:第六次光刻----反刻铝

36

2013-9-11

典型PN结隔离双极集成电路中元件的形成过程

A

A’

P+隔离扩散 P基区扩散 N+扩散 接触孔

• 4:第二次光刻----P+隔离扩散孔光刻

E

B

C

S

P+

n-epi

n+

p

n+

P+

Tepiepi T

n+-BL

31

2013-9-11

P-Si P-Si 典型PN结隔离双极集成电路中元件的形成过程

• 5:第三次光刻----P型基区扩散孔光刻

E P+ n+

n+-BL

B

C

S

p

n+

P+

n-epi

P-Si

32

• 理想本征双极晶体管的埃伯斯-莫尔 模型 • 双极集成电路中的有源寄生效应

6

2013-9-11

双极集成电路中元件结构

双极集成电路的基本工艺

7

2013-9-11

2.1双极晶体管的单管结构及工作原理

• 双极器件:两种载流子(电子和空穴)同时参与导电

发 射 极

发射区 N+

发 射 基区 P 结

集 电 结

14

2013-9-11

E N P N

C

B

当发射结正偏(VBE>0),集电结也正偏(VBC>0)时(但注意,VCE仍

大于0),为饱和工作区。 1. 发射结正偏,向基区注入电子,集电结也正偏,也向基区注入电 子(远小于发射区注入的电子浓度),基区电荷明显增加(存在 少子存储效应),从发射极到集电极仍存在电子扩散电流,但明 显下降。 2.不再存在象正向工作区一样的电流放大作用,即 I c I b 不再成立。 3. 对应饱和条件的VCE值,称为饱和电压VCES,其值约为0.3V,深 饱和时VCES达0.1~0.2V。

E E P+ n+

B B

C C

S

铝线

S

隐埋层

p

n+-BL

n+

P+

n-epi

P-Si

37

2013-9-11

双极集成电路元件断面图

E

B

C

S

P+

n+

p

n+

P+

n-epi

n+-BL

P-Si

为了减小结电容,击穿电压高,外延层下推小,电阻率应取大; 为了减小集电极串联电阻,饱和压降小,电阻率应取小. TTL电路:0.2Ω .cm 模拟电路:0.5~5Ω .cm

15 2013-9-11

当发射结反偏(VBE<0),集电结也反偏(VBC<0) 时,为截止区。

当VBC>0 , VBE<0时,为反向工作区。工作原理类似于正向工作区, 但是由于集电区的掺杂浓度低,因此其发射效率低, R 很小(约0.02)。

C

E N P N

B

16 2013-9-11

反向工作区

2.2双极集成晶体管的结构与制造工艺

半导体 集成电路

夏炜炜 扬州大学物理科学与技术学院 E-mail:wwxia@

1. 集成电路的基本概念 2. 半导体集成电路的分类 3. 半导体集成电路的几个重要概念

2

2013-9-11

内容概述

双极型集成电路 集 成 电 路

按器件类型分

BiCMOS集成电路 MOS集成电路 SSI(100以下个等效门) MSI(<103个等效门) LSI (<104个等效门) VLSI(>104个以上等效门)

n

C端 E端

p

n

B

p

C端

E

B

C

E

B

C

E

N

P

N

C

E

P

N

P

C

19

2013-9-11

B E

B

C

?

N C

E

N

P

C

B

E

C

BE

N+ n

2013-9-11

p

20

3

双极集成电路中元件的隔离

B B C

E

B E

E

B E

C

C

C

n n p

B E C E

n n

B

p

21

2013-9-11

C

B

E

C

B

E

n

n p n p

n

介质隔离 (SiO2)

E

I

E

I1

N

P

N

IC

I2

C

V1

V2

I1 A I2 I2 B I1

V 1 0

NPN管反向运用时 共基极短路电流增 益 IE V 1 0 R IC

V 20

IC IE

V 20

F

2013-9-11

NPN管正向运用时 共基极短路电流增 43 益 理想本征集成双极晶体管的EM模型

E P+ n+

B

C

S P+

p

n+-BL

n+

n-epi P-Si

26 2013-9-11

N+隐埋层

P-Si衬底

典型PN结隔离双极集成电路中元件的形成过程

具体步骤如下: 1.生长二氧化硅(湿法氧化):

SiO2

Si- 衬底

Si(固体)+ 2H2O SiO2(固体)+2H2

27

2013-9-11

2.隐埋层光刻:

2013-9-11

典型PN结隔离双极集成电路中元件的形成过程

• 6:第四次光刻----N+发射区扩散孔光刻

E P+ n+

n+-BL

B

C

S

p

n+

P+

n-epi

P-Si

33

2013-9-11

典型PN结隔离双极集成电路中元件的形成过程

• 7:第五次光刻----引线孔光刻

E P+ n+

n+-BL

B

C

S

p

涂胶

光源

腌膜对准

曝光

28 2013-9-11

显影

E

B

C

S

刻蚀(等离子体刻蚀)

去胶

n+ n-epi

n+-BL

3.N+掺杂: N+

P+

p

n+

P+

Tepiepi T

P-Si P-Si N+

As掺杂(离子注入)

2013-9-11

去除氧化膜

29

• 3:外延层