电子技术 集成计数器74LS160

74ls160工作原理

74ls160工作原理

74LS160是一种4位二进制同步计数器,它可以在数字电路中实现计数功能。

它的工作原理是基于时钟信号和输入控制信号的变化来实现计数。

该计数器有四个输入端口,分别是时钟输入端口CLK、异步清零端口MR、并行加载端口P和使能端口ENP。

其中,时钟输入端口CLK是最重要的输入端口,它接收时钟信号,控制计数器的计数。

当时钟信号发生变化时,计数器会根据时钟信号的变化进行计数。

异步清零端口MR可以将计数器的值清零,当MR端口接收到低电平信号时,计数器的值会被清零。

并行加载端口P可以将计数器的值设置为任意值,当P端口接收到高电平信号时,计数器的值会被设置为P端口的输入值。

使能端口ENP可以控制计数器的使能状态,当ENP端口接收到低电平信号时,计数器会被禁用,不再进行计数。

当ENP端口接收到高电平信号时,计数器会被启用,开始进行计数。

在74LS160计数器中,计数器的值可以从0000到1111进行计数,当计数器的值达到1111时,它会自动回到0000,重新开始计数。

这种计数器可以广泛应用于数字电路中,例如在计数器、分频器、时序控制器等电路中。

74LS160是一种可靠的计数器,它的工作原理基于时钟信号和输入控制信号的变化来实现计数。

它可以广泛应用于数字电路中,为电路的计数、分频、时序控制等提供了可靠的支持。

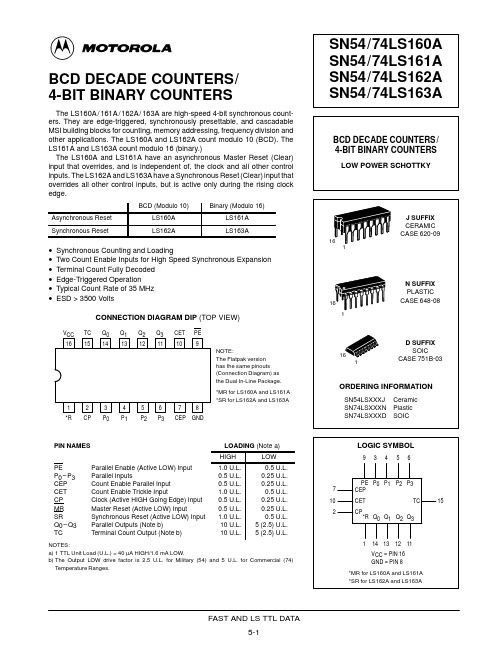

74LS160中文资料_数据手册_参数

16 1

N SUFFIX PLASTIC CASE 648-08

16 1

D SUFFIX SOIC

CASE 751B-03

ORDERING INFORMATION

SN54LSXXXJ Ceramic SN74LSXXXN Plastic SN74LSXXXD SOIC

LOGIC SYMBOL 934 56

NOTE: The LS160A and LS162A can be preset to any state, but will not count beyond 9. If preset to state 10, 11, 12, 13, 14, or 15, it will return to its normal sequence within two clock pulses.

SN54/74LS160A • SN54/74LS161A SN54/74LS162A • SN54/74LS163A

STATE DIAGRAM

LS160A • LS162A

0

1

2

3

4

15

5

14

6

13

7

12

11

10

9

8

LS161A • LS163A

0

1

2

3

4

15

5

14

6

13

7

12

11

10

9

8

LOGIC EQUATIONS

*MR for LS160A and LS161A *SR for LS162A and LS163A

PIN NAMES

PE P0 – P3 CEP CET CP

74ls160集成芯片的模值

74ls160集成芯片的模值74LS160集成芯片是一种二进制计数器芯片,具有模值功能。

本文将详细介绍74LS160集成芯片的模值以及其在电子领域中的应用。

我们需要明确什么是模值。

在二进制计数器中,模值指的是计数器能够计数的最大值。

例如,一个4位二进制计数器的模值为16,即能够计数从0000到1111共16个数值。

而74LS160芯片作为一个4位二进制计数器,它的模值也是16。

74LS160芯片是一种同步计数器,它可以通过外部的时钟信号进行计数。

当时钟信号上升沿到来时,计数器会加1,从而实现计数的功能。

在74LS160芯片中,有四个计数器输出线Q0、Q1、Q2和Q3,它们分别对应计数器的四个位数。

当计数器的值为0时,输出信号Q0、Q1、Q2和Q3都为低电平;当计数器的值为1时,Q0为高电平,Q1、Q2和Q3为低电平;以此类推,当计数器的值为15时,Q0、Q1、Q2和Q3都为高电平。

通过74LS160芯片的模值功能,我们可以实现多种应用。

首先,模值功能可以用于周期性计数。

例如,我们可以设置74LS160的模值为10,即计数范围为0到9。

这样,当计数器从0计数到9后,又会重新从0开始计数。

通过这种周期性计数,我们可以实现各种周期性操作,如LED灯的闪烁、定时器的计时等。

模值功能还可以用于频率分割。

通过将74LS160芯片的输出接入其他电路,可以将一个较高频率的时钟信号分割为多个较低频率的时钟信号。

例如,我们可以将74LS160的输出Q0接入一个LED灯,将Q1接入一个蜂鸣器,将Q2接入一个数码管,将Q3接入一个电机。

这样,每当计数器的值发生变化时,就会触发相应的输出信号,从而实现多个设备的控制。

模值功能还可以用于状态机的设计。

状态机是一种常见的电路设计方法,用于控制电子系统中的状态转换。

通过将74LS160芯片的输出与逻辑门电路相连,我们可以根据计数器的值来切换不同的状态。

例如,我们可以设计一个简单的交通信号灯控制系统,将74LS160芯片的输出接入逻辑门电路,根据不同的计数值来控制红灯、黄灯和绿灯的显示。

74Ls160

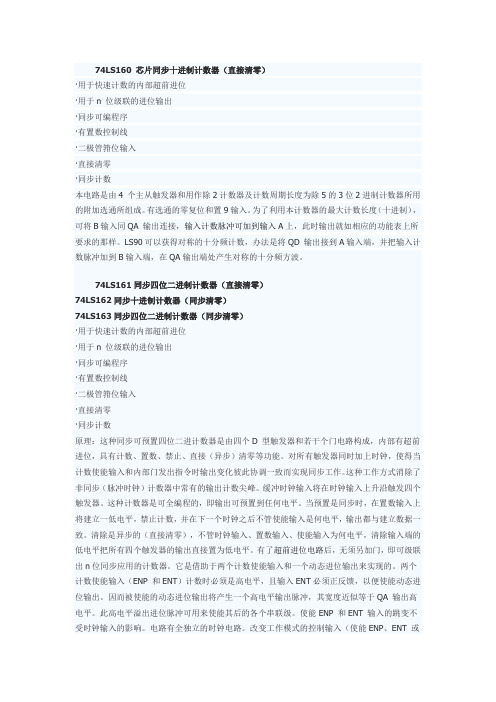

74LS160 芯片同步十进制计数器(直接清零)·用于快速计数的内部超前进位·用于n 位级联的进位输出·同步可编程序·有置数控制线·二极管箝位输入·直接清零·同步计数本电路是由4 个主从触发器和用作除2计数器及计数周期长度为除5的3位2进制计数器所用的附加选通所组成。

有选通的零复位和置9输入。

为了利用本计数器的最大计数长度(十进制),可将B输入同QA 输出连接,输入计数脉冲可加到输入A上,此时输出就如相应的功能表上所要求的那样。

LS90可以获得对称的十分频计数,办法是将QD 输出接到A输入端,并把输入计数脉冲加到B输入端,在QA输出端处产生对称的十分频方波。

74LS161同步四位二进制计数器(直接清零)74LS162同步十进制计数器(同步清零)74LS163同步四位二进制计数器(同步清零)·用于快速计数的内部超前进位·用于n 位级联的进位输出·同步可编程序·有置数控制线·二极管箝位输入·直接清零·同步计数原理:这种同步可预置四位二进计数器是由四个D 型触发器和若干个门电路构成,内部有超前进位,具有计数、置数、禁止、直接(异步)清零等功能。

对所有触发器同时加上时钟,使得当计数使能输入和内部门发出指令时输出变化彼此协调一致而实现同步工作。

这种工作方式消除了非同步(脉冲时钟)计数器中常有的输出计数尖峰。

缓冲时钟输入将在时钟输入上升沿触发四个触发器。

这种计数器是可全编程的,即输出可预置到任何电平。

当预置是同步时,在置数输入上将建立一低电平,禁止计数,并在下一个时钟之后不管使能输入是何电平,输出都与建立数据一致。

清除是异步的(直接清零),不管时钟输入、置数输入、使能输入为何电平,清除输入端的低电平把所有四个触发器的输出直接置为低电平。

有了超前进位电路后,无须另加门,即可级联出n位同步应用的计数器。

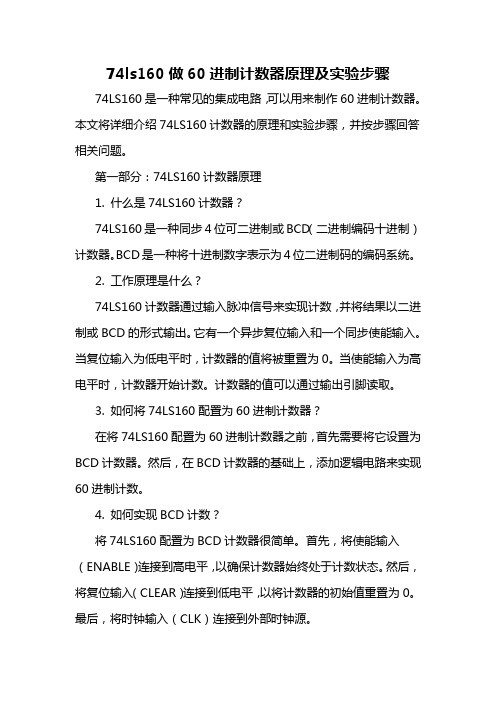

74ls160做60进制计数器原理及实验步骤

74ls160做60进制计数器原理及实验步骤74LS160是一种常见的集成电路,可以用来制作60进制计数器。

本文将详细介绍74LS160计数器的原理和实验步骤,并按步骤回答相关问题。

第一部分:74LS160计数器原理1. 什么是74LS160计数器?74LS160是一种同步4位可二进制或BCD(二进制编码十进制)计数器。

BCD是一种将十进制数字表示为4位二进制码的编码系统。

2. 工作原理是什么?74LS160计数器通过输入脉冲信号来实现计数,并将结果以二进制或BCD的形式输出。

它有一个异步复位输入和一个同步使能输入。

当复位输入为低电平时,计数器的值将被重置为0。

当使能输入为高电平时,计数器开始计数。

计数器的值可以通过输出引脚读取。

3. 如何将74LS160配置为60进制计数器?在将74LS160配置为60进制计数器之前,首先需要将它设置为BCD计数器。

然后,在BCD计数器的基础上,添加逻辑电路来实现60进制计数。

4. 如何实现BCD计数?将74LS160配置为BCD计数器很简单。

首先,将使能输入(ENABLE)连接到高电平,以确保计数器始终处于计数状态。

然后,将复位输入(CLEAR)连接到低电平,以将计数器的初始值重置为0。

最后,将时钟输入(CLK)连接到外部时钟源。

5. 如何实现60进制计数?要实现60进制计数,我们需要添加一个逻辑电路来增加计数器的位数。

由于74LS160只是一个4位计数器,我们需要使用多个74LS160并联来扩展位数。

例如,如果我们想要一个6位的60进制计数器,我们可以使用两个74LS160,并将第二个计数器的CLK输入连接到第一个计数器的某个输出引脚。

第二部分:74LS160计数器实验步骤1. 准备材料- 1个或多个74LS160计数器芯片(取决于所需的位数)- 逻辑门IC(用于扩展位数)- 面包板- 连接线- 4个LED(用于将计数器结果显示出来)- 电源(通常为5V)2. 连接电路首先,将74LS160芯片插入面包板中。

74ls160组成n进制计数器

实验 74LS160组成n进制计数器一、实验内容1.掌握集成计数器的功能测试及应用2.用异步清零端设计6进制计数器,显示选用数码管完成。

3.用同步置零设计7进制计数器,显示选用数码管完成。

二、演示电路74LS160十进制计数器连线图如图1所示。

图1 74LS160十进制计数器连线图CLR:异步清零端CLK:时钟输入端(上升沿有效)A-D:数据输入端ENP,ENT:计数控制端LOAD:同步并行置入控制端RCO:进位输出端74160的功能表如表1所示。

由表1可知,74160具有以下功能:①异步清零当CR(CLR’)=0时,不管其他输入端的状态如何(包括时钟信号CP),计数器输出将被直接置零,称为异步清零。

②同步并行预置数在CR=1的条件下,当LD(LOAD’)=0、且有时钟脉冲CP 的上升沿作用时,D0、D1、D2、D3输入端的数据将分别被Q0~Q3所接收。

由于这个置数操作要与CP上升沿同步,且D 0、D 1、D 2、D 3的数据同时置入计数器,所以称为同步并行置数。

③ 保持在CR =LD =1的条件下,当EN T =EN P =0,即两个计数使能端中有0时,不管有无CP 脉冲作用,计数器都将保持原有状态不变(停止计数)。

需要说明的是,当EN P =0, EN T =1时,进位输出C 也保持不变;而当ENT=0时,不管EN P 状态如何,进位输出RCO=0。

④ 计数当CR =LD =EN P =EN T =1时,74161处于计数状态,电路从0000状态开始,连续输入16个计数脉冲后,电路将从1111状态返回到0000状态,R CO 端从高电平跳变至低电平。

可以利用R CO 端输出的高电平或下降沿作为进位输出信号。

连上十进制加法计数器160,电路如图1所示,给2管脚加矩形波,看数码管显示结果,并记录显示结果。

三、用160和与非门组成6进制加法计数器-用异步清零端设计74160从0000状态开始计数,当输入第6个CP 脉冲(上升沿)时,输出Q 3 Q 2 Q 1 Q 0=0110,此时03Q Q CR==0,反馈给CR 端一个清零信号,立即使Q 3Q 2 Q 1 Q 0返回0000状态,接着,CR 端的清零信号也随之消失,74160重新从0000状态开始新的计数周期。

74LS160计数器

实验九74LS160计数器一、实验目的:1. 了解计数器的基本原理。

2. 掌握集成计数器芯片74LS160工作原理及应用。

二、实验原理:1、74LS160 为可预置的十进制同步计数器,其管脚图如图所示:RCO 进位输出端ENP 计数控制端QA-QD 输出端ENT 计数控制端CLK 时钟输入端CLR 异步清零端(低电平有效)LOAD 同步并行置入端(低电平有效)2、74LS160功能表:三、实验内容:1、利用同步十进制计数器74LS160接成同步七进制计数器。

设计思路:列出七进制计数器的真值表:计数顺序电路状态等效十进制进位输出CQ3Q2Q1Q00000000100011020010203001130401004050101506011061设计该电路要求在6时进位,即在输出为6时给输入端置0。

由真值表的逻辑函数式:Y’= (Q’0Q1Q2Q’3)’化简得:Y= (Q1Q2)’于是得设计电路:2、试用同步十进制计数器74LS160接成16进制计数器。

设计思路:74LS160是10进制计数器,要做成16进制计数器,先要做一个比16大的计时器。

这里用两片74LS160接成一个100进制计数器,再通过置0法实现16进制计数。

设计电路:四、实验分析:1、通过本实验,让我进一步了解74LS160计数器的基本原理。

基本掌握集成计数器芯片74LS160工作原理及应用。

2、设计电路时,注意思路清晰,结果简单易懂。

(注:专业文档是经验性极强的领域,无法思考和涵盖全面,素材和资料部分来自网络,供参考。

可复制、编制,期待你的好评与关注)。

74LS160_集成计数器

Q3 Q2 Q1 Q 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 0 0 0

要求: 每来一个CP,计数器加1

74LS160 集成计数器

▲ 逻辑符号 ▲ 引脚功能说明 D0~D3:并行数据输入端 Q0~Q3:数据输出端 EP、ET:计数控制端 C:进位输出端 CP:时钟输入端 RD :异步清除输入端 LD :同步并行置入控制端

▲ 表5.5

输 入

74LS160的功能表

输 出 D2 D3 Q 0 Q 1 Q 2 Q 3 × × 0 d0 d2 d3 × × × × × × 0 d1 计 保 保 0 0 d 2 d3 数 持 持

RD LD EP ET CP D0 D1 0 × × × × × × 1 0 × × ↑ d0 d1 1 1 1 1 ↑ × × 1 1 0 × × × × 1 1 × 0 × × ×

同步并行置入控制端ld74ls16074ls160集成计数器的应用举例集成计数器的应用举例反馈法反馈法构成模构成模66计数器的四种方法计数器的四种方法由此可见n进制计数器可以利用在n1时将变为0的方法构成这种方法称为反馈置0法

2 计数器的分析

1 计数器的功能和分类

1. 计数器的作用

记忆输入脉冲的个数;用于定时、分频、产 生节拍脉冲及进行数字运算等等。

第0位的1相当于十进制的1

第1位的1相当于十进制的2

4位二进制数: Q3 位数: 权重: 相当于十进制数: 3

3Hale Waihona Puke Q2 22Q1 Q0 1 0

0

2 2

8

2 2

2

1

4

1

8421码

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录一参考资料························( 2 )二工作原理························( 7 )三引脚图························( 8 )四电路图························( 9 )一参考资料(一)74LS4874LS48的管脚排列如图(c)所示。

其真值表如表3所示。

该器件输入信号为BCD码,输出端为a、b、c、d、e、f、g共7线,另有3条控制线LE、RBI、BI/RBO。

LE端为测试端。

在BI端接高电平的条件下,当LE=0时,无论输入端A、B、C、D为何值,a~g输出全为高电平,使7段显示器件显示“8”字型,此功能用于测试器件。

RBI端为灭零输入端。

在LE=1,BI =1条件下,当输入A、B、C、D=0000时,输出a~g全为低电平,可使共阴LED显示器熄灭。

但当输入A、B、C、D不全为零时,仍能正常译码输出,使显示器正常显示。

BI端为消隐输入端。

该输入端具有最高级别的控制权,当该端为低电平时,不管其他输入端为何值,输出端a~g均为低电平,这可使共阴显示器熄灭。

另外,该端还有第二功能——灭零信号输出端,记为RBO。

当该位输入的A、B、C、D=0000且RBI=0时,此时RBO输出低电平;若该位输入的A、B、C、D不等于零,则RBO输出高电平。

若将RBO与RBI配合使用,很容易实现多位数码显示时的灭零控制。

例如对整数部分,将最高位的RBI接地,这样当最高位为零时“灭零”,同时该位RBO输出低电平,使下一位的RBI为低电平,故也具有“灭零”功能;而对于小数部分,应将最低位的RBI接地,个位的RBI端悬空或接高电平,低位的RBO接至高位的RBI。

74LS48可直接驱动共阴极LED数码管而不需外接限流电阻。

表3 74LS48七段显示译码器的真值表(二)74LS00四2输入与非门(三)集成计数器74LS1601.74LS160为异步清零计数器,即RD 端输入低电平,不受CP 控制,输出端立即全部为“0”,功能表第一行。

74LS160具有同步预置功能,在RD 端无效时,LD 端输入低电平,在时钟共同作用下,CP 上跳后计数器状态等于预置输入DCBA ,即所谓“同步”预置功能(第二行)。

RD 和LD 都无效,ET 或EP 任意一个为低电平,计数器处于保持功能,即输出状态不变。

只有四个控制输入都为高电平,计数器(161)实现模10加法计数,Q 3 Q 2 Q 1 Q 0=1001时,RCO=1。

。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 74LS160RD CP D 1 GNDEP V CC D 0 15 16 D 2 D 3 LDET Q 3 Q 2 Q 1 Q 0 CO RD LD ET EP CP D 3D 2 D 1 D 0 Q 3 Q 2 Q 1 Q 00 × × × × × × × × 0 0 0 0 1 0 × × ↑ D C B A D C B A 1 1 0 × × × × × × 保 持1 1 × 0 × × × × × 保 持1 1 1 1 ↑ × × × × 计 数74LS160功能表(四)555555定时器是一种中规模集成电路,外形为双列直插8脚结构,体积很小,使用起来方便。

只要在外部配上几个适当的阻容元件,就可以构成史密特触发器、单稳态触发器及自激多谐振荡器等脉冲信号产生与变换电路。

它在波形的产生与变换、测量与控制、定时电路、家用电器、电子玩具、电子乐器等方面有广泛的应用。

引脚功能:V i1(TH ):高电平触发端,简称高触发端,又称阈值端,标志为TH 。

V i2(TR ):低电平触发端,简称低触发端,标志为TR 。

V CO :控制电压端。

V O :输出端。

Dis :放电端。

Rd :复位端。

555定时器内含一个由三个阻值相同的电阻R 组成的分压网络,产生 1/3V CC 和2/3V CC 两个基准电压;两个电压比较器C 1、C 2;一个由与非门G 1、G 2组成的基本RS 触发器(低电平触发);放电三极管T 和输出反相缓冲器G 3。

Rd 是复位端,低电平有效。

复位后, 基本RS 触发器的Q 端为1(高电平),经反相缓冲器后,输出为0(低电平)。

T H6T R 2Di s7V C C8R d4Q3G N D1Vc o555512345678GNDT RVoRdVc o T HDi s VCC 555..(a) 555的逻辑符号(b) 555的引脚排列图2.4 555定时器逻辑符号和引脚分析图2.4的电路:在555定时器的V CC端和地之间加上电压,并让V CO悬空,则比较器C1的同相输入端接参考电压2/3V CC,比较器C2反相输入端接参考电压1/3V CC,为了学习方便,我们规定:当TH端的电压>2/3V CC时,写为V TH=1,当TH端的电压<2/3V CC时,写为V TH=0。

当TR端的电压>1/3V CC时,写为V TR=1,当TR端的电压<1/3V CC时,写为V TR=0。

①低触发:当输入电压V i2<1/3V CC且V i1<2/3V CC时,V TR=0,V TH=0,比较器C2输出为低电平,C1输出为高电平,基本RS触发器的输入端S=0、R=1,使Q=1,Q=0,经输出反相缓冲器后,V O=1,T截止。

这时称555定时器“低触发”;②保持:若V i2>1/3V CC且V i1<2/3V CC,则V TR=1,V TH=0,S=R=1,基本RS触发器保持,V O和T状态不变,这时称555定时器“保持”。

③高触发:若V i1>2/3V CC,则V TH=1,比较器C1输出为低电平,无论C2输出何种电平,基本RS触发器因R=0,使Q=1,经输出反相缓冲器后,V O=0;T导通。

这时称555定时器“高触发”。

V CO为控制电压端,在V CO端加入电压,可改变两比较器C1、C2的参考电压。

正常工作时,要在V CO和地之间接0.01μF(电容量标记为103)电容。

放电管T l的输出端Dis为集电极开路输出。

555定时器的控制功能说明见表2.6。

根据555定时器的控制功能,可以制成各种不同的脉冲信号产生与处理电路电路,例如,史密特触发器、单稳态触发器、自激多谐振荡器等。

2.6 555定时器的控制功能说明输入输出TH(6)TR(2)Rd(4)Q(3)T ××0 0(复位)导通>2/3Vcc >1/3Vcc 1 0(复位)导通<2/3Vcc <1/3Vcc 1 1(置位)截止<2/3Vcc >1/3Vcc 1 不变不变>2/3Vcc <1/3Vcc 1 不确定图8.7所示为自激多谐振荡器电路和波形图。

(五)BCD七段数码管显示译码器电路发光二极管(LED)由特殊的半导体材料砷化镓、磷砷化镓等制成,可以单独使用,也可以组装成分段式或点阵式LED显示器件(半导体显示器)。

分段式显示器(LED数码管)由7条线段围成8型,每一段包含一个发光二极管。

外加正向电压时二极管导通,发出清晰的光,有红、黄、绿等色。

只要按规律控制各发光段的亮、灭,就可以显示各种字形或符号。

七段数码管是共阴极还是共阳极需要看它的端口,如果有CK则是共阴极,CK端接地;如果有CA则是共阳极,CA端接高电平..图4 - 17(a)是共阴式LED 数码管的原理图,图4-17(b)是其表示符号。

使用时,公共阴极接地,7个阳极a~g 由相应的BCD七段译码器来驱动(控制),如图4 - 17(c)所示。

C、B、A表示),输出是数码管各段的驱动信号(以F a~F g表示),也称4—7译码器。

若用它驱动共阴LED数码管,则输出应为高有效,即输出为高(1)时,相应显示段发光。

例如,当输入8421码DCBA=0100时,应显示,即要求同时点亮b、c、f、g段,熄灭a、d、e段,故译码器的输出应为F a~F g=0110011,这也是一组代码,常称为段码。

同理,根据组成0~9这10个字形的要求可列出8421BCD七段译码器的真值表。

常用的显示器件有液晶显示(LCD)、发光二极管显示(LED)、等。

LCD显示体积小、功耗低,但亮度不高。

LED数码管是把发光二极管制成条状,再按一定方式连接,组成8,使用时让某些笔段上的发光二极管发亮,即可组成0-9的一系列数字。

二工作原理秒表计时器工作原理:准备CC7555定时器,74LS00P与非门集成块,两片74LS160N 计数器,两片74LS48P解码器与两块7段数码管。

令这些芯片的Vcc端都接高电平,GND端全接低电平,使其全部能正常工作。

为了能让CC7555输出1Hz=1s 的CP,有公式f=1.43/[(R1+2R2)C] 求出R1,R2,C的值,按电路图连之。

由CC7555输出端1Hz的分别与两块74LS160N的2端(CP端)接入,使74LS160N能得到1Hz=1s的CP。

芯片74LS160N的2P(7端)、1P(7端)和1T(10端)共连在一开关(保持键)上,开关另一端接地。

当开关断开时,T,P端输入高电平,是两块芯片处于计数状态;当开关闭合时,T、P接地,输入低电平,芯片处于保持状态。