数电课件第10次课

合集下载

数字电子技术教学课件 (10)

0

0

1

1

0

0

1 0

0 1

R、S不允许

1

1 同时有效

0

×

1

×

4

2.特性方程(又称为状态方程) 由状态转换表得到Qn+1的状态转换卡诺图。

SR

Qn

00

0

00

1

01

0

பைடு நூலகம்

01

1

10

0

10

1

11

0

11

1

输入

Qn+1 0 1 0 0 1 1 × ×

输出

图4-15

进一步可写出Qn+1的表达式。

RS触发器的Qn+1卡诺图

仿真

图4-24 接成计数形式的D触发器 (a)电路 (b)工作波形

2021/1/11

16

4.4 集成触发器及其应用

表4-12 常用集成触发器

目前市场上出售的集成触发器产品通常为JK触

发202器1/1/1和1 D触发器两种类型。

17

4.4.1 集成JK触发器

常1.用74的LS有11724的LS外11引2、脚C图C和40逻27辑等符。号 74LS112为负边沿触发的双JK触发器。SD、RD

换所必备的条件

2021/1/11

6

4.3.2 D触发器

1.状态转换表

D

Qn

Qn+1

0

0

0

0

1

0

1

0

1

1

1

1

表4-6 D触发器的状态转换表

3. 状态转换图

2.特性方程 Qn+1=D

2021/1/11

10第十次课PPT资料31页

R in

u is

该方法也可用于纯电阻构成的一端口网络。

例2-10 求输入电阻 Rab和Rcd

c

d

Rab=(5+5) //15+6=12 a

..

6

5

Rcd=(15+5)//5=4

u

理想电压源:

Us

其特性仅由唯一参

理想电压源 实际电压源

数Us来描述,且与外电

路无关。

0

i

实际电压源:端电压随着输出电流改变而变化。

原因:实际电源内部存在电阻,即内部有损耗。

实际电压源可用一个理想电压源Us和一个电阻 Rs相串联的电路模型来替代。

i

a

u

Rs

+

Us

Rsi

+

u

Us

b

0

i

由模型可得端口处伏安关系:u = UsRs i 上式表明:实际电压源的端电压是低于定值电

1k

1k

I

0.5I

º

+

10V

U_

º

2k +500I- I º

+

10V

U_

º

U500I2000I10 =1500I10

1.5k

I

º

+

10V

U_

º

例3 如图所示,求Ux=?

解: 7A

此时,不可再继续做等

效变换,为求Ux,须通过 列方程的方法。由KCL:

UX UX UX 7

7A

284

111 (284)UX 7

7A Ux= 8V

4 + 2 Ux 4

0.5Ux

4 4 + 2 U x

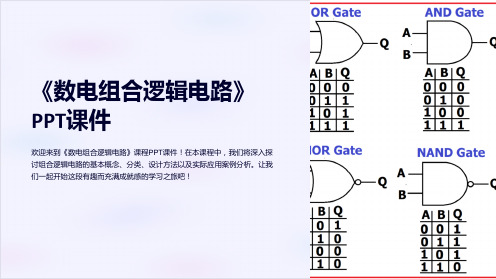

《数电组合逻辑电路》课件

2 设计和分析组合逻辑电路的方法

学习使用真值表、卡诺图和逻辑代数等工具进行组合逻辑电路的设计和分析。

3 应用案例的实际运用

通过实例,了解组合逻辑电路在数字系统和计算机中的应用。

课程大纲

第一章

组合逻辑电路概述

第三章

组合逻辑电路的简化与优化器

组合逻辑电路的基本概念

应用案例分析

在本节中,我们将通过精选的实际应用案例分析,展示组合逻辑电路在数字系统和计算机中的广泛应用。 这些案例将帮助您理解组合逻辑电路的实际应用价值和意义。

常见的组合逻辑电路元器件

组合逻辑电路的元器件有很多种,其中包括逻辑门、触发器、多路选择器等。在本节中,您将熟悉这些 常见的元器件以及它们在组合逻辑电路中的作用。

组合逻辑电路的设计方法

设计一个高效且可靠的组合逻辑电路需要一定的方法和技巧。在本节中,我们将探讨使用真值表、卡诺 图和逻辑代数等工具来进行组合逻辑电路的设计与优化。

组合逻辑电路由多个逻辑门电路组合而成,其输出仅取决于输入的当前状态。 在本节中,您将了解组合逻辑电路的基本概念,如逻辑运算、布尔代数、真 值表等。

组合逻辑电路的分类

根据功能和结构的不同,组合逻辑电路可以被分为多个子类。常见的分类包括编码器、解码器、多路选 择器、加法器等。通过本节,您将深入了解不同类型的组合逻辑电路及其应用。

《数电组合逻辑电路》 PPT课件

欢迎来到《数电组合逻辑电路》课程PPT课件!在本课程中,我们将深入探 讨组合逻辑电路的基本概念、分类、设计方法以及实际应用案例分析。让我 们一起开始这段有趣而充满成就感的学习之旅吧!

课程目标

通过本课程,您将学习到:

1 组合逻辑电路的基本原理和概念

掌握组合逻辑电路中的AND、OR、NOT等基本门电路的工作原理和特性。

学习使用真值表、卡诺图和逻辑代数等工具进行组合逻辑电路的设计和分析。

3 应用案例的实际运用

通过实例,了解组合逻辑电路在数字系统和计算机中的应用。

课程大纲

第一章

组合逻辑电路概述

第三章

组合逻辑电路的简化与优化器

组合逻辑电路的基本概念

应用案例分析

在本节中,我们将通过精选的实际应用案例分析,展示组合逻辑电路在数字系统和计算机中的广泛应用。 这些案例将帮助您理解组合逻辑电路的实际应用价值和意义。

常见的组合逻辑电路元器件

组合逻辑电路的元器件有很多种,其中包括逻辑门、触发器、多路选择器等。在本节中,您将熟悉这些 常见的元器件以及它们在组合逻辑电路中的作用。

组合逻辑电路的设计方法

设计一个高效且可靠的组合逻辑电路需要一定的方法和技巧。在本节中,我们将探讨使用真值表、卡诺 图和逻辑代数等工具来进行组合逻辑电路的设计与优化。

组合逻辑电路由多个逻辑门电路组合而成,其输出仅取决于输入的当前状态。 在本节中,您将了解组合逻辑电路的基本概念,如逻辑运算、布尔代数、真 值表等。

组合逻辑电路的分类

根据功能和结构的不同,组合逻辑电路可以被分为多个子类。常见的分类包括编码器、解码器、多路选 择器、加法器等。通过本节,您将深入了解不同类型的组合逻辑电路及其应用。

《数电组合逻辑电路》 PPT课件

欢迎来到《数电组合逻辑电路》课程PPT课件!在本课程中,我们将深入探 讨组合逻辑电路的基本概念、分类、设计方法以及实际应用案例分析。让我 们一起开始这段有趣而充满成就感的学习之旅吧!

课程目标

通过本课程,您将学习到:

1 组合逻辑电路的基本原理和概念

掌握组合逻辑电路中的AND、OR、NOT等基本门电路的工作原理和特性。

《数字电路实验》课件

体管数量越来越多。

02

低功耗设计

随着便携式电子设备的普及,低功耗设计成为数字电路发展的重要趋势

。

03

可编程逻辑器件的应用

可编程逻辑器件(PLD)如现场可编程门阵列(FPGA)和复杂可编程

逻辑器件(CPLD)的应用越来越广泛,使得数字电路设计更加灵活和

高效。

THANKS

感谢观看

03

认真观察实验现象,记录实验数据。

04

分析实验结果,总结实验经验,撰写实验 报告。

02

CATALOGUE

数字电路基础知识

数字电路概述

数字电路的定义

01

数字电路是处理离散信号的电路,其输入和输出信号通常为二

进制形式。

数字电路的特点

02

数字电路具有稳定性、可靠性、可重复性、易于大规模集成等

优点。

数字电路的应用

实验结果对比与分析

实验结果对比

将实验结果与理论值或预期结果进行 对比,找出差异和符合之处。

结果分析

对实验结果进行深入分析,探讨可能 的原因和影响因素,为实验总结提供 依据。

实验总结与建议

实验总结

根据实验过程和结果分析,总结实验的主要发现和结论,指出实验的局限性和不足之处 。

实验建议

针对实验中存在的问题和不足,提出改进和优化的建议,为后续的实验提供参考和借鉴 。

05

CATALOGUE

数字电路实验拓展

数字电路应用实例

01

02

03

数字钟

通过数字电路技术实现时 钟显示,包括时、分、秒 的计数和显示。

数字存储器

用于存储数据,如随机存 取存储器(RAM)、只读 存储器(ROM)等。

数字电子技术课件10

多路输入

Y=D1

一路输出

地址码输入

数据选择器的输入信号个数 N 与地址 常用 2 选 1、4 选 1、8 选 1和 16 选1 码个数 n 的关系为 N = 2n 等数据选择器。

组合逻辑电路

二、数据选择器的逻辑功能及其使用

1. 双 4 选 1 数据选择器 CC14539 两个数据选 择器的公共地址 输入端。

ST 1时 Y 0 ST 0时

Y = A1 A0 D0 + A1 A0 D1 + A1 A0 D2 + A1 A0 D3 = m0 D0 + m1 D1 + m2 D2 + m3 D3

EXIT

组合逻辑电路

CC14539 数据选择器 1 真值表

输 入 输出 1ST A1 A0 1D3 1D2 1D1 1D0 1Y 使能端低电平有效 1 ×× × × × × 0 0 0 0 × × × 0 0 1D0 0 0 0 × × × 1 1 1ST = 1 时,禁止数据 选择器工作,输出 1Y = 0。 0 0 1 × × 0 × 0 1D 0 0 1 × × 1 ×1 1 0 1 0 × 0 × ×0 1D2 1ST = 0 时,数据选择 0 1 0 × 1 × ×1 器工作。输出哪一路数据 0 1 1 0 × × ×0 1D 由地址码 A1 A0 决定。 0 1 1 1 × × ×1 3

数据选择器 2 的逻辑功能同理。 EXIT

组合逻辑电路

CC14539 数据选择器输出函数式

ST 0时

1Y = A1 A0 1D0 + A1 A0 1D1 + A1 A0 1D2 + A1 A0 1D3

= m0 1D0 + m1 1D1 + m2 1D2 + m3 1D3

数字电路基础数字教案第10章课件

二、CMOS IC

《规范》及指导原则适用于食品药品 监管部 门对第 三类医 疗器械 批发/零 售经营 企业经 营许可 (含变 更和延 续)的 现场核 查,第 二类医 疗器械 批发/零 售经营 企业经 营备案 后的现 场核查 ,以及 医疗器 械经营 企业的 各类监 督检查

施密特触发器的主要特点:

输入信号在上升和下降过程中,电路状态转换的输入 电平不同

当VI 0时, VO0。

当VI ,至VI' VTH时,进入传输大 特区 性, 的故 放

VI' VO1 VO使电路迅速Βιβλιοθήκη 变VO到 VOHV I VTH

R1

R2 R2

V

I

VI

VT

(1

R1 R2

)V TH

《规范》及指导原则适用于食品药品 监管部 门对第 三类医 疗器械 批发/零 售经营 企业经 营许可 (含变 更和延 续)的 现场核 查,第 二类医 疗器械 批发/零 售经营 企业经 营备案 后的现 场核查 ,以及 医疗器 械经营 企业的 各类监 督检查

10.2 施密特触发器(常用的一类脉冲整形电路)

特点 1、两个稳定状态 2、输入信号从低电平上升过程中电路状态转

换时对应的输入电平与输入信号从高电平下 降过程中电路状态转换时对应的输入电平不 同 3、在电路状态转换时,通过电路内部的正反 馈过程使输出电压波形的边沿变陡

《规范》及指导原则适用于食品药品 监管部 门对第 三类医 疗器械 批发/零 售经营 企业经 营许可 (含变 更和延 续)的 现场核 查,第 二类医 疗器械 批发/零 售经营 企业经 营备案 后的现 场核查 ,以及 医疗器 械经营 企业的 各类监 督检查

一、微分型 G1和G2为CMOS门

《规范》及指导原则适用于食品药品 监管部 门对第 三类医 疗器械 批发/零 售经营 企业经 营许可 (含变 更和延 续)的 现场核 查,第 二类医 疗器械 批发/零 售经营 企业经 营备案 后的现 场核查 ,以及 医疗器 械经营 企业的 各类监 督检查

施密特触发器的主要特点:

输入信号在上升和下降过程中,电路状态转换的输入 电平不同

当VI 0时, VO0。

当VI ,至VI' VTH时,进入传输大 特区 性, 的故 放

VI' VO1 VO使电路迅速Βιβλιοθήκη 变VO到 VOHV I VTH

R1

R2 R2

V

I

VI

VT

(1

R1 R2

)V TH

《规范》及指导原则适用于食品药品 监管部 门对第 三类医 疗器械 批发/零 售经营 企业经 营许可 (含变 更和延 续)的 现场核 查,第 二类医 疗器械 批发/零 售经营 企业经 营备案 后的现 场核查 ,以及 医疗器 械经营 企业的 各类监 督检查

10.2 施密特触发器(常用的一类脉冲整形电路)

特点 1、两个稳定状态 2、输入信号从低电平上升过程中电路状态转

换时对应的输入电平与输入信号从高电平下 降过程中电路状态转换时对应的输入电平不 同 3、在电路状态转换时,通过电路内部的正反 馈过程使输出电压波形的边沿变陡

《规范》及指导原则适用于食品药品 监管部 门对第 三类医 疗器械 批发/零 售经营 企业经 营许可 (含变 更和延 续)的 现场核 查,第 二类医 疗器械 批发/零 售经营 企业经 营备案 后的现 场核查 ,以及 医疗器 械经营 企业的 各类监 督检查

一、微分型 G1和G2为CMOS门

精品课件-数字电子技术-第10章

uo(1)=D1UR/8 uo(2)=D2UR/4 uo(3)=D3UR/2

第10 D/A转换电路

图10-5 D1、D2、D3单独作用时T型电阻网络的戴维南等效电 路

第10 D/A转换电路

利用叠加原理可得到转换器的总输出为

uo= uo(0)+ uo(1)+ uo(2)+ uo(3)

= D0V R D1VR D2V R D3VR

第10 D/A转换电路 图10-1 D/A转换器的一般结构

பைடு நூலகம் 第10 D/A转换电路

现在我们来讨论如何把一个二进制的数值 D 转换成一个 模拟电压 uo,这是 D/A 转换的典型问题。一种简单的解决方 法是,用二进制数的每一位数码按权大小产生一个电压,此电 压的值正比于对应位码的权值。例如,位 Dn-1=1 时产生电压 2n-1K 伏、Dn-1=0 时产生电压 0 伏,即位 Dn-1 产生的电压为 Dn-1×2n-1K 伏;位 Dn-2 产生的电压为 Dn-1×2n-2K 伏;……;位 D0 产生的电压为 D0×20K 伏;以上 K 为定常系数。然后,把这 些电压简单地加起来,结果就是,

16

8

4

2

= VR

24

×(D0×20+D1×21+D2×22+D3×23)

可见,输出模拟电压正比于数字量的输入。推广到n位,

D/A转换器的输出为

uo

UR 2n

(D0

20

D1 21

Dn1 2n1)

(10-2)

第10 D/A转换电路

T型电阻网络由于只用了R和2R两种阻值的电阻,其精度 易于提高,也便于制造集成电路。但也存在以下缺点:在工作 过程中,T型网络相当于一根传输线,从电阻开始到运放输入 端建立起稳定的电流电压为止,需要一定的传输时间,当输入 数字信号位数较多时,将会影响D/A转换器的工作速度。另外, 电阻网络作为转换器参考电压UR的负载电阻将会随二进制数D 的不同有所波动,参考电压的稳定性可能因此受到影响。所以 实际中常用下面的倒T型D/A转换器。

第10 D/A转换电路

图10-5 D1、D2、D3单独作用时T型电阻网络的戴维南等效电 路

第10 D/A转换电路

利用叠加原理可得到转换器的总输出为

uo= uo(0)+ uo(1)+ uo(2)+ uo(3)

= D0V R D1VR D2V R D3VR

第10 D/A转换电路 图10-1 D/A转换器的一般结构

பைடு நூலகம் 第10 D/A转换电路

现在我们来讨论如何把一个二进制的数值 D 转换成一个 模拟电压 uo,这是 D/A 转换的典型问题。一种简单的解决方 法是,用二进制数的每一位数码按权大小产生一个电压,此电 压的值正比于对应位码的权值。例如,位 Dn-1=1 时产生电压 2n-1K 伏、Dn-1=0 时产生电压 0 伏,即位 Dn-1 产生的电压为 Dn-1×2n-1K 伏;位 Dn-2 产生的电压为 Dn-1×2n-2K 伏;……;位 D0 产生的电压为 D0×20K 伏;以上 K 为定常系数。然后,把这 些电压简单地加起来,结果就是,

16

8

4

2

= VR

24

×(D0×20+D1×21+D2×22+D3×23)

可见,输出模拟电压正比于数字量的输入。推广到n位,

D/A转换器的输出为

uo

UR 2n

(D0

20

D1 21

Dn1 2n1)

(10-2)

第10 D/A转换电路

T型电阻网络由于只用了R和2R两种阻值的电阻,其精度 易于提高,也便于制造集成电路。但也存在以下缺点:在工作 过程中,T型网络相当于一根传输线,从电阻开始到运放输入 端建立起稳定的电流电压为止,需要一定的传输时间,当输入 数字信号位数较多时,将会影响D/A转换器的工作速度。另外, 电阻网络作为转换器参考电压UR的负载电阻将会随二进制数D 的不同有所波动,参考电压的稳定性可能因此受到影响。所以 实际中常用下面的倒T型D/A转换器。

电工电子技术基础课件第10章

R2

T3 T2

R3

+5V

R5

R4

拉电流

T4

uY = 3.6 V

Y

T5 RL

A

B1 R1 C1

B

设:uA= 0.3V uB= uC=3.6V,则 VB1= (0.3+0.7) V= 1V

C

T2 、T5 截止,

T3、 T4 导通,

uY = 5 – ube3 – ube4 – uR2 = (5 – 0.7 – 0.7)V = 3.6 V

扰

保证输出高电平所允许的最大输入低电平的电压值

能

力 (4)开门电压 U ON

通常: U ON≤1.8V

保证输出低电平所允许的最小输入高电平的电压值

(5)扇形系数 N

输出端能带动同类门的最大数目 典型:N≥8

章目录 节首页 上一页 下一页

第10章 门电路和组合逻辑电路——TTL门电路

(6)平均传输延时时间 tpd

第10章 门电路和组合逻辑电路

教学目标

1 掌握与、或、非基本逻辑运算及与非、异或逻辑 运算功能。

2 理解逻辑代数的基本运算法则和基本定律。 3 掌握复合逻辑运算关系表达式、逻辑符号和逻辑 规律,掌握逻辑代数运算法则及逻辑化简方法。 4 了解数字集成门电路特点及其使用方法。 5 掌握组合逻辑电路分析和设计方法。 6 了解编码器、译码器、加法器等逻辑部件及功能。

(3) 逻辑符号

(2) 真值表

AB F

001 010 100 110

口诀 有1出0,全0出1

(4) 逻辑表达式

F AB

章目录 节首页 上一页 下一页

第10章 门电路和组合逻辑电路——逻辑门电路

3.与或非门 (1) 与或非门组成

NO10 (2)

图10-9 74LS85引线图

四位比较器可直接用来比较两个四位或小于四位的二进制整数的大小。

当两个待比较的数的位数超过四位时,往往要将多个比较器级联使用。

这种编码器有一个特点:任何时刻只允许输入一个有效信号,不允许同时出现两个或两

进制数0~9 0~9相应的BCD码,因此也称104线编码器。

它和二进制编码器特点一样,任何时刻只允许

10-13 8线-3线优先编码器74LS148功能简图

译码与编码是相反的过程,是将二进制代码表示的特定含义翻译出来的过程。

能实现译码功能的组合逻辑电路称为译码器。

二进制译码器是将输入的二进制代码的各种状态按特定含义翻译成对应输出信号的电。

【精品】数电详解PPT课件

VOL≤0.33V.

解:驱动管输出为高电平时

R

L(

max

)=

VDD- VOHmin nIOH+ mI IH

=

5 4.4

2 5 10 6 9 110 6

=31 .6K

驱动管输出为低电平时

R

= L(m in)

VD

-

D

VOL

I

OL(

m

a

-

x)

m

I

IL(m

ax)

=

5 0.33

5.2 10 3 9 10 6

4.上拉电阻RL的计算 P95

设有n 个OD门 的输出端并联使用, 负载为CMOS与非门 的输入端。

① 输出为高电平

当所有的OD门输 出管截止输出为高电 平时,其电流的方向 如图所示。

IOH、IIL是保护二极管和寄生二极管的反向漏电流形成

若OD门输出管截 止时的漏电流为IOH, 负载门输入为高电平 时的输入电流为IIH, n为并联OD门(驱动 门)的个数, m为负载门输入高电平 电流的个数,所以:

3.3.5 其他类型的CMOS逻辑门

输出端逻辑式为

YY1Y2 (AB )(C)D (ABCD)

故OD门的线与实现了与或 非的逻辑功能。 4.上拉电阻RL的计算

在使用OD门做线与时,一定外接上拉电阻RL。但 RL的大小会影响驱动门输出电平的大小。 RL上的压降不 能太大,否则高电平会低于标准值;RL上的压降不能太 小,否则低电平会高于标准值。故R L的 取值要合适。

设RL>> RON, VIH= VDD,

VIL=0。C的高低电平为VDD

和0。

(1)C=0, C=1

1 VDD

无论vI在0~ VDD之间 0 如何变化, T1和T2同时截止, 输入和输出断开,传输门截

解:驱动管输出为高电平时

R

L(

max

)=

VDD- VOHmin nIOH+ mI IH

=

5 4.4

2 5 10 6 9 110 6

=31 .6K

驱动管输出为低电平时

R

= L(m in)

VD

-

D

VOL

I

OL(

m

a

-

x)

m

I

IL(m

ax)

=

5 0.33

5.2 10 3 9 10 6

4.上拉电阻RL的计算 P95

设有n 个OD门 的输出端并联使用, 负载为CMOS与非门 的输入端。

① 输出为高电平

当所有的OD门输 出管截止输出为高电 平时,其电流的方向 如图所示。

IOH、IIL是保护二极管和寄生二极管的反向漏电流形成

若OD门输出管截 止时的漏电流为IOH, 负载门输入为高电平 时的输入电流为IIH, n为并联OD门(驱动 门)的个数, m为负载门输入高电平 电流的个数,所以:

3.3.5 其他类型的CMOS逻辑门

输出端逻辑式为

YY1Y2 (AB )(C)D (ABCD)

故OD门的线与实现了与或 非的逻辑功能。 4.上拉电阻RL的计算

在使用OD门做线与时,一定外接上拉电阻RL。但 RL的大小会影响驱动门输出电平的大小。 RL上的压降不 能太大,否则高电平会低于标准值;RL上的压降不能太 小,否则低电平会高于标准值。故R L的 取值要合适。

设RL>> RON, VIH= VDD,

VIL=0。C的高低电平为VDD

和0。

(1)C=0, C=1

1 VDD

无论vI在0~ VDD之间 0 如何变化, T1和T2同时截止, 输入和输出断开,传输门截

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Pulse Widths

The minimum pulse widths for reliably operation are usually specified by the manufacturer for the clock, preset, and clear inputs.

CHAPTER 7

CHAPTER 7

Sec.7.4 Flip-Flop Applications

Frequency Division

Dividing (reducing) the frequency of a periodic waveform

CHAPTER 7

Sec.7.4 Flip-Flop Applications

CHAPTER 7

Sec.7.3 Flip-Flop Operating Characteristics

Maximum Clock Frequency

The maximum clock frequency is the highest rate at which a flipflop can be reliably triggered.

CHAPTER 7

Sec.7.3 Flip-Flop Operating Characteristics

Propagation Delay Times

CHAPTER 7

Sec.7.3 Flip-Flop Operating Characteristics

Set-up Time

The set-up time is the minimum interval required for the logic levels to be maintained constantly on the inputs prior to the triggering edge of the clock pulse in order for the levels to be reliably clocked into the flipflop.

Main Contents

• Synchronous Counter Operation • Asynchronous Counter Operation • Cascaded Counters • Counter Decoding

input X1 signal Xi

…

Combinational circuit

Parallel Data Storage

A common requirement in digital systems is to store several bits of data from parallel lines simultaneously in a group of flipflops.

Frequency Division

CHAPTER 7

Sec.7.4 Flip-Flop Applications

Frequency Division

CHAPTER 7

Sec.7.4 Flip-Flop Applications

Counting

Figure 7–41 Flip-flops used to generate a binary count sequence. Two repetitions (00, 01, 10, 11) are shown.

The power dissipation is very important in most applications in which the capacity of the dc supply is concern.

CHAPTER 7

Sec.7.4 Flip-Flop Applications

Sec.7.3 Flip-Flop Operating Characteristics

Power Dissipation

The power dissipation of any digital circuit is the total power consumption of the device.

CHAPTER 7

Sec.7.3 Flip-Flop Operating Characteristics

Hold Time

The hold time is the minimum interval required for the logic levels to remain on the inputs after the triggering edge of the clock pulse in order for the levels to be reliably clocked into the flip-flop.

…

Z1 output Zj signal

Flip-flop Output signal

Q1

D1

Fli…

…

circuit

Input signal

Qm

Dm

CP

Sec.8.1 Asynchronous Counter Operation

The term asynchronous refers to events that do not have a fixed time relationship with each other and, generally, do not occur at the same time.

CHAPTER 7

Sec.7.4 Flip-Flop Applications

Counting

Example 7-11 Determine the output waveforms.

CHAPTER 7

Sec.7.4 Flip-Flop Applications

Counting

CHAPTER 7

Chapter 8 Counters

Review

• Latch • Flip-Flop

Sec.7.3 Flip-Flop Operating Characteristics

Propagation Delay Times

A propagation delay time is the interval of time required after an input signal has been applied for the resulting output change to occur.

The minimum pulse widths for reliably operation are usually specified by the manufacturer for the clock, preset, and clear inputs.

CHAPTER 7

CHAPTER 7

Sec.7.4 Flip-Flop Applications

Frequency Division

Dividing (reducing) the frequency of a periodic waveform

CHAPTER 7

Sec.7.4 Flip-Flop Applications

CHAPTER 7

Sec.7.3 Flip-Flop Operating Characteristics

Maximum Clock Frequency

The maximum clock frequency is the highest rate at which a flipflop can be reliably triggered.

CHAPTER 7

Sec.7.3 Flip-Flop Operating Characteristics

Propagation Delay Times

CHAPTER 7

Sec.7.3 Flip-Flop Operating Characteristics

Set-up Time

The set-up time is the minimum interval required for the logic levels to be maintained constantly on the inputs prior to the triggering edge of the clock pulse in order for the levels to be reliably clocked into the flipflop.

Main Contents

• Synchronous Counter Operation • Asynchronous Counter Operation • Cascaded Counters • Counter Decoding

input X1 signal Xi

…

Combinational circuit

Parallel Data Storage

A common requirement in digital systems is to store several bits of data from parallel lines simultaneously in a group of flipflops.

Frequency Division

CHAPTER 7

Sec.7.4 Flip-Flop Applications

Frequency Division

CHAPTER 7

Sec.7.4 Flip-Flop Applications

Counting

Figure 7–41 Flip-flops used to generate a binary count sequence. Two repetitions (00, 01, 10, 11) are shown.

The power dissipation is very important in most applications in which the capacity of the dc supply is concern.

CHAPTER 7

Sec.7.4 Flip-Flop Applications

Sec.7.3 Flip-Flop Operating Characteristics

Power Dissipation

The power dissipation of any digital circuit is the total power consumption of the device.

CHAPTER 7

Sec.7.3 Flip-Flop Operating Characteristics

Hold Time

The hold time is the minimum interval required for the logic levels to remain on the inputs after the triggering edge of the clock pulse in order for the levels to be reliably clocked into the flip-flop.

…

Z1 output Zj signal

Flip-flop Output signal

Q1

D1

Fli…

…

circuit

Input signal

Qm

Dm

CP

Sec.8.1 Asynchronous Counter Operation

The term asynchronous refers to events that do not have a fixed time relationship with each other and, generally, do not occur at the same time.

CHAPTER 7

Sec.7.4 Flip-Flop Applications

Counting

Example 7-11 Determine the output waveforms.

CHAPTER 7

Sec.7.4 Flip-Flop Applications

Counting

CHAPTER 7

Chapter 8 Counters

Review

• Latch • Flip-Flop

Sec.7.3 Flip-Flop Operating Characteristics

Propagation Delay Times

A propagation delay time is the interval of time required after an input signal has been applied for the resulting output change to occur.