计算机组成原理原码列除法器

计算机组成原理第六章答案

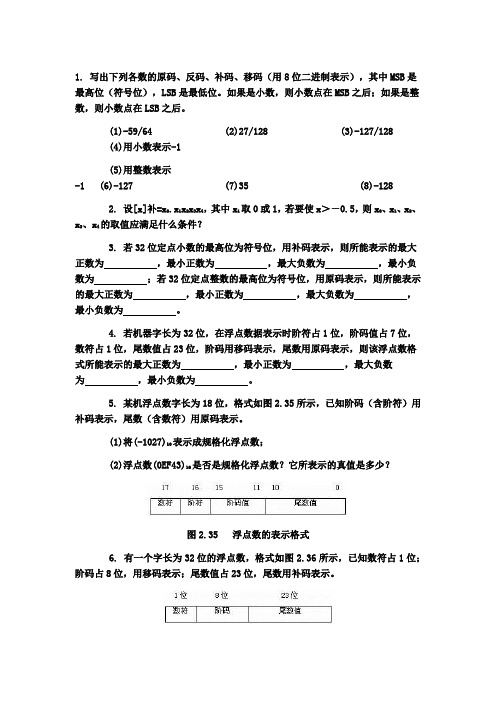

1. 写出下列各数的原码、反码、补码、移码(用8位二进制表示),其中MSB是最高位(符号位),LSB是最低位。

如果是小数,则小数点在MSB之后;如果是整数,则小数点在LSB之后。

(1)-59/64 (2)27/128 (3)-127/128(4)用小数表示-1(5)用整数表示-1 (6)-127 (7)35 (8)-1282. 设[x]补=x0.x1x2x3x4,其中x i取0或1,若要使x>-0.5,则x0、x1、x2、x3、x4的取值应满足什么条件?3. 若32位定点小数的最高位为符号位,用补码表示,则所能表示的最大正数为,最小正数为,最大负数为,最小负数为;若32位定点整数的最高位为符号位,用原码表示,则所能表示的最大正数为,最小正数为,最大负数为,最小负数为。

4. 若机器字长为32位,在浮点数据表示时阶符占1位,阶码值占7位,数符占1位,尾数值占23位,阶码用移码表示,尾数用原码表示,则该浮点数格式所能表示的最大正数为,最小正数为,最大负数为,最小负数为。

5. 某机浮点数字长为18位,格式如图2.35所示,已知阶码(含阶符)用补码表示,尾数(含数符)用原码表示。

(1)将(-1027)10表示成规格化浮点数;(2)浮点数(0EF43)16是否是规格化浮点数?它所表示的真值是多少?图2.35 浮点数的表示格式6. 有一个字长为32位的浮点数,格式如图2.36所示,已知数符占1位;阶码占8位,用移码表示;尾数值占23位,尾数用补码表示。

图2.36 浮点数的表示格式请写出:(1)所能表示的最大正数;(2)所能表示的最小负数;(3)规格化数所能表示的数的范围。

7. 若浮点数x的IEEE754标准的32位存储格式为(8FEFC000)16,求其浮点数的十进制数值。

8. 将数(-7.28125)10转换成IEEE754标准的32位浮点数的二进制存储格式。

9. 已知x=-0.x1x2…x n,求证:[x]补=+0.00…01。

计算机组成原理课后答案(白中英主编_第五版_立体化教材)_2

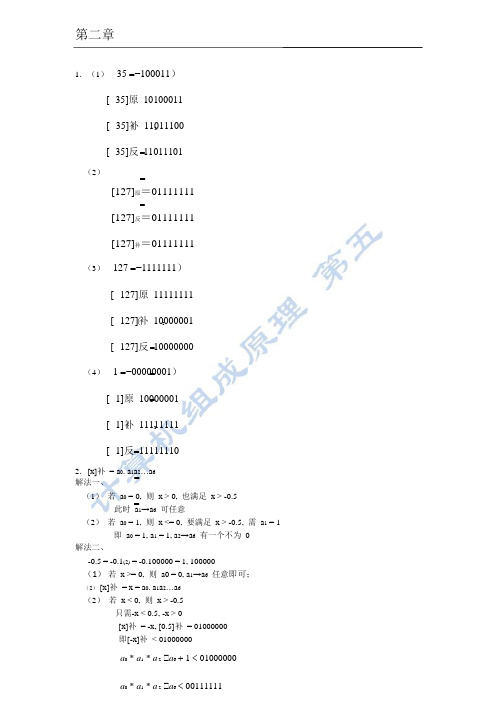

( 2= ==( 2= = =( 2===第二章1.(1) 35 =−100011)[ 35]原 10100011[ 35]补 11011100 [ 35]反 11011101(2)[127]原=01111111[127]反=01111111[127]补=01111111(3) 127 =−1111111)[ 127]原 11111111[ 127]补 10000001[ 127]反 10000000(4) 1 =−00000001)[ 1]原 10000001[ 1]补 11111111 [ 1]反 111111102.[x]补 = a 0. a 1a 2…a 6解法一、(1) 若 a 0 = 0, 则 x > 0, 也满足 x > -0.5此时 a 1→a 6 可任意(2) 若 a 0 = 1, 则 x <= 0, 要满足 x > -0.5, 需 a 1 = 1 即 a 0 = 1, a 1 = 1, a 2→a 6 有一个不为 0解法二、-0.5 = -0.1(2) = -0.100000 = 1, 100000(1) 若 x >= 0, 则 a0 = 0, a 1→a 6 任意即可;(2) [x]补= x = a 0. a 1a 2…a 6(2) 若 x < 0, 则 x > -0.5只需-x < 0.5, -x > 0[x]补 = -x, [0.5]补 = 01000000 即[-x]补 < 01000000a 0 * a 1 * a 2 a 6 + 1 < 01000000⋅ (1 2 ) 即: 2 2 ⋅ 2(最接近 0 的负数)即: 2 2 ⋅ (2 + 2[ 2 2 ⋅ 2 ⋅ (1 2 ) ] [ 22 1 ⋅ ( 1) , 2 2 ⋅ (2 1 + 2 ) ]a 0 a 1a 2 a 6 > 11000000即 a 0a 1 = 11, a 2→a 6 不全为 0 或至少有一个为 1(但不是“其余取 0”)3.字长 32 位浮点数,阶码 8 位,用移码表示,尾数 23 位,用补码表示,基为 2EsE 1→E 8MsM 21M 0(1) 最大的数的二进制表示E = 11111111Ms = 0, M = 11…1(全 1)1 11111111 01111111111111111111111(2) 最小的二进制数E = 11111111Ms = 1, M = 00…0(全 0) 1 11111111 1000000000000000000000(3) 规格化范围正最大E = 11…1, M = 11…1, Ms = 08 个22 个即: 227 122正最小E = 00…0, M = 100…0, Ms = 08 个7121 个负最大E = 00…0, M = 011…1, Ms = 18 个 21 个负最小7 1E = 11…1, M = 00…0, Ms =18 个22 个22 )即: 22⋅ ( 1) 规格化所表示的范围用集合表示为:71, 227122 7 7 2244.在 IEEE754 标准中,一个规格化的 32 位浮点数 x 的真值表示为:X=( 1)s ×(1.M )× 2 E 127(1)27/64=0.011011=1.1011× 22E= -2+127 = 125= 0111 1101 S= 0M= 1011 0000 0000 0000 0000 000最后表示为:0 01111101 10110000000000000000000 (2)-27/64=-0.011011=1.1011× 22E= -2+127 = 125= 0111 1101 S= 1M= 1011 0000 0000 0000 0000 000最后表示为:1 01111101 10110000000000000000000 5.(1)用变形补码进行计算:[x]补=00 11011 [y]补=00 00011[x]补 = [y]补 = [x+y]补00 11011 + 00 00011 00 11110结果没有溢出,x+y=11110(2) [x]补=00 11011 [y]补=11 01011[x]补 = [y]补 = [x+y]补=00 11011 + 11 01011 00 00110结果没有溢出,x+y=00110(3)[x]补=11 01010 [y]补=11 111111[x]补 = [y]补 = [x+y]补=00 01010 + 00 11111 11 01001结果没有溢出,x+y=−101116.[x-y]补=[x]补+[-y]补 (1)[x]补=00 11011[-y]补=00 11111[x]补 =00 11011 [-y]补 = + 00 11111 [x-y]补= 01 11010结果有正溢出,x−y=11010(2)[x]补=00 10111[-y]补=11 00101[x]补 =00 10111 [-y]补 = + 11 00101 [x-y]补结果没有溢出,x−y=−00100(3)[x]补=00 11011 [-y]补=00 10011[x]补= 00 11011[-y]补= + 00 10011[x-y]补= 01 01110结果有正溢出,x−y=100107.(1)用原码阵列乘法器:[x]原=0 11011 [y]原=1 11111因符号位单独考虑,|x|=11011 |y|=111111 1 0 1 1×) 1 1 1 1 1——————————————————————————1 1 0 1 11 1 0 1 11 1 0 1 11 1 0 1 11 1 0 1 11 1 0 1 0 0 0 1 0 1[x×y]原=1 1101000101用补码阵列乘法器:[x]补=0 11011 [y]补=1 00001乘积符号位为:1|x|=11011 |y|=111111 1 0 1 1×) 1 1 1 1 1——————————————————————————1 1 0 1 11 1 0 1 11 1 0 1 11 1 0 1 11 1 0 1 0 0 0 1 0 1[x×y]补=1 0010111011(2) 用原码阵列乘法器:[x]原=1 11111 [y]原=1 11011因符号位单独考虑,|x|=11111 |y|=110111 1 1 1 1×) 1 1 0 1 1——————————————————————————1 1 1 1 11 1 1 1 10 0 0 0 01 1 1 1 11 1 1 1 11 1 0 1 0 0 0 1 0 1[x×y]原=0 1101000101用补码阵列乘法器:[x]补=1 00001 [y]补=1 00101乘积符号位为:1|x|=11111 |y|=110111 1 1 1 1×) 1 1 0 1 1——————————————————————————1 1 1 1 11 1 1 1 10 0 0 0 01 1 1 1 111111[x×y]补=0 11010001018.(1) [x]原=[x]补=0 11000[-∣y ∣]补=1 00001被除数 X 0 11000 +[-|y|]补 1 00001----------------------------------------------------余数为负 1 11001 →q0=0左移 1 10010 +[|y|]补0 11111----------------------------------------------------余数为正 0 10001 →q1=1左移 1 00010 +[-|y|]补1 00001----------------------------------------------------余数为正 0 00011 →q2=1左移 0 00110 +[-|y|]补1 00001----------------------------------------------------余数为负 1 00111 →q3=0左移 0 01110 +[|y|]补0 11111----------------------------------------------------余数为负 1 01101 →q4=0左移 0 11010 +[|y|]补0 11111----------------------------------------------------余数为负 1 11001 →q5=0+[|y|]补0 11111 ----------------------------------------------------余数 0 11000故 [x÷y]原=1.11000 即 x÷y= −0.11000 余数为 0 11000(2)[∣x ∣]补=0 01011[-∣y ∣]补=1 00111被除数 X 0 01011 +[-|y|]补 1 00111----------------------------------------------------余数为负 1 10010 →q0=0x+y= 1.010010*2 = 2 *-0.101110左移 1 00100 +[|y|]补 0 11001----------------------------------------------------余数为负 1 11101 →q1=0左移 1 11010 +[|y|]补0 11001----------------------------------------------------余数为正 0 10011 →q2=1左移 1 00110 +[-|y|]补1 00111----------------------------------------------------余数为正 0 01101 →q3=1左移 0 11010 +[-|y|]补1 00111----------------------------------------------------余数为正 0 00001 →q4=1左移 0 00010 +[-|y|]补1 00111----------------------------------------------------余数为负 1 01001 →q5=0 +[|y|]补0 11001----------------------------------------------------余数 0 00010x÷y= −0.01110余数为 0 000109.(1) x = 2-011*0.100101, y = 2-010*(-0.011110)[x]浮 = 11101,0.100101 [y]浮 = 11110,-0.011110 Ex-Ey = 11101+00010=11111 [x]浮 = 11110,0.010010(1)x+y 0 0. 0 1 0 0 1 0 (1)+ 1 1. 1 0 0 0 1 01 1. 1 1 0 1 0 0 (1)规格化处理: 1.010010 阶码11100-4 -4x-y0 0. 0 1 0 0 1 0 (1) + 0 0. 0 1 1 1 1 00 0 1 1 0 0 0 0 (1) 规格化处理:0.110000阶码11110x-y=2-2*0.110001(2) x = 2-101*(-0.010110), y = 2-100*0.010110[x]浮= 11011,-0.010110 [y]浮= 11100,0.0101109Ex-Ey = 11011+00100 = 11111 [x]浮= 11100,1.110101(0) x+y 1 1. 1 1 0 1 0 1+ 0 0. 0 1 0 1 1 00 0. 0 0 1 0 1 1规格化处理: 0.101100 x+y= 0.101100*2阶码-611010x-y1 1.1 1 0 1 0 1 + 1 1.1 0 1 0 1 01 1.0 1 1 1 1 1规格化处理: 1.011111 阶码11100x-y=-0.100001*2-410.(1) Ex = 0011, Mx = 0.110100Ey = 0100, My = 0.100100 Ez = Ex+Ey = 0111 Mx*My 0. 1 1 0 1* 0.1 0 0 101101 00000 00000 01101 00000 001110101规格化:26*0.111011(2) Ex = 1110, Mx = 0.011010Ey = 0011, My = 0.111100 Ez = Ex-Ey = 1110+1101 = 1011 [Mx]补 = 00.011010[My]补 = 00.111100, [-My]补 = 11.00010010计算机组成原理第五版习题答案00011010 +[-My]11000100 11011110 10111100+[My]00111100 11111000 111100000.0 +[My]00111100 00101100 010110000.01 +[-My]11000100 00011100 001110000.011 +[-My]11000100 11111100 111110000.0110 +[My]00111100 00110100 011010000.01101 +[-My]1 1 0 00 1 0 0 0 0 1 0 1 10 00.01101 商 = 0.110110*2-6, 11.4 位加法器如上图,C i = A i B i + A i C i 1 + B i C i 1 = A i B i + ( A i + B i )C i 1 = A i B i + ( A i B i )C i 1(1)串行进位方式余数=0.101100*2-6C 1 = G 1+P 1C 0 C 2 = G 2+P 2C 1 C 3 = G 3+P 3C 2 C 4 = G 4+P 4C 3 其中:G 1 = A 1B 1G 2 = A 2B 2G 3 = A 3B 3 G 4 = A 4B 4P1 = A 1⊕B 1(A 1+B 1 也对) P 2 = A 2⊕B 2 P 3 = A 3⊕B 3 P 4 = A 4⊕B 4(2)并行进位方式 C 1 = G 1+P 1C 0C 2 = G 2+P 2G 1+P 2P 1C 0C 3 = G 3+P 3G 2+P 3P 2G 1+P 3P 2P 1C 0C 4 = G 4+P 4G 3+P 4P 3G 2+P 4P 3P 2G 1+P 4P 3P 2P 1C 0“计算机组成原理第五版习题答案12.(1)组成最低四位的74181 进位输出为:C4 = C n+4 = G+PC n = G+PC0,C0为向第0 位进位其中,G = y3+y2x3+y1x2x3+y0x1x2x3,P = x0x1x2x3,所以C5 = y4+x4C4C6 = y5+x5C5 = y5+x5y4+x5x4C4(2)设标准门延迟时间为T,与或非”门延迟时间为1.5T,则进位信号C0,由最低位传送至C6需经一个反相器、两级“与或非”门,故产生C0的最长延迟时间为T+2*1.5T = 4T(3)最长求和时间应从施加操作数到ALU 算起:第一片74181 有3 级“与或非”门(产生控制参数x0, y0, C n+4),第二、三片74181 共 2 级反相器和 2 级“与或非”门(进位链),第四片74181 求和逻辑(1 级与或非门和 1 级半加器,设其延迟时间为3T),故总的加法时间为:t0 = 3*1.5T+2T+2*1.5T+1.5T+3T = 14T13.设余三码编码的两个运算数为X i和Y i,第一次用二进制加法求和运算的和数为S i’,进位为C i+1’,校正后所得的余三码和数为S i,进位为C i+1,则有:X i = X i3X i2X i1X i0Y i = Y i3Y i2Y i1Y i0S i’ = S i3’S i2’S i1’S i0’s i3 s i2 s i1 s i0Ci+1FA FA FA FA十进校正+3VFA s i3'FAs i2'FAs i1'FAs i0'二进加法X i3 Y i3 X i2 Y i2 X i1 Y i1 X i0 Y i0当C i+1’ = 1时,S i = S i’+0011并产生C i+1当C i+1’ = 0时,S i = S i’+1101根据以上分析,可画出余三码编码的十进制加法器单元电路如图所示。

计算机组成原理_第四版课后习题答案(完整版)[1]

![计算机组成原理_第四版课后习题答案(完整版)[1]](https://img.taocdn.com/s3/m/47ac64e919e8b8f67c1cb928.png)

第一章1.比较数字计算机和模拟计算机的特点解:模拟计算机的特点:数值由连续量来表示,运算过程是连续的;数字计算机的特点:数值由数字量(离散量)来表示,运算按位进行。

两者主要区别见P1 表1.1。

2.数字计算机如何分类?分类的依据是什么?解:分类:数字计算机分为专用计算机和通用计算机。

通用计算机又分为巨型机、大型机、中型机、小型机、微型机和单片机六类。

分类依据:专用和通用是根据计算机的效率、速度、价格、运行的经济性和适应性来划分的。

通用机的分类依据主要是体积、简易性、功率损耗、性能指标、数据存储容量、指令系统规模和机器价格等因素。

3.数字计算机有那些主要应用?(略)4.冯. 诺依曼型计算机的主要设计思想是什么?它包括哪些主要组成部分?解:冯. 诺依曼型计算机的主要设计思想是:存储程序和程序控制。

存储程序:将解题的程序(指令序列)存放到存储器中;程序控制:控制器顺序执行存储的程序,按指令功能控制全机协调地完成运算任务。

主要组成部分有:控制器、运算器、存储器、输入设备、输出设备。

5.什么是存储容量?什么是单元地址?什么是数据字?什么是指令字?解:存储容量:指存储器可以容纳的二进制信息的数量,通常用单位KB、MB、GB来度量,存储容量越大,表示计算机所能存储的信息量越多,反映了计算机存储空间的大小。

单元地址:单元地址简称地址,在存储器中每个存储单元都有唯一的地址编号,称为单元地址。

数据字:若某计算机字是运算操作的对象即代表要处理的数据,则称数据字。

指令字:若某计算机字代表一条指令或指令的一部分,则称指令字。

6.什么是指令?什么是程序?解:指令:计算机所执行的每一个基本的操作。

程序:解算某一问题的一串指令序列称为该问题的计算程序,简称程序。

7.指令和数据均存放在内存中,计算机如何区分它们是指令还是数据?解:一般来讲,在取指周期中从存储器读出的信息即指令信息;而在执行周期中从存储器中读出的信息即为数据信息。

计算机组成原理第二章参考答案

第2章 参考答案2写出下列十进制数的原码、反码、补码和移码表示(用8位二进制数)。

如果是小数,则用定点小数表示;若为整数,则用定点整数表示。

其中MSB 是最高位(符号位),LSB 是最低位。

(1)-1 (2) -38/64 解:(1)-1=(-0000001)2 原码: 10000001反码: 11111110 补码: 11111111 移码: 01111111(2)-38/64=-0.59375=(-0.1001100)2或-38/64=-(32+4+2)*2-6=-(100110)*2-6=(-0.1001100)2 原码: 1.1001100反码: 1.0110011补码: 1.0110100移码: 0.0110100注:-1如果看成小数,那么只有补码和移码能表示得到,定点小数-1的补码为:1.0000000此例类似于8位定点整数的最小值-128补码为100000003 有一字长为32位的浮点数,符号位1位;阶码8位,用移码表示;尾数23位,用补码表示;基数为2.请写出:(1)最大数的二进制表示,(2)最小数的二进制表示,(3)规格化数所能表示的数的范围。

解:(题目没有指定格式的情况下,用一般表示法做)(1)最大数的二进制表示:0 11111111 11111111111111111111111 (2)最小数的二进制表示:1 11111111 00000000000000000000000(1) 7232112*2---() (2) 7211*2--()(3)规格化最大正数:0 11111111 111111111111111111111117232112*2---()规格化最小正数:0 00000000 100000000000000000000007122*2--规格化最大负数:1 00000000 011111111111111111111117123222*2----+()规格化最小负数:1 11111111 000000000000000000000007211*2--()规格化数的表示的数的范围为:7777211232122321[1*2,22*2][2*2,12)*2]----------+- ()()(下面补充IEEE 754的规格化浮点数表示范围:IEEE 754的尾数采用1.M 的形式,原码表示;阶e=E-127 (相对于一般表示法的e=E-128,人为的加了1);并且最大的阶(11111111)和最小的阶(00000000)用去作为特殊用途。

4并行除法运算解读

2. 比较r0和2-1y, 因r0>2-1y, 表示够减, 小数点后第一位商“1”,作r0-2-1y,

得余数r1。 3. 比较r1和2-2y, 因r1>2-2y, 表示够减, 小数点后第二位商“1”, 作r1-2-2

y, 得余数r2。

4. 比较r2和2-3y, 因r2<2-3y, 不够减, 小数点后第三位商“0”, 不作减法, 得 余数r3(=r2)。 5. 比较r3和2-4y, 因r3>2-4y, 表示够减, 小数点后第四2位商“1”, 作r3-2-4

计算机组成原理 2

手算运算步骤

例: 设被除数x=0.1001, 除数y=0.1011, 仿十进制除法运算, 手算求x÷y的过程。 0.1 1 0 1 0.1 0 0 1 0 -0.0 1 0 1 1 0.0 0 1 1 1 0 -0.0 0 1 0 1 1 0.0 0 0 0 1 1 0 -0.0 0 0 1 0 1 1 0.0 0 0 0 1 1 0 0 -0.0 0 0 0 1 0 1 1 -0.0 0 0 0 0 0 0 1 商q x ( r0 ) 2- 1y r1 2- 2y r2 2- 3y r3 2- 4y r4

计算机组成原理

13

最上面一行所执行的初始操作经常是减法。因此最上面一行的控制 线P固定置成“1”。减法是用2的补码运算来实现的,这时右端各CAS单 元上的反馈线用作初始的进位输入。每一行最左边的单元的进位输出决 定着商的数值。将当前的商反馈到下一行,我们就能确定下一行的操作。 由于进位输出信号指示出当前的部分余数的符号,因此,它将决定下一 行的操作将进行加法还是减法。

y, 得余数r4,

计算机组成原理

共求四位商, 至此除法完毕。

4

机器运算与手算的不同 (1) 在计算机中,小数点是固定的,不能简单地采用手算的办法。为便于 机器操作, 除数Y固定不变, 被除数和余数进行左移 (相当于乘2) (2)机器不会心算,必须先作减法,若余数为正, 才知道够减;若余数为负, 才知道不够减。不够减时必须恢复原来的余数,以便再继续往下运算。这种 方法称为恢复余数法。 (3)要恢复原来的余数, 只要当前的余数加上除数即可。但由于要恢复余数, 使除法进行过程的步数不固定, 因此控制比较复杂。 实际中常用不恢复余数法,又称加减交替法。其特点是运算过程中如出 现不够减,则不必恢复余数,根据余数符号,可以继续往下运算,因此步数 固定,控制简单。

计算机组成原理试题二答案

南昌航空大学2008—2009学年第1学期期末考试课程名称: 计算机组成与结构A B 卷参考答案题号一二三四五六七合计满分502525100实得分一. 基本题(共50分)1. 冯诺依曼型计算机的主要设计思想是什么?它包括哪些主要组成部分?(10分)答:冯诺依曼型计算机的主要设计思想是:采用存储程序的方式,编好的程序和数据存放在同一个存储器中,计算机可以在无人干预的情况下自动完成逐条取出指令和执行指令的任务;在机器内部,指令和数据均采用二进制码表示,指令在存储器中按顺序存放。

其主要组成部分有:运算器、控制器、存储器、输入输出设备,以及总线。

2. 已知x和y,用变形补码计算x-y,同时指出结果是否溢出。

(16分)(1) x=10111 y=11011 (2) x=11011 y=-10011解: [x-y]补=[x]补+[-y]补 (8分)(1) [x]补=00 10111, [-y]补=11 00101[x]补 00 10111+ [-y]补 11 00101 11 11100 双符号位为“11”,结果没有溢出, x-y=-00100。

(2) [x]补=00 11011, [-y]补=00 10011 (8分)[x]补 00 11011+ [-y]补 00 10011 01 01110 双符号位为“01”,表示已溢出, x-y=10010。

3. 总线仲裁分集中式仲裁和分布式仲裁两类。

简述集中式仲裁可分为哪几种方式?每种方式各自的特点是什么?(12分)答:集中式仲裁可分为链式查询方式、计数器定时查询方式和独立请求方式三种,各自的特点如下:(1)链式查询方式:总线授权信号BG串行地从一个I/O接口传送到下一个I/O接口。

由近至远依次查询各I/O接口,一旦到达有总线请求的接口就不再往下查询。

显然,离总线仲裁器越近的设备优先级越高。

该方式的优点是:只用很少几根线就能按一定优先次序实现总线仲裁,且这种结构分容易扩充设备。

计算机组成原理课设 定点原码一位除法器的设计

沈阳航空航天大学课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:定点原码一位除法器的设计院(系):计算机学院专业:计算机科学与技术班级:94010101学号:2009040101013姓名:胡桂林指导教师:周大海完成日期:2012年1月13日沈阳航空航天大学课程设计报告目录第1章总体设计方案 (1)1.1设计环境 (1)1.2设计原理 (2)第2章详细设计方案 (4)2.1总流程图 (4)2.2上商置0模块流程图 (6)2.3上商置1模块流程图 (6)2.4商的符号流程图 (7)第3章测试结果 (9)3.1程序仿真 (9)3.2仿真测试一 (9)3.3仿真测试二 (10)附录 (11)参考文献 (14)第1章总体设计方案1.1 设计环境伟福COP2000实验箱,用汇编语言编程实现定点原码一位除法器COP2000 计算机组成原理实验系统由实验平台、开关电源、软件三大部分组成。

实验平台上有寄存器组R0-R3、运算单元、累加器A、暂存器W、直通/左移/右移单元、地址寄存器、程序计数器、堆栈、中断源、输入/输出单元、存储器单元、微地址寄存器、指令寄存器、微程序控制器、组合逻辑控制器、扩展座、总线插孔区、微动开关/指示灯、逻辑笔、脉冲源、20 个按键、字符式LCD、RS232 口。

COP2000集成调试软件(即仿真测试软件)共分为6部分:(1)主菜单区实现实验仪的各项功能的菜单,包括[文件][编辑][汇编][运行][帮助]五大项,各项线面做详细介绍。

(2)快捷图标区快速实现各项功能按键(3)源程序/机器码区在此区域有源程序窗口,反汇编窗口,EM程序代码窗口。

源程序用于输入,显示,编辑汇编源程序:反汇编窗口显示程序编译后的机器码及反汇编的程序;EM程序代码窗口用数据方式机器码。

(4)机构图/逻辑波形区结构图能结构化显示模型机的各部件,以及运行时数据走向寄存器值;逻辑波形图能显示模型机运行时所有信号的程序。

计算机组成原理第3章 运算方法和运算器

6

3 如何用加法器实现补码加减法呢?图3.1给出 了补码加减运算器示意框图。图中有一个n+1位加 法器(∑0~∑n),提供操作数与暂存结果的寄存 器A与B(n+1)位,运算器功能为A±B→A。现以 粗框表示寄存器,只画出其中一位加、减控制逻辑

7

图3.1

补码加减运算器示意框图

第 3章

运算器是计算机系统的重要组成部件,它在控 制器的控制下实现其功能。主要完成算术运算和逻 辑运算,也是数据信息的重要传送通道。本章主要 讨论运算方法和运算器,内容包括算术逻辑运算基础 、算术逻辑运算部件ALU、定点乘法运算、定点除 法运算、浮点算术运算及其实现,以及运算器的基

1

第一节 前一章我们介绍了定点数是指小数点位置固定 的数,这一特点决定了其表示的数值范围是有限的, 其要求的硬件比较简单。在计算机中,带符号的数 有原码、补码、反码等几种表示方法,原码加减和 补码加减是一切算术运算的基础。但原码加减运算 复杂,例如,加法指令指示做(+A)+(-B),由 于一操作数为负,实际操作是做减法(+A)-(+ B),结果符号与绝对值大的数的符号相同。

47

图3.8

组间串行进位的ALU图

48

图3.9

组间并行进位的ALU

49

运算器中除了有作为核心部件的加法器外,还 应该有能提供操作数和暂存运算结果的寄存器和数

50

运算器中的各个部件之间需要通信,为了简化 通信线路,通常采用总线方式。常采用三态门来控 制总线上的数据传送方向。例如对于8位单向总线, 其控制逻辑如图3.10所示,当T=0(有效)时,三 态门开通,8位的数据可以从a端传送到b端,通过 8条总线可以从源件传送到目的件中;当T=1(无 效)时,三态门关闭,跟b端相连的数据总线处于