实验2—占空比可调的PWM信号发生器

3.PWM信号发生器设计

第一期可编程逻辑设计培训研讨 2013年1月 湖北武汉

4

华中科技大学 国家电工电子实验教学示范中心

PWM信号发生器实验

• *编写TestBench并在ModelSim中仿真

`timescale 1ns/1ps module testbench; reg clk; reg [7:0] data; wire pwm; initial begin clk = 1'b1; data = 8'd0; pwm_t = 1'b0; #100000 data = 8'd32; #100000 data = 8'd64; #100000 data = 8'd128; #100000 data = 8'd160; #100000 data = 8'd192; #100000 data = 8'd224; #100000 data = 8'd255; #100000 $stop(); end always begin #20 clk = ~clk; end pwm pwm_inst(.clk(clk), .data(data), .pwm(pwm)); endmodule

• 编写并添加按键驱动和显示占空比的逻辑 • 下载至EDA-CPLD板上,并用示波器观察

第一期可编程逻辑设计培训研讨 2013年1月 湖北武汉 5 华中科技大学 国家电工电子实验教学示范中心

实验过程(自编)

• 直接在ModelSim ALTERA STARTER EDITION 6.5b 中进行编写、访真即可。 新建三个文件,

module pwm( input clk, input [7:0] data, output pwm ); reg [7:0] cnt; always@(posedge clk) begin cnt <= cnt + 1’b1; end always@(posedge clk) begin pwm <= (data > cnt); end endmodule

pwm调节占空比实验

}

while(key0&&key1==1);

while(key0&&key1==0);

}

void delay(uchar z)

{

for(x=0;x<z;x++)

for(y=0;y<125;y++);

}

void extern0() interrupt 1

{if(in==1)

{TL0=LPWM;

#include<reg52.h>

#define uchaine uint unsigned int

uchar x,z,key,LPWM,HPWM;

uint y;

sbit key0=P1^0;

sbit key1=P1^1;

sbit in=P1^2;//输出PWM

in=0;

}

else

{TL0=HPWM;

in=1;

}

}

pwm调节占空比实验 #include<reg52.h>#define uchar unsigned char #define uint unsigned int uchar x,z,key,lpwm,hpwm; uint sbitkey0=p1^0; sbit key1=p1^1; sbit in=p1^2;//输出pwm void time0(); void scankey(); void delay(uchar voidmain() time0();while(1) scankey();if(key==0) {if(hpwm<=253) {hpwm++; lpwm--;} if(lpwm<=253){hpwm--; lpwm++; voidtime0() {tmod=2; lpwm=224; hpwm=224; th0=224; tl0=224; ea=1; et0=1; tr0=1; voidscankey() do{while(key0&&key1==1); delay(40); if(key0==0) key=0; if(key1==0) key=1; while(key0&&key1==1);while(key0&&key1==0); voiddelay(uchar voidextern0() interrupt else{tl0=hpwm; hyhgyy144 分享于 2013-03-30 19:39:6.8 暂无简介 文档格式: .doc 文档页数: 2页 文档大小: 25.0k 文档热度: 文档分类: 待分类 文档标签: 报告

一种利用比较器实现占空比可调PWM信号的电路分析与应用

+ VL*

R1 / / R2

, B=Aຫໍສະໝຸດ R1+ R2 / / R5

R1 / / R2 + R5

VCC* R2 / / R5 + VH* R1 / / R2 )。 R1 + R2 / / R5 R1 / / R2 + R5

这样,电容 C1 就完成了一个完整的充放电循环,同时按照此循环过程不断进行充放电,

2. 电路仿真分析 在以上对原理分析的基础上,下面将利用 Multisim 软件对电路中的元件参数进行设定, 对电路性能进行仿真验证。图四为仿真原理图和元件参数设定值:

图四

图五为比较器 U1 同相输入 V2、反向输入 V3 和 U1 输出波形 Vout1 及二极管 D2 正极波 形:

图五

从图五中可以看到:振荡波形的周期 T 为 17.9ms,比较器 U1 输出高电平时为 10.8V, 输出低电平时为 1.196V。

比较器型号不同),并对输出 PWM 信号进行数据测试。

以下为 U1 同相输入和输出波形图(图七)、同相与反向输入波形图(图八)、Vout2 与 Vout 波形图(图九):

图七 U1A 同相输入和输出波形 图八 同相与反向输入波形

图九 Vout2 与 Vout 波形

以下为实际测试数据:

参数

频率 f

关键词:液晶模组;比较器;背光;PWM;占空比;仿真

一、PWM 信号的特点及产生方式

1. PWM 信号的特点 PWM 是 Pulse Width Modulation 的缩写,即脉冲宽度调制。它是利用数字输出来对模 拟电路进行控制的一种非常有效的技术,广泛应用于测量,通信,功率控制与变换等许多领 域,其中包括电动机控制、伺服控制、调光、开关电源,甚至某些音频放大器。 PWM 的一个优点是从处理器到被控系统信号都是数字形式的,无需进行数模转换。另外, 由于噪声只有在强到足以将逻辑 1 改变为逻辑 0 或将逻辑 0 改变为逻辑 1 时,才能对信号内 容产生影响。所以,抗噪能力强是 PWM 相对于模拟控制的另一个显著特点。 2. PWM 信号产生方式 产生 PWM 信号的方式有很多,主要可以分为以下几种: 1)分立元件 即采用电阻、电容、二极管、比较器等分立元器件搭建的电路。此类电路使用的元器件 数量较多,但能够对 PWM 波形产生的过程进行较为详细的分析和测试。便于对 PWM 电路进行 细致的学习和分析。 2)MCU 当前,MCU 应用的领域无所不在,其功能也是越来越强。通过设置定时器并软件编程由 MCU 的 IO 口输出 PWM 信号已经变得十分简单,一些更强大的 MCU 内部甚至直接集成了 PWM 输出功能,使用时只需设定 PWM 波形的相关参数即可。

STM32Cubemx输出可调频率与占空比的PWM

STM32Cubemx输出可调频率与占空⽐的PWM 这⾥就不对STM32的PWM进⾏讲解了,想要了解的可以百度⼀下,这⾥主要说怎么实现。

1、建⽴⼯程,我选的是STM32F103zet6芯⽚,选择定时器的PWM功能 2、配置时钟,我这⾥配的是内部时钟,没有配外部时钟,⽽且不是最⼤时钟,有需要的可以⾃⼰改 3、配置定时器,这⾥的话默认就可以,因为代码⾥⾯需要对配置的初始化代码进⾏修改的,⽽修改后才可以实现该功能 4、⽣成代码后,修改代码,找到PWM初始化函数,修改为如下代码,注意要把初始化函数前⾯的static关键字也去掉,⽽且函数声明也要跟着修改void MX_TIM4_Init(uint16_t pre,uint16_t pul) //修改初始化函数,改变频率与PWM{//占空⽐=Pulse/Period;频率:f=48M/pre/perTIM_MasterConfigTypeDef sMasterConfig;TIM_OC_InitTypeDef sConfigOC;htim4.Instance = TIM4;htim4.Init.Prescaler =pre; //分频(关键)htim4.Init.Period = 100-1;//计数周期(关键,若100的计数周期对于⼀些频率跟占空⽐误差⼤的话,可以⾃⼰计算更改调试计数周期⼤⼩)htim4.Init.CounterMode = TIM_COUNTERMODE_UP;htim4.Init.ClockDivision = TIM_CLOCKDIVISION_DIV1;htim4.Init.AutoReloadPreload = TIM_AUTORELOAD_PRELOAD_DISABLE;if (HAL_TIM_PWM_Init(&htim4) != HAL_OK){_Error_Handler(__FILE__, __LINE__);}sMasterConfig.MasterOutputTrigger = TIM_TRGO_RESET;sMasterConfig.MasterSlaveMode = TIM_MASTERSLAVEMODE_DISABLE;if (HAL_TIMEx_MasterConfigSynchronization(&htim4, &sMasterConfig) != HAL_OK){_Error_Handler(__FILE__, __LINE__);}sConfigOC.OCMode = TIM_OCMODE_PWM1;sConfigOC.Pulse = pul;//脉冲计数(关键)sConfigOC.OCPolarity = TIM_OCPOLARITY_HIGH;sConfigOC.OCFastMode = TIM_OCFAST_DISABLE;if (HAL_TIM_PWM_ConfigChannel(&htim4, &sConfigOC, TIM_CHANNEL_1) != HAL_OK){_Error_Handler(__FILE__, __LINE__);}HAL_TIM_MspPostInit(&htim4);} 5、接着在⾃⼰需要的代码⾥插⼊,PWM开始停⽌函数就可以啦HAL_TIM_PWM_Start(&htim4, TIM_CHANNEL_1); //PWM开启函数MX_TIM4_Init(uint16_t pre,uint16_t pul);//改变参数就可实现改变占空⽐跟频率的⽬的了HAL_TIM_PWM_Stop(&htim4, TIM_CHANNEL_1);//停⽌PWM 这⾥我说⼀下核⼼部分:占空⽐ = (Pulse/Period)*100%;频率: f = 48M/Prescaler/Period;影响PWM占空⽐跟频率的参数这主要是 Pulse、Prescaler、Period这3个;频率跟占空⽐都与Period(计数周期)有关,只要我们把计数周期定下来,修改Prescaler、跟Pulse 这两个值,就可以直接修改PWM的频率跟占空⽐了。

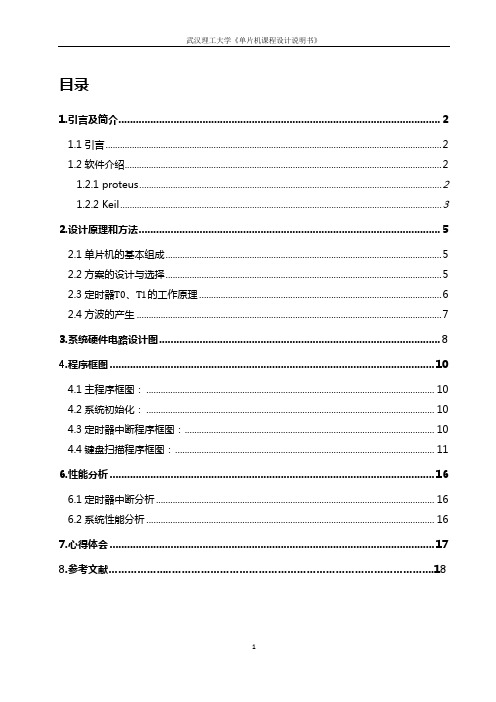

占空比可调信号发生器

目录1.引言及简介 (2)1.1引言 (2)1.2软件介绍 (2)1.2.1 proteus (2)1.2.2 Keil (3)2.设计原理和方法 (5)2.1单片机的基本组成 (5)2.2方案的设计与选择 (5)2.3定时器T0、T1的工作原理 (6)2.4方波的产生 (7)3.系统硬件电路设计图 (8)4.程序框图 (9)4.1主程序框图: (9)4.2系统初始化: (10)4.3定时器中断程序框图: (10)4.4键盘扫描程序框图: (10)6.性能分析 (16)6.1定时器中断分析 (16)6.2系统性能分析 (16)7.心得体会 (17)8.参考文献 (18)1.引言及简介1.1引言单片机集成度高,功能强,可靠性高,体积小,功耗低,使用方便,价格低廉等一系列优点,目前已经渗入到人们工作和生活的方方面面,几乎无处不在,无所不为。

单片机的应用领域已经从面向工业控制,通讯,交通,智能仪表等迅速发展到家用消费产品,办公自动化,汽车电子,PC机外围一记网络通讯等广大领域。

单片机有两种基本结构形式:一种是在通用微型计算机中广泛采用的,将程序存储器和数据存储器合用一个存储器空间的结构,成为普林斯机构。

另一种是将程序存储器个数据存储器截然分开,分别寻址的结构,一般需要较大的程序存储器,目前单片机以采用程序存储器截然分开的结构多。

本课题讨论的占空比可调的信号发生器的核心是目前应用极为广泛的51系列单片机。

基于单片机的信号发生器的设计,该课题的设计目的是充分运用大学期间所学的专业知识,考察现在正在使用的信号发生器的基本功能,完成一个基本的实际系统的设计全过程。

关键是这个实际系统设计的过程,在整个过程中我可以充分发挥自动化的专业知识。

特别是这个信号发生器的设计中涉及到一个典型的控制过程。

通过单片机控制一个有特殊功能的信号发生芯片,可以产生一系列有规律的幅度和频率可调的波形。

这样一个信号发生器装置在控制领域有相当广泛的应用范围。

设计并实现占空比可调信号发生器

2011年至2012年第1学期《单片机原理与应用》课程设计班级1006402指导教师涂立李旎学生人数___ _3__ ___设计份数 1 2011年12月23日单片机课程设计报告一.设计时间2011年12月19日-----2011年12月23日二.设计地点一实验楼-401机房三.设计目的1、进一步熟悉和掌握单片机的结构及工作原理。

2、掌握单片机的接口技术及相关外围芯片的外特性,控制方法。

3、通过课程设计,掌握以单片机核心的电路设计的基本方法和技术,了解有关电路参数的计算方法。

4、通过实际程序设计和调试,逐步掌握模块化程序设计方法和调试技术,提高我们的自学能力与动手能力。

6、充分运用我们所学的专业知识,考察现在正在使用的信号发生器的基本功能,完成一个基本的实际系统的设计全过程,充分培养我们的分析能力与创新能力。

四.设计小组成员五.指导老师涂立(副教授)、李旎(讲师)六.设计课题设计并实现占空比可调信号发生器;要求:用4个按键分别控制输出信号的占空比和频率(用示波器观察输出波形),显示占空比范围10%、30%、50%,频率范围1Hz和5Hz,实时测量输出信号的占空比和频率值。

七.基本思路及关键问题的解决方法1、基本思路(1)实现可调节占空比信号发生器,我们可以设计K1是频率调节开关,K2,K3,K4为占空比调节开关。

K1按下一次时,对应的频率为1HZ,再按下K2,K3,K4为此频率下占空比分别为10%,30%,50%的输出信号;按下K1两次时(当按下次数大于2时将默认为初始状态),对应的频率为5HZ,K2,K3,K4按键的功能如上,本设计可实现同频率不同占空比的任意切换和不同频率间的直接切换。

(2)实验过程1.开打keil软件,建立一个新工程单击【Project】在下拉菜单中找到【Newproject...】选项,如图1所示:图1. 新建工程图2.选择工程要保存的路径,并且输入工程文件名。

Keil的一个工程里通常含有很多小文件,为了方便管理,一般将一个工程放在一个独立的文件夹下,比如保存到课程设计文件夹,工程文件的名字为lession,如图2所示:图2. 保存文件图3.单击保存后会弹出一个对话框,要求选择单片机的型号,可以根据使用的单片机来选择。

pwm信号发生器.实验报告

EDA实验报告学院:电气学院班级:电科1班学号:12401720126姓名:刘明煌实验三PWM信号发生器的设计1.实验目的(1)进一步熟悉掌握Quartus H。

(2)进一步熟悉和掌握GW48-CK或其他EDA实验开发系统的应用。

(3)学习和掌握VHDL进程语句和元件例化语句的使用。

2.实验内容设计并调试好PWM信号发生器电路PWM.VHD,并用GW48-CK或其他EDA实验开发系统进行硬件验证。

3.实验条件(1)开发软件:Quartus H。

(2)实验设备:GW48-CK EDA实验开发系统。

(3)拟用芯片:EP2C8Q208C8N。

4.实验设计1) 系统原理框图为了简化设计并便于显示,本信号发生器电路PWM的设计分为两个层次,其底层电路可,再由包括两个完全相同的加载加法计数器LCNT8而成。

PWM电路图2) VHDL程序PWM信号发生器的底层和顶层电路均采用VHDL文本输入,有关VHDL程序如下。

加载加法计数器LCNT8的VHDL源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY LCNT8 ISPORT(CLK ,L D:IN STD_LOGIC;D:IN INTEGER RANGE 0 TO 255;CAO:OUT STD_LOGIC);END ENTITY LCNT8;ARCHITECTURE ART OF LCNT8 ISSIGNAL COUNT:INTEGER RANGE 0 TO 255;BEGINIF CLKEVENT AND CLK=1THENIF LD=1THEN COUNT<=D;ELSE C0UNT<=C0UNT+1;END IF;END IF;END PROCESS;PROCESS(COUNT) ISBEGINIF COUNT=255 THEN CAO<=1;ELSE CAO<=0END IF;END PROCESS;END ARCHITECTURE ART;PWM信号发生器的VHDL源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY PWM ISPORT(CLK:IN STD_LOGIC;A,B:IN STD_LOGIC_VECTOR(7 DOWNTO 0);PWM:OUT STD_LOGIC);END ENTITY PWM;ARCHITECTURE ART OF PWM ISCOMPONENT LCNT8 ISPORT(CLK ,L D:IN STD_LOGIC;D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);CAO:OUT STD_LOGIC);END COMPONENT LCNT8;SIGNAL CAO1,CAO2:STD_LOGIC;SIGNAL LD1,LD2:STD_LOGIC;SIGNAL SPWM:STD_LOGIC;BEGINU1:LCNT8 PORT MAP(CLK=>CLK,LD=>LD1,D=>A,CAO=>CAO1);U2:LCNT8 PORT MAP(CLK=>CLK,LD=>LD2,D=>B,CAO=>CAO2);PROCESS(CAO1,CAO2)ISBEGINIF CAO1='1'THEN SPWM<='0';ELSIF CAO2'EVENT AND CAO2='1'THEN SPWM<='1';END IF;END PROCESS;LD1<=NOT SPWM;LD2<=SPWM;PWM<=SPWM;END ARCHITECTURE ART;3)工程编译后:4)仿真波形设置本程序包括两个程序,因此先进行底层的加载加法计数器 LCNT8的仿真,在进行顶层 PWM 的仿真,下图为 PWM 的 输入设置及可能结果估计图。

PWM信号发生器的设计——毕业设计论文

PWM信号发生器的设计实验/上机报告一、实验目的1、掌握序列发生器和检测器的工作原理;2、初步学会用状态机进行数字系统设计。

二、实验环境Quartus II 7.0 开发系统三、实验内容用状态机设计实现串序列检测器设计,可以用原理图输入法设计序列信号发生器,要求产生序列:0111010011011010;再进行检测设计,若检测到序列:11010则输出为“1”,否则输出为“0”。

并对其进行仿真和硬件测试。

四、实验过程本实验可以分为两部分来设计。

第一步设计序列信号发生器,在这里可以采用模16的计数器74LS161来产生模16的计数,并由它的4位输出可以产生16种状态,由此可以用来设计序列产生器,也可以采用状态机产生序列,本实验用状态机产生序列。

第二步设计序列检测器,这里用状态机设计,如果为真输出1,为假输出为0;第三步设计串行转并行输出,将序列并行输出在LED管上显示。

第四步是设计一个计数脉冲,记录出现所需要的序列的次数。

第五步是将所有模块连接起来,构成一个完整的序列发生和检测设计器。

实验代码:1、序列发生器library ieee;use ieee.std_logic_1164.all;entity xulie_produce is—序列产生电路port(clk,reset:in std_logic;comb_outputs:out std_logic);--序列输出end xulie_produce;architecture behav of xulie_produce istype fsm_st is (s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15);--状态设计signal current_state,next_state:fsm_st;beginreg:process(reset,clk)—主控时序进程beginif reset ='1'then current_state<=s0;elsif clk='1'and clk'event thencurrent_state<=next_state;end if;end process;com:process(current_state)—主控组合进程begincase current_state iswhen s0 => comb_outputs<='0';next_state<=s1; when s1 => comb_outputs<='1';next_state<=s2; when s2 => comb_outputs<='1';next_state<=s3; when s3 => comb_outputs<='1';next_state<=s4; when s4 => comb_outputs<='0';next_state<=s5; when s5 => comb_outputs<='1';next_state<=s6; when s6 => comb_outputs<='0';next_state<=s7; when s7 => comb_outputs<='0';next_state<=s8; when s8 => comb_outputs<='1';next_state<=s9; when s9 => comb_outputs<='1';next_state<=s10; when s10 => comb_outputs<='0';next_state<=s11; when s11 => comb_outputs<='1';next_state<=s12; when s12 => comb_outputs<='1';next_state<=s13; when s13 => comb_outputs<='0';next_state<=s14; when s14 => comb_outputs<='1';next_state<=s15; when s15 => comb_outputs<='0';next_state<=s0; end case;end process;end behav;2、序列检测器library ieee;use ieee.std_logic_1164.all;entity s_machine is—序列检测电路port(clk,reset:in std_logic;state_inputs:in std_logic;--状态转移控制comb_outputs:out std_logic);检测结果输出end s_machine;architecture behav of s_machine istype fsm_st is (s0,s1,s2,s3,s4,s5);signal current_state,next_state:fsm_st;beginreg:process(reset,clk)主控时序进程beginif reset ='1'then current_state<=s0;elsif clk='1'and clk'event thencurrent_state<=next_state;end if;end process;com:process(current_state,state_inputs)—主控组合进程begincase current_state iswhen s0 => comb_outputs<='0';if state_inputs='1' then next_state<=s1;else next_state<=s0;end if;when s1 => comb_outputs<='0';if state_inputs='1' then next_state<=s2;else next_state<=s0;end if;when s2 => comb_outputs<='0';if state_inputs='0' then next_state<=s3;else next_state<=s2;end if;when s3 => comb_outputs<='0';if state_inputs='1' then next_state<=s4;else next_state<=s0;end if;when s4 => comb_outputs<='0';if state_inputs='0' then next_state<=s5;else next_state<=s2;end if;when s5 => comb_outputs<='1';--检测到11010输出1 if state_inputs='0' then next_state<=s0;else next_state<=s1;end if;end case;end process;end behav;3、串行输出变并行输出library ieee;use ieee.std_logic_1164.all;entity shift is –串行变并行电路port(clk,load,a:in std_logic;din :out std_logic_vector(7 downto 0));--并行输出end shift;architecture behav of shift isbeginprocess(clk,load,a)variable reg8 :std_logic_vector(7 downto 0);beginif clk'event and clk='1'thenif load='1'then reg8(7 downto 1):=reg8(6 downto 0);--load为1时开始装载reg8(0):=a;end if;end if;din<=reg8;end process;end behav;4、计数器设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY CNTM IS –计数电路PORT (CLK,RST,EN:IN STD_LOGIC;a,b,c:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END CNTM;ARCHITECTURE behav OF CNTM ISsignal a1,b1,c1:std_logic_vector(3 downto 0); BEGINPROCESS (CLK,RST,EN)VARIABLE N :INTEGER RANGE 0 TO 1000;BEGINIF RST ='1' THEN N:=0;ELSIF CLK 'EVENT AND CLK='1' THENIF EN = '1' THENIF N<100 THEN N:=N+1;--设计为100计数ELSE N:=0;END IF;END IF;END IF;a1<=conv_std_logic_vector((N/100),4);b1<=conv_std_logic_vector(((N/10)mod 10),4); c1<=conv_std_logic_vector((N mod 10),4);a<=a1;b<=b1;c<=c1;END PROCESS;实验步骤:1、建立工作库文件和编辑设计文件(1)在D盘新建一个文件夹用来保存工程文件(2)打开QuartusⅡ8.0软件,选择菜单File->New->VHDL File,点击OK后在打开的界面下输入已经设计好的程序。

51单片机实现PWM波占空比可调

51单片机实现PWM波占空比可调单片机实现PWM波占空比可调的方法有很多种,下面将详细介绍一种常见的实现方式。

PWM(脉冲宽度调制)是一种常用的数字信号调制技术,可以通过改变脉冲的高电平时间来控制电平的占空比,从而实现对信号的调节。

在单片机中,可以使用定时器/计数器模块来生成PWM波,并通过改变计数器的值来调整占空比。

以AT89C51单片机为例,以下是实现PWM功能的步骤:1.设置定时器模式:选择合适的定时器模式来生成所需的PWM信号。

AT89C51单片机有定时器/计数器模块,可以选择模式2,该模式下定时器有自动重装载功能,能够方便地实现周期性的PWM波。

3. 设置PWM参数:根据需要调节的占空比,计算出所需的高电平时间和低电平时间。

通常,PWM波的高电平时间与低电平时间之和等于一个周期的时间(定时器的重装载值)。

例如,如果需要一个占空比为60%的PWM波,周期为20ms,则高电平时间为「20ms * 60% = 12ms」,低电平时间为「20ms - 12ms = 8ms」。

4.设置PWM引脚:选择一个合适的IO口作为PWM波的输出引脚,并在程序中设置该引脚为输出模式。

5.编写中断服务程序(ISR):针对定时器溢出中断(TOF)编写中断服务程序。

每当定时器溢出时,PWM波应该翻转输出引脚的电平,以实现所需的占空比。

6.初始化定时器和中断:在程序初始化阶段,将定时器设为所需的模式,设置中断向量表中的对应中断服务函数,并开启定时器中断。

7.主循环中设置占空比:在主循环中,通过改变定时器的初值来实现不同占空比的调节。

将计算得到的高电平时间和低电平时间分别赋值给定时器初值,即可实现占空比的调整。

通过上述步骤,我们可以实现占空比可调的PWM波。

在实际应用中,可以根据需要进行适当的优化和改进,例如增加输入口的设置,使得用户可以通过外部按键或旋钮来实时调整占空比,从而更加灵活地控制PWM波的输出。

总结:通过合适的定时器模式、初值设置和中断服务程序编写,配合适当的IO口配置和占空比计算,我们可以在单片机中实现占空比可调的PWM波。

单片机占空比可调的PWM波形发生器

机电高等专科学校电气工程系微控制器技术课程设计报告设计题目:占空比可调的PWM波形发生器微控制器技术课程设计任务书设计题目:占空比可调的PWM波形发生器设计时间: 2013.10.21——2013.10.27设计任务:在Proteus中画出原理图或使用实物,编制程序,实现以下功能:1、理解PWM的工作原理。

2、编制PWM程序,使用八段发光字符管显示占空比。

3、可与电机连接,驱动电机以不同的转速旋转。

背景资料:1、单片机原理与应用2、检测技术3、计算机原理与接口技术进度安排:1、第一天,领取题目,熟悉设计容,分解设计步骤和任务;2、第2天,规划设计软硬件,编制程序流程、绘制硬件电路。

3、第3天,动手制作硬件电路,或编写软件,并调试。

4、第4天,中期检查,书写设计报告。

5、第5天,提交设计报告,整理设计实物,等待答辩。

6、第6天,设计答辩。

题目:占空比可调的PWM波形发生器一、设计目的掌握PWM的工作原理;学会编制PWM程序,使用八段发光字符管显示占空比;并与电机连接,驱动电机以不同的转速旋转。

二、设计思路直流电机PWM控制系统的主要功能包括:实现对直流电机转速的调整,能够很方便的实现电机的智能控制。

主体电路:即直流电机PWM控制模块。

这部分电路主要由AT89C51单片机的I/O端口、定时计数器、外部中断扩展等调整直流电机的转速,能够很方便的实现电机的智能控制。

其间是通过AT89C51单片机产生脉宽可调的脉冲信号并输入到L298驱动芯片来控制直流电机工作的。

该直流电机PWM控制系统由以下电路模块组成:设计输入部分:这一模块主要是利用带中断的独立式键盘来实现对直流电机的加速、减速控制。

设计控制部分:主要由AT89C51单片机的外部中断扩展电路组成。

直流电机PWM控制实现部分主要由一些二极管、电机和L298直流电机驱动模块组成。

设计显示部分: LED数码显示部分,实现对PWM脉宽调制占空比的实时显示。

三、方案设计系统框架设计总体设计方案的硬件部分详细框图如图一所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验2 占空比可调的PWM信号发生器

一、实验任务

基本部分:

(1)用51单片机设计一个周期固定且占空比可调的PWM信号发生器。

(2)参数要求:

a、信号周期为20ms,占空比范围1%-100%可调;

b、用两个按键分别调整增量或减量;增量级别分为±1%和±5%两档可调,

且要求可用按键选择;

c、要求用两位LED数码管实时显示当前的占空比;

d、51单片机晶振频率为12MHz。

扩展部分:

(1)在基本部分设计的电路中,为输出的PWM信号增加光耦隔离输出电路;(2)为占空比调整过程增加超界声光报警电路;

(3)可否改为脉宽固定而周期可改变的PWM信号发生器(简略说明,不要求设计编程)。

二、实验要求

1、在PROTEUS中画出硬件设计图(AT89C51、12MHz晶振震荡电路、复位电路、

按键调整电路、LED数码管显示电路、扩展部分电路)。

2、按任务要求用汇编或C编写程序并编译通过。

3、在PROTEUS下仿真通过。

三、报告要求

1、任务分析、实现方案和程序流程图;

2、硬件电路图;

3、全部程序清单;

4、打印出实验报告。