七段数码管显示十进制数字 (10)

2022金华市《电子技术基础》模拟卷3

2022金华市《电子技术根底》模拟卷22022金华市中职会考《电子技术根底》模拟卷武义职校班级______姓名______学号______?填空题〔每空1分,共30分〕1.晶体二极管具有___ _______,硅二极管的死区电压约为______V。

2.在选择整流二极管时我们主要考虑参数是:最大整流电流和_____________。

3.按内部结构的不同,三极管可分为型和型。

三极管的三个电极名称分别是、集电极和发射极。

4.三极管电流放大的实质____ ____的微小变化控制较大的__ ____电流变化。

5.放大器无信号输入时的直流工作状态叫_________,要使放大器不失真地将电信号放大,须建立适宜的______ ______。

6.多级放大器有三种耦合方式,即阻容耦合,__ __耦合和_ _耦合。

7.放大器的_____________的全部或局部通过某种方式回送到输入端,这局部信号叫反应信号。

根据反应的极性来分,可分为_______反应和反应。

8.按照逻辑功能和电路组成的不同,数字电路可以分成_________电路和_______电路两大类。

9.根本的逻辑门电路有________、________、________三种。

10.A·0=_______ A+ā=________ A+AB= 11.8421BCD码为0101它代表的十进制数__________。

12.组合逻辑电路的特点是任何时刻的输出状态,直接由当时的所决定,也就是说,组合逻辑电路不具有功能。

?三极管作为开关使用时,它是工作在、两种状态下。

14.D触发器具有置0、置1、保持和功能。

15.一个七段数码管显示器,输入为高电平时数码管发光,那么当abcdefg=1101101时,显示的十进制数为。

二、是非题〔每题1分,共10分〕? 单级共射放大器接上负载后,电压放大倍数将增大。

-----------------------( ) ? 稳压管、整流管都工作在正向导通状态。

共阳极七段数码管真值表

共阳极七段数码管真值表共阳极七段数码管是一种常见的电子显示器件,它由七个段码组成,可以显示0-9的数字以及一些其他字符。

下面是共阳极七段数码管的真值表,包含七个段码a、b、c、d、e、f、g。

1. 段码a:* 数字0:0x3F(二进制:00111111)* 数字1:0x06(二进制:00000110)* 数字2:0x5B(二进制:01011011)* 数字3:0x4F(二进制:01001111)* 数字4:0x66(二进制:01100110)* 数字5:0x6D(二进制:01101101)* 数字6:0x7D(二进制:01111101)* 数字7:0x07(二进制:00000111)* 灭零:0x7C(二进制:01111100)2. 段码b:* 数字0:0x39(二进制:00111001)* 数字1:0x5F(二进制:01011111)* 数字2:0x49(二进制:01001001)* 数字3:0x65(二进制:01100101)* 数字4:0x77(二进制:01110111)* 数字5:0x79(二进制:01111111)* 数字6:0x3D(二进制:00111101)* 数字7:没有对应的编码。

可以通过特定的编程实现显示。

3. 段码c:* 数字0:没有对应的编码。

可以通过特定的编程实现显示。

* 数字8以下与段码b相同。

4. 段码d、e、f、g与b相同。

请注意,这里提供的编码是基于常见的共阳极七段数码管编码,不同型号或品牌的数码管可能会有不同的编码。

此外,对于大于9的数字或特殊字符,可能需要通过特定的编程来实现显示。

七段数码管设计电路

EDA基础及应用实验项目报告项目题目:七段数码管显示电路设计姓名:胡小琴院系:电子信息工程学院专业:电子信息工程(对口高职)学号: 201315294127指导教师:徐正坤综合成绩:完成时间: 2015年5月22日一、项目实验内容摘要1、设计一个共阴7段数码管控制接口,要求:在时钟信号的控制下,使8位数码管动态刷新显示0—9。

2、设计一个基本功能十进制计数器,实现十进制计数器输出的动态显示。

二、项目实验源代码程序1LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY countbasic ISPORT(CLK:IN STD_LOGIC;DOUT:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT:OUT STD_LOGIC);END countbasic ;ARCHITECTURE behav OF countbasic ISBEGINPROCESS(CLK)V ARIABLE Q:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF CLK'EVENT AND CLK='1' THENIF Q<9 THEN Q:=Q+1;ELSE Q:=(OTHERS=>'0');END IF;END IF;IF Q="1001" THEN COUT<='1';ELSE COUT<='0';END IF;DOUT<=Q;END PROCESS;END behav;程序2 ENTITY countbasic_vhd_tst ISEND countbasic_vhd_tst;ARCHITECTURE countbasic_arch OF countbasic_vhd_tst IS -- constants-- signalsSIGNAL CLK : STD_LOGIC;SIGNAL COUT : STD_LOGIC;SIGNAL DOUT : STD_LOGIC_VECTOR(3 DOWNTO 0); constant clk_cycle : time := 100 ns;COMPONENT countbasicPORT (CLK : IN STD_LOGIC;COUT : OUT STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;BEGINi1 : countbasicPORT MAP (-- list connections between master ports and signalsCLK => CLK,COUT => COUT,DOUT => DOUT);processbeginclk <= '1';wait for clk_cycle;clk <= '0';wait for clk_cycle;end process;END countbasic_arch;程序3LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY Seg7_Dsp isPORT(CP : IN STD_LOGIC; -- CLOCKSEGOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); -- SEG7 Display O/PSELOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); -- Select SEG7 O/PNUMOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); -- Number Display Signal OUTNUM : IN STD_LOGIC_VECTOR( 3 DOWNTO 0); -- Number Display Signal INM : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END Seg7_Dsp;ARCHITECTURE a OF Seg7_Dsp ISSIGNAL SEG : STD_LOGIC_VECTOR( 7 DOWNTO 0); -- SEG7 Display Signal SIGNAL SEL : STD_LOGIC_VECTOR( 7 DOWNTO 0); -- Select SEG7 Signal BEGINConnection : BlockBeginM <= "0010";SELOUT <= SEL; -- Seg7 Disp Selection SEGOUT(7 DOWNTO 0) <= SEG; -- Seven Segment Display NUMOUT <= NUM;End Block Connection;Free_Counter : Block -- 计数器-- 产生扫描信号Signal Q : STD_LOGIC_VECTOR(24 DOWNTO 0);Signal S : STD_LOGIC_VECTOR(2 DOWNTO 0);BeginPROCESS (CP) -- 计数器计数BeginIF CP'Event AND CP='1' thenQ <= Q+1;END IF;END PROCESS;S <= Q(15 DOWNTO 13); --about 300 Hz--扫描信号SEL <= "11111110" WHEN S=0 ELSE"11111101" WHEN S=1 ELSE"11111011" WHEN S=2 ELSE"11110111" WHEN S=3 ELSE"11101111" WHEN S=4 ELSE"11011111" WHEN S=5 ELSE"10111111" WHEN S=6 ELSE"01111111" WHEN S=7 ELSE"11111111";End Block Free_Counter;SEVEN_SEGMENT : Block -- Binary Code -> Segment 7 CodeBegin--SEG <= "00111111"WHEN NUM = 0 ELSE"00000110"WHEN NUM = 1 ELSE"01011011"WHEN NUM = 2 ELSE"01001111"WHEN NUM = 3 ELSE"01100110"WHEN NUM = 4 ELSE"01101101"WHEN NUM = 5 ELSE"01111101"WHEN NUM = 6 ELSE"00000111"WHEN NUM = 7 ELSE"01111111"WHEN NUM = 8 ELSE"01101111"WHEN NUM = 9 ELSE"01110111"WHEN NUM = 10 ELSE"01111100"WHEN NUM = 11 ELSE"00111001"WHEN NUM = 12 ELSE"01011110"WHEN NUM = 13 ELSE"01111001"WHEN NUM = 14 ELSE"01110001"WHEN NUM = 15 ELSE"00000000";End Block SEVEN_SEGMENT;END a;三、项目实验工具软件项目试验工具:EL-SOPC400试验箱、主芯片:EP4CE22F17C8、计算机与QUARTUS Ⅱ软件四、实验步骤1、建立项目文件以及VHDL文件同前几个实验一样2、将前两个程序按照一点的步骤设置然后进行仿真3、将三个实验添加到项目中来并设置为顶层文件4、建立顶层图,选择“File→New→Block Diorgram Schematic File”按OK 就可以建立一个顶层图,我们在把他进行保存,名字为默认的文件名,并将“Add file to current project”选项选中,让他加入到工程中去。

一个8421码十进制计数器(异步置数)及七段数码管显示系统

一个8421码十进制计数器(异步置数)及七段数码管显示系统一个8421码十进制计数器(异步置数)及七段数码管显示系统LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter10 ISPORT( clk: IN STD_LOGIC;load: IN STD_LOGIC;din: IN STD_LOGIC_VECTOR(3 DOWNTO 0);qout: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);c: OUT STD_LOGIC);END counter10;ARCHITECTURE art2 OF counter10 ISSIGNAL temp: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk,load,din)BEGINIF(load='0') THENtemp<=din;ELSIF(clk'EVENT AND clk='1') THENIF(temp="1001") THENtemp<="0000";ELSEtemp<=temp+1;END IF;END IF;END PROCESS;qout<=temp;c<='1' WHEN temp="1001" ELSE'0';END art2;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY bcd ISPORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0); Y:OUT STD_LOGIC_VECTOR(6 DOWNTO 0) );END bcd;ARCHITECTURE art1 OF bcd ISBEGINY<="1111110" WHEN A="0000" ELSE "0110000" WHEN A="0001" ELSE "1101101" WHEN A="0010" ELSE "1111001" WHEN A="0011" ELSE "0110011" WHEN A="0100" ELSE "1011011" WHEN A="0101" ELSE "0011111" WHEN A="0110" ELSE "1110000" WHEN A="0111" ELSE "1111111" WHEN A="1000" ELSE "1110011" WHEN A="1001" ELSE "0000000";END art1;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter10_bcd ISPORT(clkin,clrin: IN STD_LOGIC;yout: OUT STD_LOGIC_VECTOR(6 DOWNTO 0);d: IN STD_LOGIC_VECTOR(3 DOWNTO 0));END counter10_bcd;ARCHITECTURE art3 OF counter10_bcd IS COMPONENT counter10PORT( clk: IN STD_LOGIC;load: IN STD_LOGIC;din: IN STD_LOGIC_VECTOR(3 DOWNTO 0);qout: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);c: OUT STD_LOGIC);END COMPONENT;COMPONENT bcdPORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);Y:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END COMPONENT;SIGNAL q: STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL c1: STD_LOGIC;BEGINu1:counter10 PORTMAP(clk=>clkin,load=>clrin,din=>d,qout=>q,c=>c1);u2:bcd PORT MAP(A=>q,Y=>yout);END art3;。

数字电子技术课程设计题目

数电课设说明1.单人单题,每个题目在同一班不能超过5人选择!为了避免重复过多,请填写两个心仪的题目。

2.如果这些题目都进不了尊驾法眼,请自行设计题目名称、题目要求并提交给老师,审核通过后也可以正式进场施工。

3.建议先用Multisim或Proteus仿真测试再制作。

1.智力竞赛抢答装置的设计(1)基本功能①4名选手编号为:1,2,3,4。

各有一个抢答按钮,按钮的编号与选手的编号对应;②给主持人设置一个控制按钮,用来控制系统清零(抢答显示数码管灭灯)和抢答的开始;③抢答器具有数据锁存和显示的功能。

抢答开始后,若有选手按动抢答按钮,该选手编号立即锁存,并在抢答显示器上显示该编号,同时给出音响提示,封锁输入编码电路,禁止其他选手抢答。

抢答选手的编号一直保持到主持人将系统清零为止;④抢答器具有定时(9秒)抢答的功能。

当主持人按下开始按钮后,定时器开始倒计时,定时显示器显示倒计时间,若无人抢答,倒计时结束时,扬声器响,音响持续0.5秒。

参赛选手在设定时间(9秒)内抢答有效,抢答成功,扬声器响,音响持续0.5秒,同时定时器停止倒计时,抢答显示器上显示选手的编号,定时显示器上显示剩余抢答时间,并保持到主持人将系统清零为止;⑤如果抢答定时已到,却没有选手抢答时,本次抢答无效。

系统扬声器报警(音响持续0.5秒),并封锁输入编码电路,禁止选手超时后抢答,时间显示器显示0。

(2)设计成果要求①利用集成芯片、分立元件制作线路板,实现有关电路功能;②设计报告一份。

(3)主要器件74LS175、74LS20、74LS00、CC40192、CC4511、CC40106、555、数码管、蜂鸣器2.多功能数字钟的设计(1)基本功能①用七段LED数码管以十进制显示“时”、“分”、“秒”;②计时计数器用24进制计时电路;③可手动校时,能分别进行时、分的校正;④整点报时。

(2)设计成果要求①利用集成芯片、分立元件制作线路板,实现有关电路功能;②设计报告一份。

七段数码管动态显示控制

实验二七段数码管动态显示控制一、实验目的利用AT89S52和使用两位数码管显示器,循环显示两位数00-99。

其中P2.0和P2.1端口分别控制数码管的个位和十位的供电,当相应的端口变成低电平时,驱动相应的三极管会导通,+5V通过驱动三极管给数码管相应的位供电,这时只要P3口送出数字的显示代码,数码管就能正常显示数字。

二、实验要求1、使用两位数码管显示器,循环显示两位数00-99;2、具有电源开关和指示灯,有复位键;3、数码管动态显示,即扫描方式,每一位每间隔一段时间扫描一次。

字符的亮度及清晰度与每位点亮的停留时间和每位显示的时间内轮换导通次数有关。

三、实验电路四、实验器材AT89S52;动态扫描显示;共阳极数码管;电阻五、实验原理说明图1 AT89S52引脚图图2 共阳极七段数码管引脚图1AT89S52引脚图,说明如下:按照功能,AT89S52的引脚可分为主电源、外接晶体振荡或振荡器、多功能I/O 口、控制和复位等。

1.多功能I/O口AT89S52共有四个8位的并行I/O口:P0、P1、P2、P3端口,对应的引脚分别是P0.0 ~ P0.7,P1.0 ~ P1.7,P2.0 ~ P2.7,P3.0 ~ P3.7,共32根I/O线。

每根线可以单独用作输入或输出。

①P0端口,该口是一个8位漏极开路的双向I/O口。

在作为输出口时,每根引脚可以带动8个TTL输入负载。

当把“1”写入P0时,则它的引脚可用作高阻抗输入。

当对外部程序或数据存储器进行存取时,P0可用作多路复用的低字节地址/数据总线,在该模式,P0口拥有内部上拉电阻。

在对Flash存储器进行编程时,P0用于接收代码字节;在校验时,则输出代码字节;此时需要外加上拉电阻。

②P1端口,该口是带有内部上拉电阻的8位双向I/O端口,P1口的输出缓冲器可驱动(吸收或输出电流方式)4个TTL输入。

对端口写“1”时,通过内部的上拉电阻把端口拉到高电位,此时可用作输入口。

七段数码管显示十进制数字 (2)

Led灯显示实验

1.实验目的:

通过相关的逻辑电路在proteus上实现单片的led灯的显示;

2.实验内容:

选取相关工具,在仿真环境下配置电路图如图一。

当按上面那个开关时,led灯显示0。

按下面那一排开关的时候从右至左依次是1,2,3,4,5,6,7,8,9。

当然不按的时候灯是灭的。

如图一所示,当不按的时候,1,2,3,4,5,6,7,8,9开关可以看成接高电平,与一相连的那个非与门的另一端接地,所以是0。

通过9个非与门后B1端输入0,所以灭零。

0开关也没按所以也是0.当按0时,B1端有高电平,配合九个输入显示0.当按1开关时,一号非与门两个输入端为0,自然输出1给B1,所以这个时候U1工作。

根据九个输入显示相应的1.余下的2至9开关原理一样。

3.实验过程:

图一

各数字显示如下:

1

2

3,4,5,6,7,8,9由于原理一样所以图略。

4.实验总结:

本次实验没有采用教员上课所讲授的那种方法,这是我在选工具的过程中意外发现的一个非与门工具,然后联想到了led灯显示,所以想做得不一样,就用了此种方法。

这次实验的难

点还是0的显示。

实验2:8255七段数码管静动态显示

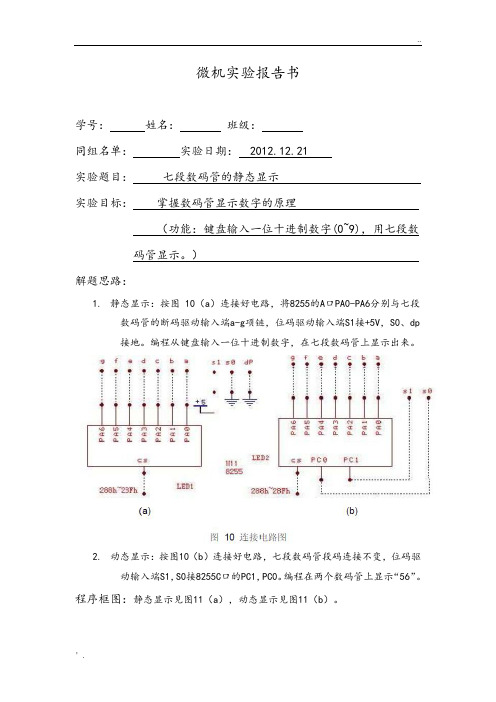

微机实验报告书学号:姓名:班级:同组名单:实验日期: 2012.12.21实验题目:七段数码管的静态显示实验目标:掌握数码管显示数字的原理(功能:键盘输入一位十进制数字(0~9),用七段数码管显示。

)解题思路:1.静态显示:按图 10(a)连接好电路,将8255的A口PA0-PA6分别与七段数码管的断码驱动输入端a-g项链,位码驱动输入端S1接+5V,S0、dp接地。

编程从键盘输入一位十进制数字,在七段数码管上显示出来。

2.动态显示:按图10(b)连接好电路,七段数码管段码连接不变,位码驱动输入端S1,S0接8255C口的PC1,PC0。

编程在两个数码管上显示“56”。

程序框图:静态显示见图11(a),动态显示见图11(b)。

关键问题分析(静态显示):1、按键判断和程序结束判断按键来说,由于程序中必须输入数字,所以没有必要对是否按键进行判断,只需要判断按键是否在0-9之间即可。

用以下程序即可:cmp al,'0'jl exit ; jl,条件转移指令,即在小于时转移cmp al,'9'jg exit ;jg, 条件转移指令,即在大于时转移程序中还要用到“cmp”即比较指令,用来比较输入数与0、9的大小关系。

程序结束:如若输入的数字小于0或者大于9,必须直接跳出程序,即结束指令必须单独占用一个程序段,这样,程序顺序执行完毕也可以顺利返回DOS。

2、七段码显示。

实验指导书中给出了七段码的字型代码。

这样一来,七段码的显示只需要用换码指令“XLAT”便可以轻松实现。

前提是必须将七段码字型编成数码表以字符串的形式写进程序中。

3、数字键ASCII码与数值间的转换。

因为0的ASCII码为30H,所以数字键ASCII码与数值间的转换时只需减去30H即可,可用下列语句实现:sub al,30h程序清单:静态显示:data segmentioport equ 0c800h-0280hio8255a equ ioport+288hio8255b equ ioport+28bhled db 3fh,06h,5bh,4fh,66h,6dh,7dh,07h,7fh,6fhmesg1 db 0dh,0ah,'Input a num (0--9h):',0dh,0ah,'$'data endscode segmentassume cs:code,ds:datastart: mov ax,datamov ds,axmov dx,io8255b ;使8255的A口为输出方式mov al,80h ;10000000B,控制字PA以方式0输出out dx,alzby: mov dx,offset mesg1 ;显示提示信息mov ah,09hint 21hmov ah,01 ;从键盘接收字符int 21hcmp al,'0' ;是否小于0jl exit ;如若小于0,则跳转到exit退出程序cmp al,'9' ;是否大于9jg exit ; 如若大于9,则跳转到exit退出程序sub al,30h ;将所得字符的ASCII码减30H,数字键ascii码同数值转换mov bx,offset led ;bx为数码表的起始地址xlat ;求出相应的段码mov dx,io8255a ;从8255的A口输出out dx,aljmp zby ;转zbyexit: mov ah,4ch ;返回DOSint 21hcode endsend start动态显示:data segmentioport equ 0c800h-0280hio8255a equ ioport+28ahio8255b equ ioport+28bhio8255c equ ioport+288hled db 3fh,06h,5bh,4fh,66h,6dh,7dh,07h,7fh,6fh ;段码buffer1 db 5,6 ;存放要显示的个位和十位bz dw ? ;位码data endscode segmentassume cs:code,ds:datastart: mov ax,datamov ds,axmov dx,io8255b ;将8255设为A口输出mov al,80h ;10000000B,控制字PA以方式0输出out dx,almov di,offset buffer1 ;设di为显示缓冲区loop2: mov bh,02zby: mov byte ptr bz,bhpush didec diadd di, bzmov bl,[di] ;bl为要显示的数pop dimov al,0mov dx,io8255aout dx,almov bh,0mov si,offset led ;置led数码表偏移地址为SIadd si,bx ;求出对应的led数码mov al,byte ptr [si]mov dx,io8255c ;自8255A的口输出out dx,almov al,byte ptr bz ;使相应的数码管亮mov dx,io8255aout dx,almov cx,3000delay: loop delay ;延时mov bh,byte ptr bzshr bh,1jnz zbymov dx,0ffhmov ah,06int 21hje loop2 ;有键按下则退出mov dx,io8255amov al,0 ;关掉数码管显示out dx,almov ah,4ch ;返回int 21hcode endsend start运行结果:静态显示:在键盘上输入一个0-9的任意数字,会显示在数码管上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验报告

一、实验题目

有10个开关,编号为0,1,2,3,4,5,6,7,8,9。

设计电路实现某开关闭合时对应显示相应的十进制数字.

二、实验方案设计

该实验分四个主要部分。

一是按键部分,二是将十进制数字编成对应的BCD代码,三是将BCD编码译为七段显示码,四是LED数码管显示。

对应第二、三部分,可以分别选取74LS147和74LS49作为主要器件。

三、四部分的连接:74LS49是集电极开路输出的8421BCD码七段显示译码器。

该译码器的输出为高电平有效,因此适用于连接共阴极数码管。

二、三部分的连接。

由于74LS147输出为低电平有效,而74LS49输入为高电平有效,故在连接这两个器件时应加入反向器,器件型号为74LS04。

连接一、二部分时,因为74LS147只有9个输入端,故先不连接按键“0”,因此直接将按键1~9与74LS147连接即可。

三、实验过程

先连接三、四部分。

具体电路如下所示:

连接二、三部分,电路如图所示:

连接一、二部分,电路如图所示:整体电路如图所示:

于是,一个实现编号为0~9的某开关闭合时对应显示相应的十进制数字的电路完成。

四、实验结果

下图为按键4按下的结果:

下图为按键7均按下的结果:。