7段数码管实验报告

计算机组成原理实验报告

实验一:数字逻辑——交通灯系统设计子实验1:7 段数码管驱动电路设计(1)理解利用真值表的方式设计电路的原理;(2)利用Logisim 真值表自动生成电路的功能,设计一个 7 段数码管显示驱动。

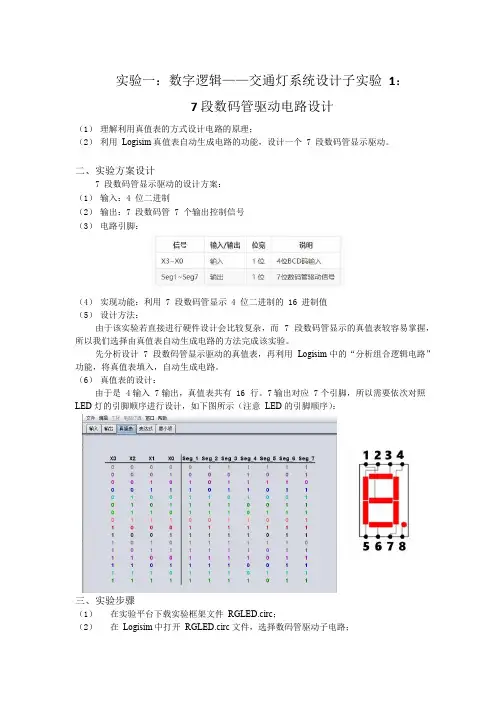

二、实验方案设计7 段数码管显示驱动的设计方案:(1)输入:4 位二进制(2)输出:7 段数码管 7 个输出控制信号(3)电路引脚:(4)实现功能:利用 7 段数码管显示 4 位二进制的 16 进制值(5)设计方法:由于该实验若直接进行硬件设计会比较复杂,而7 段数码管显示的真值表较容易掌握,所以我们选择由真值表自动生成电路的方法完成该实验。

先分析设计 7 段数码管显示驱动的真值表,再利用Logisim 中的“分析组合逻辑电路”功能,将真值表填入,自动生成电路。

(6)真值表的设计:由于是 4输入 7输出,真值表共有 16 行。

7输出对应 7个引脚,所以需要依次对照LED 灯的引脚顺序进行设计,如下图所示(注意LED 的引脚顺序):三、实验步骤(1)在实验平台下载实验框架文件RGLED.circ;(2)在Logisim 中打开RGLED.circ 文件,选择数码管驱动子电路;(3)点击“工程”中的“分析组合逻辑电路”功能,先构建4输入和7输出,再在“真值表”中,将已设计好的真值表的所有数值仔细对照着填入表格中,确认无误后点击“生成电路”,自动生成的电路如下图所示:(4)将子电路封装为如下形式:(5)进行电路测试:·自动测试在数码管驱动测试子电路中进行测试;·平台评测自动测试结果满足实验要求后,再利用记事本打开RGLED.circ 文件,将所有文字信息复制粘贴到Educoder 平台代码区域,点击评测按钮进行测试。

四、实验结果测试与分析(1)自动测试的部分结果如下:(2)平台测试结果如下:综上,本实验测试结果为通过,无故障显示。

本实验的关键点在于:在设计时需要格外注重LED 灯的引脚顺序,保证0-9 数字显示的正确性,设计出正确的真值表。

七段数码管显示实验报告

七段数码管显示实验报告实验目的:本实验的目的是通过控制7段数码管的亮灭状态来显示不同的数字和字母。

实验原理:7段数码管常用于显示数字和字母,每个数码管由7个LED灯组成,分别表示A、B、C、D、E、F、G等7个段。

通过控制这些LED灯的亮灭状态,就可以显示不同的数字和字母。

在实际应用中,通常需要使用一个译码器来根据输入的数字或字母输出相应的控制信号。

常用的译码器有7447、DM9368等。

这些译码器通常都是BCD码到7段数码管的译码器。

在本实验中,我们将使用7447译码器来控制7段数码管的亮灭状态。

7447译码器具有4个输入线和7个输出线,每个输入线上的BCD码可以转换成相应的控制信号,用于控制数码管的7个LED 灯。

实验材料:1.7段数码管2.7447译码器3.电路板4.电压源5.连接线实验步骤:1.将7447译码器插入电路板上相应的插槽中,并将数码管连接到电路板上。

2.将电压源连接到电路板上,并调节电压和电流值。

3.根据所需显示的数字或字母,设置相应的BCD码输入信号。

4.打开电源,观察数码管是否能够正确显示。

实验结果:通过本实验,我们可以成功控制7段数码管的亮灭状态,实现了数字和字母的显示。

同时,我们也了解了7447译码器的原理和使用方法。

实验小结:本实验是电子技术的基础实验之一,通过实验我们深入了解了7段数码管和7447译码器的原理和应用,同时也锻炼了我们的动手能力和实验技能。

在实际应用中,7段数码管和译码器常常被用于数字显示、计数器、时钟、温度计等电子设备中,具有广泛的应用前景。

数码管动态显示实验报告

数码管动态显示实验报告1.实验目的:本实验旨在通过使用单片机控制数码管的动态显示,了解数码管的原理和使用方法,加深对单片机控制的理解。

2.实验原理:数码管是由许多发光二极管(LED)组成的,每个数码管有7个发光二极管组成7段,再加上一个小数点(或8段数码管),通过控制每个发光二极管的亮灭状态,可以显示出数字、字母等字符。

本实验使用的是共阴极数码管,在通常情况下,数码管引脚为低电平时亮灯,为高电平时灭灯。

3.实验器材:-STC89C52单片机-共阴极数码管-电阻-面包板及连接线-电源4.实验步骤:步骤1:连接电路将数码管的7个引脚分别连接到单片机的7个I/O引脚上,并通过电阻限流。

连接电路后,确认连接无误。

步骤2:编写程序使用C语言编写程序,实现数码管的动态显示。

可以使用延时函数和位操作函数控制数码管的亮灭,通过改变每个数码管引脚的高低电平状态,实现显示不同的数字、字母。

步骤4:实验观察与分析观察数码管的显示效果,通过改变程序中的参数,可以实现不同的显示效果。

5.实验结果与分析:经过实验,我们成功实现了数码管的动态显示。

通过编写程序,我们可以实现数码管显示数字、字母等不同的字符。

调整程序中的参数,可以实现不同的动态显示效果,如流水灯、闪烁等。

数码管的动态显示是通过改变每个数码管引脚的高低电平实现的,通过快速改变引脚电平状态的时间间隔,创建了肉眼无法察觉的视觉效果,从而实现了动态显示。

此外,通过实验我们还了解到了单片机控制数码管的原理和方法,加深了对单片机控制的理解。

6.实验总结:通过本实验,我们了解到了数码管的动态显示原理和方法,并通过编写程序,成功实现了数码管的动态显示。

同时,我们还巩固了单片机控制的知识,提高了自己的动手能力和问题解决能力。

在今后的学习和工作中,我们将进一步掌握数码管的使用方法,并能够将其应用于更加复杂的应用场景中,实现更多有趣的功能。

FPGA实验三七段数码管静态与动态显示实验报告

FPGA实验三七段数码管静态与动态显示实验报告实验目的:通过FPGA实现七段数码管的静态与动态显示,在FPGA上可实现对任意数字的显示和计数功能。

实验原理:七段数码管是一种能够显示数字的晶体管数字显示器件,它由七个LED数码管组成,每个数码管分别由a、b、c、d、e、f、g七个LED组成。

通过控制每个LED的亮灭情况,可以对任意数字进行显示。

七段数码管的静态显示是指每个数字的显示都是固定的,而动态显示则是通过快速地刷新七段数码管的显示,使得数字像是在变化。

在FPGA 中,可以通过时钟信号和计数器实现刷新,从而实现数字的动态显示。

实验过程:首先,将FPGA和七段数码管连接,在FPGA上选择适当的引脚连接到a、b、c、d、e、f、g七个数码管。

在FPGA中创建工程,并添加适当的引脚约束,以实现与七段数码管的连接。

然后,根据需要选择静态或动态显示。

静态显示:静态显示的原理是通过直接控制每个LED的亮灭情况,使得每个数字都可以被显示出来。

首先,需要定义每个数字对应的LED的状态(亮灭),例如数字0对应的LED状态可能为(1,1,1,1,1,1,0)等。

然后,通过FPGA的逻辑电路实现对应数字的显示。

动态显示:动态显示的原理是通过快速地刷新显示,使得数字在若干个数码管中切换,从而造成数字变化的视觉效果。

这里需要使用时钟信号和计数器来控制刷新。

首先,需要设计一个计数器,它的计数范围应该与显示数字的个数相同。

然后,通过时钟信号让计数器开始计数,并根据计数器的值选择对应的数字显示在七段数码管上。

通过控制计数器的计数速度和刷新频率,可以实现数字的动态显示。

实验结果:经过实验,我们成功地实现了七段数码管的静态显示和动态显示。

在静态显示中,我们可以通过FPGA的逻辑电路对七段数码管的每个LED进行控制,从而实现任意数字的显示。

在动态显示中,我们通过时钟信号和计数器实现了刷新功能,使得数字在七段数码管中快速地切换,从而呈现出动态的显示效果。

实验四 LED数码管显示实验报告

实验名称 LED数码管显示实验指导教师曹丹华专业班级光电1202班姓名陈敬人学号联系电话一、任务要求实验目的:理解LED七段数码管的显示控制原理,掌握数码管与MCU的接口技术,能够编写数码管显示驱动程序;熟悉接口程序调试方法。

实验内容:1.基础部分:利用C8051F310单片机控制数码管显示器。

利用末位数码管循环显示数字0-F,显示切换频率为1Hz。

2.提高部分:在数码管上显示0→199计数,计数间隔为0.5秒。

二、设计思路1.基础部分C8051F310单片机片上晶振为24.5MHz,采用8分频后为3.0625MHz ,输入时钟信号为48个机器周期,T1采用定时器工作方式1,单次定时最长可达1.027s,可以实现1s定时要求。

定时采用软件查询工作方式,利用JNB TF0, HERE实现。

置P0.6和P0.7端口为0,位选信号选定末位数码管。

通过MOVC A, @A+DPTR指令,利用顺序查表法取出显示段码数据。

寄存器R0自增1,并赋给A以取出下一个显示段码数据。

为减短代码长度,利用CJNE指令实现循环结构。

当寄存器R0增至0FH后,跳转至开头,重新开始下一轮显示。

2.提高部分定时方式及查表方式同基础部分,由于要实现三个数码管同时显示,因此采用动态扫描显示法。

三、资源分配1.基础部分P0.6: 位选信号端口P0.7:位选信号端口P1:输出段码数据R0:存放显示数据DPTR:指向段码数据表首 2.提高部分P0.6:位选信号端口P0.7:位选信号端口R0:存放个位显示数据 R5:存放十位显示数据 R6:存放百位显示数据 P1:输出段码数据DPTR: 指向段码数据表首四、流程图1.基础部分2.提高部分五、源代码(含文件头说明、语句行注释)1.基础部分;******************基础部分源代码***************************;Filename: test.asm;Decription: 末位数码管循环显示数字0-F,显示切换频率为1Hz。

十六进制7段数码显示译码器设计实验报告

十六进制7段数码显示译码器设计实验报告实验报告:十六进制7段数码显示译码器设计一、实验目的本实验的主要目的是设计一种用于将十六进制数码转化为七段显示的译码器电路。

通过这个实验,我们可以学习和了解数字电路的工作原理、数码管的控制方式以及七段数码的译码方法。

二、实验原理本实验所用到的数码管为共阳数码管,它由7个发光二极管组成,其中的每一个发光二极管称为一个段。

这七个段依次为a、b、c、d、e、f和g,它们分别对应数码管上的abcdefg七个引脚。

当一些引脚输出高电平时,相应的段就会被点亮,从而显示出特定的字符。

为了实现将十六进制数码转化为七段显示的功能,我们需要设计一个译码器电路。

译码器电路的输入为十六进制数码,输出为七段信号,用于控制数码管的每个段的亮灭情况。

为了简化设计,我们可以采用CMOS数字集成电路74LS47来实现译码器电路。

该集成电路内部集成了BCD转七段译码器,可以将二进制代码转化为七段数码显示所需要的信号。

它的输入为四个二进制输入端口A、B、C和D,输出为七个段芯片(a、b、c、d、e、f和g)的控制信号。

三、实验步骤1.首先,根据74LS47的真值表,确定译码器的输入和输出。

2.根据真值表,画出逻辑图,确定硬件电路的连接方式。

3.按照逻辑图和电路连接方式,进行硬件电路的布线。

4.按照实验仪器的操作说明,对电路进行调试和测试。

5.将输入端口连接至外部的十六进制信号源,观察输出端口的数据是否正确。

6.验证电路的正确性和稳定性,如果出现问题,进行排除和修复。

四、实验结果经过实验,我们成功地设计并实现了一个十六进制7段数码显示译码器电路。

当输入端口接收到一个十六进制信号时,通过电路的处理和转换,将其转化为了相应的七段信号,用于控制数码管的每个段的亮灭情况。

通过实验观察,我们发现电路的输出结果与预期一致,且工作稳定。

五、实验总结通过这个实验,我们对于数字电路的工作原理和数码管的控制方式有了更深的了解。

微机原理实验报告-实验三-七段数码管.doc

实验三七段数码管一、实验目的:进一步熟悉8255,掌握数码管显示数字的原理二、实验原理:1、实验台上的七段数码管为共阴型,段码采用同相驱动,输入端加高电平,选中的数码管亮,位码加反相驱动器,位码输入端高电平选中。

2、七段数码管的字形码:3、在实验 2 中加入键盘是否有输入判断,如有则去读取键盘输入数据,并加入提示信息,比如“输入十位数”,“输入个位数”,从键盘读入的数据放入十位和个位数据定义区,取代要显示的数据。

4、只需要添加两位变量作为缓存,一个记录键盘输入的值,一个记录循环减 1 的结果,将其通过数码管显示出来,减至0 时重载键盘输入的值。

三、实验步骤:静态显示:将8255 的 A 口 PA0~PA6分别与气短数码管的段码驱动输入端A~G相连,位码驱动输入端S1 接 +5V(选中), S0、 DP接地(关闭)。

动态显示:七段数码管段码不变,位码驱动输入端S1,S0 接 8255 C 口的 PC1,PC0。

8253 的接法参考第二次实验的接法,CLK0接入 1MHz, CLK1接 8255 的 PC7。

1、在两个数码管上显示两位数字,要求延时应用8253 硬件延时2、可以改变数码管显示数字,从键盘读入两位数字,并在数码管显示出来。

3、对输入数据进行倒计时计数,时间显示在数码管上,计到0 重新开始。

四、流程图:开始对 8255 进行初设置 8255C 口输从键盘读入数据Y根据十位获得段码,延时N根据个位获得段码,按键延时N循环显示这Y要输出的数重新载入输Y要输出的数据减 1五、实验结果:实验结果如预期一致,可以键盘输入倒计时的值,时间显示在数码管上,计数到0 重新计数。

六、程序代码:;******************************************;*数码管显示对键盘输入数据进行倒计时计数*;******************************************data segmentio8255a equ 288hio8255c equ 28ahio8255_mode equ 28bhio8253a equ 280hio8253b equ 281hio8253c equ 282hmesg1 db 0dh,0ah,'Input a num (00--99) for high position,other key isexit:',0dh,0ah,'$'mesg2 db 0dh,0ah,'Input a num (00--99) for low position,other key isexit:',0dh,0ah,'$'led db 3fh,06h,5bh,4fh,66h,6dh,7dh,07h,7fh,6fh; 段码buffer db , ; 存放要显示的个位和十位buffer1 db , ; 存放临时的个位和十位用于减一bz dw;data endscode segmentassume cs:code,ds:datastart:位码mov ax,datamov ds,axmov dx,io8255_mode ; 将8255 的A 口为输出mov ax,88hout dx,almov dx,offset mesg1mov ah,09hint 21h; 显示提示信息mov ah,01int 21h; 从键盘接收十位字符cmp al,'0' jl exit ; 是否小于0 ; 若是则退出cmp al,'9' jg exit sub al,30h ; 是否大于9 ; 若是则退出mov buffer,almov dx,offset mesg2 mov ah,09hint 21hmov ah,01hint 21h; 将输入的十位数存入指定地址; 显示提示信息cmp al,'0'jl exitcmp al,'9'jg exitsub al,30h; 判断方法同十位mov buffer+1,aljmp reset; 将输入的个位数存入指定地址exit:mov ah,4chint 21hreset:mov al,buffermov buffer1,almov al,buffer+1mov buffer1+1,al; 返回mov di,offset buffer1loop1:call time; 取得显示缓冲区的地址loop2:mov bh,02h ; 数码管循环显示部分lll:mov byte ptr bz,bhpush didec diadd di, bzmov bl,[di] ;bl 为要显示的数pop dimov al,0mov dx,io8255cout dx,almov bh,0mov si,offset led ; 置led 数码表偏移地址为SI add si,bx ; 求出对应的led 数码mov al,byte ptr [si]mov dx,io8255a ; 自8255A 的口输出out dx,almov al,byte ptr bz; 使相应的数码管亮mov dx,io8255cout dx,almov cx,3000delay:loop delay; 延时mov bh,byte ptr bzshr bh,1jnz lllmov dx,io8255cin al,dxtest al,80hjnz setjmp loop2set:test buffer1+1,0fhjz set1dec buffer1+1jmp loop1set1:test buffer1,0fhjz resetdec buffer1mov buffer1+1,09hjmp loop1time proc near ; 定时一秒的子程序mov dx,io8253c ; 向 8253 写控制字mov al,37h ; 使0 通道为工作方式 3 out dx,almov ax,1000h ; 循环计数初值1000 mov dx,io8253aout dx,al; 先写低字节mov al,ahout dx,al; 后写高字节mov dx,io8253cmov al,71h ; 设8253 通道 1 工作方式0out dx,almov ax,1000h ; 循环计数初值1000mov dx,io8253bout dx,al ; 先写低字节mov al,ahout dx,al; 后写高字节rettime endpcode endsend start七、实验总结:本次实验需要结合上次实验的知识,应用 8253 硬件延时,因此增加了些许难度,代码的修改也不少。

实验报告模板:实验二7段数码显示译码器

实验二7段数码显示译码器【实验目的】1.设计七段显示译码器,并在实验板上验证2.学习V erilog HDL文本文件进行逻辑设计输入;3.学习设计仿真工具的使用方法;【实验内容】1.实现BCD/七段显示译码器的“Verilog ”语言设计。

说明:7段显示译码器的输入为:IN0…IN3共5根,7段译码器的逻辑表同学自行设计,要求实现功能为:输入“0…15 ”(二进制),输出“0…9…F ”(显示数码),输出结果应在数码管(共阴)上显示出来。

2.使用工具为译码器建立一个元件符号3.设计仿真文件,进行验证。

4.编程下载并在实验箱上进行验证。

【实验原理】7段数码是纯组合电路。

通常的小规模专用IC,如74或4000系列的器件只能作十进制的BCD码译码,然而数字系统的数据处理和运算都是二进制的,所以输出表达式都是十六进制的。

为了满足十六进制数的译码显示,最方便的方法就是利用Verilog译码程序在FPGA/CPLD中实现。

首先要设计一段程序。

该程序可按照例3-2的case语句表述方法,再根据表4-2的真值表写出程序。

者输入的4位码为A【3:0】,输出控制7段共阴数码管的7位数据位LED7S【6:0】。

输出信号LED7S的7位分别接图4-74的工银数码管的7个段,高位在左,低位在右。

【程序源代码】(加注释)module LED (IN,led7);input[3:0] IN;output[6:0] led7; //定义输出信号reg[6:0] led7; //定规输出信号位7位的寄存器变量always@(IN) //IN为敏感性信号begin //主块开始case(IN) //使用了case语句4'b0000: led7<=7'b0111111;4'b0001: led7<=7'b0000110;4'b0010: led7<=7'b1011011;4'b0011: led7<=7'b1001111;4'b0100: led7<=7'b1100110;4'b0101: led7<=7'b1101101;4'b0110: led7<=7'b1111101;4'b0111: led7<=7'b0000111;4'b1000: led7<=7'b1111111;4'b1001: led7<=7'b1101111;default: led7<=7'b0111111;endcaseend //主块结束endmodule【仿真和测试结果】【硬件仿真结果:】【实验心得和体会】通过这次的7段数码显示译码器实验,我对EDA有了进一步的了解,对QuartusII有了了解以及在QuartusII的使用上有了一些经验。

实验四 七段数码管显示实验报告

实验四七段数码管显示实验一、实验目的掌握数码管显示数字的原理。

二、实验内容1.静态显示:数码管为共阴极,通过BCD码译码驱动器CD4511驱动,其输入端A~D输入4位BCD码,位码输入低电平选中。

按图4-1连接好电路,将8255的A口PA0~PA3与七段数码管LED1的BCD码驱动输入端A1~D1相连,8255的A口PA4~PA7与七段数码管LED2的BCD码驱动输入端A2~D2相连,8255的B口PB0~PB3与七段数码管LED3的BCD码驱动输入端A3~D3相连,8255的B口PB4~PB7与七段数码管LED4的BCD码驱动输入端A4~D4相连,8255的C口PC0~PC3分别与七段数码管LED4~LED4的位驱动输入端DG1~DG4相连。

编程从键盘上每输入4个0~9数字,在七段数码管LED4~LED4上依次显示出来。

图4-12.动态显示:数码管为共阴极,段码采用相同驱动,输入端加高电平,选中的数码管对应段点亮,位码采用同相驱动,位码输入端低电平选中,按图4-2连接好电路,图中只画了2个数码管,实际是8个数码管,将8255的A口PA0~PA7分别与七段数码管的段码驱动输入端a~g相连(32TCI0模块上的J1连32LED8模块J2),8255的C口的PC0~PC7接七段数码管的段码驱动输入(32TCI0模块上的J3连32LED8模块J1),跳线器K1连2和3。

编程在8个数码管上显示“12345678”。

按任意键推出运行。

图4-2三、编程提示1.由于DVCC卡使用PCI总线,所以分配的IO地址每台微机可能都不用,编程时需要了解当前的微机使用那段IO地址并进行处理。

2.对实验内容1,七段数码管字型代码与输入的关系如下表:四、参考流程图1.实验内容一的参考流程图图4-3 2.实验内容二的参考流程图图4-4五、参考程序1.内容一的参考程序源程序清单如下:data segmentioport equ 0c400h-0280hio8255a equ ioport+288hio8255b equ ioport+289hio8255c equ ioport+28ahio8255k equ ioport+28bhled db 3fh,06h,5bh,4fh,66h,6dh,7dh,07h,7fh,6fhmesg1 db 0dh,0ah,'Input a num (0--9),other key is exit:',0dh,0ah,'$'bz db ?cz db 04hdata endscode segmentassume cs:code,ds:datastart: mov ax,datamov ds,axmov dx,io8255k ;使8255的A口为输出方式mov ax,80hout dx,alsss0: mov si,offset bzmov cx,04hsss1: mov dx,offset mesg1 ;显示提示信息mov ah,09hint 21hmov ah,01 ;从键盘接收字符int 21hcmp al,'0' ;是否小于0jl exit ;若是则退出cmp al,'9' ;是否大于9jg exit ;若是则退出sub al,30h ;将所得字符的ASCII码减30Hmov [si],al ;存入显示缓冲区inc si ;显示缓冲区指针加1dec cx ;判断输入满4个数字吗?jnz sss1 ;不满继续mov si,offset bz ;从显示缓冲区取第一个数字的BCD 码mov al,[si]and al,0fh ;屏蔽高四位暂存ALinc si ;显示缓冲区指针加1mov ah,[si] ;取第二个数字的BCD码到AHsal ah,4h ;右移4次到高四位add al,ah ;两个BCD码合并成一个字节mov bl,al ;暂存入BLinc simov al,[si] ;取第三个数字的BCD码and al,0fhinc simov ah,[si] ;取第四个数字的BCD码到AHsal ah,4hadd ah,almov al,ahmov dx,io8255a ;从8255的A口输出(后两个数字)out dx,almov al,blmov dx,io8255b ;从8255的B口输出(前两个数字)out dx,almov al,0f0hmov dx,io8255c ;从8255的C口输出位码out dx,almov dl,0ffhmov ah,06int 21hje sss0 ;有键按下则退出exit: mov ah,4ch ;返回int 21hcode endsend start2.内容二的参考程序源程序清单如下:data segmentioport equ 0C400h-0280hio8255c equ ioport+28ahio8255k equ ioport+28bhio8255a equ ioport+288hled db 3fh,06h,5bh,4fh,66h,6dh,7dh,07h,7fh,6fh ;段码buffer1 db 01h,02h,03h,04h,05h,06h,07h,08h ;存放要显示的十位和个位con db ? ;位码data endscode segmentassume cs:code, ds:datastart: mov ax,datamov ds,axmov dx,io8255k ;将8255设为A口C口输出mov al,80hout dx,alloop2: mov al,08h ;设置数码管位计数器初值到CON mov byte ptr con,almov si,offset buffer1 ;置显示缓冲器指针SImov ah,7fh ;置位码初值disp0: mov cx,0ffffhmov bl,ds:[si] ;取显示缓冲区显示值存BXmov bh,0hpush simov dx,io8255c ;位码从C口输出mov al,ahout dx,almov dx,io8255amov si,offset led ;置led数码表偏移地址为SIadd si,bx ;求出对应的led数码mov al,byte ptr [si]out dx,al ;段码从A口输出disp1: loop disp1 ;延时mov cx,0ffffhdisp2: loop disp2ror ah,01h ;位码右移1位pop siinc si ;显示缓冲区指针加1mov al,byte ptr condec almov byte ptr con,aljnz disp0 ;数码管位计数器减1为0吗?,不为0继续mov dx,io8255a ;为0,关数码管显示mov al,0out dx,almov dl,0ffhmov ah,06int 21hje loop2 ;有键按下则退出mov ah,4ch ;返回int 21hcode endsend start实验总结:通过这次试验,我了解到自定义数据类型可以根据自己的需要方便设定,有很大的灵活性。

键盘输入与七段数码管显示实验

;查第 5 行无键按下,转查第 6 行 ;第 5 行有键按下,行首键码#05H 送(A) ;转求键码

;查第 6 行无键按下,转查第 7 行 ;第 6 行有键按下,行首键码#06H 送(A) ;转求键码

实 才知道原因,原来是我们那设备箱没有初始化好。后来在老师的指导下,我

验 们把设备箱设置好后,终于做出了结果。也达到了实验目的。①.学会利用

总 8255 扩展 I/O 口;

结

②.掌握行列式键盘、7 段数码显示器接口的设计方法,验证 7 段数码管

显示原理;

③.通过软硬件结合,了解单片机应用中软硬件的相依性。 总的来说,这次实验让我收获颇多啊,锻炼了我独自想考和动手的能力。

;查第 2 行无键按下,转查第 3 行

.

MOV A, #02H

AJMP LKP

LTHR: JB ACC.3, LFOU

MOV A, #03H

AJMP LKP

LFOU: JB

ACC.4, LFIV

MOV A, #04H

AJMP LKP

LFIV: JB

ACC.5, LSIX

MOV A, #05H

AJMP LKP

MOV A, #00H

;第 0 行有键按下,行首键码#00H 送(A)

AJMP LKP

;转求键码

LONE: JB

ACC.1, LTWO

;查第 1 行无键按下,转查第 2 行

MOV A, #01H

;第 1 行有键按下,行首键码#01H 送(A)

AJMP LKP

;转求键码

LTWO: JB

ACC.2, LTHR

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA 实验报告

实验名称: 7段数码管控制接口学院:信息工程学院

专业: 11级电子信息工程2班年级、班: 2009级2班

学生姓名:王璐

指导教师:郭华

2014 年 6 月24 日

7段数码管控制接口

一、实验要求。

用设计一个共阴7 段数码管控制接口,要求:在时钟信号的控制下,使 6 位数码管动态刷新显示0—F,其中位选信号为8-3 编码器编码输出。

二、实验内容。

在实验仪器中,8 位7 段数码显示的驱动电路已经做好,并且其位选信(SEL[7..0])为一3-8 译码器的输出,所以我们在设计7 段数码管控制接口时,其位选信号输出必须经8-3编码。

显示控制器的引脚图如图40-1:

图1

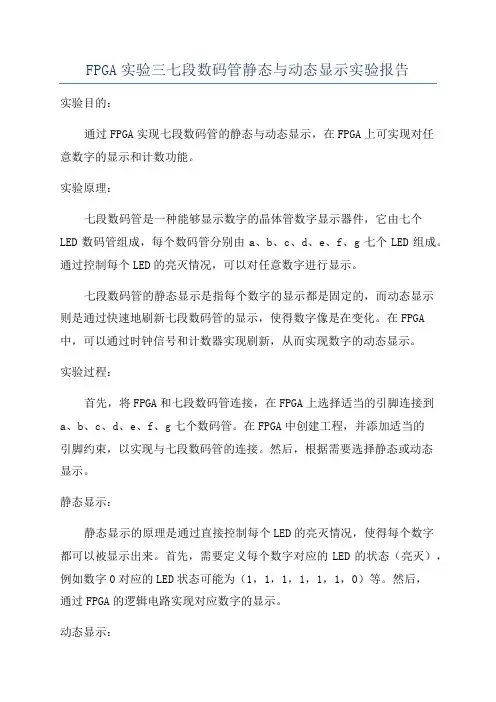

图中CP 为时钟输入端,SEGOUT[7..0]为段驱动输出;SELOUT[2..0]为位选信号输出;NUMOUT[3..0]为当前显示的数据输出。

图40-2 7段显示控制器仿真波形图

从图40-2可以看出,6位数码管是轮流点亮的,我们以NUMOUT=1 这段波形为参考:当SELOUT为000时,点亮第一位显示器,显示的数字为1,同时,NUMOUT 输出的数据也为“0001”。

同理,当SELOUT 为001 时,点亮第二位显示器,显示数字为1,直到 6 位显示器全都显示完毕,等待进入下一个数字的显示。

同时,还有一个问题不可忽视,位扫描信号的频率至少需要多少以上,才能使显示器不闪烁?简单的说,只要扫描频率超过眼睛的视觉暂留频率24HZ以上就可以达到点亮单个显示,却能享有6个同时显示的视觉效果,而且显示也不闪烁。

当我们输入频率为5MHZ时,我们通过加法计数器来产生一个约300HZ 的信号,并且由它来产生位选信号,请参考下面程序段:

PROCESS (CP) -- 计数器计数

Begin

IF CP'Event AND CP='1' then

Q <= Q+1;

END IF;

END PROCESS;

NUM <= Q(24 DOWNTO 21); --about 1 Hz

S <= Q(15 DOWNTO 13); --about 300 Hz

--扫描信号

SEL <= "000" WHEN S=0 ELSE

"001" WHEN S=1 ELSE

"010" WHEN S=2 ELSE

"011" WHEN S=3 ELSE

"100" WHEN S=4 ELSE

"101" WHEN S=5 ELSE

"111111";

由计数器Q 引出到S信号,若时钟信号为5MHZ时,Q13 得到的信号频率约为300HZ,再将它分给扫描信号,最后每个显示器扫描信号频率为:300/6=50HZ>24HZ,所以不会有闪烁情形产生。

实验程序设计如下:

module ledCycle(outData,VGA,CLK);

input CLK;

output [3:0] VGA;

assign VGA[3:0]=4'b0010;

output reg [15:0] outData;

reg [7:0]temp=8'h00;

parameter font0=16'h803F;

parameter font1=16'h8006;

parameter font2=16'h805B;

parameter font3=16'h804F;

parameter font4=16'h8066;

parameter font5=16'h806D;

parameter font6=16'h807D;

parameter font7=16'h8007;

parameter font8=16'h807F;

parameter font9=16'h806F;

parameter fontA=16'h8077;

parameter fontB=16'h807C;

parameter fontC=16'h8039;

parameter fontD=16'h805E;

parameter fontE=16'h8079;

parameter fontF=16'h8071;

always @(posedge CLK)

begin

if(temp>16)

begin

temp=1;

outData=font0;

end

else

begin

case (temp)

0: outData=font0;

1: outData=font1;

2: outData=font2;

3: outData=font3;

4: outData=font4;

5: outData=font5;

6: outData=font6;

7: outData=font7;

8: outData=font8;

9: outData=font9;

10: outData=fontA;

11: outData=fontB;

12: outData=fontC;

13: outData=fontD;

14: outData=fontE;

15: outData=fontF;

default ;

endcase

temp=temp+1;

end

end

endmodule

三、实验连线和引脚分配。

实验连线:IO_CLK连接IO3

图3 引脚分配图

四、RTL图和时序仿真波形。

图4 时序仿真图

图6 RTL电路图。