第二章 封装工艺流程

合集下载

第二章 封装工艺流程

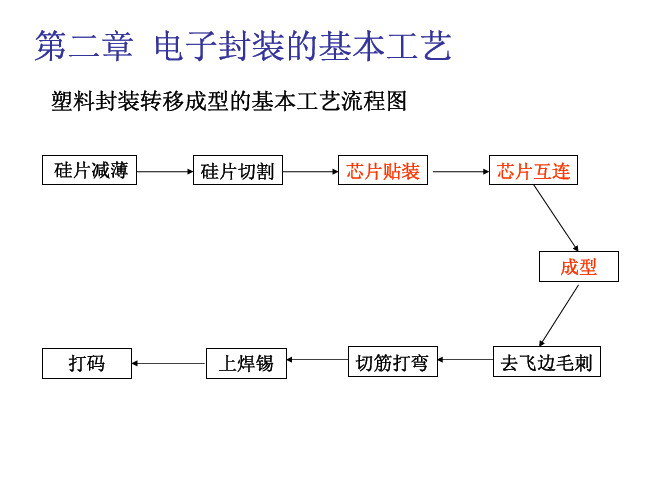

封装工艺的基本流程:

硅片减薄 芯片切割 硅片贴装 芯片互连

打码

上焊锡 切筋成形

成型技术即 (塑料封装) 去飞边毛刺

尹小田

硅片的尺寸越来越大,为了方便制 造、测试和运送过程,厚度增加。

硅片减薄 芯片切割 硅片贴装 芯片互连

成型技术即

打码 上焊锡 切筋成形

(塑料封装) 去飞边毛刺

背面减薄技术有: 磨削、研磨、干式抛光(Dry Polishing)、 化学机械抛光(chemical mechanicai polishing,CMP)、 电化学腐蚀(Electrochemical Etching)、 湿法腐蚀(Wet Etching,WE)、 等离子增强化学腐蚀(Plasma-Enhanced Chemical Etching,PECE) 常压等离子腐蚀(Atmosphere Downstream Plasma

尹小田

(4)玻璃胶粘贴法

方法:用高分子材料聚合物玻璃胶进行芯片粘贴。 工艺:先以盖印、网印、点胶的技术把胶原料涂布在基

板的芯片座中,再把芯片置于玻璃胶上粘贴。

1、多用于陶瓷封装中 2、冷却过程谨慎控制降温的速度以免造成应力破 裂

优3、点增:加可热以、得点到传无导空性隙能、,热可稳以定加性金优属良如的:、箔低、结银合应力、 低湿气含量的芯片粘贴;

尹小田

4、芯片互连

硅片减薄 芯片切割 硅片贴装 芯 切筋成形

(塑料封装) 去飞边毛刺

定义:把电子外壳的I/O引线或基板上的金线焊区与芯片的 焊区相连。

涂布合适的厚度和轮廓的芯片焊盘上进行固化。

1、各向同性材料。

不精确会怎样?

2、导电硅橡胶。

3、各向异性导电聚合物。 导电胶的缺点:热稳定性不好、高温时容易劣化和引发导 目电用的胶于导是中高电:有可胶改机靠中善物度填胶气要充的体求银导充的颗热分封粒性泄装或,漏。银增而薄强降片散低,热产因能品此力的都。 可是靠是度导,电因的此。不

第二章-电子封装的基本工艺-PDF全

优点: 键合温度低,操作方便、灵活,焊点牢固,压

点面积大,无方向性,可自动化焊接。

三种引线键合的焊接拉力比较

热压焊:<0.05N/点 超声焊:>0.1N/点(Al丝, 40µm) 热超声焊:0.07-0.09N/点(Au丝, 25µm)

引线键合可能产生的失效

脱焊(lift-off):原因是焊盘上存在有机沾污或是 表面氧化层太厚 疲劳断裂(fatigue break):原因是生成金属间化 合物,使接触电阻增大。金属间化合物形成的同 时,在焊接点产生空洞,在热冲击、温度循环过 程中,空洞越来越大,导致焊点断裂。 (金属间化合物的生成是二种金属键合的关键, 金属间化合物的剪切强度比纯金和纯铝高。)

TAB的应用

主要应用在低成本,大规模生产的电子产品。

TAB的引线在九十年代: 200—300根,内引线间距50—80um,外引线

间距<0.3mm 2000年:达到800—1000根引线

2.2.3 倒装焊

倒装焊(FCB)是芯片面朝下,芯片焊区直接与基板 焊区直接互连的一种方法。

优点: • 互连线短,互连电容、电阻、电感小,适合高频高速器件; • 占基板的面积小,安装密度高; • 芯片焊区可面分布,适合高I/O器件; • 芯片安装和互连可以同时进行,工艺简单、快速,适合

1.热压焊:

利用加热和加压力使金属丝与Al或Au金属焊区压焊在一 起。 原理:使焊区金属塑性形变,破坏压焊界面氧化层,使金属 丝和焊区金属接触面产生原子间吸引力,达到键合的目的。 此外,界面上、下金属在加热加压下相互镶嵌。 焊接压力:0.5-1.5N/点 焊头温度:150℃ 芯片温度:>200℃ 缺点:高温:氧化,生成金属间化合物;

第二章 电子封装的基本工艺

点面积大,无方向性,可自动化焊接。

三种引线键合的焊接拉力比较

热压焊:<0.05N/点 超声焊:>0.1N/点(Al丝, 40µm) 热超声焊:0.07-0.09N/点(Au丝, 25µm)

引线键合可能产生的失效

脱焊(lift-off):原因是焊盘上存在有机沾污或是 表面氧化层太厚 疲劳断裂(fatigue break):原因是生成金属间化 合物,使接触电阻增大。金属间化合物形成的同 时,在焊接点产生空洞,在热冲击、温度循环过 程中,空洞越来越大,导致焊点断裂。 (金属间化合物的生成是二种金属键合的关键, 金属间化合物的剪切强度比纯金和纯铝高。)

TAB的应用

主要应用在低成本,大规模生产的电子产品。

TAB的引线在九十年代: 200—300根,内引线间距50—80um,外引线

间距<0.3mm 2000年:达到800—1000根引线

2.2.3 倒装焊

倒装焊(FCB)是芯片面朝下,芯片焊区直接与基板 焊区直接互连的一种方法。

优点: • 互连线短,互连电容、电阻、电感小,适合高频高速器件; • 占基板的面积小,安装密度高; • 芯片焊区可面分布,适合高I/O器件; • 芯片安装和互连可以同时进行,工艺简单、快速,适合

1.热压焊:

利用加热和加压力使金属丝与Al或Au金属焊区压焊在一 起。 原理:使焊区金属塑性形变,破坏压焊界面氧化层,使金属 丝和焊区金属接触面产生原子间吸引力,达到键合的目的。 此外,界面上、下金属在加热加压下相互镶嵌。 焊接压力:0.5-1.5N/点 焊头温度:150℃ 芯片温度:>200℃ 缺点:高温:氧化,生成金属间化合物;

第二章 电子封装的基本工艺

第二章 封装工艺流程

各种连线技术依IC集成度区分的应用范围

3.1 打线键合技术

打线键合(焊接)技术 打线键合(焊接)技术为集成电路芯片与封装结构之间的电路连线最常被使用的方 法。其方法是将细金属线或金属带按顺序打在芯片与引脚架或封装基板的键合点 (Pad)上而形成电路连接。 超声波键合(Ultrasonic Bonding U/ S Bonding ) 打线键合技术 热压键合( Thermocompression Bonding T/C ) 热超声波焊接(Thermosonic Bonding T/S Bonding)

焊接粘结法

2.3 导电胶粘贴法

导电胶是大家熟悉的填充银的高分子材料聚合物,是具有良好导热导电性能的环氧 树脂。导电胶粘贴法不要求芯片背面和基板具有金属化层,芯片粘贴后,用导电胶 固化要求的温度时间进行固化,可在洁净的烘箱中完成固化,操作起来简便易行。 因此成为塑料封装常用的芯片粘贴法。以下有三种导电胶 三种导电胶的配方可以提供所需的电 三种导电胶 互连: (1)各向同性材料( ICA,isotropic conductive adhesive ),它能沿所 有方向导电,代替热敏元件上的焊料,也能用于需要接地的元器件 (2)导电硅橡胶,它能有助于保护器件免受环境的危害,如水、汽,而且 可屏蔽电磁和射频干扰(EMI/RFI) (3)各向异性导电聚合物(ACA,anisotropic conductive adhesive ), 它只允许电流沿某一方向流动,提供倒装芯片元器件的电连接和消除应变 以上三种类型导电胶都有两个共同点 两个共同点:在接合表面形成化学结合和导电功能。 两个共同点 导电胶填充料是银颗粒或者是银薄片,填充量一般在75%~80%之间,粘贴剂都是导电的。 但是,作为芯片的粘贴剂,添加如此高含量的填充料,其目的是改善粘贴剂的导热性,即 为了散热。因为在塑料封装中,电路运行过程产生的绝大部分热量将通过芯片粘贴剂和框 架散发出去。

CH2封装工艺流程

2.3.1共晶粘贴法 共晶反应 指在一定的温度下,一定成分的液体同时结晶出两种一定

成分的固相反应。例如,含碳量为2.11%-6.69%的铁碳合 金,在1148摄氏度的恆温下发生共晶反应,产物是奥氏体 (固态)和渗碳体(固态)的机械混合物,称为“莱氏 体”。

一般工艺方法 陶瓷基板芯片座上镀金膜-将芯片放置在芯片座上-热氮气

2.4.2 载带自动键合技术

(1)单层结构载带

(3)三层结构载带

这仅为一铜带,其上腐蚀出引线图

第二章 封装工艺流程

打线键合的线材与可靠度 (1)合金线材 铝合金线

因纯铝线材太软很少使用。铝合金线标准线材是铝-1% 硅。令你一种是含0.5-1%镁的铝导线。其优点是抗疲劳 性优良,生成金属间化合物的影响小。

金线 纯金线的纯度一般用4个9。为增加机械强度,往往在金

中添加5-10ppm 铍或铜。金线抗氧化性好,常由于超声 波焊接中。

这两种方法都很好地避免了或减少了减薄引起 的硅片翘曲以及划片引起的边缘损害,大大增强了 芯片的抗碎能力。

第二章 封装工艺流程

2.3 芯片贴装 芯片贴装,也称芯片粘贴,是将芯片固定于封装基板或引

脚架芯片的承载座上的工艺过程。

贴装方式

• 共晶粘贴法 • 焊接粘贴法 • 导电胶粘贴法 • 玻璃胶粘贴法

第二章 封装工艺流程

基带材料:要求耐高温,与金属箔粘贴性好,热匹配性好, 抗化学腐蚀性强,机械强度高,吸水率低。例如,聚酰亚胺

(PI)、聚乙烯对本二甲酸脂(PET)和苯并环丁烯(BCB)

TAB金属材料:要求导电性能好,强度高,延展性、表面 平滑性良好,与各种基带粘贴牢固,不易剥离,易于用光刻 法制作出精细复杂的图形,易电镀Au、Ni、Pb/Sn焊接材料, 例如,Al、Cu。

成分的固相反应。例如,含碳量为2.11%-6.69%的铁碳合 金,在1148摄氏度的恆温下发生共晶反应,产物是奥氏体 (固态)和渗碳体(固态)的机械混合物,称为“莱氏 体”。

一般工艺方法 陶瓷基板芯片座上镀金膜-将芯片放置在芯片座上-热氮气

2.4.2 载带自动键合技术

(1)单层结构载带

(3)三层结构载带

这仅为一铜带,其上腐蚀出引线图

第二章 封装工艺流程

打线键合的线材与可靠度 (1)合金线材 铝合金线

因纯铝线材太软很少使用。铝合金线标准线材是铝-1% 硅。令你一种是含0.5-1%镁的铝导线。其优点是抗疲劳 性优良,生成金属间化合物的影响小。

金线 纯金线的纯度一般用4个9。为增加机械强度,往往在金

中添加5-10ppm 铍或铜。金线抗氧化性好,常由于超声 波焊接中。

这两种方法都很好地避免了或减少了减薄引起 的硅片翘曲以及划片引起的边缘损害,大大增强了 芯片的抗碎能力。

第二章 封装工艺流程

2.3 芯片贴装 芯片贴装,也称芯片粘贴,是将芯片固定于封装基板或引

脚架芯片的承载座上的工艺过程。

贴装方式

• 共晶粘贴法 • 焊接粘贴法 • 导电胶粘贴法 • 玻璃胶粘贴法

第二章 封装工艺流程

基带材料:要求耐高温,与金属箔粘贴性好,热匹配性好, 抗化学腐蚀性强,机械强度高,吸水率低。例如,聚酰亚胺

(PI)、聚乙烯对本二甲酸脂(PET)和苯并环丁烯(BCB)

TAB金属材料:要求导电性能好,强度高,延展性、表面 平滑性良好,与各种基带粘贴牢固,不易剥离,易于用光刻 法制作出精细复杂的图形,易电镀Au、Ni、Pb/Sn焊接材料, 例如,Al、Cu。

封装工艺流程

合金焊料

软质焊料

2.3.3 导第电二胶章粘贴法封装工艺流程

导电胶是银粉与高分子聚合物(环氧树脂) 的混合物。银粉起导电作用,而环氧树脂起 粘接作用导。电胶有三种配方:

(1)各向同性材料,能沿所有方向导电。 (2)导电硅橡胶,能起到使器件与环境隔 绝,防止水、汽对芯片的影响,同时还可 以屏蔽电磁干扰。 (3)各向异性导电聚合物,电流只能在一 个方向流动。在倒装芯片封装中应用较多。 无应力影响。

(3)TAB技术中使用铜线而不使用铝线,从而改善器 件的热耗散性能。

(4)在芯片最终封装前可进行预测试和通电老化。这 样可剔除坏芯片,不使它流入下一道工序,从而节省了 成本,提高了可靠性。

(5)TAB工艺中引线的键合平面低,使器件薄化。

2.4.2 载第带二自动章键合封技术装工艺流程

TAB技术的关键材料

第二章 封装工艺流程

2.2.2减薄工艺

先划片DB后G(d减icin薄g b和efo减re g薄rin划din片g) 在两背种面方磨削法之前,将硅片的

正面切割出一定深度的切口,然后再进行磨削。

DBT(dicing by thinning) 在减薄之前先用机械的或化学 的方法切割出一定深度的切口,然后用磨削方法减薄到一 定厚度后,采用常压等离子腐蚀技术去除掉剩余加工量。。

集成电路封装技术

2.1.1 为第什二么要章学习封封装装工工艺流艺程流程

熟悉封装工艺流程是认识封装技术的前提,是进行封 装设计、制造和优化的基础。

芯片封装和芯片制造不在同一工厂完成 它们可能在同一工厂不同的生产区、或不同的

地区,甚至在不同的国家。许多工厂将生产好 的芯片送到几千公里以外的地方去做封装。芯 片一般在做成集成电路的硅片上进行测试。在 测试中,先将有缺陷的芯片打上记号(打一个 黑色墨点),然后在自动拾片机上分辨出合格 的芯片。

软质焊料

2.3.3 导第电二胶章粘贴法封装工艺流程

导电胶是银粉与高分子聚合物(环氧树脂) 的混合物。银粉起导电作用,而环氧树脂起 粘接作用导。电胶有三种配方:

(1)各向同性材料,能沿所有方向导电。 (2)导电硅橡胶,能起到使器件与环境隔 绝,防止水、汽对芯片的影响,同时还可 以屏蔽电磁干扰。 (3)各向异性导电聚合物,电流只能在一 个方向流动。在倒装芯片封装中应用较多。 无应力影响。

(3)TAB技术中使用铜线而不使用铝线,从而改善器 件的热耗散性能。

(4)在芯片最终封装前可进行预测试和通电老化。这 样可剔除坏芯片,不使它流入下一道工序,从而节省了 成本,提高了可靠性。

(5)TAB工艺中引线的键合平面低,使器件薄化。

2.4.2 载第带二自动章键合封技术装工艺流程

TAB技术的关键材料

第二章 封装工艺流程

2.2.2减薄工艺

先划片DB后G(d减icin薄g b和efo减re g薄rin划din片g) 在两背种面方磨削法之前,将硅片的

正面切割出一定深度的切口,然后再进行磨削。

DBT(dicing by thinning) 在减薄之前先用机械的或化学 的方法切割出一定深度的切口,然后用磨削方法减薄到一 定厚度后,采用常压等离子腐蚀技术去除掉剩余加工量。。

集成电路封装技术

2.1.1 为第什二么要章学习封封装装工工艺流艺程流程

熟悉封装工艺流程是认识封装技术的前提,是进行封 装设计、制造和优化的基础。

芯片封装和芯片制造不在同一工厂完成 它们可能在同一工厂不同的生产区、或不同的

地区,甚至在不同的国家。许多工厂将生产好 的芯片送到几千公里以外的地方去做封装。芯 片一般在做成集成电路的硅片上进行测试。在 测试中,先将有缺陷的芯片打上记号(打一个 黑色墨点),然后在自动拾片机上分辨出合格 的芯片。

第2章 封装工艺流程

后者的特点是将一根、一根的引线先后分立的快速的键合到搭接

片上。TAB技术中内引线键合后还要作后道工序,包括电学测试、

对芯片的影响,同时还可以屏蔽电磁干扰。

③各向异性导电聚合物:电流只能在一个方向流动。

❖ 导电胶功能:(形成化学结合、具有导电功能)

❖

精选2021版课件

25

2.3.4 玻璃胶粘贴法

与导电胶类似,玻璃胶也属于厚膜导体材料(后面

我们将介绍)。不过起粘接作用的是低温玻璃粉。它

是起导电作用的金属粉(Ag、Ag-Pd、Au、Cu等)

与低温玻璃粉和有机溶剂混合,制成膏状。

为低成本芯片粘贴材料,适用于低成本的陶瓷

封装。

❖ 优点:无缝隙、热稳定性优良、低接合应力与

低湿气含量。

❖

精选2021版课件

26

精选2021版课件

27

2.4 互连技术

是微系统封装的基础技术和专有技术。

❖ 服务对象:芯片与芯片间、芯片与封装衬底

间、器件与基板间的物理连接。

12

Optical Inspection 光学检查

主要是针对Wafer Saw之后在显微镜下进行Wafer的外观检查,是否有

出现废品。

精选2021版课件

Chipping Die

崩边

13

2.3 芯片粘贴

芯片贴装:也称芯片粘贴,是将芯片固定

于封装基板或引脚架芯片的承载座上的工

艺过程。

贴装方式4种:

❖ 共晶粘贴法(Au-Si合金)

到原子引力范围,通过原子间吸引力,达到

“键合”的目的。

❖ 缺点:金属丝变形过大,受损,影响键合质

量,限制了使用范围。

❖

精选2021版课件

片上。TAB技术中内引线键合后还要作后道工序,包括电学测试、

对芯片的影响,同时还可以屏蔽电磁干扰。

③各向异性导电聚合物:电流只能在一个方向流动。

❖ 导电胶功能:(形成化学结合、具有导电功能)

❖

精选2021版课件

25

2.3.4 玻璃胶粘贴法

与导电胶类似,玻璃胶也属于厚膜导体材料(后面

我们将介绍)。不过起粘接作用的是低温玻璃粉。它

是起导电作用的金属粉(Ag、Ag-Pd、Au、Cu等)

与低温玻璃粉和有机溶剂混合,制成膏状。

为低成本芯片粘贴材料,适用于低成本的陶瓷

封装。

❖ 优点:无缝隙、热稳定性优良、低接合应力与

低湿气含量。

❖

精选2021版课件

26

精选2021版课件

27

2.4 互连技术

是微系统封装的基础技术和专有技术。

❖ 服务对象:芯片与芯片间、芯片与封装衬底

间、器件与基板间的物理连接。

12

Optical Inspection 光学检查

主要是针对Wafer Saw之后在显微镜下进行Wafer的外观检查,是否有

出现废品。

精选2021版课件

Chipping Die

崩边

13

2.3 芯片粘贴

芯片贴装:也称芯片粘贴,是将芯片固定

于封装基板或引脚架芯片的承载座上的工

艺过程。

贴装方式4种:

❖ 共晶粘贴法(Au-Si合金)

到原子引力范围,通过原子间吸引力,达到

“键合”的目的。

❖ 缺点:金属丝变形过大,受损,影响键合质

量,限制了使用范围。

❖

精选2021版课件

微电子封装技术第2章 封装工艺流程

2.4芯片贴装

焊接粘贴法工艺是将芯片背面淀积一定厚度的 Au或Ni,同时在焊盘上淀积Au-Pd-Ag和Cu的金属 层。

其优点是热传导好。工艺是将芯片背面淀积一 定厚度的Au或Ni,同时在焊盘上淀积Au-Pd-Ag和 Cu的金属层。这样就可以使用Pb-Sn合金制作的合 金焊料将芯片焊接在焊盘上。焊接温度取决于PbSn合金的具体成分比例。

微电子封装技术

董海青 李荣茂

第2章 封装工艺流程

2.1 流程概述 2.2 芯片减薄 2.3 芯片切割 2.4 芯片贴装 2.5 芯片互连技术 2.6 成形技术 2.7 后续工艺

2.1 流程概述

芯片封装工艺流程一般可以分为两个部分:前 段操作和后段操作。前段操作一般是指用塑料封装 (固封)之前的工艺步骤,后段操作是指成形之后 的工艺步骤。

2.4芯片贴装

导电胶粘贴法不要求芯片背面和基板具有金属 化层,芯片座粘贴后,用导电胶固化要求的温度时 间进行固化,可以在洁净的烘箱中完成固化,操作 起来比较简便易行。

导电胶进行芯片贴装的工艺过程如下:用针筒 或注射器将黏着剂涂布在芯片焊盘上,然后将芯片 精确地放置到焊盘的黏着剂上面。

导电胶粘贴法的缺点是热稳定性不好,容易在 高温时发生劣化及引发黏着剂中有机物气体成分泄 露而降低产品的可靠度,因此不适用于高可靠度要 求的封装。

2.4芯片贴装

玻璃胶粘贴芯片时,先以盖印、网印、点胶等 技术将玻璃胶原料涂布在基板的芯片座上,将IC芯 片放置在玻璃胶上后,再将封装基板加热至玻璃熔 融温度以上即可完成粘贴。

玻璃胶粘贴法的优点是可以得到无空隙、热稳 定性优良、低结合应力与低湿气含量的芯片粘贴; 其缺点是玻璃胶中的有机成分与溶剂必须在热处理 时完全去除,否则对封装结构及其可靠度将有所损 害。

集成电路封装工艺流程-PPT文档资料

凸块式芯片TAB,先将金属凸块长成于IC芯片的铝键合 点上,再与载带的内引脚键合。预先长成的凸块除了提供引 脚所需要的金属化条件外,可避免引脚与IC芯片间可能发生 短路,但制作长有凸块的芯片是TAN工艺最大的困难。

第二章 封装工艺流程

2.4.2 载带自动键合技术

芯片凸点制作技术 凸点因形状不同可分为两种

板上的金属焊区相连接。 芯片互连常见的方法:

打线键合(WB wire bonding)

倒装芯片键合(FCB flip chip bonding,C4)

载带自动键合(TAB tape automate bonding)

这三种连接技术对于不同的封装形式和集成电路 芯片集成度的限制各有不同的应用范围。

打线键合适用引脚数为3-257;载带自动键合的适 用引脚数为12-600;倒装芯片键合适用的引脚数为616000。可见C4适合于高密度组装。

IC芯片制作完成后其表面均镀有钝化保护层,厚度高于 电路的键合点,因此必须在IC芯片的键合点上或TAB载带的 内引线前端先长成键合凸块才能进行后续的键合,通常TAB 载带技术也据此区分为凸块化载带与凸块化芯片TAB两大类。

地状金属凸块;单层载带可配合铜箔引脚的刻蚀制成凸 块,在双层与三层载带上,因为蚀刻的工艺容易致导带变形, 而使未来键合发生对位错误,因此双层与三层载带较少应用 于凸块载带TAB的键合。

这两种方法都很好地避免了或减少了减薄引起 的硅片翘曲以及划片引起的边缘损害,大大增强了 芯片的抗碎能力。

第二章 封装工艺流程

2.3 芯片贴装 芯片贴装,也称芯片粘贴,是将芯片固定于封装基板或引

脚架芯片的承载座上的工艺过程。

贴装方式

• 共晶粘贴法 • 焊接粘贴法 • 导电胶粘贴法 • 玻璃胶粘贴法

第二章 封装工艺流程

2.4.2 载带自动键合技术

芯片凸点制作技术 凸点因形状不同可分为两种

板上的金属焊区相连接。 芯片互连常见的方法:

打线键合(WB wire bonding)

倒装芯片键合(FCB flip chip bonding,C4)

载带自动键合(TAB tape automate bonding)

这三种连接技术对于不同的封装形式和集成电路 芯片集成度的限制各有不同的应用范围。

打线键合适用引脚数为3-257;载带自动键合的适 用引脚数为12-600;倒装芯片键合适用的引脚数为616000。可见C4适合于高密度组装。

IC芯片制作完成后其表面均镀有钝化保护层,厚度高于 电路的键合点,因此必须在IC芯片的键合点上或TAB载带的 内引线前端先长成键合凸块才能进行后续的键合,通常TAB 载带技术也据此区分为凸块化载带与凸块化芯片TAB两大类。

地状金属凸块;单层载带可配合铜箔引脚的刻蚀制成凸 块,在双层与三层载带上,因为蚀刻的工艺容易致导带变形, 而使未来键合发生对位错误,因此双层与三层载带较少应用 于凸块载带TAB的键合。

这两种方法都很好地避免了或减少了减薄引起 的硅片翘曲以及划片引起的边缘损害,大大增强了 芯片的抗碎能力。

第二章 封装工艺流程

2.3 芯片贴装 芯片贴装,也称芯片粘贴,是将芯片固定于封装基板或引

脚架芯片的承载座上的工艺过程。

贴装方式

• 共晶粘贴法 • 焊接粘贴法 • 导电胶粘贴法 • 玻璃胶粘贴法

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

切割机的刀片一般为脉冲激光束或金钢石,划得边缘整 齐,很少有裂口。只是划片时会出现没有划到底的情况,取 片时是顶针的顶力把芯片分离的,则端口出现不规则的状态, 划片槽业也会有少量微裂纹和凹槽存在。为此开发了先划片 后减薄 (Dicing Before Grinding,DBG)和减薄划片 (Dicing By Thinning,DBT)

优点:塑变应力值高,具有 良好的抗疲劳与抗潜变特性;

缺点:难缓和热膨胀系数差 异所引起的压力破坏。

优点:应力问题小。

缺点:使用时必须在芯片背面 先镀上类似制作焊锡凸块时的 多层金属薄膜以利焊料的润湿。

尹小田

(3)导电胶粘贴法

方法:用填充银的高分子材料聚合物导电胶固化。 工艺:把芯片精确置于用针筒或注射器将导电胶(粘贴剂) 涂布合适的厚度和轮廓的芯片焊盘上进行固化。

超声波键合(Ultrasonic Bonding,U/S Bonding) 打线 键合 技术 分:

热压键合(Thermocompression Bonding,T/C Bonding)

热超声波键合(Thermosonic Bonding, T/S Bonding)

尹小田

超声波键合(U/S Bonding)

方法:用高分子材料聚合物玻璃胶进行芯片粘贴。 工艺:先以盖印、网印、点胶的技术把胶原料涂布在基 板的芯片座中,再把芯片置于玻璃胶上粘贴。 1、多用于陶瓷封装中

2、冷却过程谨慎控制降温的速度以免造成应力破 裂

3、增加热、点传导性能,可以加金属如:箔、银 优点:可以得到无空隙、热稳定性优良的、低结合应力、 低湿气含量的芯片粘贴; 缺点:胶中有机成分与溶剂必须在热处理时完全去除,以 免对封装结构及其可靠度有损害。

打码

上焊锡

切筋成形

去飞边毛刺

尹小田

硅片的尺寸越来越大,为了方便制 造、测试和运送过程,厚度增加。 硅片减薄 打码 芯片切割 上焊锡 硅片贴装 芯片互连

切筋成形

去飞边毛刺

成型技术即 (塑料封装)

背面减薄技术有: 磨削、研磨、干式抛光(Dry Polishing)、 化学机械抛光(chemical mechanicai polishing,CMP)、 电化学腐蚀(Electrochemical Etching)、 湿法腐蚀(Wet Etching,WE)、 等离子增强化学腐蚀(Plasma-Enhanced Chemical Etching,PECE) 常压等离子腐蚀(Atmosphere Downstream Plasma Etching,ADPE).

方法:利用合金反应进行芯片的粘贴。 工艺:把芯片置于已经镀了金膜的陶瓷基板的芯片承载 座上,在一定的压力下(附以摩擦或超声),再加热到 共晶点温度,当温度高于共晶温度时,金硅合金融化成 液态的Au-Si共熔体。冷却后,当共熔体由液相变为以 晶粒形式互相结合的机械混合物-金硅共熔晶体而全部 凝固,从而形成了牢固的欧姆接触。

切筋成形

定义:把电子外壳的I/O引线或基板上的金线焊区与芯片的 焊区相连。 设备:打线机

打线键合(Wire Bonding,WB)

芯片互连 的方式: 载带自动键合(Tape AutomatedBonding,TAB) 倒装芯片键合(Flip Chip Bonding,FCB)

尹小田

IC 封装成品构造图

超声波键合(Ultrasonic Bonding,U/S Bonding) 打线 键合 技术 分:

热压键合(Thermocompression Bonding,T/C Bonding)

热超声波键合(Thermosonic Bonding, T/S Bonding)

尹小田

热超声波键合(T/S Bonding)

常用线材:金线 方法:先再金属线末端成球,再用超声波脉冲进行 键合。 热超声波键合是热压键合和超声波键合的混合技 术。接合工具不需预热,这样可以抑制键合界面的 金属间长成化合物,降低基板的高分子材料因为高 温的劣化变形,因此常用于结合难度较高的封装连 线。

尹小田

(2)载带自动键合技术,TAB

TAB技术:用有引线图形的金属箔丝把芯片焊区与电子 封装外壳的I/O或基板上的金属布线焊区互连的工艺技术。

1、各向同性材料。

2、导电硅橡胶。

不精确会怎样?

3、各向异性导电聚合物。 导电胶的缺点:热稳定性不好、高温时容易劣化和引发导 电胶中有机物气体充分泄漏而降低产品的可靠度,因此不 导电胶中填充银颗粒或银薄片,因此都是是导电的。 用于高可靠度要求的封装。 目的是:改善胶的导热性,增强散热能力。

尹小田

(4)玻璃胶粘贴法

尹小田

楔形-楔形键合

尹小田

显微镜下的图形

尹小田

超声楔形键合图片

尹小田

楔形键合的键合点的形状

尹小田

(1)打线键合技术

打线键合就是用非常细小的线把芯片上焊盘和引线框架 (或者基板)连接起来的过程。 商家从成本考虑的角度,90% 都是使用引线键合技术。

超声波键合(Ultrasonic Bonding,U/S Bonding) 打线 键合 技术 分:

TAB

凸块式芯片TAB:在键合点上长成凸块,在与载带内 芯片有钝化保护层,厚度高于键合 引脚键合。 点,必须在芯片的键合点上或TAB载 带的内引脚前端先长成键合凸点。

尹小田

尹小田

钝态保护

芯片清洗

铝键合点

成像

粘贴阻挡层

电镀金凸块

光刻

选择性刻蚀

尹小田

TAB的关键技术——

1、芯片凸点制作技术 良好的键合力与低

第二章 封装工艺流程

1、封装工艺的流程 2、芯片切割 3、芯片贴装 4、芯片互连 5、封装工艺流程的其余步骤

尹小田

1、封装工艺的流程

封装流程可 分成2部分:

前段操作(Front End Operation): 用塑料封装之前的工艺步骤 后段操作(Back End Operation): 在塑料封装之后的工艺步骤 封装工艺的基本流程: 硅片减薄 芯片切割 硅片贴装 芯片互连 成型技术即 (塑料封装)

6、TAB采用Cu箔引线,导热、导电好,机械强度高。

7、TAB焊点键合拉力比WB高3至10倍。 8、载带的尺寸可实现标准化和自动化。可规模生产,提 高效率,降低成本。

尹小田

TAB技术的关键材料

导电性能好,

尹小田

TAB的关键技术

1、芯片凸点制作技术

2、TAB载带制作技术 有引线图形的金属箔丝

凸点 3、载带引线与芯片凸点的内引线焊接技术以及载带 外引线焊接技术。 凸块式载带TAB:在载带内引脚的前端长成台地状金 属凸块再键合。后研发成新型技 术——凸点载带自动焊接技术 (BTAB)

接触电阻 凸点的制作工艺流程(图2.13): 1、清洗 2、在芯片表面镀具有粘着、扩散阻挡和保护功能 的多层金属薄膜(阻挡层); 3、光刻成像; 4、电镀金凸块;

5、除去光刻胶;

间的扩散

防止凸块底部阻挡层金属的测侵蚀 而破坏芯片的铝线和焊垫结构

尹小田

键合工具需预热至300~400度

尹小田

尹小田

尹小田

球形-楔形键合

尹小田

球形键合的第一键合点的形状

尹小田

球形键合的第二键合 点的形状

新月状

尹小田

(1)打线键合技术

打线键合就是用非常细小的线把芯片上焊盘和引线框架 (或者基板)连接起来的过程。商家从成本考虑的角度,90% 都是使用引线键合技术。

尹小田

蓝 膜

芯片粘上一层薄膜(称蓝膜),起 保护晶圆表面电路的作用。

硅片减薄

芯片切割

硅片贴装

芯片互连 成型技术即 (塑料封装)

打码

上焊锡

切筋成形

去飞边毛刺

尹小田

2、芯片切割

硅片减薄 打码 芯片切割 上焊锡 硅片贴装 芯片互连 成型技术即 (塑料封装) 去飞边毛刺

切筋成形

定义:切割晶圆,将各个芯片分离开。 设备:切割机(划片机)

尹小田

粘贴法的比较

共晶粘贴法 芯片粘贴 的方式: 焊接粘贴法 导电胶粘贴法

玻璃胶粘贴法

1、共晶粘贴应力问题,少用

2、前两个都是利用合金反应粘贴芯片,后两个是用高分 子聚合物粘贴。

3、热稳定性和可靠度不好,不适合高可靠性要求

尹小田

4、芯片互连

硅片减薄 打码 芯片切割 上焊锡 硅片贴装 芯片互连 成型技术即 (塑料封装) 去飞边毛刺

尹小田

DBG和DBT

先划片后减薄 (Dicing Before Grinding,DBG):顾名 思义就是先将硅片的正面切割到一定的深度,然后 再进行背面磨削。 减薄划片法(Dicing By Thinning,DBT):先用机械或 化学的方式切割出切口,然后用磨削方法减薄到一 定厚度后,采用ADPE(常压等离子腐蚀)技术去掉 剩余加工量,实现裸芯片的自动分离。 其优点:很好地避免或减小了减薄引起的硅片翘曲以 及划片引起的芯片边缘损害,DBT更是能去除硅片背面 研磨损伤,并能除去芯片引起的微裂和凹槽。

芯片托盘(DIE PAD) L/F 内引脚 (INNER LEAD) 芯片(CHIP)

L/F 外引脚 (OUTER LEAD) 热固性环氧树脂 (EMC) 金线(WIRE)

尹小田

(1)打线键合技术

打线键合就是用非常细小的线把芯片上焊盘和引线框架 (或者基板)互连的过程。 商家从成本考虑的角度,90%都是 使用引线键合技术。

1、热氮气——防止硅的高温氧化,避免液面润湿性能降低, 以免减弱粘贴强度、产生孔隙、热传导质量降低和应力不均。

2、芯片背面镀金或植入金-硅预型片——利于粘贴强度。

3、相互摩擦——除去表面硅氧化物。

尹小田

(1)共晶粘贴法的问题

1、芯片和引脚架的膨胀系数严重失配,应力难以解决。 2、人工操作,不适合现代生产。

优点:塑变应力值高,具有 良好的抗疲劳与抗潜变特性;

缺点:难缓和热膨胀系数差 异所引起的压力破坏。

优点:应力问题小。

缺点:使用时必须在芯片背面 先镀上类似制作焊锡凸块时的 多层金属薄膜以利焊料的润湿。

尹小田

(3)导电胶粘贴法

方法:用填充银的高分子材料聚合物导电胶固化。 工艺:把芯片精确置于用针筒或注射器将导电胶(粘贴剂) 涂布合适的厚度和轮廓的芯片焊盘上进行固化。

超声波键合(Ultrasonic Bonding,U/S Bonding) 打线 键合 技术 分:

热压键合(Thermocompression Bonding,T/C Bonding)

热超声波键合(Thermosonic Bonding, T/S Bonding)

尹小田

超声波键合(U/S Bonding)

方法:用高分子材料聚合物玻璃胶进行芯片粘贴。 工艺:先以盖印、网印、点胶的技术把胶原料涂布在基 板的芯片座中,再把芯片置于玻璃胶上粘贴。 1、多用于陶瓷封装中

2、冷却过程谨慎控制降温的速度以免造成应力破 裂

3、增加热、点传导性能,可以加金属如:箔、银 优点:可以得到无空隙、热稳定性优良的、低结合应力、 低湿气含量的芯片粘贴; 缺点:胶中有机成分与溶剂必须在热处理时完全去除,以 免对封装结构及其可靠度有损害。

打码

上焊锡

切筋成形

去飞边毛刺

尹小田

硅片的尺寸越来越大,为了方便制 造、测试和运送过程,厚度增加。 硅片减薄 打码 芯片切割 上焊锡 硅片贴装 芯片互连

切筋成形

去飞边毛刺

成型技术即 (塑料封装)

背面减薄技术有: 磨削、研磨、干式抛光(Dry Polishing)、 化学机械抛光(chemical mechanicai polishing,CMP)、 电化学腐蚀(Electrochemical Etching)、 湿法腐蚀(Wet Etching,WE)、 等离子增强化学腐蚀(Plasma-Enhanced Chemical Etching,PECE) 常压等离子腐蚀(Atmosphere Downstream Plasma Etching,ADPE).

方法:利用合金反应进行芯片的粘贴。 工艺:把芯片置于已经镀了金膜的陶瓷基板的芯片承载 座上,在一定的压力下(附以摩擦或超声),再加热到 共晶点温度,当温度高于共晶温度时,金硅合金融化成 液态的Au-Si共熔体。冷却后,当共熔体由液相变为以 晶粒形式互相结合的机械混合物-金硅共熔晶体而全部 凝固,从而形成了牢固的欧姆接触。

切筋成形

定义:把电子外壳的I/O引线或基板上的金线焊区与芯片的 焊区相连。 设备:打线机

打线键合(Wire Bonding,WB)

芯片互连 的方式: 载带自动键合(Tape AutomatedBonding,TAB) 倒装芯片键合(Flip Chip Bonding,FCB)

尹小田

IC 封装成品构造图

超声波键合(Ultrasonic Bonding,U/S Bonding) 打线 键合 技术 分:

热压键合(Thermocompression Bonding,T/C Bonding)

热超声波键合(Thermosonic Bonding, T/S Bonding)

尹小田

热超声波键合(T/S Bonding)

常用线材:金线 方法:先再金属线末端成球,再用超声波脉冲进行 键合。 热超声波键合是热压键合和超声波键合的混合技 术。接合工具不需预热,这样可以抑制键合界面的 金属间长成化合物,降低基板的高分子材料因为高 温的劣化变形,因此常用于结合难度较高的封装连 线。

尹小田

(2)载带自动键合技术,TAB

TAB技术:用有引线图形的金属箔丝把芯片焊区与电子 封装外壳的I/O或基板上的金属布线焊区互连的工艺技术。

1、各向同性材料。

2、导电硅橡胶。

不精确会怎样?

3、各向异性导电聚合物。 导电胶的缺点:热稳定性不好、高温时容易劣化和引发导 电胶中有机物气体充分泄漏而降低产品的可靠度,因此不 导电胶中填充银颗粒或银薄片,因此都是是导电的。 用于高可靠度要求的封装。 目的是:改善胶的导热性,增强散热能力。

尹小田

(4)玻璃胶粘贴法

尹小田

楔形-楔形键合

尹小田

显微镜下的图形

尹小田

超声楔形键合图片

尹小田

楔形键合的键合点的形状

尹小田

(1)打线键合技术

打线键合就是用非常细小的线把芯片上焊盘和引线框架 (或者基板)连接起来的过程。 商家从成本考虑的角度,90% 都是使用引线键合技术。

超声波键合(Ultrasonic Bonding,U/S Bonding) 打线 键合 技术 分:

TAB

凸块式芯片TAB:在键合点上长成凸块,在与载带内 芯片有钝化保护层,厚度高于键合 引脚键合。 点,必须在芯片的键合点上或TAB载 带的内引脚前端先长成键合凸点。

尹小田

尹小田

钝态保护

芯片清洗

铝键合点

成像

粘贴阻挡层

电镀金凸块

光刻

选择性刻蚀

尹小田

TAB的关键技术——

1、芯片凸点制作技术 良好的键合力与低

第二章 封装工艺流程

1、封装工艺的流程 2、芯片切割 3、芯片贴装 4、芯片互连 5、封装工艺流程的其余步骤

尹小田

1、封装工艺的流程

封装流程可 分成2部分:

前段操作(Front End Operation): 用塑料封装之前的工艺步骤 后段操作(Back End Operation): 在塑料封装之后的工艺步骤 封装工艺的基本流程: 硅片减薄 芯片切割 硅片贴装 芯片互连 成型技术即 (塑料封装)

6、TAB采用Cu箔引线,导热、导电好,机械强度高。

7、TAB焊点键合拉力比WB高3至10倍。 8、载带的尺寸可实现标准化和自动化。可规模生产,提 高效率,降低成本。

尹小田

TAB技术的关键材料

导电性能好,

尹小田

TAB的关键技术

1、芯片凸点制作技术

2、TAB载带制作技术 有引线图形的金属箔丝

凸点 3、载带引线与芯片凸点的内引线焊接技术以及载带 外引线焊接技术。 凸块式载带TAB:在载带内引脚的前端长成台地状金 属凸块再键合。后研发成新型技 术——凸点载带自动焊接技术 (BTAB)

接触电阻 凸点的制作工艺流程(图2.13): 1、清洗 2、在芯片表面镀具有粘着、扩散阻挡和保护功能 的多层金属薄膜(阻挡层); 3、光刻成像; 4、电镀金凸块;

5、除去光刻胶;

间的扩散

防止凸块底部阻挡层金属的测侵蚀 而破坏芯片的铝线和焊垫结构

尹小田

键合工具需预热至300~400度

尹小田

尹小田

尹小田

球形-楔形键合

尹小田

球形键合的第一键合点的形状

尹小田

球形键合的第二键合 点的形状

新月状

尹小田

(1)打线键合技术

打线键合就是用非常细小的线把芯片上焊盘和引线框架 (或者基板)连接起来的过程。商家从成本考虑的角度,90% 都是使用引线键合技术。

尹小田

蓝 膜

芯片粘上一层薄膜(称蓝膜),起 保护晶圆表面电路的作用。

硅片减薄

芯片切割

硅片贴装

芯片互连 成型技术即 (塑料封装)

打码

上焊锡

切筋成形

去飞边毛刺

尹小田

2、芯片切割

硅片减薄 打码 芯片切割 上焊锡 硅片贴装 芯片互连 成型技术即 (塑料封装) 去飞边毛刺

切筋成形

定义:切割晶圆,将各个芯片分离开。 设备:切割机(划片机)

尹小田

粘贴法的比较

共晶粘贴法 芯片粘贴 的方式: 焊接粘贴法 导电胶粘贴法

玻璃胶粘贴法

1、共晶粘贴应力问题,少用

2、前两个都是利用合金反应粘贴芯片,后两个是用高分 子聚合物粘贴。

3、热稳定性和可靠度不好,不适合高可靠性要求

尹小田

4、芯片互连

硅片减薄 打码 芯片切割 上焊锡 硅片贴装 芯片互连 成型技术即 (塑料封装) 去飞边毛刺

尹小田

DBG和DBT

先划片后减薄 (Dicing Before Grinding,DBG):顾名 思义就是先将硅片的正面切割到一定的深度,然后 再进行背面磨削。 减薄划片法(Dicing By Thinning,DBT):先用机械或 化学的方式切割出切口,然后用磨削方法减薄到一 定厚度后,采用ADPE(常压等离子腐蚀)技术去掉 剩余加工量,实现裸芯片的自动分离。 其优点:很好地避免或减小了减薄引起的硅片翘曲以 及划片引起的芯片边缘损害,DBT更是能去除硅片背面 研磨损伤,并能除去芯片引起的微裂和凹槽。

芯片托盘(DIE PAD) L/F 内引脚 (INNER LEAD) 芯片(CHIP)

L/F 外引脚 (OUTER LEAD) 热固性环氧树脂 (EMC) 金线(WIRE)

尹小田

(1)打线键合技术

打线键合就是用非常细小的线把芯片上焊盘和引线框架 (或者基板)互连的过程。 商家从成本考虑的角度,90%都是 使用引线键合技术。

1、热氮气——防止硅的高温氧化,避免液面润湿性能降低, 以免减弱粘贴强度、产生孔隙、热传导质量降低和应力不均。

2、芯片背面镀金或植入金-硅预型片——利于粘贴强度。

3、相互摩擦——除去表面硅氧化物。

尹小田

(1)共晶粘贴法的问题

1、芯片和引脚架的膨胀系数严重失配,应力难以解决。 2、人工操作,不适合现代生产。