南邮微机原理试验一二

南邮微机原理实验报告

微机原理硬件实验报告实验一 I/O 地址译码一、实验目的1、掌握 I/O 地址译码电路的工作原理。

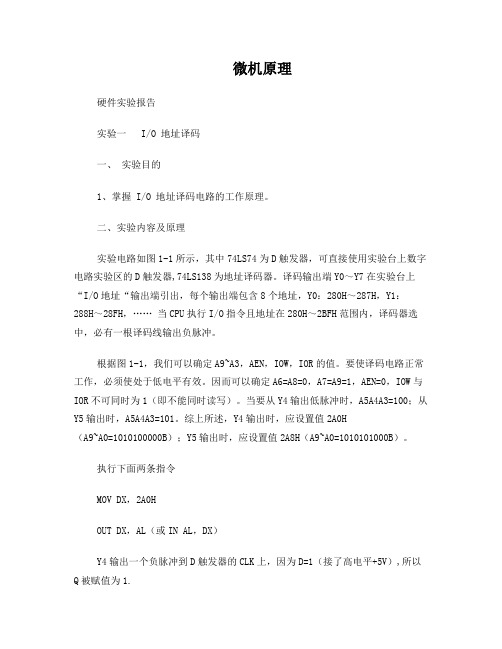

二、实验内容及原理实验电路如图1-1所示,其中74LS74为D触发器,可直接使用实验台上数字电路实验区的D触发器,74LS138为地址译码器。

译码输出端Y0~Y7在实验台上“I/O地址“输出端引出,每个输出端包含8个地址,Y0:280H~287H,Y1:288H~28FH,…… 当CPU执行I/O指令且地址在280H~2BFH范围内,译码器选中,必有一根译码线输出负脉冲。

根据图1-1,我们可以确定A9~A3,AEN,IOW,IOR的值。

要使译码电路正常工作,必须使处于低电平有效。

因而可以确定A6=A8=0,A7=A9=1,AEN=0,IOW与IOR不可同时为1(即不能同时读写)。

当要从Y4输出低脉冲时,A5A4A3=100;从Y5输出时,A5A4A3=101。

综上所述,Y4输出时,应设置值2A0H(A9~A0=1010100000B);Y5输出时,应设置值2A8H(A9~A0=1010101000B)。

执行下面两条指令MOV DX,2A0HOUT DX,AL(或IN AL,DX)Y4输出一个负脉冲到D触发器的CLK上,因为D=1(接了高电平+5V),所以Q被赋值为1.延时一段时间(delay);执行下面两条指令;MOV DX,2A8HOUT DX,AL(或IN AL,DX)Y5输出一个负脉冲到CD,D触发器被复位,Q=0。

再延时一段时间,然后循环上述步骤。

利用这两个个负脉冲控制L7闪烁发光(亮、灭、亮、灭、……),时间间隔通过软件延时实现。

三、硬件接线图与软件流程图硬件接线:Y4/IO 地址接 CLK/D 触发器Y5/IO地址接 C/D触发器D/D触发器接 SD/D角发器接+5VQ/D触发器接 L7(LED灯)或逻辑笔软件流程图:四、源程序OUTPORT1 EQU 2A0H ;预置,方便修改OUTPORT2 EQU 2A8HCODE SEGMENTASSUME CS:CODESTART: MOV DX,OUTPORT1 ;根据原理图设定A9~A0 的值(Y4)OUT DX,AL ;让译码器Y4 口输出一个负脉冲CALL DELAY ;延时MOV DX,OUTPORT2 ;根据原理图设定A9~A0 的值(Y5)OUT DX,AL ;让译码器Y5 口输出一个负脉冲CALL DELAY ;延时MOV AH,1 ;调用1 号DOS 功能,等待键盘输入INT 16HJE START ;若有键盘输入则退出程序,否继续循环MOV AH,4CHINT 21HDELAY PROC NEAR ;延时子程序MOV BX,200 ;时延长度 (200)A: MOV CX,0B: LOOP BDEC BXJN E ARETDELAY ENDPCODE ENDSEND START五、实验结果LED 灯处于闪烁状态,键盘有输入后,成功退出。

南邮 微机原理(微型计算机与接口技术)第2章2010修改

8位名称 32位名称 EAX 16位名称 AH AX AL BH BX BL CH CX CL 名称

累加器

基址变址 计数 数据 堆栈指针 基址指针 源变址

EBX

ECX EDX ESP EBP ESI EDI

DH DX DL

SP BP SI DI

IP

EIP

目的变址

IP、SP、BP、SI、DI:为寻址存贮单元提供偏移地址。其中:

3.标志寄存器

31

EFLAGS

15

FLAGS

0

标志寄存器

标志寄存器FLAGS又称为程序状态字PSW,实模式下使 用16位寄存器,该寄存器主要有两个作用: • 记录CPU运行结果状态标志; • 提供控制标志。 FLAGS定义如下:

15

OF DF IF

8

7

ZF AF PF

0

CF

TF SF

根据功能,8086的标志可以分为两类:

32位名称 EAX

8位名称 16位名称 AH AX AL AHAX AL BH BX BL CH CX CL DH DX DL SP

名称 累加器 基址变址

EBX

ECX EDX ESP

计数

数据 堆栈指针 基址指针 目的变址 源变址

EBP

EDI ESI

BP

DI SI

AX、BX、CX、DX 共同特点: • 既可作为16位寄存器来用又可作为两个8位寄存器(高、低位)来用; • 都是用于暂存操作数,或是运算的中间结果或其它一些信息。 指令=操作码+操作数

• 总线接口单元 BIU

(寄存器组) • 执行单元 EU (:

• 存储管理(分段和分页部件) • 指令和数据流水线 • 指令和数据CACHE • 指令预取

南京邮电大学微机原理作业

斜体下划线部分可跳过

用户定义的中断服务程序有两个设计方法:

①定义用户中断服务程序为“71H型”

②定义用户中断服务程序为“0AH型”

用户中断服务程序结束

①若用户中断定义为0AH型,服务程序结束前只向主8259送结束命令

5.用系统机串行口采用中断方式完成字符发送和接收,编程时应采取哪些措施?

答:⑴中断允许寄存器相应位置1

⑵MODEM控制寄存器 ,即 打通8250的中断请求通道。

⑶8259相应中断屏蔽位置0(主8259 、 )— 8259

⑷CPU处于开中断(STI)— CPU

6.A、B两台PC机利用主串口进行点-点单工通信(不用联络线),发送采用查询方式,接收采用中断方式。一帧字符包含7个数据位,1个停止位,1个校验位,通信速率为4800波特(分频系数为0018H)。

STI;开中断

SCAN:MOVAH, 01H;设置功能号

INT16H;有键入?

JZSCAN;否循环

CALLRESET;恢复现场

MOVAH, 4CH

INT21H

;--------------------------------------

SERVICEPROC

PUSHA

PUSHDS;保护现场

MOVAX, DATA

MESGDB'Welcome!','$';显示的字符串

DATAENDS

CODESEGMENTUSE16

ASSUMECS:CODE, DS:DATA

BEG:MOVAX, DATA

MOVDS, AX

CLI;关中断

CALLI8259;8259初始化

南邮微机原理考研真题

南邮微机原理考研真题微机原理是计算机科学与技术专业考研的一门重要课程,而南京邮电大学(简称南邮)是中国计算机科学与技术领域的一所知名高校。

本文将介绍南邮微机原理考研真题,并对考试内容进行详细分析和解答。

一、概述南邮微机原理考研真题主要围绕计算机体系结构、指令系统和中央处理器(CPU)等内容展开。

通过解答这些题目,考生需要展示对计算机内部结构和运行原理的深入理解,以及对计算机编程和指令集的熟悉程度。

二、考试题型南邮微机原理考研真题主要包括选择题和简答题两种题型。

1. 选择题选择题是南邮微机原理考研真题中最常见也是最基础的题型。

考生需要从给出的选项中选择正确答案。

选择题主要涉及计算机原理中的知识点,如计算机的基本组成、存储器层次结构、指令的执行过程等。

下面是一个例子:题目:在多道程序环境下,若按照时间片轮转的方式为每个程序分配10ms的执行时间,则每秒钟能够执行最多多少道程序?A. 10B. 100C. 1000D. 10000答案:B. 1002. 简答题简答题是南邮微机原理考研真题中较为复杂的题型,要求考生用文字解答问题,充分展示对计算机原理的理解和应用能力。

简答题主要涉及计算机体系结构、指令系统、CPU等内容。

下面是一个例子:题目:请简述流水线技术在CPU中的应用,并列举三个流水线冒险和解决方法。

解答:流水线技术是一种有效提高CPU运行效率的技术。

在CPU中,流水线将指令的执行过程划分为多个阶段,使得不同阶段的指令可以并行执行。

流水线技术可以提高指令的吞吐量和执行效率。

然而,流水线也会面临一些问题,即流水线冒险。

流水线冒险主要包括结构冒险、数据冒险和控制冒险。

1) 结构冒险:多个指令需要访问同一硬件资源,导致资源冲突。

解决方法包括同时访问、等待和重排等。

2) 数据冒险:后续指令依赖前一指令的运算结果,但前一指令的结果尚未产生。

解决方法包括数据旁路、提前加载和延迟加载等。

3) 控制冒险:指令间的转移关系导致流水线的重新调整,降低执行效率。

南邮通信原理实验

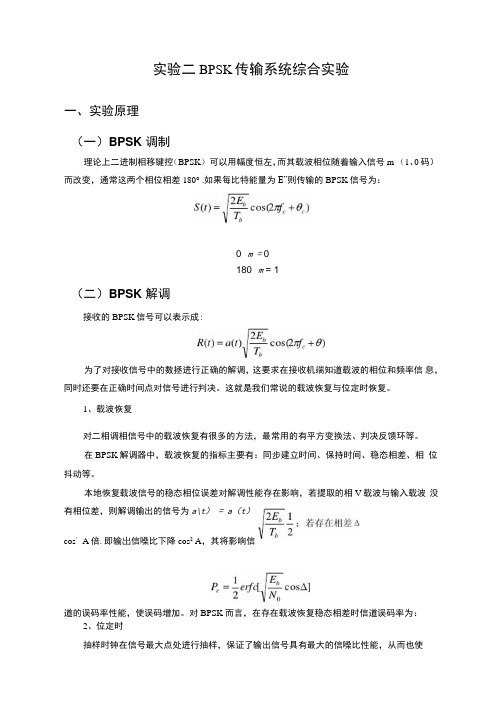

实验二BPSK传输系统综合实验一、实验原理(一)BPSK 调制理论上二进制相移键控(BPSK)可以用幅度恒左,而其载波相位随着输入信号m (1、0 码)而改变,通常这两个相位相差180° .如果每比特能量为E”则传输的BPSK信号为:0°m = 0180°m = 1(二)BPSK 解调接收的BPSK信号可以表示成:为了对接收信号中的数拯进行正确的解调,这要求在接收机端知道载波的相位和频率信息,同时还要在正确时间点对信号进行判决。

这就是我们常说的载波恢复与位定时恢复。

1、载波恢复对二相调相信号中的载波恢复有很多的方法,最常用的有平方变换法、判决反馈环等。

在BPSK解调器中,载波恢复的指标主要有:同步建立时间、保持时间、稳态相差、相位抖动等。

本地恢复载波信号的稳态相位误差对解调性能存在影响,若提取的相V载波与输入载波没有相位差,则解调输出的信号为a\t) = a(t)cos: A倍.即输岀信噪比下降cos2 A,其将影响信道的误码率性能,使误码增加。

对BPSK 而言,在存在载波恢复稳态相差时信道误码率为:2、位定时抽样时钟在信号最大点处进行抽样,保证了输出信号具有最大的信噪比性能,从而也使误码率较小。

在刚接收到BPSK信号之后,位左时一般不处于正确的抽样位置,必须采用一左的算法对抽样点进行调整,这个过程称为位左时恢复。

常用的位左时恢复有:滤波法、数字锁相环等。

最后,对通信原理综合实验系统中最常用的几个测量方法作一介绍:眼图、星座图与抽样判决点波形。

1、眼图:利用眼图可方便直观地估讣系统的性能。

示波器的通道接在接收滤波器的输出端,调整示波器的水平扫描周期,使其与接收码元的周期同步。

在荧光屏上看到显示的图型很像人的眼睛,所以称为眼图。

2、星座图:与眼图一样,可以较为方便地估计出系统的性能,同时它还可以提供更多的信息,如I、Q支路的正交性、电平平衡性能等。

星座图的观察方法如下:用一个示波器的一个通道接收I支路信号,另一通道接Q支路信号,将示波器设置成X-Y方式。

南邮微机原理实验报告资料

COUNT EQU $-STR2

EXTRA ENDS

CODE SEGMENT USE16

ASSUME CS:CODE,DS:DATA,ES:EXTRA

BEG: MOV AX,DATA

MOV DS,AX

MOV AX,EXTRA

MOV ES,AX

MOV CX,COUNT

源程序:

.586

DATA SEGMENT USE16

MESG DB 'What is your name?$'

MESG2 DB '?(Y/N)$'

BUF DB 30

DB ?

DB 30 DUP(?)

DATA ENDS

CODE SEGMENT USE16

ASSUME CS:CODE,DS:DATA

BEG: MOV AX,DATA

七、教师评阅

日期:

DATA ENDS

CODE SEGMENT USE16

ASSUME CS:CODE,DS:DATA

BEG: MOV AX,DATA

MOV DS,AX

MOV ES,AX

MOV CX,5

LL1: MOV MESG+5,0DH

MOV MESG+6,0AH

MOV MESG+7,'$'

CALL DISP

MOV MESG+5,0

MOV DI,OFFSET STRING

MOV CX,LENS

CLD

AGA: REPNE SCASB

JNZ NEXT

MOV FLAG,1

MOV SI,DI

DEC SI

南邮通信原理 实验二 BPSK_BDPSK 传输系统综合实验 (2)

实验一AMI/HDB3码型变换一、实验原理AMI码的全称是传号交替反转码。

这是一种将消息代码0(空号)和1(传号)按如下规则进行编码的码:代码的0仍变换为传输码的0,而把代码中的1交替地变换为传输码的+1、–1、+1、–1…由于AMI码的传号交替反转,故由它决定的基带信号将出现正负脉冲交替,而0电位保持不变的规律。

由此看出,这种基带信号无直流成分,且只有很小的低频成分,因而它特别适宜在不允许这些成分通过的信道中传输。

AMI码除有上述特点外,还有编译码电路简单及便于观察误码情况等优点,它是一种基本的线路码,并得到广泛采用。

但是,AMI码有一个重要缺点,即接收端从该信号中来获取定时信息时,由于它可能出现长的连0串,因而会造成提取钟时的困难。

为了保持AMI码的优点而克服其缺点,人们提出了许多种类的改进AMI码,HDB3码就是其中有代表性的一种。

HDB3码的全称是三阶高密度双极性码。

它的编码原理是这样的:先把消息代码变换成AMI码,然后去检查AMI码的连0串情况,当没有4个以上连0串时,则这时的AMI码就是HDB3码;当出现4个以上连0串时,则将每4个连0小段的第4个0变换成与其前一非0符号(+1或–1)同极性的符号。

显然,这样做可能破坏“极性交替反转”的规律。

这个符号就称为破坏符号,用V符号表示(即+1记为+V, –1记为–V)。

为使附加V符号后的序列不破坏“极性交替反转”造成的无直流特性,还必须保证相邻V符号也应极性交替。

这一点,当相邻符号之间有奇数个非0符号时,则是能得到保证的;当有偶数个非0符号时,则就得不到保证,这时再将该小段的第1个0变换成+B或–B符号的极性与前一非0符号的相反,并让后面的非0符号从V符号开始再交替变化。

虽然HDB3码的编码规则比较复杂,但译码却比较简单。

从上述原理看出,每一个破坏符号V总是与前一非0符号同极性(包括B在内)。

这就是说,从收到的符号序列中可以容易地找到破坏点V于是也断定V符号及其前面的3个符号必是连0符号,从而恢复4个连0码,再将所有–1变成+1后便得到原消息代码。

南邮微机原理

ADS:地址选通信号(输出) 该信号由1 → 0,表白地址线和总线定义

信号(M/IO,W/R,D/C)均为有效可用。

Pentium 处理器旳外部引脚

RDY:准备就绪信号(输入) 该信号由外电路产生→ X86

RDY=0,表白外部电路(存储器、I/O接口)已经做好 数据W/R旳准备,能在要求时间内完毕数据旳读写。 RDY=1,表白存储器或I/O不能在要求时间内完毕数 据旳读/写,请CPU延长总线周期。

PCI 总 线

主板上旳 PCI插槽

(2)AGP(Accelerate Graphics Port) 图形 加速接口 P.189

AGP接口是一种显示卡专用旳局部总线。严格旳 说,AGP不能称为总线,它与PCI总线不同,因为 它是点对点连接,即连接控制芯片和AGP显示卡, 但在习惯上我们依然称其为AGP总线。

ISA (AT) 总 线

GND RESET DRV

+5V IRQ9

-5V DRQ2 -12V 0WS +12V GND

SMEMW SMEMR

IOW IOR DACK3 DRQ3

DACK1 DRQ1

REFRESH CLK IRQ7 IRQ6 IRQ5 IRQ4 IRQ3

DACK2 T/C

BALE +5V OSC GND

BE0~BE3 A2~A31 M/IO、D/C

W/R RDY

D0~D31

T1 T2 TW T1 T2 TW T1

读

写

有等待状态总线周期

Pentium 处理器旳外部引脚

6.总线仲裁信号

(1)HOLD:总线保持祈求(输入) (2)HLDA:总线保持响应(输出)

(完整版)南邮微机原理实验二

;从BUF单元开始存有一字符串(长度<255),编程实现统计该字符串中的ASCII码在42H~45H之间的字符个;数,并将统计结果以二进制形式显示在屏幕。

;DATA SEGMENTBUF DB 255DB ?DB 255 DUP(?)crlf db 0dh,0ah,24h ;回车换行n db 0 ;统计的字符数DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATABEG:MOV AX,DATAMOV DS,AXMOV AH,0AHMOV DX,OFFSET BUFINT 21Hmov ah,9mov dx,offset crlfint 21hMOV SI,OFFSET BUF INC SIMOV CL,[SI]MOV Ch,0inc siLAST1:mov al,[si]cmp al,42hjb no_1cmp al,45hja no_1inc nno_1:inc siloop LAST1mov al,nMOV CX,8d_next:roL aL,1push axmov ah,2jc disp_1mov dl,'0'jmp dispdisp_1:mov dl,'1'disp:int 21hpop axloop d_nextMOV AH,4CHINT 21HCODE ENDSEND BEG追问(⊙o⊙)…我的程序没救了?我想知道我的程序哪边有问题回答你的程序问题不少。

不好意思,暂无时间详细叙述!追问好吧、、、谢谢你了还有昨天你的程序我没运行出来。

回答我是用MASM5.0 编译的。

没问题。

南邮 微机原理接口技术课后习题答案

第一章作业1.(1)29.6875(2)10010011 93(3)940(4)01100000(5)FF -5B(6)原码-0E 补码-72反码-71无符号数8E(7)(a)补码结果01000101B,69无溢出(d)补码结果10001010B,-118有溢出第二章作业5.32位:EAX EBX ECX EDX ESP EBP EDI ESI16位:AX BX CX DX SP BP DI SI8位:AH BH CH DH AL BL CL DL9.存储空间为1M。

先将该单元所在的段寄存器的16位段地址值左移4位,得到一个20位的值,再加上16位的段内偏移量,就形成了20位的物理地址。

或者段基址*16+偏移地址10.89832H第三章作业1.(1)179B8H(2)2F636H (3)586C4H (4)2FE00H(1)XOR AH,0F0H(2)XOR BX,0F00FH(3)AND CX,0FFF0H5.(1)方法一:MOV AL, FIRSTXCHG SECOND, ALMOV FIRST, ALMOV AL, FIRST+1XCHG SECOND+1, ALMOV FIRST+1, AL方法二:MOV AX, WORD PTR FIRST XCHG AX, WORD PTR SECOND MOV WORD PTR FIRST, AX (2)PUSH WORD PTR FIRST PUSH WORD PTR SECOND POP WORD PTR FIRSTPOP WORD PTR SECOND堆栈操作示意图如下:6. 6601H。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.1 程序修改

.486

DATA SEGMENT USE16

SUM DB ?,?

MESG DB '25+9='

DB 0,0,'$'

N1 DB 9,0F0H

N2 DB 25

DATA ENDS

CODE SEGMENT USE16 ASSUME CS:CODE,DS:DATA BEG: MOV AX,DATA

MOV DS,AX

MOV BX,OFFSET SUM

MOV AH,N1

MOV AL,N2

ADD AH,AL

MOV [BX],AH

CALL CHANG

MOV AH,9

MOV DX,OFFSET MESG

INT 21H

MOV AH,4CH

INT 21H

CHANG PROC

LAST: CMP BYTE PTR [BX],10 JC NEXT

SUB BYTE PTR[BX],10

INC BYTE PTR [BX+7]

MOV AH, BYTE PTR[BX]

JMP LAST

NEXT: MOV DX,WORD PTR SUM ADD [BX+8],DX

ADD BYTE PTR [BX+7],30H

ADD BYTE PTR [BX+8],30H RET

CHANG ENDP

CODE ENDS

END BEG

2.3.4从数据段NUM单元开始存有9个有符号数,并编写一个程序实现:找出最小值存放到数据段MIN单元,并将负数的个数以十进制的形式显示在屏幕上。

.486

DATA SEGMENT USE16

NUM DB -8,-44,-88,-37,2,-1,8,-26,-18

MIN DB ?

AB DB '0'

DATA ENDS

CODE SEGMENT USE16

ASSUME CS:CODE , DS:DATA

BEG: MOV AX,DATA

MOV DS,AX

MOV BX,OFFSET NUM

MOV CH,0

MOV CL,9

AGAIN: CMP BYTE PTR [BX] ,0

JG NEXT1

INC AB

CMP BYTE PTR [BX], CH

JG NEXT1

MOV CH,BYTE PTR [BX]

NEXT1: INC BYTE PTR BX

DEC CL

JNE AGAIN

MOV MIN,CH

MOV AH,2

MOV DL,AB

INT 21H

MOV AH,4CH

INT 21H

CODE ENDS

END BEG

.486

DATA SEGMENT USE16

BUF1 DB '123456'

BUF2 DB '000000'

BUF3 DB 'Please input communication words:',0DH,0AH,'$' BUF4 DB 3

OUT1 DB 'ERRORS',0DH,0AH,'$'

OUT2 DB 'RIGHT',0DH,0AH,'$'

OUT3 DB '*','$'

OUT4 DB 0DH,0AH,'$'

DATA ENDS

CODE SEGMENT USE16

ASSUME CS:CODE,DS:DATA,ES:DATA BEG: MOV AX,DATA

MOV DS,AX

MOV ES,AX

MOV AH,00H

MOV AL,3

INT 10H

LAST1:LEA SI,BUF1

LEA DI,BUF2

MOV BX,OFFSET BUF2

MOV CX,6

MOV AH,09H

LEA DX,BUF3

INT 21H

LAST: MOV AH,07H

INT 21H

MOV BYTE PTR [BX],AL

INC BX

MOV AH,09H

MOV DX,OFFSET OUT3

INT 21H

LOOP LAST

MOV AH,09H

LEA DX,OUT4

INT 21H

MOV CX,6

CLD

REPE CMPSB

JZ EXIT

MOV AH,09H

LEA DX,OUT1

INT 21H

DEC BUF4

JZ LAST2

JMP LAST1

EXIT: MOV AH,09H

LEA DX,OUT2

INT 21H

LAST2:MOV AH,4CH

INT 21H

CODE ENDS

END BEG。