32位PowerPC构架通用寄存器分析及总结一

32位PowerPC构架通用寄存器分析及总结一

32位PowerPC构架通用寄存器分析及总结一第一部分 32位 PowerPC构架下寄存器概述32 位PowerPC构架寄存器模型可以分成三个类级别:UISA,VEA,OEA,我们根据这三个级别把PowerPC所使用的所有寄存器分为三类:第一类:用户指令集构架(UISA-User Instruction Set Architecture)下所使用的寄存器;第二类:虚拟环境构架(VEA-Virtual Environment Architecture)下所使用的寄存器;第三类:操作系统环境(OEA-Operating Environment Architecture)下所使用的寄存器;PowerPC指令集构架为所有的算术逻辑运算指令定义了“寄存器到寄存器”格式的指令,这些指令的操作数来自或者来自于寄存器,或者来自于指令中的立即数。

而对于“三寄存器”格式的指令,PowerPC指令集定义其中一个寄存器用来存目的操作数,另外两个寄存器用来存放源操作数。

这样的话,存放源操作数的寄存器还可以被其它指令使用,从而减少了某些操作的指令数目。

并且对于访问寄存器,PowerPC构架定义了明确的load和store访存指令(这是RISC指令集的典型特点)。

备注:寄存器中的保留位允许软件写任何值(其实就是0或者1),但是读出来的值,未必是我们写出来的值。

它的值依赖于具体的执行系统。

接下来,我们分别来介绍这三类寄存器。

第二部分 UISA寄存器集合用户模式下的寄存器可以被所有的用户级软件和特权级软件所使用,它包含以下的寄存器:32个通用寄存器GPRs(General-purpose registers):GPR0-GPR31;32个浮点寄存器FRPs(Floating-point registers):FPR0-FPR31;1个条件寄存器:CR(Condition register);1个XER寄存器;1个LR(Link register)寄存器;1个CTR(Count register)寄存器;1个浮点状态控制寄存器:FPSCR(Floating-point status and control register);备注:不管是单精度数还是双精度数,在浮点寄存器中都是以双精度格式存储。

powerpc寄存器学习笔记

powerpc寄存器学习笔记今天谈一下E500中的系统级寄存器,也就是在内核态可以访问的寄存器,主要给操作系统用的。

这里主要说的是比较通用的几个寄存器,与中断,Cache和MMU有关的将在后面谈到这些内容的时候涉及到。

首先说一下访问系统级寄存器的指令:mfspr和mtspr。

E500会对各个寄存器进行编址,一般指令形式就是“mtspr 268, r3”或者“mfspr r3, 268”。

MSR(Machine State Register)寄存器。

用于设置CPU核心的状态,初始化CPU时第一个设置的寄存器。

不过这个寄存器不能通过mfspr/mtspr指令对访问,有一对特殊的指令mfmsr/mtmsr。

其中有几个重要的位需要提一下:UCLE(User-mode Cache Lock Enable,第37位)。

为1时程序运行在用户模式也可以锁定Cache行。

SPE(SPE Enable,第38位)。

为1时使能SPE。

WE(Wait State Enable,第45位)。

与HID0寄存器的DOZE,NAP和SLEEP位联合使用可以设置E500进入等待模式。

CE(Critical Enable,第46位),ME(Machine Check Enable,第51位),DE(Debug Interrupt Enable,第54位)。

用于使能和关闭Critical异常,Machine check异常和Debug异常。

EE(External Enable,第48位)。

为1时使能外部中断,为0时屏蔽外部中断。

当处理器进入中断处理时会自动屏蔽该位。

使用方法与MIPS的SR(IE)位很象。

同时E500还提供了wrtee和wrteei 指令对该位进行修改,就像MIPS中的ei与di指令。

PR(第49位)。

为0表示处理器在内核模式,为1表示处理器在用户模式。

IS,DS(第58,59位)。

E500支持两个地址空间——0和1。

32位PowerPC构架通用寄存器分析及总结三

32位PowerPC构架通用寄存器分析及总结三4.6SR(Segment Registers)寄存器OEA定义了16个32位的SR寄存器,段寄存器SR可以使用mtsr/mfsr,mtsrin/mfsrin指令进程访问。

随着CR[0]位(我们称之为T位)的值的不同,CR寄存器有两种不同的格式。

当T位为1时格式如下:CR[1]位:系统模式保护位CR[2]位:用户模式保护位CR[3]位:不可执行保护位CR[4:7]位:保留位CR[8:31]位:VSID位,我们在4.5节页面地址映射中已经看到该位段的作用。

当T位为0时格式如下:CR[1]位:系统模式保护位CR[2]位:用户模式保护位CR[3]位:不可执行保护位CR[3:11]位:Bus unit IDCR[12:31]位:Device-specific data for I/O controller备注:这个位段,我现在不清楚,暂时附上datasheet原文,以后再修改O(∩_∩)O~4.7 DAR(Data Address Register)寄存器存放访存指令产生的引发中断的有效地址,比较简单。

格式如下:4.8 SPRG0–SPRG3寄存器提供给操作系统使用,格式如下:SPRG0:操作系统可能会加载一个独立的物理地址到该寄存器中,来标识一个内存区域是第一级的中断句柄专用的。

SPRG2:可以被第一级的中断来保存通用寄存器的内容,该内容可以作为内存中保存其它通用寄存器的基地址。

SPRG2和SPRG3可以在操作系统需要时使用!备注:E600有8个SPRGs寄存器。

4.9 DSISR寄存器用来决定DSI中断的中断源,格式如下:4.10 SRR0(Machine Status Save/Restore Register 0)寄存器当发生中断时,SRR0用来保持中断发生的那一刻MSR的状态,当中断返回结束执行rfi指令时,SRR0用来恢复MSR寄存器的值,它也可以用来保持系统调用之前的那条指令的有效地址,当系统中断结束时会执行rfi指令,汇编SPR0保持的地址赋值给NIA(Next Instruction Address)寄存器(也就是我们通常说的PC寄存器)格式如下:4.11 SRR1(Machine Status Save/Restore Register 1)该寄存器同4.104.12 FPECR(Floating-Point Exception Cause Register)FPECR寄存器用来支持产生浮点中断的原因。

32位PowerPC常用指令集总结

32位PowerPC常用指令集总结第一部分PowerPC 精简指令集计算机(RISC)简介PowerPC 体系结构是一种精减指令集计算机(Reduced Instruction Set Computer,RISC)体系结构,定义了200 多条指令。

PowerPC 之所以是RISC,原因在于大部分指令在一个单一的周期内执行,而且通常只执行一个单一的操作(比如将内存加载到寄存器,或者将寄存器数据存储到内存)。

PowerPC 体系结构分为三个级别(或者说是“book”)。

通过对体系结构以这种方式进行划分,为实现可以选择价格/性能比平衡的复杂性级别留出了空间,同时还保持了实现间的代码兼容性。

Book I. 用户指令集体系结构(Power ISA User Instruction Set Architecture)定义了通用于所有PowerPC 实现的用户指令和寄存器的基本集合。

这些是非特权指令,为大多数程序所用。

Book II. 虚拟环境体系结构(Power ISA Virtual Environment Architecture)定义了常规应用软件要求之外的附加的用户级功能,比如高速缓存管理、原子操作和用户级计时器支持。

虽然这些操作也是非特权的,但是程序通常还是通过操作系统调用来访问这些函数。

Book III. 操作环境体系结构(Power ISA Operating Environment Architecture)定义了操作系统级需要和使用的操作。

其中包括用于内存管理、异常向量处理、特权寄存器访问、特权计时器访问的函数。

Book III 中详细说明了对各种系统服务和功能的直接硬件支持。

由于我目前手上的开发板是基于e600内核,所以我在学习PowerPC指令集的过程中,顺便总结了e600内核常用的指令集,如果大家发现我总结的指令集有错误或者不准确的地方,欢迎留言指出来,O(∩_∩)O~第二部分e600指令集飞思卡尔的e600内核实现了booke内核构架中64位指令集的中的32位指令(即在e600的32位寄存器中,第0位相当于booke中的64寄存器的第32位,第31位相当于booke中64寄存器的第63位),E600内核采用大端编码方式,指令的第0位是MSB(Most Significant Bit)位,第31位是LSB(Least Significant Bit)。

[整理]寄存器详细讲解

![[整理]寄存器详细讲解](https://img.taocdn.com/s3/m/2562f8711fb91a37f111f18583d049649b660e6f.png)

[整理]寄存器详细讲解-------------寄存器32位CPU的寄存器结构寄存器是中央处理器内的组成部分。

寄存器是有限存贮容量的高速存贮部件,它们可用来暂存指令、数据和位址。

在中央处理器的控制部件中,包含的寄存器有指令寄存器(IR)和程序计数器(PC)。

在中央处理器的算术及逻辑部件中,包含的寄存器有累加器(ACC)。

目录编辑本段寄存器英文名称:Register寄存器寄存器是内存阶层中的最顶端,也是系统获得操作资料的最快速途径。

寄存器通常都是以他们可以保存的位元数量来估量,举例来说,一个“8 位元寄存器”或“32 位元寄存器”。

寄存器现在都以寄存器档案的方式来实作,但是他们也可能使用单独的正反器、高速的核心内存、薄膜内存以及在数种机器上的其他方式来实作出来。

寄存器通常都用来意指由一个指令之输出或输入可以直接索引到的暂存器群组。

更适当的是称他们为“架构寄存器”。

例如,x86 指令集定义八个32 位元寄存器的集合,但一个实作x86 指令集的CPU 可以包含比八个更多的寄存器。

寄存器是CPU内部的元件,寄存器拥有非常高的读写速度,所以在寄存器之间的数据传送非常快。

编辑本段分类数据寄存器- 用来储存整数数字(参考以下的浮点寄存器)。

在某些简单/旧的CPU,特别的数据寄存寄存器器是累加器,作为数学计算之用。

地址寄存器- 持有存储器地址,以及用来访问存储器。

在某些简单/旧的CPU里,特别的地址寄存器是索引寄存器(可能出现一个或多个)。

通用目的寄存器(GPRs)- 可以保存数据或地址两者,也就是说他们是结合数据/地址寄存器的功用。

浮点寄存器(FPRs) - 用来储存浮点数字。

常数寄存器- 用来持有只读的数值(例如0、1、圆周率等等)。

向量寄存器- 用来储存由向量处理器运行SIMD(Single Instruction, Multiple Data)指令所得到的数据。

特殊目的寄存器- 储存CPU内部的数据,像是程序计数器(或称为指令指针),堆栈寄存器,以及状态寄存器(或称微处理器状态字组)。

PowerPC汇编指令集简析

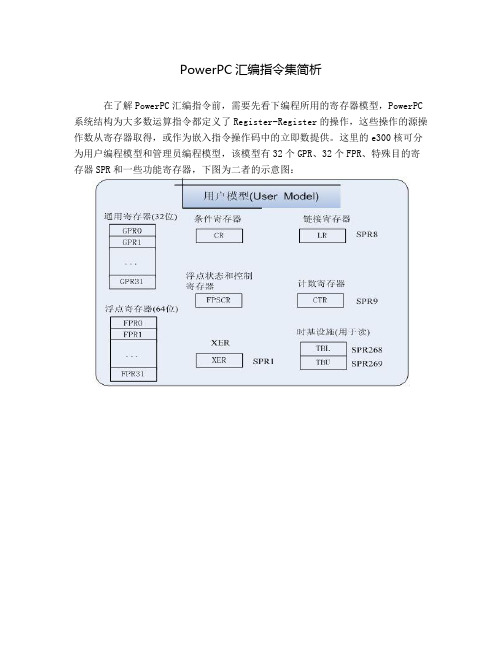

PowerPC汇编指令集简析在了解PowerPC汇编指令前,需要先看下编程所用的寄存器模型,PowerPC 系统结构为大多数运算指令都定义了Register-Register的操作,这些操作的源操作数从寄存器取得,或作为嵌入指令操作码中的立即数提供。

这里的e300核可分为用户编程模型和管理员编程模型,该模型有32个GPR、32个FPR、特殊目的寄存器SPR和一些功能寄存器,下图为二者的示意图:上面这些寄存器可能不太好理解,因为名字和Intel汇编不一样,其实,可以这样理解,GPR就相当于EAX/EBX/ECX,而CTR则完全就是ECX的功能,是吧?区别就是没有堆栈而已咯。

CR被分为8段,每段4位,分别代表LT、GT、EQ和SO(小于、大于、等于和溢出);LR用于记录跳转地址;特殊寄存器XER用于记录溢出和进位标志;FPSCR用于记录浮点运算类型和异常等。

再看下指令集,大部分的CPU指令集可分为:数据读写、数值计算、流程控制和设备管理四个部分,由于PowerPC使用RISC,指令字长为32bit,Endian一般是可调的,默认为大端,另外,PowerPC没有栈,所以程序需要自己实现相关操作。

首先为运算和逻辑指令,列举如下:它们与通用寄存器有关,源数据来自GPR 或16 位立即数,目的是GPR 寄存器,操作为32 位,GPR 中存放32 位更新数据。

大多数指令都可以根据字面意思理解其作用,注意还有一个“cntlzw”指令,意为计算字中的第一个0,用于在一个字中找到1时将一个指令中的0的数量找出,它在决定例外寄存器中最高优先服务时有用。

下面是数据读写指令,它们对数据在存储器中核通用寄存器中的传送很有用,若数据小于传送长度(单字,半字或字节),指令会使数据变位为32位,将不同位填0或符号扩展。

指令列举如下:这里需要注意的是上面列举的lbz和lhz两个指令并不完全等同于moval,[ebx]和mov ax,[ebx+10]这两个,因为前面两个是将字节和半字加载到r3时还清空了高位,而后两条指令只是加载数据到eax,并不会清空高位。

32位PowerPC经常使用指令集总结

32位PowerPC常用指令集总结第一部分PowerPC 精简指令集计算机(RISC)简介PowerPC 体系结构是一种精减指令集计算机(Reduced Instruction Set Computer,RISC)体系结构,定义了200 多条指令。

PowerPC 之所以是RISC,原因在于大部分指令在一个单一的周期内执行,而且通常只执行一个单一的操作(比如将内存加载到寄存器,或者将寄存器数据存储到内存)。

PowerPC 体系结构分为三个级别(或者说是“book”)。

通过对体系结构以这种方式进行划分,为实现可以选择价格/性能比平衡的复杂性级别留出了空间,同时还保持了实现间的代码兼容性。

Book I. 用户指令集体系结构(Power ISA User Instruction Set Architecture)定义了通用于所有PowerPC 实现的用户指令和寄存器的基本集合。

这些是非特权指令,为大多数程序所用。

Book II. 虚拟环境体系结构(Power ISA Virtual Environment Architecture)定义了常规应用软件要求之外的附加的用户级功能,比如高速缓存管理、原子操作和用户级计时器支持。

虽然这些操作也是非特权的,但是程序通常还是通过操作系统调用来访问这些函数。

Book III. 操作环境体系结构(Power ISA Operating Environment Architecture)定义了操作系统级需要和使用的操作。

其中包括用于内存管理、异常向量处理、特权寄存器访问、特权计时器访问的函数。

Book III 中详细说明了对各种系统服务和功能的直接硬件支持。

由于我目前手上的开发板是基于e600内核,所以我在学习PowerPC指令集的过程中,顺便总结了e600内核常用的指令集,如果大家发现我总结的指令集有错误或者不准确的地方,欢迎留言指出来,O(∩_∩)O~第二部分e600指令集飞思卡尔的e600内核实现了booke内核构架中64位指令集的中的32位指令(即在e600的32位寄存器中,第0位相当于booke中的64寄存器的第32位,第31位相当于booke中64寄存器的第63位),E600内核采用大端编码方式,指令的第0位是MSB(Most Significant Bit)位,第31位是LSB(Least Significant Bit)。

PowerPC体系结构学习笔记之内存管理

PowerPC体系结构学习笔记之内存管理(1)——E500MMU简介E500采用了两级MMU机制,L1-MMU和L2-MMU,以及一些辅助寄存器和指令来实现虚实地址的转换。

E500与其他PowerPC处理器相比的一个最大不同就是,E500不能禁止虚实地址转换,并且支持两个地址空间,分别是地址空间0与地址空间1。

其实这点有些类似于MIPS,除了直接通过虚拟地址来区分以外,MIPS处理器也没有机制禁止/启用地址翻译。

L1-MMU包含I-L1VSP,D-L1VSP,I-L1TLB4K和D-L1TLB4K。

I-L1VSP和D-L1VSP含有4个条目,采用全相连结构。

I-L1TLB4K和D-L1TLB4K含有64个条目,采用4路组相连结构。

L2-MMU包含TLB0和TLB1。

其中TLB0含有256个条目,采用2路组相连结构。

TLB1含有16个条目,采用全相连结构。

TLB0用来进行页式映射,TLB1用来处理段式映射。

PowerPC体系结构学习笔记之内存管理(2)——E500虚拟地址与MMU结构在E500内核中将MMU分为两级有一下两个作用:L1-MMU的访问速度较快。

这个原理类似于Cache的原理。

L1-MMU采用哈佛结构,也就是程序地址空间与数据地址空间分离,可以提高地址转换的效率。

但是L2-MMU没有采用这种结构。

E500是一个32位的处理器,支持4GB的地址空间。

在内部使用41位的临时虚拟地址,组成如下:40 39 32 31 0AS PID EAAS:来自于MSR寄存器的IS或DS位。

所以,E500可以根据AS位将地址空间分为两种:地址空间0和地址空间1。

但是,Linux并没有使用这个功能。

kernel和用户空间的代码,数据都在地址空间0中,即AS位一直是0。

PID:E500支持3个8位的PI的寄存器来保存进程的PID。

这点于MIPS的ASID作用一样。

但是,Linux并没有使用PID,在TLB中简单的忽略PID的检查,全部设为0。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

32位PowerPC构架通用寄存器分析及总结一第一部分 32位 PowerPC构架下寄存器概述32 位PowerPC构架寄存器模型可以分成三个类级别:UISA,VEA,OEA,我们根据这三个级别把PowerPC所使用的所有寄存器分为三类:第一类:用户指令集构架(UISA-User Instruction Set Architecture)下所使用的寄存器;第二类:虚拟环境构架(VEA-Virtual Environment Architecture)下所使用的寄存器;第三类:操作系统环境(OEA-Operating Environment Architecture)下所使用的寄存器;PowerPC指令集构架为所有的算术逻辑运算指令定义了“寄存器到寄存器”格式的指令,这些指令的操作数来自或者来自于寄存器,或者来自于指令中的立即数。

而对于“三寄存器”格式的指令,PowerPC指令集定义其中一个寄存器用来存目的操作数,另外两个寄存器用来存放源操作数。

这样的话,存放源操作数的寄存器还可以被其它指令使用,从而减少了某些操作的指令数目。

并且对于访问寄存器,PowerPC构架定义了明确的load和store访存指令(这是RISC指令集的典型特点)。

备注:寄存器中的保留位允许软件写任何值(其实就是0或者1),但是读出来的值,未必是我们写出来的值。

它的值依赖于具体的执行系统。

接下来,我们分别来介绍这三类寄存器。

第二部分 UISA寄存器集合用户模式下的寄存器可以被所有的用户级软件和特权级软件所使用,它包含以下的寄存器:32个通用寄存器GPRs(General-purpose registers):GPR0-GPR31;32个浮点寄存器FRPs(Floating-point registers):FPR0-FPR31;1个条件寄存器:CR(Condition register);1个XER寄存器;1个LR(Link register)寄存器;1个CTR(Count register)寄存器;1个浮点状态控制寄存器:FPSCR(Floating-point status and control register);备注:不管是单精度数还是双精度数,在浮点寄存器中都是以双精度格式存储。

示意图如下:2.1 通用寄存器GPRs32个32位通用寄存器主要用来操作整数数据,它们可以作为指令源寄存器和目的寄存器使用,使用起来比较简单,这里就不再相信介绍2.2 浮点寄存器FPRsPowerPC构架使用32个64位的浮点寄存器,这些寄存器可以在浮点指令中用作源操作数和目的操作数。

无论是单精度浮点数还是双精度浮点数在浮点寄存器中都是以双精度格式存储。

除了浮点比较指令之外,其他的浮点操作指令都是操作FPRs中的数据,然后把操作结果放入FPRs中,同时把浮点操作的状态信息存入FPSCR中;而浮点比较指令的结果一般会存放在CR寄存器的CR2字段中。

另外对于FPRs同存放在内存中的双精度输进行数据转存时,不需要格式转换;而对于FPRs 和放在在内存中的单精度数进行转存时需要格式转换;而且单精度指令操作FPRs中的数据时,必须把FPRs中的双精度格式的数据转化成单精度格式,单精度指令才能使用。

2.3 CR寄存器32位的CR寄存器可以反映某些操作的结果(比如cmp指令),协助测试和分支转移指令的执行。

CR寄存器用来存放指令执行之后的状态,该寄存器分为8个字段。

分别为CR0,CR1,…,CR7。

每个字段都由4bit组成。

各个字段CRn(n从0至7)都可以表示响应指令执行的结果:比如整数的加减及逻辑运算,使用CR0来存放状态,CR0的四个bit位的含义如下:CR0(0):用来表示LT(小于),当整型指令运算结果为负时置1;CR0(1):用来表示GT(大于),当整型指令运算结果为正时置1;CR0(2):用来表示EQ(等于),当整型指令运算结果为0时置1;CR0(3):用来表示SO(溢出),当整型指令运算结果溢出时置1;同理浮点数的运算使用CR1来保存运算状态,保存过程同上。

其实比较指令可以使用CR寄存器的全部的CRn(n从0至7)来保存运算的结果。

在使用CR 寄存器时,比较指令cmp之后都会有一个条件跳转指令,比如bc指令。

其中cmp指令可以指定由CR寄存器的CRn段来保存结构, cmpi指令就用BF字段来指定CRn字段,一般而言bc指令就会指向cmp中相同的CRn段来决定跳转。

下面的指令用来操作CR寄存器的各个CRn域:1:mtcrf用一个GPR的值来设置CR寄存器的CRn域;2:mcrf把CR寄存器的一个域CRn拷贝到另一个域CRm;3:mcrxr把XER寄存器的bit0-bit3拷贝到CR寄存器的一个域CRn4:mcrfs把指定的FPSCR寄存器的一个域拷贝到指定的CR寄存器的一个域CRn5:CR寄存器的CR0域存放整数指令的运算结果6:CR寄存器的CR1域存放浮点数指令的运算结果7:可以指定CR寄存器的任何一个域CRn来存放整数指令和浮点数指令的运算结果;2.3.1 对于CR寄存器的CR0域解释对于所有的整数指令比如addic. ,adni. 和andis.等(.表示Rc位置位),指令的执行结果将会反映在CR0位上。

CR0[0:2]位根据整数指令的运算结构设定,CR[3]由XER[S0]位拷贝过来,四个bit位的含义上面已经讲过。

备注:我们不难想到,如果发生溢出,CR0的前三个bit就没有参考价值了。

2.3.2对于CR寄存器的CR1域对于所有的浮点运算指令(指令的Rc位置位),CR1将反映浮点运算指令的结果。

具体的说CR1[0:3]位拷贝自FPSCR[0:3],来反映浮点运算的异常状态。

2.3.3 对于指定的CRn域的解释对于比较指令而言,它们通常会自己指定一个CRn域来存放比较指令的运算结果。

比如对cmpi指令:cmpi BF,L,RA,SI语义:n <— BF表示的数值if L = 0 then a <—EXTS((RA)32:63)else a <—(RA)if a < EXTS(SI) then c <—0b100 //小于时设置CRn(0)为1else if a > EXTS(SI) then c <—0b010 //大于时设置CRn(1)为1else c <—0b001 //等于时设置CRn(2)为1CR寄存器中的:4×BF+32:4×BF+35 <- c || XER寄存器中SO位 //||表示字符连接解释:将寄存器RA与立即数SI进行比较,然后将比较指令产生的状态放入CR寄存器的不同字段中,CR寄存器有8个CRn字段(n从0至7),可以有三个bit位的BF段指定。

L表示是进行32位还是64的比较。

对于e600而言,只有L=0的比较。

2.4 FPSCR寄存器FPSCR寄存器的各个bit位的作用:1:记录浮点操作的异常2:记录浮点操作的结果的类型3:控制浮点操作的回旋模式(rounding mode)4:使能或者禁止异常报告FPSCR[0:23]是状态bit位,在浮点指令的执行单元完成时更新;FPSCR[24:31]是控制位;2.5 XER寄存器XER寄存器是用户模式寄存器,存放整数运算操作的进位,溢出信息以及特殊加载和存储指令lswd和stsws传输的字节数。

XER寄存器有三个有效位(SO-Summary Overflow,OV-Overflow,CA-Carry)和一个有效字段Byte countSO位:XER[0]位,该位为1表示算术指令曾经将OV位置1;CR寄存器的SO位就是复制了XER寄存器的SO位,SO位一旦被设置,就不会被清除,真到程序使用mtspr,mcrxr指令进行清除。

OV位:XER[1]位,表示有符合数的算术运算产生了溢出。

CA位:XER[2]位,表示无符号数运算产生了进位。

Byte count字段:XER[25:31]存放lswd和stsws传输的字节数。

2.6 LR寄存器LR寄存器用来存放函数的返回地址,某些转移指令可以自动的将LR寄存器赋值为该转移指令所在地址的下一个地址。

LR寄存器还可以用作bclr指令的目标地址,来实现长跳转。

示意图如下:备注:图中的blr 是 bclr 20, 0指令的助记符。

2.7 CTR指令CTR寄存器用来保存循环变量,并可以根据bclr的BO操作数来自动进行减1操作。

此外CTR寄存器还可用来保存bcctr指令的目标地址,用来实现长调转。

第三部分虚拟环境构架(VEA-Virtual Environment Architecture)寄存器集虚拟环境工具寄存器集只包含Time-Base寄存器组。

示意图如下:VEA寄存器组可以被所有的处于用户模式或者系统模式下的软件所访问,从VEA寄存器组的示意图我们可以看出,和UISA寄存器相比。

VEA寄存器只是引入了一个64位的结构体,它包含两个寄存器:TBU(Time Base Upper)寄存器和TBL(Time Base Lower)寄存器,这两个寄存器可以被用户模式和系统模式的指令访问。

在VEA环境中,用户模式下的应用程序仅能访问TB寄存器,而在操作系统环境构架(OEA)定义的系统模式下,系统模式指令可以写入TB寄存器。

TB寄存器组是存放了一个64bit的无符号整数,这个整数周期性的递增。

每次递增,TB中的TBL寄存器第31bit位加1,TB中计数器更新的周期与具体的操作相关,即它依赖于具体的实现。

TB 寄存器会以一种依赖于实现的频率周期性地增加,这个频率可能不是恒定的。

操作系统(OS)要负责确定更新频率是否发生了变化,以及对内部结构进行必要的调整。

小结一下:1:TB 寄存器是 64 位长的;2:每次更新都会增加 1;3:操作系统必须要能够确定更新频率;4:当 TB 达到自己的最大值时,就会溢出并从 0 重新开始。

此时没有明显的迹象,要交由操作系统进行处理。

5:OS 必须要在开机时对 TB 寄存器进行初始化。

备注:TB 寄存器自己并没有包含计算时间所需要的足够信息。

Power Architecture 规范将很多对TB 寄存器进行处理的责任都交给操作系统来完成,操作系统需要提供其他一些信息,例如更新频率、启动时的 Time Base 寄存器的值,等等。

整个计算机制非常迅速且高效。

关于TB寄存器的使用,更详细的内容可以参考:64 位 Linux 中 Power Architecture Time Base 的寄存器这篇文章写的很到位。

待续。