基于FPGA的语音识别前端算法研究实现

基于FPGA的卷积神经网络手写数字识别系统的实现共3篇

基于FPGA的卷积神经网络手写数字识别系统的实现共3篇基于FPGA的卷积神经网络手写数字识别系统的实现1随着科技的发展,人工智能已经成为人们生活中不可分割的一部分。

其中,深度学习是人工智能领域的一个热门话题。

而卷积神经网络作为深度学习的重要算法之一,其应用也愈加广泛。

本文将重点介绍基于FPGA的卷积神经网络手写数字识别系统的实现。

一、卷积神经网络简介卷积神经网络(Convolutional Neural Network, CNN)是一种前向反馈人工神经网络,是深度学习中常见的算法之一。

该网络主要用于图像识别、语音识别等领域。

卷积神经网络主要由输入层、隐藏层和输出层构成。

其中,隐藏层包括多个卷积层、池化层和全连接层。

卷积层是卷积神经网络中的核心层,它利用一组可学习的滤波器对输入的图像进行卷积操作,从而获得图像中的特征。

这些特征在后面的池化层和全连接层中都会用到。

池化层则对卷积层中获得的特征图进行降维处理,从而减少计算量。

常见的池化操作有最大池化和平均池化两种。

全连接层则将池化层中的特征图作为输入,进行分类判断。

全连接层的输出通常会经过一个激活函数。

二、FPGA简介FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,其具有高度灵活性和可重构性。

FPGA可以通过编程实现不同的电路功能,因此在高速、低功耗、高可靠等方面有着很强的优势。

在深度学习中,利用FPGA进行计算的方式可以大大提高计算速度和效率。

三、基于FPGA的卷积神经网络手写数字识别系统本文的识别系统采用了FPGA作为处理器,并使用卷积神经网络对手写数字进行识别,部分个人感想如下。

1. FPGA的搭建本次实验搭建使用的是Altera的CYCLONE II FPGA,需要先进行硬件电路的设计和代码实现。

硬件电路的设计可以使用VHDL或Verilog等HDL语言进行实现,代码实现则可以使用Quartus II或其他类似的软件进行集成。

语音识别的技术实现原理

语音识别的技术实现原理随着人工智能技术的不断发展,语音识别技术越来越成熟。

语音识别技术是指将人的语音信号转换为文字信号的过程。

这种技术已经广泛应用于智能家居、车载导航、医疗诊断等领域,为人们生活的方方面面带来了很多的方便。

语音识别的基本流程语音识别的基本流程包括:信号的获取、预处理、特征提取、语音识别、后处理和结果输出等环节。

这些环节的主要作用是,首先将人的语音信号录制下来,然后对信号进行预处理和特征提取,最终生成可供计算机处理的数学模型,从而实现语音识别。

信号获取语音信号的获取是语音识别技术实现的第一步。

在实际应用中,人们通常使用麦克风等设备采集语音信号,然后将信号传输到计算机中,由计算机对信号进行处理。

预处理语音信号的预处理是为了提高语音识别的准确率。

预处理包括去除杂音、增加信号的能量、滤波等处理方法。

例如,如果语音信号中包含明显的环境噪声,就需要进行噪声消除处理,以提高信号的清晰度和可分辨性。

特征提取语音信号的特征提取是为了将其转化为计算机可以处理的数学模型。

在这个过程中,需要从语音信号中提取出一些特殊的特征,例如频率、音量、节奏等,然后将这些特征映射到数学模型中。

常见的特征提取方法包括Mel 频率倒谱系数(MFCC)、傅里叶变换等。

语音识别语音识别是将语音信号转化为文字信号的过程。

这一过程是通过计算机算法来实现的。

计算机首先将处理后的语音信号转化为数学模型,然后应用统计学知识来计算每个可能的字或词的概率,从而选择最有可能的单词或语句。

最终,计算机将文字结果输出。

后处理语音识别的后处理是为了减少识别错误,提高识别准确率。

后处理可以使用语言模型、上下文信息等进行修正和优化,从而减少识别错误率和提高识别准确率。

结果输出结果输出是将结果呈现给用户的过程。

结果可以直接输出为文字,也可以通过合成语音的方式,将结果直接转化为人类可以听懂的语音。

在实际的应用中,一般会综合考虑应用场景、用户需求等因素,选择输出方式。

基于FPGA和DSP音频接口模块的设计与实现

2音频接 口模 块应用 实例

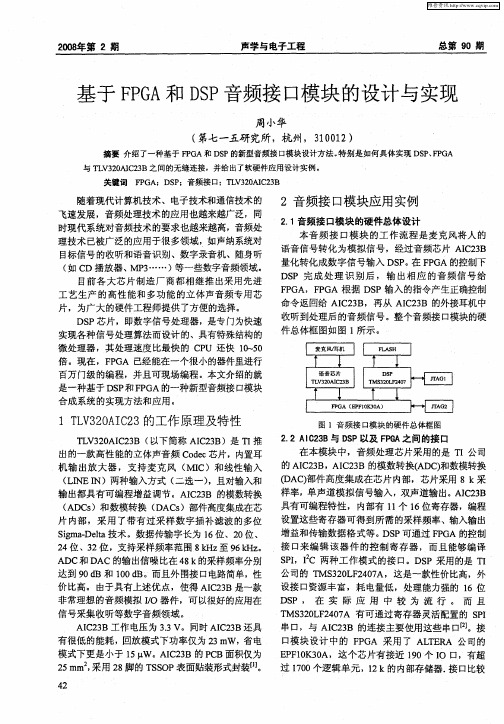

21 。 音频接 口模块的硬件总体设计 本音频接 口模块 的工 作流程是麦克风将人的 语音信号转化为模拟信号,经过音频芯片 AC 3 I2 B

量化转化成数字信号输入 DS 。 F G P 在 P A的控制下 D P 完 成处 理 识 别后 ,输 出相 应 的音频信 号给 S FG P A,F G 根 据 DS PA P输 入 的指 令产 生正确控制 命令返回给 A C 3 ,再从 A C 3 的外接耳机中 I2B I2 B 收听到处理后的音频信号。整个音频接 口模块的硬 件总体框 图如图 1 所示。

在本模块 中,音频处理芯片采用的是 T I公司 的 AC 3 AC 3 I2B, I2 B的模数转换( D ) A C和数模转换 (A ) D C 部件高度集成在芯片内部,芯片采用 8k 采 样率,单声道模拟信号输入 , 双声道输出。 I2 B AC 3 具有可编程特性 ,内部有 1 个 1 位寄存器 ,编程 1 6 设置这些寄存器可得到所需的采样频率、输入输出 增益和传输数据格式等 。 S 可通过 F G DP P A的控制 接 口来编 辑该器件 的控制 寄存器 ,而且能够编译

随着现代计算机技术、电子技术和通信技术的 飞速发展,音频处理技术的应用也越来越广泛,同 时现代系统对音频技术的要求也越来越高,音频处 理技术已被广泛的应用于很多领域 , 如声纳系统对 目标信号的收听和语音识别 、数字录音机、随身听 ( C 播放器 、 3 .)等一 些数字 音频领 域 。 如 D MP … . ・ 目前 各 大 芯 片 制 造 厂 商 都 相 继推 出采 用 先进 工 艺 生 产 的 高 性 能 和 多 功 能 的立 体 声 音频 专 用 芯 片,为广大的硬件工程师提供 了方便的选择。 DS P芯片,即数字信号处理器 ,是专门为快速 实现各种信号处理算法而设计 的、具有特殊结构的 微处理器 ,其处理速度 比最快的 C U 还快 1 ̄ 0 P 0 5 倍。现在 ,F G 已经能在一个很小的器件里进行 PA 百万 门级的编程,并且可现场编程。本文介绍的就 是一种基于 D P P A的一种新型音频接 口 S 和F G 模块 合成系统的实现方法和应用。

语音识别中的端到端技术研究

语音识别中的端到端技术研究语音识别是指将口述语音转化为文本的过程。

它是如今最热门的研究领域之一,因为语音识别可以提高我们的效率,方便人们的日常工作和生活。

在此领域,端到端技术的出现对于语音识别的开展和研究起到了巨大的推动作用。

什么是端到端技术?端到端(End-to-End)技术是一种新兴的技术领域,是指一个系统能够完整地处理输入信息并输出期望的结果,从而所有处理步骤都由一个统一的系统实现,而不是由多个单元(如系统和模块)协同工作实现的。

在语音识别中,端到端技术指的是通过机器学习算法和神经网络来实现从音频输入到文本输出的完整过程,省略了传统语音识别技术中需要用到的各种模块和中间环节,减少了错误和失误的发生,提高了识别的准确性和效率。

端到端技术的研究现状近年来,端到端技术在语音识别中的应用和研究快速兴起。

大量的研究机构和企业在这一领域积极投入了研究,并发布了许多高水平的论文和科研成果。

例如,2015年,谷歌的语音团队就发布了一篇名为“End-to-End Speech Recognition”的论文,其中提到了他们使用了一个经典的递归神经网络(RNN)作为识别器,取得了显著的成果。

这样的模型可以不需要词典和发音字典,直接学习从声学场景到文本的转换,可以适应不同的语言和方言,从而在离线语音识别领域中取得了不少成绩。

另外,因为英语相比其他语言更加规范,因此在端到端技术领域的研究中,也有不少重要成果。

2016年,IBM的语音团队就在NTIMIT数据集上发布了一篇名为“End-to-End Speech Recognition with Recurrent Neural Networks”的论文,他们使用长短时记忆(LSTM)网络,结合有限状态转移网络(FST)来提高准确性,将最优词图检索添加到最终的解码过程中。

这种系统还可以直接输入音频流,并逐帧输出一个连续的文字流。

端到端技术的优势传统的语音识别技术中,多阶段的算法需要多个子系统共同协作完成。

基于FPGA的神经网络硬件实现

基于FPGA的神经网络硬件实现随着和深度学习领域的快速发展,神经网络的规模和复杂性不断增加,对计算能力和效率的要求也越来越高。

传统的基于CPU和GPU的实现方式虽然可以实现大规模神经网络的训练和推理,但是存在着计算资源利用率低、功耗高等问题。

FPGA作为一种可编程逻辑器件,具有高度的灵活性和并行计算能力,可以被用来实现神经网络硬件加速器。

本文将介绍基于FPGA的神经网络硬件实现的相关技术和应用。

FPGA(Field Programmable Gate Array)是一种可以通过编程来配置其硬件资源的集成电路。

它由大量的可编程逻辑块和可编程互连资源组成,可以用来实现各种数字电路和算法。

与传统的ASIC和GPU相比,FPGA具有以下优点:可编程性:FPGA可以通过编程来配置其硬件资源,实现不同的算法和电路。

并行计算:FPGA由大量的可编程逻辑块和可编程互连资源组成,可以实现并行计算。

灵活性:FPGA不仅可以用来实现数字电路和算法,还可以用来实现模拟电路和信号处理算法。

低功耗:FPGA的功耗比CPU和GPU低得多,可以提高设备的续航能力和可靠性。

基于FPGA的神经网络硬件实现主要可以分为以下几个步骤:算法设计:根据实际应用需求,设计和实现神经网络模型,确定网络结构和参数。

数据流图设计:将神经网络模型转化为硬件可实现的数据流图,确定每个计算单元的计算方式和数据传输方式。

硬件描述语言编程:使用硬件描述语言(如Verilog或VHDL)编写程序,将数据流图转化为硬件电路。

硬件仿真与验证:使用仿真工具对硬件电路进行仿真测试,验证其正确性和性能是否达到预期。

硬件实现:将硬件电路加载到FPGA上,进行实际测试和性能优化。

基于FPGA的神经网络硬件加速器可以广泛应用于各种领域,如图像处理、语音识别、自然语言处理等。

以下是一个图像处理领域的应用案例:神经网络模型:YOLO(You Only Look Once)算法数据流图设计:将YOLO算法的卷积层、激活层和全连接层等计算单元转化为硬件可实现的数据流图。

基于机器学习的语音识别系统设计与实现

基于机器学习的语音识别系统设计与实现语音识别系统是指将语音信号转换为对应的文字或命令的技术系统。

近年来,随着机器学习技术的不断发展与应用,基于机器学习的语音识别系统得到了广泛的关注和研究。

本文将介绍基于机器学习的语音识别系统的设计与实现,并讨论其应用领域、关键技术和挑战。

一、应用领域基于机器学习的语音识别系统广泛应用于语音助手、智能音箱、电话语音识别、语音翻译等领域。

它能够实现方便快捷的人机交互,提高人们对计算机的操作和控制效率,推动智能化应用的发展。

二、系统设计与实现1. 数据采集与预处理语音识别系统的第一步是收集并预处理语音数据。

通常会采集大量的语音样本,包括来自不同说话人的不同语音单元,以确保系统的鲁棒性。

采集的语音数据需要经过预处理,包括语音分帧、语音去噪、音调归一化等步骤,以保证输入的语音数据质量。

2. 特征提取与表示特征提取是将语音信号转换为机器学习算法可接受的数学形式的过程。

常用的特征提取方法包括MFCC(Mel频率倒谱系数)和PLP(偏移谱线性预测系数)等。

这些特征能够捕捉语音信号的频谱特征,并且对噪声具有一定的鲁棒性。

3. 训练模型在语音识别系统中,常用的机器学习算法包括隐马尔可夫模型(HMM)和深度神经网络(DNN)。

通过使用带有标注的语音数据集进行模型训练,可以使系统逐渐学习到语音信号与文本之间的映射关系。

而在模型训练过程中,还可以利用大规模数据和GPU加速技术,以提高模型的准确性和性能。

4. 解码与后处理解码是将音频数据转换为对应的文本或命令的过程。

在解码阶段,语音识别系统会根据模型学习到的语音特征与文本之间的对应关系,选择最有可能的文本输出。

针对不同的场景,还可以应用后处理技术来进一步提升识别结果的准确性。

三、关键技术1. 深度学习随着深度学习技术的快速发展,特别是深度神经网络(DNN)在语音识别领域的广泛应用,语音识别系统的准确性和性能得到了极大的提升。

DNN能够自动提取高级特征并建模语音信号的复杂结构,从而实现更准确的语音识别。

HMM非特定人孤立词语音识别系统的FPGA实现

型, 是语音信号时变特征 的有效表示法 , 在话音处理 各个 领域 中得 到 了成 功 应用 [。 目前孤 立词 语 音识 2 】

别技术 已经 趋 于成熟 , 、 词 表 ( 中 小 词表 容 量 为 1 O~ 10个 ) 0 的识别 率 已经 达 到 9 %以上 , 立词 语 音识 8 孤 别技 术 已经 由 P C机 走 向嵌 入式 应 用 [。孤 立 词识 3 ]

2 0 牟g 2 08 1期

中图分类号 :P9 . T 3 14 文献标识码 : A 文章编 号 :09 52 20 )2— 09 4 10 —25 (08 1 0 8 —0

H MM 非 特定 人孤 立 词 语 音 识 别 系统 的 F G P A实现

万卫锋 ,赵 峰

( 上海交通 大学微电子学院 ,上海 204 ) 0 20

( A ) ae el . nr cl a o sc t i o eost f t e x at nadd oig ot V D bsdO t g E e ya e rtna oie wt vi ne,e u t co e d e nh o g c ei s a d h c a rer i n c n th

识别方法的不足 , 许多科研机构相继开始研发基于

非特定 人 的语 音识 别 芯 片 。20 美 国 T 公 司 开 00年 I 发 出 以 T S25x系列 D P为核心 的嵌入 式非 特定 M 304 S 人语音识 别 芯片 , 系 统 英 文 连 续 数字 串的识 别 率 该

为 9 . 3 条英文控制指令 的识别率为9 .%_, 82 4 %, 84 4 ]

( do o Mi ol t ne,l a J o n nvrt,Sa ga 04 , n ) S a ̄ f e e e o i s1 r e r s 啪I i i t gU iesy hn hi 0 20 O ̄ a a o i 2

基于深度学习的语音识别系统的研究与实现

基于深度学习的语音识别系统的研究与实现随着科技的不断发展,语音识别技术也得以迅速提升。

其中基于深度学习的语音识别系统不仅可以识别出口语,还可以识别手语、普通话、英语、粤语等各种语言。

该系统已经广泛应用于人工智能、家庭智能控制、语音助手、智能汽车等领域中,给我们的生活带来了巨大的便利。

一、深度学习在语音识别中的应用深度学习技术是一种人工神经网络技术,它能够模拟人类神经系统对信息进行处理和分析。

在语音识别中,深度学习技术被广泛应用,通过神经网络对声音信号进行处理和分析,而不是传统的傅里叶变换等数学计算方法。

深度学习技术对语音信号进行的处理包括噪声消除、声音特征提取和语音识别等多个方面。

其中对声音特征的提取是深度学习技术中的核心环节,常见的方法包括时域特征分析、频域特征分析和梅尔频率倒谱系数(MFCC)等方法。

通过这些方法对声音信号进行分析和提取,即可为接下来的语音识别提供准确的特征。

二、语音识别系统的构建语音识别系统的构建需要包括四个部分:数据准备、声音特征提取、深度学习模型训练和语音识别结果输出。

其中,数据准备是语音识别中的第一步,需要从各种来源收集大量的语音数据集并进行处理。

声音特征提取是语音识别的第二步,需要采用各种声音特征提取方法对声音信号进行处理和分析。

深度学习模型训练是语音识别的第三步,需要构建深度学习模型并使用训练数据对其进行训练和优化。

最后一步是语音识别结果输出,在这一步中,我们需要根据模型得到的结果进行后续处理和输出结果。

三、语音识别系统的模型选择和优化在语音识别系统的构建过程中,深度学习模型的选择和优化是十分关键的。

常见的语音识别系统模型包括循环神经网络(RNN)、长短时记忆网络(LSTM)和卷积神经网络(CNN)等。

其中,LSTM模型受到了广泛的关注和应用,它具有记忆能力、长序列处理能力以及较强的抗干扰性等优点。

对于模型的优化,我们可以采用dropout、正则化等方法,同时通过采用不同的激活函数和优化器等手段,也能够提高模型的准确率和性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

信号。 对每一帧经过预处理的语音信号进行自相关分

R ( k )= Σ x ( i-k ) x ( i ) , 0 ≤ k ≤ P

i=k

(3)

式 中 P 是 LPC 的 阶 数 , 取 P =10 。 所 采 用 结 构 如 图 1 。 在计算自相关系数的部分,如果在累加部分采用移 位 寄 存 器 来 计 算 保 存 11 个 LPC 系 数 , 会 产 生 不 必 要 的 移 位 功 耗 [6] 。 考 虑 到 FPGA 丰 富 的 存 储 器 资 源 , 采 用 RAM 进行累加部分的计算,从而使功耗得到降低,如图 1 所 示。 寄存器的输出形成了连接到 加 法 器 的 数 据 通 路 ,而 加 法器的输出存储在指定位置的寄 存 器 中 ,主 状 态 机 提 供 操 作地址 ,并控制读﹑ 写次序以避免在同一位置同时进行读 写 操 作 。 采 用 此 结 构 ,可 以 避 免 不 必 要 的 移 位 功 耗 ,而 性 能 上 与 采 用 移 位 寄 存 器 无 差 别 ,故 优 于 后 者 。

中 图 分 类 号 : TN47 文献标识码: A

Realization of speech recognition front-end algorithm based on FPGA

LIU Wen Shu , JI Ai Ming , WANG Zi Ou

(Soochow University, Suzhou 215021 , China ) Abstract : According to the research of distributed speech recognition (DSR ),this paper introduces a front -end processing sys tem ,which is based on the FPGA. Especially, the system adopts LUT (look_up table ) divider and constant divider. Finally, after comparing the system simulation with the result of Matlab modeling , the system could compute LPCC coefficient in shorter clock cy cle . The experiment results show that comparing with the method used previously, this method saves numbers of operation time and some areas in the chip. Key words : speech recognition ; DSR(distributed speech recognition ) ; FPGA ; divider

设 ξi = ici 则有:

n-1

ξn =-nan - Σ ( n-m ) am ξn-m , 其 中 1 ≤ n ≤ P

m=1 p

(11) (12)

2 仿真验证

为 了 验 证 算 法 的 可 行 性 , 本 文 用 VerilogHDL 语 言 对 整 个 语 音 参 数 的 提 取 进 行 建 模 。 依 照 图 2 进 行 了 LPC 系

式 中 P 是 LPC 的 阶 数 , 取 10 阶 。 采 用 Levinson - Durbin [ 7] 方法来解。 在该方法的计算中,可以看到求偏相关系数

(Parcor) k 时 , 由 于 存 在 式 (5) 中 的 关 系 : ki = temp E ( i - 1)

(5)

表 1 两种除法器算法性能比较表格

ncn =-nan - Σ ( n-m ) am cn-m , 其 中 1 ≤ n ≤ P

m=1

(9) (10)

器。 这里的除法运算所涉及到的除数仅为一组有限的常 数,采用一个通用的除法器就显得没有必要了 。 为此使 用 文 献 [10] 中 提 到 的 专 用 常 数 除 法 器 , 它 的 主 要 运 算 部 分由规则的处理单元阵列所构成,大大节省面积,易于 实现并易于扩展。

1.2 LPC 系 数

采 用 自 相 关 法 来 计 算 LPC 系 数 。 解 LPC 系 数 的 矩 阵 方程为:

p

Rn ( i )= Σ ak Rn (| i-k |) , 1 ≤ i ≤ p

k=1

(4)

位数)个时钟周期短得多。 该除法器有 2 点好处:一是 2 个乘法和查表可以并行执行,除法器延时较短;二是乘 法 数 据 位 数 较 少 , 乘 法 器 面 积 较 小 , 而 由 其 决 定 的 LUT 面 积 也 不 大 [ 8] 。 两 种 除 法 器 算 法 性 能 比 较 如 表 1 。

H =1- hz -1 (1) 本 系 统 中 h 取 15 , 所 以 加 重 的 语 音 信 号 为 : 16 y ( n +1)= x ( n +1)- 15 x ( n ) (2) 16 窗 函 数 采 用 汉 明 (Hamming) 窗 , 汉 明 窗 函 数 要 先 计 算

好 放 于 ROM 中 , 直 接 与 语 音 信 号 相 乘 得 到 加 窗 的 语 音

n-1

Σ Σ 1- m ≤ c =- Σ ≤ a c , 其 中 P≤n≤Q n

p n m n-m m=1

m cn =- an - Σ 1am cn - m , 其 中 1 ≤ n ≤ P n m=1

r1

r2

(7) (8)

r4 multipler r3

P 是 LPC 的 阶 数 , Q 是 LPCC 的 阶 数 。

1.1 自 相 关

对 语 音 信 号 进 行 分 帧 , 使 得 每 一 帧 有 N =256 个 采 样 , 帧 移 为 64 。 对 每 一 帧 信 号 进 行 预 加 重 和 加 窗 。 预加重采用:

tributed Speech Recognition) 。 移 动 终 端 只 需 进 行 语 音 采

近年来,语音识别在通信与电子系统、自动控制等 领域中有着广泛的应用。 其中一个重要的发展方向是硬 件实现语音识别算法的研究。 这个方向主要是小型化、 便携式语音产品的应用 ,在这类设备上,通常是小词汇 量的 孤立 词识别 ,例如 :手机﹑ PDA 以 及 车 载 应 用 等 装 置 上。 国外 在硬 件实现 方面 的研 究较早 ,而国 内起步 较晚 , 因 此 对 基 于 FPGA 的 语 音 识 别 前 端 算 法 研 究 具 有 重 要 的 意 义 [ 1] 。 近 两 年 国 际 上 提 出 了 分 布 式 语 音 识 别 DSR (Dis-

集、特征提取 ,有关 信息 则通过 无线 数据信 道送 往网 络 中的远 程服 务器,由 服务 器 中 的 识 别 单 元 完 成 语 音 识 别 功 能 [ 2] 。 就 目 前 的 研 究 情 况 来 看 , 通 常 用 相 关 的 方 法 实 现 LPCC 系 数 的 提 取 。 而 在 LPC 系 数 提 取 部 分 的 除 法 器 , 采 用 的 结 构 不 尽 相 同 , 有 采 用 搜 索 算 法 [ 3] , 也 有 采 用 减 并 移 位 法 [ 4] ; 在 LPCC 系 数 提 取 时 , 可 以 直 接 计 算 , 也 可 以 经 过 一 定 的 变 换 [ 5] 。 为 了 将 面 积 和 性 能 得 到 最 好 的 折中,并且考虑实际 的应 用场 合 ,在以 上两 个除法 器的

Matlab 的 建 模 结 果 进 行 了 对 比 。 结 果 表 明 , 与 之 前 的 方 法 相 比 , 系 统 能 够 在 较 短 的 时 钟 周 期 内 计 算 出 LPCC 系 数 , 节 省 了 大 量 的 运 算 时 间 和 一 定 的 面 积 。 关 键 词 : 语 音 识 别 ; DSR(distributed speech recognition) ; FPGA ; 除 法 器

查找表法 乘法器数目 搜索算法

2 1 2 MUL or 1 MUL + 1 LUT

1 0 N( 数 据 位 数 )

LUT 数 目

延时

自相关输出

图 1 计算自相关系数结构图

《电子技术应用 》 2010 年第 2 期

41

集成电路应用

1.3 LPCC 系 数

Application of Integrated Circuits

按照上面的分析,如果依计算公式计算,缺点是资 源占用过多,需要时钟周期过长。 所以采用节省资源的 方法计算中间系数,对公式进行一定的变形,算法进行 一定的改进,资源得到充分利用,并且能够缩短时钟周 期 , 节 省 乘 法 器 资 源 57% [ 5] 。 计 算 LPCC 系 数 结 构 图 , 如 图 3 所示。 实现节省资源的方法:

n-1

adder

图 3 计 算 LPCC 系 数 结 构 图

其 中 P 是 LPC 的 阶 数 , Q 是 LPCC 的 阶 数 , 取 P = Q =10 。 然而,在这个结构当中,可以看到最终的计算结果 是 ξ , 而 并 不 是 真 正 的 LPCC 系 数 。 பைடு நூலகம் 此 仍 需 要 一 个 除 法

集成电路应用

Application of Integrated Circuits

基于 FPGA 的语音识别前端算法研究实现

刘文 姝 ,季 爱 明 ,王 子 欧 ( 苏 州 大 学 , 江 苏 苏 州 215021)

摘 要 : 通 过 分 布 式 语 音 识 别 DSR 的 研 究 , 提 出 了 基 于 FPGA 平 台 的 前 端 处 理 系 统 结 构 。 对 其 中 两 个 除 法 器 分 别 采 用 了 LUT 查 找 表 和 常 数 除 法 器 的 结 构 。 用 VerilogHDL 语 言 进 行 建 模 仿 真 , 并 与