东南大学信息学院计算结构POC实验报告

【东南大学】【数据结构】实验报告机场模拟程序Airport.

【东南大学】【数据结构】实验报告机场模拟程序Airport.数据结构实验报告(第一次)oxstar名称机场模拟程序AirportSimulation(三跑道)问题描述设机场有三个跑道,跑道1专用于降落,跑道2专用于起飞,跑道3优先用于降落。

当等待降落队列为空时,跑道3也可用于起飞。

修改并运行机场模拟程序AirportSimulation,使之能利用所有的跑道资源。

分析教材中已经给出了非常详细的实例,由于只是跑道数量的不同,只需在它的基础上将模拟函数、参数设置和数据成员做一些修改即可。

数据结构和算法分析本例涉及的数据结构类型主要是环状队列,用于存储等待的飞机队列。

由于飞机从哪一条跑道降落或者起飞是由机场方面动态决定的,故仍只需两个队列。

原例中跑道大约可以提供1/2时间用于降落,不妨设权重为1/2,那么根据题意,本例降落时间权重将达1+1/2=3/2,因而将等待队列延长至15(需开设16)。

起飞等待队列同理。

队列长度在Queue.h中默认定义:const int DefaultSize = 16;Queue( int MaxQueueSize = DefaultSize );Queue结构属于数据结构基础的内容,不在此讨论,代码详见Queue.h。

与上述相似的原因,单位时间期望到达飞机总数上限也相应提升至3。

只可能同时安排2架飞机起飞或者降落,所以增加单起/降总数限制为2。

AirportSimulation::AirportSimulation(){ ……else if( expectarrive + expectdepart > 3.0 || expectarrive > 2.0 || expectdepart > 2.0 ){cout << "机场将饱和!请重新输入。

"<< endl;ok = false;}……}为确保供数据分析的数据全面,为每一条跑道提供了单独储存空闲时间单元数、降落/起飞飞机数等的变量,并在程序相应位置给出设置和显示输出。

东南大学信息学院通信电子线路实验实验报告

3.1 常用仪器的使用04012540 印友进一、实验内容1、说明频谱仪的主要工作原理,示波器测量精度与示波器带宽、与被测信号频率之间关系。

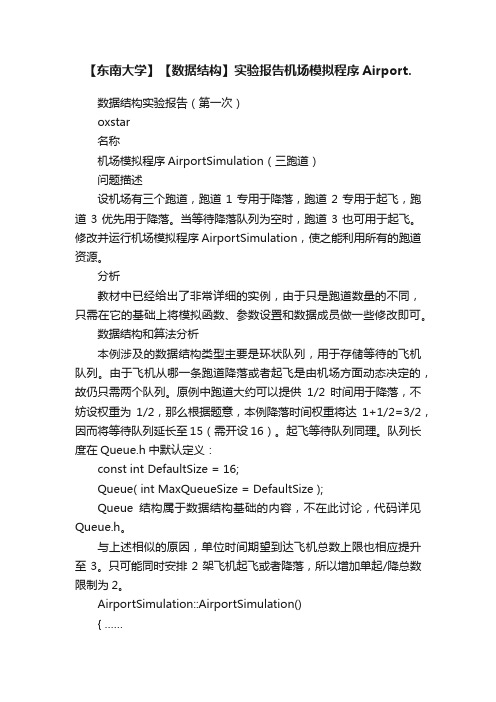

答:(1)频谱仪结构框图为:频谱仪的主要工作原理:①对信号进行时域的采集,对其进行傅里叶变换,将其转换成频域信号。

这种方法对于AD 要求很高,但还是难以分析高频信号。

②通过直接接收,称为超外差接收直接扫描调谐分析仪。

即:信号通过混频器与本振混频后得到中频,采用固定中频的办法,并使本振在信号可能的频谱范围内变化。

得到中频后进行滤波和检波,就可以获取信号中某一频率分量的大小(帕斯瓦尔定理)。

(2)示波器的测量精度与示波器带宽、被测信号频率之间的关系:示波器的带宽越宽,在通带内的衰减就越缓慢;示波器带宽越宽,被测信号频率离示波器通带截止频率点就越远,则测得的数据精度约高。

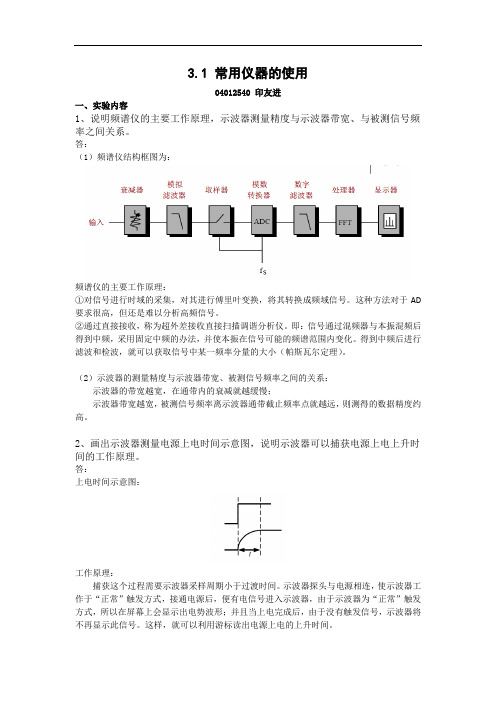

2、画出示波器测量电源上电时间示意图,说明示波器可以捕获电源上电上升时间的工作原理。

答:上电时间示意图:工作原理:捕获这个过程需要示波器采样周期小于过渡时间。

示波器探头与电源相连,使示波器工作于“正常”触发方式,接通电源后,便有电信号进入示波器,由于示波器为“正常”触发方式,所以在屏幕上会显示出电势波形;并且当上电完成后,由于没有触发信号,示波器将不再显示此信号。

这样,就可以利用游标读出电源上电的上升时间。

3、简要说明在FM 调制过程中,调制信号的幅度与频率信息是如何加到FM 波中的?答:载波的瞬时角频率为()()c f t k u t ωωΩ=+,(其中f k 为与电路有关的调频比例常数)已调的瞬时相角为000t ()()t t c f t dt t k u t dt θωωθΩ=++⎰⎰()=所以FM 已调波的表达式为:000()cos[()]t om c f u t U t k u t dt ωθΩ=++⎰当()cos m u t U t ΩΩ=Ω时,00()cos[sin ]om c f u t U t M t ωθ=+Ω+其中f M 为调制指数其值与调制信号的幅度m U Ω成正比,与调制信号的角频率Ω反比,即m f fU M k Ω=Ω。

东南大学计算机网络实验报告一

东南大学自动化学院实验报告课程名称:信息通信网络概论第1次实验实验名称:TCP/IP协议与Socket编程认识实验院(系):自动化专业:自动化姓名:学号:实验室:金智楼5楼实验组别:同组人员:实验时间:2016 年11 月29日评定成绩:审阅教师:目录一.实验目的和要求 (3)二.实验原理 (3)三. 实验方案与实验步骤 (5)四.实验设备与器材配置 (7)五.实验记录 (7)六.实验总结 (9)七.思考题或讨论题 (9)附录:部分代码一.实验目的和要求1)熟悉TCP/IP协议的功能和网络操作;2)了解基于SOCKET的编程原理;3)编写一个小型的Socket实用程序,初步了解Windows环境下使用Socket的编程。

二.实验原理1、什么是Windows Sockets规范?Windows Sockets规范以U.C. Berkeley大学BSD UNIX中流行的Socket接口为范例定义了一套Micosoft Windows下网络编程接口。

它不仅包含了人们所熟悉的Berkeley Socket 风格的库函数;也包含了一组针对Windows的扩展库函数,以使程序员能充分地利用Windows消息驱动机制进行编程。

Windows Sockets规范本意在于提供给应用程序开发者一套简单的API,并让各家网络软件供应商共同遵守。

此外,在一个特定版本Windows的基础上,Windows Sockets也定义了一个二进制接口(ABI),以此来保证应用Windows Sockets API的应用程序能够在任何网络软件供应商的符合Windows Sockets协议的实现上工作。

因此这份规范定义了应用程序开发者能够使用,并且网络软件供应商能够实现的一套库函数调用和相关语义。

遵守这套Windows Sockets规范的网络软件,我们称之为Windows Sockets兼容的,而Windows Sockets兼容实现的提供者,我们称之为Windows Sockets提供者。

东南大学计算方法实验报告

计算方法与实习实验报告学院:电气工程学院指导老师:***班级:160093******学号:********实习题一实验1 拉格朗日插值法一、方法原理n次拉格朗日插值多项式为:L n(x)=y0l0(x)+y1l1(x)+y2l2(x)+…+y n l n(x)n=1时,称为线性插值,L1(x)=y0(x-x1)/(x0-x1)+ y1(x-x0)/(x1-x0)=y0+(y1-x0)(x-x0)/(x1-x0)n=2时,称为二次插值或抛物线插值,精度相对高些L2(x)=y0(x-x1)(x-x2)/(x0-x1)/(x0-x2)+y1(x-x0)(x-x2)/(x1-x0)/(x1-x2)+y2(x-x0)(x-x1)/(x2-x0)/(x2-x1)二、主要思路使用线性方程组求系数构造插值公式相对复杂,可改用构造方法来插值。

对节点x i(i=0,1,…,n)中任一点x k(0<=k<=n)作一n 次多项式l k(x k),使它在该点上取值为1,而在其余点x i(i=0,1,…,k-1,k+1,…,n)上为0,则插值多项式为L n(x)=y0l0(x)+y1l1(x)+y2l2(x)+…+y n l n(x) 上式表明:n 个点x i(i=0,1,…,k-1,k+1,…,n)都是l k(x)的零点。

可求得l k三.计算方法及过程:1.输入节点的个数n2.输入各个节点的横纵坐标3.输入插值点4.调用函数,返回z函数语句与形参说明程序源代码如下:#include<iostream>#include<math.h>using namespace std;#define N 100double fun(double *x,double *y, int n,double p);void main(){int i,n;cout<<"输入节点的个数n:";cin>>n;double x[N], y[N],p;cout<<"please input xiangliang x= "<<endl;for(i=0;i<n;i++)cin>>x[i];cout<<"please input xiangliang y= "<<endl;for(i=0;i<n;i++)cin>>y[i];cout<<"please input LagelangrichazhiJieDian p= "<<endl;cin>>p;cout<<"The Answer= "<<fun(x,y,n,p)<<endl;system("pause") ;}double fun(double x[],double y[], int n,double p){double z=0,s=1.0;int k=0,i=0;double L[N];while(k<n){ if(k==0){ for(i=1;i<n;i++)s=s*(p-x[i])/(x[0]-x[i]);L[0]=s*y[0];k=k+1;}else{s=1.0;for(i=0;i<=k-1;i++)s=s*((p-x[i])/(x[k]-x[i]));for(i=k+1;i<n;i++) s=s*((p-x[i])/(x[k]-x[i]));L[k]=s*y[k];k++;}}for(i=0;i<n;i++)z=z+L[i];return z;}五.实验分析n=2时,为一次插值,即线性插值n=3时,为二次插值,即抛物线插值n=1,此时只有一个节点,插值点的值就是该节点的函数值n<1时,结果都是返回0的;这里做了n=0和n=-7两种情况3<n<100时,也都有相应的答案常用的是线性插值和抛物线插值,显然,抛物线精度相对高些n次插值多项式Ln(x)通常是次数为n的多项式,特殊情况可能次数小于n.例如:通过三点的二次插值多项式L2(x),如果三点共线,则y=L2(x)就是一条直线,而不是抛物线,这时L2(x)是一次式。

东南大学计算方法上机报告实验报告完整版

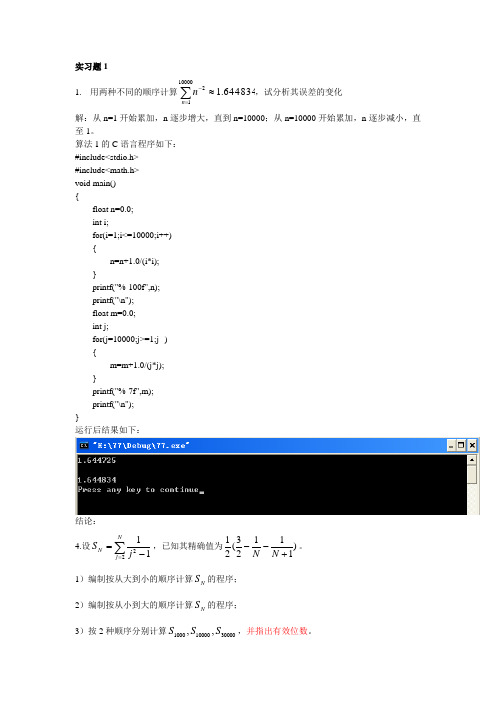

实习题11. 用两种不同的顺序计算644834.11000012≈∑=-n n,试分析其误差的变化解:从n=1开始累加,n 逐步增大,直到n=10000;从n=10000开始累加,n 逐步减小,直至1。

算法1的C 语言程序如下: #include<stdio.h> #include<math.h> void main() { float n=0.0; int i; for(i=1;i<=10000;i++) { n=n+1.0/(i*i); } printf("%-100f",n); printf("\n"); float m=0.0; int j; for(j=10000;j>=1;j--) { m=m+1.0/(j*j); } printf("%-7f",m); printf("\n"); }运行后结果如下:结论: 4.设∑=-=Nj N j S 2211,已知其精确值为)11123(21+--N N 。

1)编制按从大到小的顺序计算N S 的程序; 2)编制按从小到大的顺序计算N S 的程序;3)按2种顺序分别计算30000100001000,,S S S ,并指出有效位数。

解:1)从大到小的C语言算法如下:#include<stdio.h>#include<math.h>#include<iostream>using namespace std;void main(){float n=0.0;int i;int N;cout<<"Please input N"<<endl;cin>>N;for(i=N;i>1;i--){n=n+1.0/(i*i-1);N=N-1;}printf("%-100f",n);printf("\n");}执行后结果为:N=2时,运行结果为:N=3时,运行结果为:N=100时,运行结果为:N=4000时,运行结果为:2)从小到大的C语言算法如下:#include<stdio.h>#include<math.h>#include<iostream>using namespace std;void main(){float n=0.0;int i;int N;cout<<"Please input N"<<endl;cin>>N;for(i=2;i<=N;i++){n=n+1.0/(i*i-1);}printf("%-100f",n);printf("\n");}执行后结果为:N=2时,运行结果为:N=3时,运行结果为:N=100时,运行结果为:N=4000时,运行结果为:结论:通过比较可知:N 的值较小时两种算法的运算结果相差不大,但随着N 的逐渐增大,两种算法的运行结果相差越来越大。

结构化程序设计实训报告

一、实验背景结构化程序设计是一种计算机编程方法,旨在提高程序的可读性、可维护性和可扩展性。

通过使用顺序结构、选择结构和循环结构等基本程序结构,可以使程序更加清晰、易于理解。

本次实训旨在通过实践操作,使学生掌握结构化程序设计的基本思想和方法,提高编程能力。

二、实验目的1. 掌握结构化程序设计的基本思想。

2. 熟练掌握三种基本程序结构:顺序结构、选择结构和循环结构。

3. 学会利用结构化程序设计思想解决数据处理问题。

4. 掌握VF(Visual FoxPro)程序调试的基本方法,能进行基本的程序设计。

三、实验内容及步骤1. 实验内容本次实训主要包括以下内容:(1)顺序结构:编写一个简单的程序,实现数字1到10的累加。

(2)选择结构:编写一个程序,根据用户输入的年龄判断是否成年。

(3)循环结构:编写一个程序,计算1到100的整数之和。

(4)结合以上结构,实现一个简单的学生成绩管理系统。

2. 实验步骤(1)在VFP环境下新建一个程序文件,命名为“结构化程序设计实验.prg”。

(2)编写程序代码,实现实验内容。

(3)保存程序文件。

(4)运行程序,验证程序功能。

(5)对程序进行调试,解决可能出现的问题。

四、实验过程及结果1. 顺序结构实验代码如下:```visual foxpro顺序结构实验clearlocal sum = 0for i = 1 to 10sum = sum + iendfor"1到10的累加和为:" + str(sum) ```运行结果:1到10的累加和为:55 2. 选择结构实验代码如下:```visual foxpro选择结构实验clearlocal age = 18if age >= 18"您已成年"else"您还未成年"endif```运行结果:您已成年3. 循环结构实验代码如下:```visual foxpro循环结构实验clearlocal sum = 0for i = 1 to 100sum = sum + iendfor"1到100的整数之和为:" + str(sum)```运行结果:1到100的整数之和为:50504. 学生成绩管理系统代码如下:```visual foxpro学生成绩管理系统clearlocal score_list = {}local input_scorefor i = 1 to 5"请输入第" + str(i) + "位学生的成绩:"input_score = input("请输入成绩:") aadd(score_list, input_score) endforlocal max_score = score_list[1]local min_score = score_list[1]for i = 2 to len(score_list)if score_list[i] > max_scoremax_score = score_list[i]endifif score_list[i] < min_scoremin_score = score_list[i]endifendfor"最高分为:" + str(max_score)"最低分为:" + str(min_score)```运行结果:请输入第1位学生的成绩:90请输入第2位学生的成绩:85请输入第3位学生的成绩:78请输入第4位学生的成绩:92请输入第5位学生的成绩:88最高分为:92最低分为:78五、实验总结1. 实验收获通过本次实训,我掌握了以下内容:(1)顺序结构、选择结构和循环结构的语句格式、功能及使用方法。

东南大学 计算结构 课程设计 CPU设计报告

COA-CPU School of Information Science and Engineering Southeast University

The Design Report of the Microinstruction CPU Design

Figure 5 shows the key elements of Microprogrammed Control Unit. The set of microinstructions is stored in the control memory. The control address register contains the address of the next microinstructions to be read. When a microinstruction is read from the control memory, it is transferred to a control buffer register. The register connects to the control lines emanating from the control unit. Thus, reading a microinstruction from the control memory is the same as executing that microinstruction. The third element shown in the figure is a sequencing unit that loads the control address register and issues a read command.

2. Design Specification

东南大学信息学院微机实验报告十

实验十一、实验目的1.了解Intel 8086CPU的中断处理功能以及IBM-PC的中断结构。

2.了解8259中断控制器的使用。

3.掌握键盘中断的编程,观察中断的执行情况。

二、实验任务要求每按下一个键就向CPU发出中断请求信号,该信号由8259的IRQ1引入,中断类型号为09,CPU响应中断后转入执行KEYINT中断服务程序,并且在CRT上显示某字或某个图形,按下10次后返回DOS。

三、源程序STACK SEGMENT STACKDW 200H DUP(?)STACK ENDSDATA SEGMENTKEY DB ?BUF DB "OK!"DATA ENDSCODE SEGMENTASSUME CS:CODE, SS:STACK, DS:DATADELAY PROCPUSH CXPUSH DXMOV DX,0A64DHCON2: MOV CX,0FFFFHCON: DEC CXJNE CONDEC DXJNE CON2POP DXPOP CXRETDELAY ENDPDISP1 PROC FARPUSH AXPUSH BXPUSH CXPUSH DXMOV AH, 15 ;读当前显示状态INT 10HMOV AH, 0 ;设置显示方式INT 10HMOV CX, 1 ;要显示字符个数MOV DX, 0 ;行号为0,列号为0REPT: MOV AH, 2 ;设置光标位INT 10HMOV AL, 0FH ;读出太阳图形MOV AH, 10 ;写字符INT 10HCALL DELAYSUB AL, ALMOV AH, 10 ;清除原图形INT 10HINC DHADD DL, 2CMP KEY, 10JAE GO1CMP DH, 25JNE REPTGO1: POP DXPOP CXPOP BXPOP AXRETDISP1 ENDPDISP2 PROC FARPUSH CXPUSH BXPUSH AXMOV CX, 3NEXTC: LODSB ;AL<-[SI]MOV AH, 0EH ;写字符,并移动光标MOV BX, 01INT 10HCALL DELAYLOOP NEXTCCMP KEY, 10JAE GO2POP AXPOP BXPOP CXRETDISP2 ENDPKEYINT PROC FARPUSH AXPUSH SISTIIN AL, 60HIN AL, 61HOR AL, 80HOUT 61H, ALAND AL, 7FHOUT 61H,ALTEST AH, 80HJNE GOSTIINC KEYMOV SI, OFFSET BUFCALL DISP2GO: MOV AL, 20HOUT 20H, ALPOP SIPOP AXIRETKEYINT ENDP START: MOV AX, STACK MOV SS, AXMOV AX, DATAMOV DS, AXMOV ES, AXMOV AX, ES:[24H]PUSH AXMOV AX, ES:[26H]PUSH AXCLIMOV AX, OFFSET KEYINTMOV ES:[24H],AXMOV AX, SEG KEYINTMOV ES:[26H], AXSTIMOV KEY, 0AGAIN: CALL DISP1CMP KEY, 10JB AGAINCLIGO2: POP AXMOV ES:[26H],AXPOP AXMOV ES:[24H],AXSTIMOV AH, 4CHINT 21HCODE ENDSEND START四、实验中遇到的问题在实验编写过程中,遇到按住键,会一直显示OK,出现10次OK后也不会跳出程序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

POC实验报告目录目录 .............................................................................................................................................. 1-11 实验目的............................................................................................................................... 1-12 实验任务............................................................................................................................... 2-13 架构说明............................................................................................................................... 3-24 仿真信号设计与结果分析................................................................................................... 4-34.1 打印机模块............................................................................................................... 4-34.1.1 仿真信号说明与设计................................................................................... 4-34.1.2 仿真结果与分析........................................................................................... 4-34.2 POC模块.................................................................................................................. 4-34.2.1 仿真信号说明与设计................................................................................... 4-34.2.2 仿真结果与分析........................................................................................... 4-44.3 整体模块................................................................................................................... 4-45 总结与补充........................................................................................................................... 5-45.1 查询模式................................................................................................................... 5-55.2 中断模式................................................................................................................... 5-56 附录....................................................................................................................................... 6-6 1实验目的本实验的目的是设计一块简易的POC(并行输出控制器),从而连接系统总线和打印机。

通过本次实验,可以初步了解输入输出、存储模块的设计,为接下来CPU的设计奠定良好的基础。

2实验任务利用ISE和VHDL语言设计出POC模块和打印机模块,并且通过仿真测试并验证其主要功能的实现。

仿真主要以中断响应工作模式为主。

而查询模式也需要了解,这部分分析内容都将放在总结环节。

3架构说明整体由POC、Printer两个模块组成,整体的输入端口有:CS:片选,实际情况为地址总线13A:寄存器选取;D_bus:数据总线;CLK:时间信号;R_W:读取/写入控制,0为读取,1为写入;输出端口为:IRQ:中断请求信号,低电平有效;CNT:计数器,用于模拟打印机的忙碌情况。

4仿真信号设计与结果分析4.1 打印机模块4.1.1仿真信号说明与设计RDY:输出信号,当Printer处于空闲状态时为1,工作状态为0;TR:输入信号,表示准备传输数据,设置为保持一个时钟周期;PD:输入信号,表示当前准备打印的数据;CLK:时钟信号,虽然设计图上没有,但为了模拟打印机工作采用了计数器,相应的也暂时引入了时钟信号。

CNT:输出信号,用以模拟打印机的过程,输出用以更直观的表示。

4.1.2仿真结果与分析①初始状态时打印机显然不处于工作状态,因而RDY信号保持为1;②当PD数据填充完毕后,TR脉冲信号到来;③TR脉冲上升沿到来的同时,RDY信号置为0,表示正在忙碌;④此时打印机开始打印,表示为cnt计数,当计数完毕后RDY信号重新为1。

4.2 POC模块4.2.1仿真信号说明与设计RDY:输入信号,用以判断打印机是否空闲CS:输入信号,表示片选,实际使用时为CPU是否选中该芯片(用前13根地址线)A:输入信号,地址线的后3位,表示实际选择哪个寄存器,本次设计001为选取数据寄存器,010为选取状态寄存器。

CLK:时钟信号。

CNT:输出信号,用以模拟打印机的过程,输出用以更直观的表示。

4.2.2仿真结果与分析①初始状态时,POC未被选中,打印机处于空闲状态,因此SR7被置为1,又由于默认工作在中断方式,因此在时钟上升沿之时便发出IRQ中断请求(低电平);②发送请求后,CPU选中芯片(即前13地址线选中CS),将数据总线的数据准备好,之后选中数据寄存器(A为001),并将POC的读写状态设置为写;③经过一个时钟周期后tr脉冲输出表示数据准备传送,并且数据输出口准备好数据,打印机也回到忙碌状态。

4.3 整体模块输入信号和POC模块大致相同,因此直接进行结果分析。

首先,IRQ信号产生,CPU选中POC芯片,随后选中数据寄存器并写入数据,之后经过几个时钟后,打印机开始工作,计数器开始计数。

而CPU又去处理其他的工作(中断工作模式的体现)。

当打印机打印结束时,IRQ信号再度发出,等待CPU响应与再度传送数据。

由于CPU 当前也许正在进行不可中断的原子性操作,所以等待响应后再传送数据、再度打印是必要的。

由此仿真了整个工作流程。

由于更复杂的仿真过程需要CPU的设计与介入,在此无法展示,我将在下文做相关文字补充。

5总结与补充通过仿真,我们对POC的工作方式和细节有了进一步的了解。

然而,由于本次实验没有对CPU的特殊要求和说明,导致无法通过仿真的方式清晰的体现出中断方式和查询方式的具体区别。

所有本应CPU输出、处理、反馈的信号都由人手工输入代替。

因此,下面将对两种工作模式结合CPU作进一步阐述与补充。

5.1 查询模式首先,CPU收到有关程序的请求,准备通过I/O接口联系POC模块,试图打印有关内容。

CPU访问POC的相关状态寄存器(SR7),查看POC目前是否处于空闲状态。

如果是,那就准备打印,否则,CPU处于轮询的状态。

该进程内的每一个指令周期,CPU都在查询POC是否空闲,并不做其他的事情,直到POC处于空闲,并允许传输数据为止。

当CPU了解POC已准备就绪时,CPU便将有关内容分块传输到POC的数据缓存中。

由于实际文件数据量较大,CPU将持续处于“轮询—传输—轮询—传输”直到文件打印完毕为之。

对于已经传输到POC的数据段,POC并不能立刻将其提交给打印机,因为当前打印机可能处于忙碌状态。

当打印机用完当前数据(可能仅为一行)后,RDY信号为高电平,POC 再将本段数据提交给打印机继续操作。

通过POC的TR信号和PD数据输出传送给打印机,再通过RDY信号判断当前打印机是否用完目前的数据。

如果用完了,就将SR7置为空闲状态,以方便CPU提供新数据,否则SR7处于忙碌状态。

至此,整个查询模式的工作方式描述完毕。

5.2 中断模式首先,CPU在某个时间点将POC的SR0置为1,即命令POC工作在中断模式。

之后的前小部分和查询模式相同,CPU收到有关程序的请求,准备通过I/O接口联系POC模块,试图打印有关内容。

CPU访问POC的相关状态寄存器(SR7),查看POC目前是否处于空闲状态,如果是,那就准备打印。

如果POC忙碌,CPU则继续忙其他的工作。

由于POC事先已被CPU设置为中断模式,一旦POC处于空闲态,则会向CPU发出中断请求。

此时,CPU会通过查中断向量表得知,是POC模块发出的请求,处理完当前的原子性操作或更高级的中断请求后,则响应POC中断,选中POC芯片进行有关操作。

由于实际文件数据量较大,CPU仍然会分块传输数据。

此时CPU传完数据后继续忙其他工作,直到下一个中断来临。

整个工作将持续处于“中断—传输—中断—传输”直到文件打印完毕为之。

具体的POC处理和前文类似,不再多言。

最后需要额外指出的是,对于多文档打印,打印队列由更高一层的操作系统控制,无关物理底层的实现,因此可不用在此讨论。

5.3 结论本项仿真设计完成了任务的基本要求,实现了POC和Printer的设计,并且通过了测试,达到了预期的效果。