数字电路复习题

数字电路复习试题

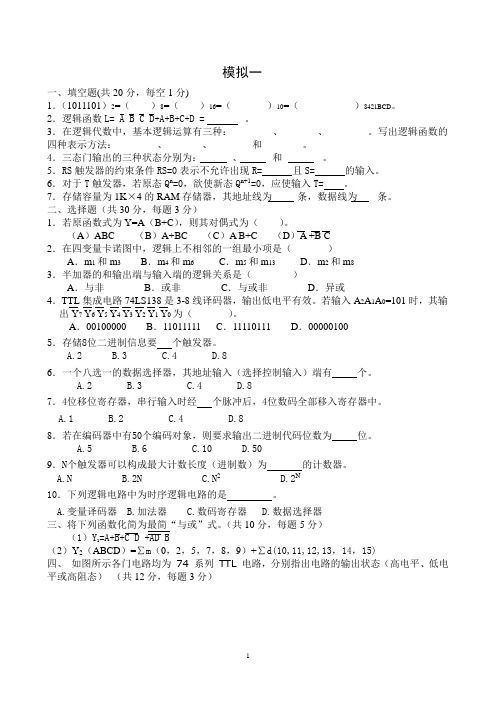

模拟一一、填空题(共20分,每空1分)1.(1011101)2=()8=()16=()10=()8421BCD。

2.逻辑函数L= A B C D+A+B+C+D = 。

3.在逻辑代数中,基本逻辑运算有三种:________、_______、________。

写出逻辑函数的四种表示方法:________、_______、________和________。

4.三态门输出的三种状态分别为:、和。

5.RS触发器的约束条件RS=0表示不允许出现R=且S=的输入。

6.对于T触发器,若原态Q n=0,欲使新态Q n+1=0,应使输入T= 。

7.存储容量为1K×4的RAM存储器,其地址线为条,数据线为条。

二、选择题(共30分,每题3分)1.若原函数式为Y=A(B+C),则其对偶式为()。

(A)ABC (B)A+BC (C)A B+C (D)A +B C2.在四变量卡诺图中,逻辑上不相邻的一组最小项是()A.m1和m3B.m4和m6C.m5和m13D.m2和m83.半加器的和输出端与输入端的逻辑关系是()A.与非B.或非C.与或非D.异或4.TTL集成电路74LS138是3-8线译码器,输出低电平有效。

若输入A2A1A0=101时,其输出Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0为()。

A.00100000 B.11011111 C.11110111 D.000001005.存储8位二进制信息要个触发器。

A.2B.3C.4D.86.一个八选一的数据选择器,其地址输入(选择控制输入)端有个。

A.2B.3C.4D.87.4位移位寄存器,串行输入时经个脉冲后,4位数码全部移入寄存器中。

A.1B.2C.4D.88.若在编码器中有50个编码对象,则要求输出二进制代码位数为位。

A.5B.6C.10D.509.N个触发器可以构成最大计数长度(进制数)为的计数器。

A.NB.2NC.N2D.2N10.下列逻辑电路中为时序逻辑电路的是。

数字电路复习考试题及答案

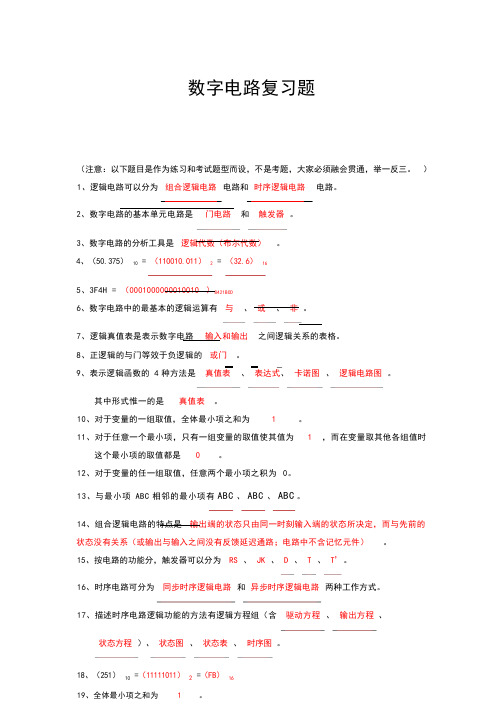

数字电路复习题(注意:以下题目是作为练习和考试题型而设,不是考题,大家必须融会贯通,举一反三。

) 1、逻辑电路可以分为 组合逻辑电路 电路和 时序逻辑电路 电路。

2、数字电路的基本单元电路是 门电路 和 触发器 。

3、数字电路的分析工具是 逻辑代数(布尔代数) 。

4、(50.375) 10 = (110010.011) 2 = (32.6) 165、3F4H = (0001000000010010 )8421BCD6、数字电路中的最基本的逻辑运算有 与 、 或 、 非 。

7、逻辑真值表是表示数字电路 输入和输出 之间逻辑关系的表格。

8、正逻辑的与门等效于负逻辑的 或门 。

9、表示逻辑函数的 4 种方法是真值表 、 表达式、 卡诺图 、 逻辑电路图 。

其中形式惟一的是 真值表 。

10、对于变量的一组取值,全体最小项之和为 1 。

11、对于任意一个最小项,只有一组变量的取值使其值为 1 ,而在变量取其他各组值时这个最小项的取值都是 0 。

12、对于变量的任一组取值,任意两个最小项之积为 0。

13、与最小项 ABC 相邻的最小项有 ABC 、 ABC 、 ABC 。

14、组合逻辑电路的特点是 输出端的状态只由同一时刻输入端的状态所决定,而与先前的状态没有关系(或输出与输入之间没有反馈延迟通路;电路中不含记忆元件) 。

15、按电路的功能分,触发器可以分为 RS 、 JK 、 D 、 T 、 T’。

16、时序电路可分为 同步时序逻辑电路 和 异步时序逻辑电路 两种工作方式。

17、描述时序电路逻辑功能的方法有逻辑方程组(含 驱动方程 、 输出方程 、状态方程 )、 状态图 、 状态表 、 时序图 。

18、(251) 10 =(11111011) 2 =(FB ) 16 19、全体最小项之和为 1 。

20、按照使用功能来分,半导体存储器可分为RAM 和ROM 。

21、RAM 可分为动态RAM 和静态RAM 。

电子技术基础与技能——数字电路复习考试题

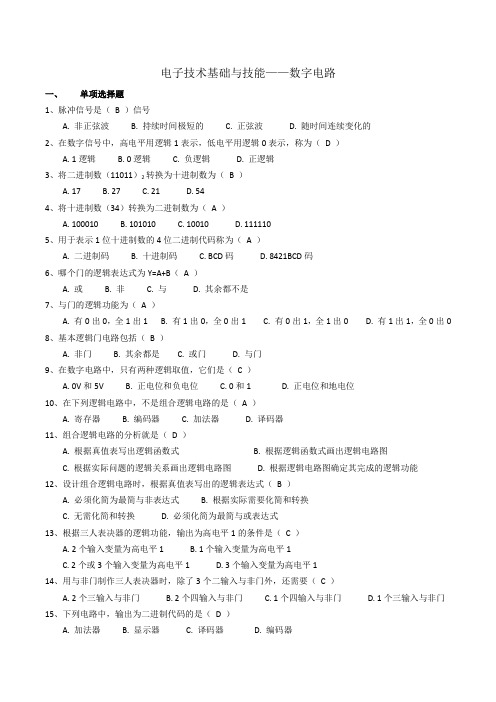

电子技术基础与技能——数字电路一、单项选择题1、脉冲信号是(B )信号A. 非正弦波B. 持续时间极短的C. 正弦波D. 随时间连续变化的2、在数字信号中,高电平用逻辑1表示,低电平用逻辑0表示,称为(D )A. 1逻辑B. 0逻辑C. 负逻辑D. 正逻辑3、将二进制数(11011)2转换为十进制数为(B )A. 17B. 27C. 21D. 544、将十进制数(34)转换为二进制数为(A )A. 100010B. 101010C. 10010D. 1111105、用于表示1位十进制数的4位二进制代码称为(A )A. 二进制码B. 十进制码C. BCD码D. 8421BCD码6、哪个门的逻辑表达式为Y=A+B(A )A. 或B. 非C. 与D. 其余都不是7、与门的逻辑功能为(A )A. 有0出0,全1出1B. 有1出0,全0出1C. 有0出1,全1出0D. 有1出1,全0出08、基本逻辑门电路包括(B )A. 非门B. 其余都是C. 或门D. 与门9、在数字电路中,只有两种逻辑取值,它们是(C )A. 0V和5VB. 正电位和负电位C. 0和1D. 正电位和地电位10、在下列逻辑电路中,不是组合逻辑电路的是(A )A. 寄存器B. 编码器C. 加法器D. 译码器11、组合逻辑电路的分析就是(D )A. 根据真值表写出逻辑函数式B. 根据逻辑函数式画出逻辑电路图C. 根据实际问题的逻辑关系画出逻辑电路图D. 根据逻辑电路图确定其完成的逻辑功能12、设计组合逻辑电路时,根据真值表写出的逻辑表达式(B )A. 必须化简为最简与非表达式B. 根据实际需要化简和转换C. 无需化简和转换D. 必须化简为最简与或表达式13、根据三人表决器的逻辑功能,输出为高电平1的条件是(C )A. 2个输入变量为高电平1B. 1个输入变量为高电平1C. 2个或3个输入变量为高电平1D. 3个输入变量为高电平114、用与非门制作三人表决器时,除了3个二输入与非门外,还需要(C )A. 2个三输入与非门B. 2个四输入与非门C. 1个四输入与非门D. 1个三输入与非门15、下列电路中,输出为二进制代码的是(D )A. 加法器B. 显示器C. 译码器D. 编码器16、可以将十进制数0~9编成二进制代码的电路,称为(B )A. 二进制编码器B. 二-十进制编码器C. 优先编码器D. 十进制编码器17、集成电路74LS138是什么译码器(B )A. 二-十进制B. 3线-8线C. 8线-3线D. 8421BCD码18、二-十进制译码器有(B )A. 3个输入端,8个输出端B. 4个输入端,10个输出端C. 4个输入端,16个输出端D. 3个输入端,10个输出端19、七段共阴极半导体数码管要显示数码“2”,则与之相连接的显示译码器a~g引脚输出的电平应为(B )A. 110000B. 1101101C. 1111011D. 101101120、与模拟电路相比,数字电路主要的优点有(C )A. 容易设计B. 通用性强C. 抗干扰能力强D. 不需要电源21、一个班级中有五个班委委员,如果要开班委会,必须这五个班委委员全部同意才能召开,其逻辑关系属于什么逻辑(B )A. 或B. 与C. 与或非D. 非22、具有“置0”、“置1”、“保持原态”和“状态翻转”的全能触发器是(D )A. 同步RS触发器B. 基本RS触发器C. D触发器D. JK触发器23、方波的占空比是(A )A. 0.5B. 0.75C. 0.85D. 124、十进制数32的二进制代码为(A )A. 100000B. 011111C. 101010D. 10000125、清零后的5位移位寄存器,如果要将5位数码全部串行输入,需要配合的CP脉冲( A )A. 5B. 10C. 15D. 20二、判断题(√)1、加法器是计算机中央处理器中算术逻辑运算单元的最基本组成部分。

聊城大学《数字电路》期末复习题及参考答案

《数字电路》练习题及参考答案一、逻辑函数化简1.用卡诺图法将逻辑函数化简为最简与一一或表达式Y=ABC+ABD+CD'+AB C+A'CD'+ACDY=A+D2.用卡诺图法将逻辑函数化简为最简与一一或表达式Y=AB,+B,C+ΛD二、简答题1.时序逻辑电路在逻辑功能和电路结构上各有什么特点?答:逻辑功能上:任意时刻的输出不仅取决于这一时刻的输入,还与电路的历史状态有关。

电路结构上:①包含存储电路和组合电路;②存储器状态和输入变量共同决定输出。

3.简述触发器电路必须具备的两个基本特点。

答:1.有两个可以自行保持的状态;2.可以根据不同的输入置成。

或1状态三、设计题1.用4选1数字选择器(74HC153/2)产生逻辑函数:Z=AβC+A t C+BC(数据选择器输出方程为Y=D0(AAi)+D i(A i A0)+D2(A i A n)+D y(A i A ii))已知输出方程为:Y=(AA)Qo+(AA)S+(AA)Qf(AA)A将给定逻辑函数化为与输出方程对应的形式为:Y=Aβ,C+A BI+ABC+ABC另数据选择器输入接成:Al=A;Ao=8;D 0=D 2=C ,;D 1=1;D 3=C2 .用3线一8线译码器74HC138和门电路产生如下多输出逻辑函数。

Y 1=ACY 2=A ,B ,C+AffC ,+BCY i =B'C+ABCY i =AC=ΛffC+ΛBC=nι5+m 7=(m 5,m 7y=(Y 5,Y 7y<Y 2≈A ,B ,C+AffC ,+BC=A'B ,C+A;BC+AB ,C+ABC≈m i +m 3+fn i +m 7≈(m,,m 3,m 4'm ιy=(Y l 'Y i ,Y 4,Y 7y X=B'C+46C=A'B'C+A&C+ABC=,/+,%+%=(/'%6')'=(可匕工)画出电路为:则:Y=Z接电路为:3¾%J %41IΛβ与。

数电复习题(含答案)

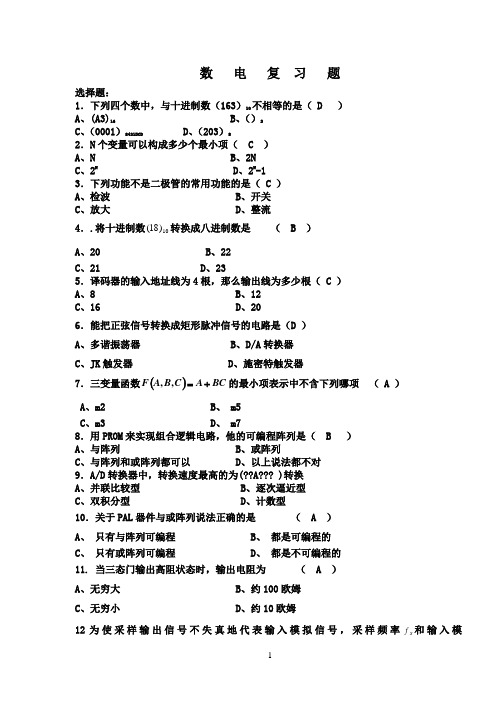

数 电 复 习 题选择题:1.下列四个数中,与十进制数(163)10不相等的是( D )A 、(A3)16B 、()2C 、(0001)8421BCD D 、(203)82.N 个变量可以构成多少个最小项( C )A 、NB 、2NC 、2ND 、2N -13.下列功能不是二极管的常用功能的是( C )A 、检波B 、开关C 、放大D 、整流4..将十进制数10)18(转换成八进制数是 ( B )A 、20B 、22C 、21D 、235.译码器的输入地址线为4根,那么输出线为多少根( C )A 、8B 、12C 、16D 、206.能把正弦信号转换成矩形脉冲信号的电路是(D )A 、多谐振荡器B 、D/A 转换器C 、JK 触发器D 、施密特触发器7.三变量函数()BC A C B A F +=,,的最小项表示中不含下列哪项 ( A )A 、m2B 、 m5C 、m3D 、 m78.用PROM 来实现组合逻辑电路,他的可编程阵列是( B )A 、与阵列B 、或阵列C 、与阵列和或阵列都可以D 、以上说法都不对9.A/D 转换器中,转换速度最高的为(??A??? )转换A 、并联比较型B 、逐次逼近型C 、双积分型D 、计数型10.关于PAL 器件与或阵列说法正确的是 ( A )A 、 只有与阵列可编程B 、 都是可编程的C 、 只有或阵列可编程D 、 都是不可编程的11. 当三态门输出高阻状态时,输出电阻为 ( A )A 、无穷大B 、约100欧姆C 、无穷小D 、约10欧姆12为使采样输出信号不失真地代表输入模拟信号,采样频率f s 和输入模拟信号的最高频率f ax Im 的关系是(C ) A 、 f s ≥f ax Im B 、f s ≤f ax Im C 、f s ≥2f ax Im D 、 f s ≤2f ax Im13. 下列说法不正确的是( C )A .集电极开路的门称为OC 门B .三态门输出端有可能出现三种状态(高阻态、高电平、低电平)C .OC 门输出端直接连接可以实现正逻辑的线或运算D.利用三态门电路可实现双向传输14. 以下错误的是( B )A .数字比较器可以比较数字大小B .实现两个一位二进制数相加的电路叫全加器C .实现两个一位二进制数和来自低位的进位相加的电路叫全加器D .编码器可分为普通全加器和优先编码器15. 下列描述不正确的是(A )A .触发器具有两种状态,当Q=1时触发器处于1态B .时序电路必然存在状态循环C .异步时序电路的响应速度要比同步时序电路的响应速度慢D .边沿触发器具有前沿触发和后沿触发两种方式,能有效克服同步触发器的空翻现象16.离散的,不连续的信号,称为( B )。

数字电路复习题

一、判断题(对的打“√”,错的打“×”共20 分)1、对于多输入端的CMOS与非门,在使用时不用的输入端悬空即可()2、TTL与非门的输入端接地时,其输入电流为零()3、在TTL门电路输出需要线与连接时,必须使用集电极开路门()4、组合逻辑电路中一定含有触发器()5、由卡诺图化简法得出的表达式不一定是最简表达式()6、基本RS触发器受触发脉冲CP控制()7、JK触发器,J=K=1时是计数状态()8、译码器是时序逻辑电路()9、组成七进制计数器最少需要四个触发器()10、施密特触发器的正、负向阈值电压相同()一、判断题(对的打“√”,错的打“×”共20 分)1、对于多输入端的TTL与非门,在使用时不用的输入端悬空即可()2、CMOS与非门的输入端接地时,其输入电流为零()3、对于低电平有效的“三态与非门”,当控制端E=1时是高阻态()4、组合逻辑电路的输出不但和现在的输入有关还和原状态有关()5、由公式化简法得出的表达式不一定是最简表达式()6、同步RS触发器受触发脉冲CP控制()7、JK触发器,当置“1”端S D=0时触发器的状态为“1”()8、计数器是时序逻辑电路()9、组成十进制计数器最少需要四个触发器()10、施密特触发器的正、负向阈值电压不相同()一选择题1、在二进制译码器中,若输入有4位代码,则输出有()信号。

① 2个②4个③8个④16个2、在下列电路中,只有()属于组合逻辑电路。

①触发器②计数器③数据选择器④寄存器3、组合逻辑电路的竞争-冒险是由于()引起的。

①电路不是最简②电路有多个输出③电路中存在延迟④电路使用不同的门电路4、能实现从多个输入端中选出一路作为输出的电路称为()。

①触发器②计数器③数据选择器④译码器5、能完成两个1位二进制数相加并考虑到低位来的进位的器件称为()①编码器②译码器③全加器④半加器6、只本位数而不考虑低位来的进位的加法称为()①全加②半加③全减④半减7、用代码代表特定信号或将代码赋予特定含义的过程称为()①译码②编码③数据选择④奇偶校验8、把代码的特定含义翻译出来得过程称为()①译码②编码③数据选择④奇偶校验9、如需要判断两个二进制数的大小或相等,可以使用()电路。

数字电路复习题及答案

《数字电子技术基础》复习题一.选择填空题(以下每小题后均给出了几个可供选择的答案,请选择其中一个最合适的答案填入空格中)1.处理 b 的电子电路是数字电路。

(a)交流电压信号(b)时间和幅值上离散的信号(c)时间和幅值上连续变化的信号(d)无法确定2.用不同数制的数字来表示2004,位数最少的是 d 。

(a)二进制(b)八进制(c)十进制(d)十六进制3.最常用的BCD码是 b 。

(a)5421码(b)8421码(c)余3码(d)循环码4.格雷码的优点是 c 。

(a)代码短(b)记忆方便(c)两组相邻代码之间只有一位不同(d)同时具备以上三者5.两个开关控制一盏灯,只有两个开关都闭合时灯才不亮,则该电路的逻辑关系是 a 。

(a)与非(b)或非(c)同或(d)异或6.已知F=ABC+CD,选出下列可以肯定使F=0的取值 d(a)ABC=011 (b)BC=11 (c)CD=10 (d)BCD=1117.2004个1连续异或的结果是 a 。

(a)0 (b)1 (c)不唯一(d)逻辑概念错误二、填空题(请在空格中填上合适的词语,将题中的论述补充完整)1.5的5421BCD码是0101 这个是8421码的。

2.逻辑表达式中,异或的符号是⊕,同或的符号是⊙。

3.逻辑函数常用的表示方法有真值表、逻辑函数式、逻辑图和卡诺图。

4.用代数法化简逻辑函数需要一定的经验和技巧,不容易确定化简结果是否是最简。

5.用卡诺图化简逻辑函数,化简结果一般是最简与-或式。

一.选择填空题(以下每小题后均给出了几个可供选择的答案,请选择其中一个最合适的答案填入空格中)1.实体(ENTITY)描述一个设计单元的 C D 的信息。

(a)行为、元件及连接关系(b)元件、子程序、公用数据类型(c)名称和端口的引脚等(d)可编译的设计单元2.结构体(ARCHITECTURE)用于描述设计单元的 A D 。

(a)行为、元件及连接关系(b)元件、子程序、公用数据类型(c)名称和端口的引脚等(d)可编译的设计单元3.在VHDL语言中,ARCHITECTURE中的语句都是 B 执行的语句。

数字电路逻辑设计复习题精选全文

可编辑修改精选全文完整版数字电路逻辑设计A复习题一、单选题(每小题2分,共计20分。

)1.一个比特时间是1ms,串行传输8个比特所需要的时间是()。

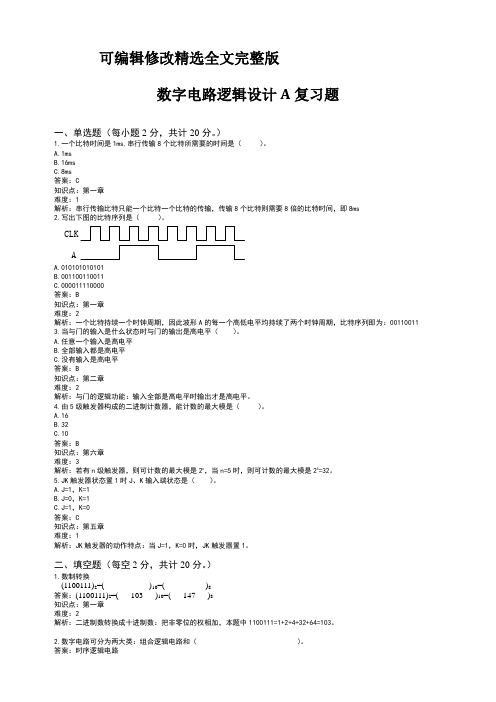

A.1msB.16msC.8ms答案:C知识点:第一章难度:1解析:串行传输比特只能一个比特一个比特的传输,传输8个比特则需要8倍的比特时间,即8ms2.写出下图的比特序列是()。

CLKAA.010*********B.001100110011C.000011110000答案:B知识点:第一章难度:2解析:一个比特持续一个时钟周期,因此波形A的每一个高低电平均持续了两个时钟周期,比特序列即为:001100113.当与门的输入是什么状态时与门的输出是高电平()。

A.任意一个输入是高电平B.全部输入都是高电平C.没有输入是高电平答案:B知识点:第二章难度:2解析:与门的逻辑功能:输入全部是高电平时输出才是高电平。

4.由5级触发器构成的二进制计数器,能计数的最大模是()。

A.16B.32C.10答案:B知识点:第六章难度:3解析:若有n级触发器,则可计数的最大模是2n,当n=5时,则可计数的最大模是25=32。

5.JK触发器状态置1时J、K输入端状态是()。

A.J=1,K=1B.J=0,K=1C.J=1,K=0答案:C知识点:第五章难度:1解析:JK触发器的动作特点:当J=1,K=0时,JK触发器置1。

二、填空题(每空2分,共计20分。

)1.数制转换(1100111)2=( )10=( )8答案:(1100111)2=( 103 )10=( 147 )8知识点:第一章难度:2解析:二进制数转换成十进制数:把非零位的权相加,本题中1100111=1+2+4+32+64=103。

2.数字电路可分为两大类:组合逻辑电路和()。

答案:时序逻辑电路知识点:第四章难度:1解析:逻辑电路的分类:当前输出只和当前输入有关的组合逻辑电路,当前输出不仅和当前输入有关,还和前一时刻的输出有关的时序逻辑电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

单项选择题1.下列表示与十六进制(AA)H 等值的数是( C )。

A (160) 10 B (276) 8 C (10101010) 2 D (251) 82. 如图1所示TTL 门电路,F(A,B)的逻辑为( A )。

A.F=A ⊕B B.F=A BC.F=ABD.F=A图13. 逻辑电路如右图,函数式为( A )。

A 、F=AB +C ; B 、F=AB +C ; C 、F=; D 、F=A+BC图24.n 个变量可以构成 ( C )个最小项。

A.nB.2nC.2nD.2n-15.已知逻辑函数 C B C A AB Y ++=与其相等的函数为( D )。

A. C A AB + C. C B AB + D. C AB +6. 采用OC门主要解决了( B ) A .TTL 与非门不能相与的问题 B. TTL与非门不能线与的问题 C. TTL与非门不能相或的问题 D. TTL与非门不能相加的问题7.八路数据选择器,其地址输入(选择控制)端有( C )个。

A. 1 B. 2 C. 3 D. 88. 只能按地址读出信息,而不能写入信息的存储器为( B )。

A.RAM B.ROM C.PROM D.EPROM9.单稳态触发器的输出状态有( A )。

A 、一个稳态、一个暂态B 、两个稳态C 、只有一个稳态D 、没有稳态10.T 触发器,在T=1时,加上时钟脉冲,则触发器 ( B )。

B FFA .保持原态 B. 翻转 C.置1 D. 置0填空题1.将八进制(123)8数转换为等值的十六进制数是___(53)H____________。

2.写出二进制数(-1001)2的原码和补码_______11001____、_10111___________。

3.集电极开路门的输出端____可以_____直接相连,以实现线与逻辑关系。

4.存储容量为4K×8位的RAM 存储器,其地址线为___12________条、数据线为_________8___条。

5.两输入同或门输入为01时,则输出为___0__________。

6.组合逻辑电路的输出只与当时的____当前_________状态有关,而与电路_________之前_____的输入状态无关。

它的基本单元电路是___逻辑门____________。

7.常用逻辑门电路的真值表如表1所示,则 F 1 、F 2 、F 3 分别属于何种常用逻辑门。

F 1_____同或门____________ ;2____与非门____________ ; F 3______或门____________ 。

8.A/D 转换是将模拟信号转换为数字信号,转换过程有__采样______________,___保持____________,___量化__________,_____编码__________。

9.在一个CP 脉冲作用下,引起触发器两次或多次翻转的现象称为触发器的__空翻___________,触发方式为_____边沿_________式或_____主从__________式的触发器不会出现这种现象。

三、解答题 1.(1)化简函数 C B ABCD D BC ABD D ABC D)C,B,F(A,++++=; (2)用卡诺图化简逻辑函数L=AB C+AB+A C+B C+C+CD 。

F(A,B,C,D)=AB+BC ’+BD ’ F (A,B,C,D )=AB ’+C ’+D2.分析如图3所示电路,写出其真值表和最简表达式。

L1=A ’B ’ L2=A ’B L3=A B ’ L4=A B图3单项选择题1.将二进制数(101011.101)2转换为等值的十进制数为( C )。

A 58.625 B 59.625 C 43.625 D 60.5252.逻辑函数Y (A ,B ,C )=∑)5,4,2,0(的最简与或非式为( A )。

A 、AB C A + B 、C A B A +C 、D 、C B C A B A ++3. 如图1所示TTL 门电路,当EN =0时,F 的状态为( A )。

A.F=A B B.F=A C.F=ABD.F=A B 图14.函数F(A,B,C)=AB+BC+AC 的最小项表达式为( B ) 。

A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7) C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7) 5. 如图2所示,该卡诺图所表示的逻辑关系式是( C )。

A .(0,3,5,7,14)L =∑B .(1,3,5,12)L =∑11&&&&A BL 1L 2L 3L 4AB CD 00011110100011110L11110×00××××××C.L B AD AC=++D.L B AB AD=++图26.下列电路中,不属于时序逻辑电路的是 ( B )。

A.计数器 B.全加器 C.寄存器 D.锁存器7. 若将一个TTL异或门(设输入端为A、B)当作反相器使用,则A、B端应怎样连接 ( B )。

A.A或B中有一个接低电平 B.A或B中有一个接高电平C.A和B并联使用D.不能实现8. N个触发器可以构成最大计数长度(进制数)为( D )的计数器。

A.NB.2NC.N 2D.2N9.RS触发器要求状态由0 → 1其输入信号为( A )。

A、RS=01B、RS=×1C、RS=×0D、RS=1010.可以用来代表A/D转换器分辨率的是 ( C )。

A. 转换时间B. 转换精度C. 转换器的位数D. 逐次逼近型或者双积分型转换器填空题1. 函数式Y=A B结果为1的条件是 __A=0,B=0 。

2.有一数码10010010,作为自然二进制数时,它相当于十进制数__146_________,作为8421BCD码时,它相当于十进制数_92____________。

3.将模拟信号转换为数字信号应采用_______模数(A/D)____________转换器。

4. 电路如图3F的逻辑表达式F=___________AB’_________。

图35.为了实现高的频率稳定度,常采用_____石英晶体________振荡器;单稳态触发器受到外触发时进入_________暂稳_____态。

6.触发器按功能分可分为__RS触发器_____________、____T触发器__________、_____T’触发器___________、__JK触发器______________和_______D触发器__________。

7.时序逻辑电路在结构上包含____组合逻辑电路__________和__存储电路__________两部分。

8.数字信号的特点是在_时间_________上和___幅度_________上都是断续变化的,其高电平和低电平常用_____1______和__0___________来表示。

9.触发器有_2_______个稳态,存储8位二进制信息要____8____个触发器。

B解答题1.化简逻辑函数(1)F AB AB BC BC =+++;(2)()()()L A B C A B C A B C =++++++。

(1)F=BC ’+B ’C+AB ’ (2)L=A+B ’C2、试设计一个4输入、4输出逻辑电路。

当控制信号C=0时,输出状态与输入状态相反;C=1时,输出状态与输入状态相同。

可以采用各种逻辑功能的门电路来实现。

设A1,A2,A3,A4为输入;B1,B2,B3,B4为输出 发现B1只与C 和A1有关(同理B2,B3,B4) A1(A2,A3,A4) C B1(B2,B3,B4) 0 0 1 0 1 0 1 0 0 1 1 1得出B1=A1⊙C B2=A2⊙CB3=A3⊙CB4=A4⊙C3.已知某电路输入信号A 、B 、C 、及输出信号Y 的波形图如图4所示, (1)写出Y (A,B,C )的逻辑函数表达式;(2)用3线-8线译码器74138和少量门电路实现逻辑函数Y 。

图 4 A B C Y 0 0 0 1 0 0 1 1111001110110110110011100000000011111A B CY0 1 0 10 1 1 01 0 0 11 0 1 11 1 0 11 1 1 0Y=C’+B’=(BC)’=m0+m1+m2+m4+m5+m6而74138系列的为输入地址码为0其余为1输出所以加个与非门,A2A1A0=ABC,得到解答如图单项选择题十六进制数转换为等值的二进制数是( B )。

1. 将(3D.CE)16A.01111101.11001110 B.00111101.11001110C.00111101.10001010 D.00101101.11011110的反码和补码分别是( D )。

2.带符号位二进制数(111011)2A.111011、100101 B. 100100、100100C. 100100、111011D. 100100、1001013.一只四输入端或非门,使其输出为1的输入变量取值组合有( D)种。

A. 7B. 8C. 15D. 14. 函数F(A,B,C)=AB+BC的最小项表达式为( A ) 。

A.F(A,B,C)=∑m(3,6,7) B. (A,B,C)=∑m(3,5,6,7)C.F(A,B,C)=∑m(0,2,3,4) D. F(A,B,C)=∑m(2,4,6,7)5. 如将TTL与非门作非门使用,则多余输入端应做 ( A ) 处理。

A. 全部接高电平B. 部分接高电平,部分接低电平C. 全部接低电平D. 部分接低电平,部分悬空6. 如图1所示,根据逻辑图,下列正确的逻辑式是( B )。

A.Y=B(A+C)+ABB. Y=A(B+C)+BCC. Y=A(B+C)+ACD. Y=C(B+A)+BC图17. 触发器三种触发方式中,( D )的触发器抗干扰能力最强。

A.电平触发 B.脉冲触发 C.主从触发 D.边沿触发8.已知74LS138译码器的输入三个使能端(E 1=1, E 2A = E 2B =0)时,地址码A 2A 1A 0=011,则输出 Y 7 ~Y 0是( C ) 。

A. 11111101B. 10111111C. 11110111D. 111111119.门电路的抗干扰能力取决于( A )。

A. 噪声容限 B.阈值电压 C. 扇出系数 D.空载功耗10.设图中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,Q 端输出电压波形恒为0的是:( BC )图。