mos的spice建模

spice模型

4)LEVEL=4 级别为4的MOS4模型又称BSIM(Berkeley short-channel IGFET model)模型。该模型 是由美国伯克利大学1984年专门为短沟道MOS 场效应晶体管而开发的模型,是AT&T Bell实验 室简练短沟道IGFET模型的改进型。模型是在 物理基础上建立的,模型参数由工艺文件经模 型参数提取程序自动产生,适用于数字电路和 模拟电路,而且运行时间比二级模型平均缩短 一半左右。现已发表的有BSIM1、BSIM2、 BSIM3和BSIM4等模型。

一、模型参数提取方法

实际电路分析中用到的一般都是元件的

等效电路模型。由于集成电路元件主要是 由半导体器件组成的,因此,这些等效电 路模型又都是以物理模型为基础的。

1)物理模型 半导体器件的物理模型是从半导体的基本方程 出发,并对器件的参数做一定的近似假设而得 到的有解析表达式的数学模型。一般说来,随 着集成电路集成度的提高,器件的结构、尺寸 都在发生变化,器件的物理模型就越加复杂。 在物理模型中经常包含有一些经验因子,目的 是为了使模型与实验结果符合得更好。一般说, 模型中考虑的因素越多,与实际结果就符合得 越好,但模型也就越复杂,在电路模拟中耗费 的计算工作量就越大。

体管模型。这两种模型均属于物理模型,其模

型参数能较好地反映物理本质并且易于测量,

便于理解和使用。

一、双极型晶体管的EM模型

C IC VBC IB + B + VBE IR aFIF

IS VBC VBE I C I S exp 1 exp V 1 Vt R t

二极管及其SPICE模型

PN结是微电子器件的基本结构之一,集成电

路和半导体器件的大多数特性都是PN结相互作 用的结果。如果通过某种方法使半导体中一部 分区域为P型,另一部分区域为N型,则在其交 界面就形成了PN结。 一般的二极管就是由一个PN结构成的,以PN 结构成的二极管的最基本的电学行为是具有单 向导电性,这在实际中有非常大的用处。

MOSFET器件热载流子效应SPICE模型

MOSFET器件热载流子效应SPICE模型戴佼容;刘斯扬;张春伟;孙陈超;孙伟锋【摘要】为了预测MOSFET器件在热载流子效应影响下的退化情况,建立了一套描述MOSFET器件热载流子效应的可靠性SPICE模型.首先,改进了BSIM3v3模型中的衬底电流模型,将拟合的精确度提高到95%以上.然后,以Hu模型为主要理论依据,结合BSIM3v3模型中各参数的物理意义及其受热载流子效应影响的物理机理,建立了器件各电学参数在直流应力下的退化模型.最后,依据准静态方法将该模型应用于热载流子交流退化模型中.实验数据显示,直流和交流退化模型的仿真结果与实测结果的均方根误差分别为3.8%和4.5%.该模型能准确反映MOSFET器件应力下电学参数的退化情况,且为包含MOSFET器件的电路的性能退化研究提供了模拟依据.【期刊名称】《东南大学学报(自然科学版)》【年(卷),期】2015(045)001【总页数】5页(P12-16)【关键词】MOSFET;热载流子效应;退化【作者】戴佼容;刘斯扬;张春伟;孙陈超;孙伟锋【作者单位】东南大学国家专用集成电路系统工程技术研究中心,南京210096;东南大学国家专用集成电路系统工程技术研究中心,南京210096;东南大学国家专用集成电路系统工程技术研究中心,南京210096;东南大学国家专用集成电路系统工程技术研究中心,南京210096;东南大学国家专用集成电路系统工程技术研究中心,南京210096【正文语种】中文【中图分类】TN322随着VLSI超大规模集成电路向深亚微米方向发展,器件沟道长度、结深和栅氧厚度等结构参数不断减小,但同时电源电压并未能随之等比减小,从而导致沟道区的横向和纵向电场显著增强,器件热载流子效应更加明显[1-2],电学特性(如阈值电压Vth、导通电阻Ron及饱和器件电流Idsat等)的退化更加严重.热载流子效应严重影响了深亚微米尺寸器件的可靠性和寿命,已经成为当今集成电路进一步往小尺寸发展的瓶颈.目前,已有大量关于MOSFET器件热载流子效应退化机理的研究[3-4],但对于能够描述MOSFET器件热载流子可靠性的SPICE模型涉及较少.实际上,SPICE模型是工艺代工厂和电路设计者之间的桥梁;基于MOSFET器件的SPICE模型,可以通过仿真手段来预测器件电学参数的变化,从而提前估算器件及相关集成电路的寿命.本文建立了一套热载流子退化的交直流可靠性SPICE模型.该模型可以准确反应MOSFET器件在不同直流及交流应力下工作一段时间后的电学特性退化状况,精确度在95%以上.此外,该模型还可进一步用于模拟包含MOSFET器件的电路的工作性能,从而为电路设计者提供更多的参考和指导.热载流子效应导致的MOSFET器件退化机理为:沟道中由碰撞电离产生的热载流子打断了Si—H键,形成界面态.这些界面态一方面可以俘获电荷,对器件的阈值产生影响;另一方面会增加载流子散射概率,影响载流子的迁移率,从而导致器件导通电阻及饱和电流等参数退化[5-8].根据Hu模型理论,可以得出MOSFET器件由热载流子效应导致的界面态的产生量为[9]式中,C为界面态产生量的常数项系数;Ids为应力下器件的漏源电流;Isub为应力下器件的衬底电流;H为模型的修正参数;W为器件的宽度;ψit为电子产生界面陷阱所需的最小能量;ψi为电子产生碰撞电离所需的最小能量,一般为1~3 eV;t为应力时间;Nit为界面态产生量随时间变化的指数项系数.在Hu模型理论中,计算器件参数的退化量时以Isub作为监测量.因此,本文首先需要建立准确的衬底电流模型;然后,根据Hu模型理论,在BSIM3v3模型的基础上建立热载流子退化的交直流可靠性模型;最后,依据一系列交直流应力退化数据来验证模型的精确度.由式(1)可知,对于MOSFET器件,由热载流子效应引起的退化程度与衬底电流密切相关.建立一个准确的衬底电流模型对于可靠性SPICE建模至关重要.在BSIM3v3模型中,衬底电流Isub的模型公式如下:式中,∂0,∂1,β0均为与器件工艺、结构相关的常数;Leff为沟道的有效夹断长度;Vds 为漏源电压;Rds为等效漏源电阻;Idso为漏端电流;Va为与饱和漏电压有关的参数;Vdseff为饱和漏电压,与偏置电压相关,可以通过BSIM3v3模型提供的计算公式来确定.式(2)给出的模型在计算Isub时无法很好地拟合所有条件,这是因为参数Leff并不是一个常数,而是与栅漏电压Vgd相关的,同时Vds-Vdseff与Isub呈指数关系,其计算误差会对衬底电流的计算带来较大影响.基于该公式的计算结果与实测数据的拟合情况如图1(a)所示.可以看出,拟合误差较大.本文根据Leff,Isub与Vgd的关系,得到如下的电压拟合关系式:式中,Vgs为栅源电压;Vth0为器件的阈值电压;Idsat为器件的饱和电流;Ic0,Ic1,Ic2为与漏源、栅源电压相关的参数;Ic3为常数项修正系数;Ic4,Ic5分别为与漏源电压相关的一阶、二阶系数;Ic6,Ic7分别为与栅源电压相关的一阶、二阶系数;Ic8为与漏源电压、栅源电压乘积相关的修正系数;η为Vdseff的修正系数,取值范围为[0,1]. 通过改变式(3)~(6)中的可调节参数,可以拟合出退化后器件的Isub退化曲线;根据多组不同偏置条件下Isub的测试数据,即可求解出Ic0~Ic8.基于修正Isub公式的计算值与测试值的拟合情况见图1(b).由图可知,此计算值与测试值更为接近,二者的均方根误差为2.7%,拟合的精确度达到95%以上.3.1 直流应力建模器件退化是由界面态的产生引起的.因此,BSIM3v3模型中考虑热载流子效应的影响时,需根据式(1),对器件性能影响较大的参数进行修正.此处需要修正的参数包括:与沟长相关的体电荷参数a0、与栅压有关的体电荷参数ags、基本迁移率参数u0、与Vgs相关载流子迁移率一次系数ua、与阈值电压相关的参数vth以及载流子饱和速度vsat.依据Hu模型理论,修正参数表达式如下:式中,a0c1,agsc1,u0c1,uac1,vsatc1,vthc1分别为与a0,ags,u0,ua,vsat,vth这5个参数相关的可靠性系数;a0nit,agsnit,u0nit,uanit,vsatnit,vthnit分别为与上述5个参数相关的物理参数;a0mit,agsmit,u0mit,uamit,vsatmit,vthmit分别为与上述5个参数相关的界面态产生量随时间变化的指数项系数.当器件发生退化时,利用式(7)~(12)便可计算出MOSFET在不同应力时间下的退化量.3.2 交流应力建模MOSFET器件通常工作在交流应力下.因此,交流建模对于研究实际工作时器件及电路的退化情况意义重大.本文采用了准静态的建模思想[10-11],即将交流应力分为许多小的时间段,每个时间段内的应力可近似为静态的,然后将每个时间段内的退化量叠加在一起以计算出总的退化量.该算法可用简化的Hu模型表达式说明,即式中,c为直流应力下界面态产生量的常数项系数;n为直流应力下界面态产生量随时间变化的指数项系数Mit.如图2所示,Vg为栅端电压,Δt为时间的采样间隔,且t2-t1=t3-t2=t4-t3=Δt.在t1~t2时间内,MOS器件的退化量按曲线1计算;t2~t3时间内,MOS器件的退化量按曲线2计算,但由于器件本身已存在退化量D1,故此时器件的退化过程应为:沿曲线2,从D=D1处开始,经过时间Δt后,退化量变为D2.将曲线2平移到曲线4处,所得曲线即为器件在t2~t3时间内的退化趋势.依此类推,在每个采样间隔Δt内进行直流近似计算,得到退化量,依次叠加,便可计算出总时间内的退化量.利用0.35 μm SOI工艺,制备MOSFET器件.器件栅氧化层厚度Tox=25nm,W/Leff=20/0.35,测试温度T=25 ℃.使用半导体参数测试仪4200对样片进行数据采集,运用最小二乘法并借助提模软件MBP完成对模型参数的提取.衬底电流参数为:Ic1=-7.654×10-5,Ic2=-3.377×10-3,Ic3=1.117,Ic4=-2.258×10-2,Ic5=0.017,Ic6=-5.179×10-3,Ic7=-5.926×10-4,Ic8=-2.56×10-2.可靠性模型参数为:a0c1=0.297,a0mit=3,a0nit=0.16,agsc1=6×10-4,agsmit=0.976,agsnit=0.039,u0c1=0.022,u0mit=5.5,u0nit=0.067,uac1=7.1×10-10,uamit=3,uanit=0.317,vsatc1=529.9,vsatmit=6.963,vthc1=3.4,vthmit=0.0 18,vthnit=0.133.5.1 直流模型验证图3为提模软件MBP中直流应力下模型计算值与测试值的拟合结果.由图可见,在不同的直流应力下,2×104 s后,相比无可靠性模型的模型计算值,基于可靠性模型的模型计算值与测试值更为接近.基于本文方法所建立的直流模型的模型计算值与测试值之间的均方根误差为3.8%,可见该模型能准确反映MOSFET器件的热载流子退化特性.5.2 交流模型验证交流模型验证的应力条件为:Vds=6 V,Vs=Vb=0 V(Vs,Vb分别为器件的漏端电压和衬底电压),Vgs表示幅值为4 V、周期为1 μm、占空比为50%、上升沿与下降沿时间均为300 ns的脉冲.测试时为避免外接导线电感引起的节点电势波动,需要在探针和被测器件的漏极接触点与地之间加一个47 μf的电容[12].图4为交流应力下模型计算值与测试值比较.由图可知,加交流应力2×104 s后,基于可靠性模型的模型计算值与测试值的均方根误差为4.5%,明显小于无可靠性模型的模型计算值与测试值的误差,说明本文建立的模型是准确合理的.本文依据MOSFET器件热载流子效应的可靠性物理研究和实验探索,建立了MOSFET器件的衬底电流模型和热载流子效应的直流模型,并在准静态思想的指导下建立了热载流子效应的交流模型,用直流模型和交流模型来模拟MOSFET器件的退化,模拟结果与实测结果较为吻合.基于此模型,电路性能随MOSFET器件退化而产生的变化亦可通过仿真预测,这为电路设计者提供了一定的参考和指导.[1]Poli S, Reggiani S, Baccarani G, et al. Full understanding of hot-carrier-induced degradation in STI-based LDMOS transistors in the impact-ionization operating regime [C]//2011 IEEE International Symposium on Power Semiconductor Devices and ICs. San Diego, CA, USA, 2011: 152-155.[2]Randriamihaja Y M, Zaka A, Huard V, et al. Hot carrier degradation: from defect creation modeling to their impact on NMOS parameters[C]//2012 IEEE International Reliability Physics Symposium. Anaheim, CA, USA, 2012: XT. 15.1-XT. 15.4.[3]Dawes M, Alavi M, Kim D M. AC/DC characterization of NMOS and PMOS hot-carrier-induced degradation under AC/DC stress[J]. IEEE Transactions on Electron Devices, 1990, 37(11): 2416-2419.[4]Starkov I, Enichlmair H, Tyaginov S. Charge-pumping extractiontechniques for hot-carrier induced interface and oxide trap spatial distributions in MOSFETs[C]//IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits. Singapore, 2012: 1-6.[5]Rozen J, Ahyi A C, Zhu X G, et al. Scaling between channel mobility and interface state density in SiC MOSFETs[J]. IEEE Transactions on Electron Devices, 2011, 58(11): 3808-3811.[6]Starkov I, Enichlmair H, Tyaginov S, et al. Analysis of the threshold voltage turn-around effect in high-voltage n-MOSFETs due to hot-carrier stress[C]//2012 IEEE International Reliability Physics Symposium. Anaheim, CA, USA, 2012: XT. 7.1-XT. 7.6.[7]Teo Z Q, Ang D S, Ng C M. Separation of hole trapping and interface-state generation by ultrafast measurement on dynamic negative-bias temperature instability[J]. IEEE Electron Device Letters, 2010, 31(7): 656-658.[8]Ji Z G, Zhang J F, Zhang W D, et al. Interface states beyond band gap and their impact on charge carrier mobility in MOSFETs[J]. IEEE Transactions on Electron Devices, 2012, 59(3): 783-790.[9]Hu C M, Tam S C, Hsu F C, et al. Hot-electron-induced MOSFET degradation—model, monitor, and improvement[J]. IEEE Journal of Solid-State Circuits, 1985, 20(1): 295-305.[10]Snyder E S, Campbell D V, Swanson S E, et al. Novel self-stressing test structures for realistic high-frequency reliability characterization[C]//1993 IEEE International Reliability Physics Symposium. Atlanta, GA, USA, 1993: 57-65.[11]Riedlberger E, Keller R, Reisinger H, et al. Modeling the lifetime of alateral DMOS transistor in repetitive clamping mode[C]//2010 IEEE International Reliability Physics Symposium. Anaheim, CA, USA, 2010: 175-181.[12]Bellens R, Heremans P, Groeseneken G, et al. The influence of the measurement setup on enhanced AC hot carrier degradation of MOSFETs[J]. IEEE Transactions on Electron Devices, 1990, 37(1): 310-313.。

高压功率VDMOST 的SPICE 直流模型

第23卷 第6期 2005年11月应用科学学报JOURNA L OF APP LIE D SCIE NCESV ol.23,N o.6 N ov.2005 收稿日期:2004207218; 修订日期:2004211212基金项目:国家“863”高技术研究发展计划资助项目(2003AA1Z 1400)作者简介:赵 野(1977-),男,辽宁绥中人,博士生,E 2mail :zhaoye @ 文章编号:025528297(2005)0620604206高压功率V DMOST 的SPICE 直流模型赵 野, 孙伟锋, 易扬波, 鲍嘉明(东南大学国家专用集成电路系统工程技术研究中心,江苏南京210096)摘 要:基于高压VDM OST 的物理机理和特殊结构,详细分析、推导了漂移区电阻、埋层电阻、内部节点电压及内部耗尽层宽度随外加偏压变化而变化的情形;采用数值计算的方法,建立了较精确的高压六角型VDM OST 三维物理模型,进而提出了VDM OST 的直流(DC )等效电路模型.该模型由level3NM OS 管、控制源、电容等元件组成,较准确地模拟了高压器件的特性.与以往文献的结果相比,该模型物理概念清晰,准确性高,避免过多工艺参数引入的同时,简化了等效电路.将该模型嵌入SPICE 进行仿真,得到了全电压范围内连续的I 2V 特性曲线,与实际测试结果相比,误差接近5%.关键词:模型;高压集成电路;高压VDM OST;漂移区;等效电路中图分类号:T N710;T N432 文献标识码:AA DC Model of H igh 2V oltage V DMOST for SPICE SimulationZH AO Y e , S UN Wei 2feng , YI Y ang 2bo , BAO Jia 2ming(National ASIC System Engineering Research Center ,Southeast Univer sity ,Nanjing 210096,China )Abstract :An accurate m odel for high 2v oltage hexag on VDM OST is derived based on a three 2dimensional structure and im plemented with SPICE.Drift region resistance ,buried layer resistance ,interior node v oltage and variation of internal capacitance with external applied v oltage are analyzed in detailed.A DC equivalent circuit m odel is als o proposed ,which includes a level 3NM OS transistor ,a controlled s ource and capacitance ,etc .It als o accounts for the quasi 2saturation effect in high v oltage device.This sim ple m odel with a clearphysical concept als o provides easy extraction of inter 2electrode capacitances.The I 2V simulation results are in g ood agreement with experimented results with the DC error approaching 5%within the entire v oltage range ,which can be used in practical applications.K ey w ords :m odel ;H VIC ;high 2v oltage VDM OST;drift region ;equivalent circuit 高压功率VDM OST 广泛用于平板显示驱动(PDP 、LC D 、LE D )以及汽车电子等领域.近年来随着高低压兼容工艺的成熟,高压集成电路(H VIC )应运而生,由于H VIC 集成了低压逻辑控制与高压功率驱动电路,因此得到了越来越广泛的应用.SPICE 是集成电路领域优秀的模拟软件,但是缺乏对高压器件的支持.因此建立准确的、可靠的高压器件SPICE 模型,用于高压集成电路的C AD 设计,成为迫切的需要.传统SPICE 电路宏模型建立在器件的测试结果之上,不能预测器件性能的变化.而基于器件的物理机理和结构提出的模型,能够较准确地预测器件性能的变化,从而进行SPICE 的仿真.文献[1]提出了一种导通电阻模型,其缺陷在于不能准确反映电阻及沟道随外加电压变化的情况;文献[2~6]基于矩形元胞从二维或准三维的角度,建立了VDM OST 的模型,克服了文献[1]的缺陷,但还不能反映器件的三维物理、电学特性;文献[7,8]从器件的结构出发,根据器件的物理特性分别建立了高低压的三维物理模型,并讨论了结构及工艺参数对器件特性的影响,准确地反映了器件的电学特性;但是它们皆是基于对矩形元胞的分析和讨论,并没有针对六角型高压VDM OST 的模型.本文从高压六角型VDM OST 的物理特性和结构出发,利用TS UPRE M 24和ME DICI 模拟结果分析了器件的电流、电场以及内部耗尽层情况,进而推导了漂移区压控电阻、内部节点电压、内部耗尽层宽度随外加偏压变化的情形,建立了较精确的高压六角型VDM OST 漂移区三维物理模型,弥补了模型[7,8]对于六角型元胞的不足;在物理模型基础上提出的VDM OST 等效电路,简单有效,适于工程应用的需要.1 器件结构图1即为高压VDM OST 结构纵向剖面图.从图1中可看出,有一个N +埋层和浓N 型漏连接层,将收集到的漏极电流经由浓N 型漏连接层传输到表面接触端,亦即把漏极电流从表面引出,其工艺与低压C M OS 工艺兼容.图1 H VIC 2VDM OS 纵向剖面图Fig.1 Cross 2section view of H VIC 2VDM OST VDM OST 的M OS 管沟道区是由双扩散形成的,双扩散工艺过程导致器件沟道浓度的不均匀分布.文献[9]已经提出了一个解决沟道不均匀掺杂的数值模型,但形式复杂,工艺参数繁多,不适于工程应用.在沟道尺寸较小的情况下,可以利用level3NM OS 管模型模拟VDM OST 的沟道部分,level3模型中NM OS 管的迁移率调制系数和载流子表面迁移率是两个关键的参数,对整个VDM OST 的导通电阻有重要的影响.图2为栅压等于5V ,漏压等于200V 条件下,ME DICI 模拟的电流、耗尽层的情况,揭示了电流路径以及耗尽层的扩展.由于体区耗尽层的存在,各个区域的厚度、向侧面耗尽的宽度会随着外加电压的变化而变化,亦即漂移区电阻是受外加电压控制的压控电阻.根据模拟的结果将器件的漂移区分为4个部分,如图3所示.在A 区中,电流沿着表面流向两个元胞的中间区域,然后再沿着P 体区与N -外延的P 2N 结耗尽层边缘流向B 区,P 2N 结耗尽层宽度受A 区末端电压V A 的控制,同时在A 区中栅下面的部分会形成积累层,由于这部分的电阻很小,相对于整个导通电阻来说可以忽略不计.在B 区,电流沿着一定的角度(α≈45°)流向漏端,电流所通过的截面和B 区的厚度跟随P 2N 结耗尽层的宽度发生变化,因此流经B 区的电流与V A 和B 区末端电压V B 有关.通过对ME DECI 模拟的结果对照可以看到电流偏转角α不随着器件结构和偏压而变化.在本文所阐述的模型中,认为B 区的掺杂浓度为准中性的,即n ≈N D .C 区的截面为六角型,其高度也与耗尽层宽度有关,因此C 区末端电压V C 也与V A 有关.通过几次深扩散形成的埋层结构,其浓度为非均匀分布,因此其电阻值也为非均匀的.本文采用了与工艺相关的精确的计算方法,利用器件和工艺模拟,得到较精确的电阻值,与实际结果很接近. 通过上述分析,A 、B 、C 区的电阻与各区的压降有关,而各区的压降又与流过该区的电流有关,以电阻作为中间变量,器件的电流电压特性可以通过一组隐含的方程组来描述,因此需要用数值方法来求得最后的结果.器件模型中包含的非线性元件,如压控电阻、压控电容等,可以用压控源或流控源的形式嵌入SPICE.对于非线性电阻可以描述成电压源的506 6期赵 野等:高压功率VDM OST 的SPICE 直流模型形式E RES =i R f (i R ,v R )(1)图2 对图1结构的ME DICI 模拟结果Fig.2 ME DICI simulation of H VIC 2VDMOST图3 VDM OST 单胞剖面图Fig.3 Cross 2section view of VDM OST2 漂移区模型体耗尽层的扩展如图4(a )所示,因为P 2N 结的边界不是平面的,假设在漂移区中的扩展边界斜率为X ′ΠY ′.由图4(b )中可以看到,由于多边形夹角的存在,电流在边角的分布很不均匀,因此在模型中,把电流流经的区域分为可变电阻R A 1区与可变电阻R A 2区(图4(b )中的阴影部分),其中R A 2区看作是半径与高度可变的圆形电阻区,A 区总电阻即为两者电阻的并联值.图4(a ) A 区耗尽层边界近似Fig.4(a) Depletion approximation of Aregion图4(b ) A 区电阻示意图Fig.4(b) Resistance of A region 对于R A 1而言,电流流过的是一个变截面的梯形体电阻,其阻值为R A 1=ρ0L P Y ′X ′ln11-X ′ΠL G (2) 在式(2)中,X ′、Y ′为耗尽层边缘在水平和竖直方向的坐标值.其值分别为X ′=W bd sin45°-(γW j -γ2W j )和Y ′=W bd cos45°+γW j ,γ为横向与纵向扩散的比例系数,其值约为0.8.其中L P 为P 体扩散区的边长,与版图的尺寸一致;L G 为有效栅长;耗尽层宽度是随A 区末端电压V A 变化的,因为P 体区的掺杂浓度很高,N -漂移区浓度相对较低,因此把它当作单边突变结来处理,可得W bd =2ε0εsi (V A -V bi -V S )ΠqN drift (3)其中,V bi 、V S 分别为P 2N 结的内建电势和源端的接触电压.对于R A 2区域,电流通过区域近似为可变截面的1Π6个圆形体电阻,采用与R A 1区同样的方法,积分可得R A 2=∫RAd R A 2=ρ0L G6πY ′X ′ln1+X ′πΠ6L G 1-X ′πΠ6L G(4)A 区的总电阻即为R A 1与R A 2的并联电阻,即R A =(R A 1R A 2)Π(R A 1+R A 2)参照图3所示的单胞结构,考虑其电流路径有一个角度α,所以六角型单胞的B 区电阻可以看作是一个如图5所示的三维结构.根据其几何结构的对称性,可以求得B 区电阻的值.对B 区进行积分,可得积分结果R B =ρ0K 332ln(-2(tan α)2L B +K 1-K 2)(K 1+K 2)(-2(tan α)2L B +K 1+K 2)(K 1-K 2)(5)其中B 区电阻高度606 应 用 科 学 学 报23卷 L B =W h -L G +X ′tan α(6)在式(5)中各个系数的含义如下K 1=2tan α[W h -(L G -X ′)](7)K 2=K 21+4(tan α)2K 3(8)K 3=2W h (L G -X ′)[1-(L G -X ′)](9)其中W h 为单胞宽度,通过以上的分析和计算,B 区的电阻基本表示完毕.分析和计算中不仅考虑了电阻区高度的变化,还考虑了电阻区截面积的变化,因此相对于文献[1]中提到的电阻模型更加精确.图5 B 区电阻示意图Fig.5 Three dimensional view of B region 电流所流过的C 区是一个截面为六角型的柱体,只有其高度随着外加电压的变化而变化,因此相对A 、B 区要简单一些.直接应用电阻率定义即可求解,结果如下R C =3ρ0(L T -L B -Y ′)27L 2A(10)其中L T 是外延的厚度,注意到C 区高度也是一个与耗尽层厚度有关的量,因此这部分电阻也是随电压而变化的.通过以上的推导计算,可以看到,正如引言中所述,A 区末端电压是一个关键变量,只要获得此处的电压,就可以建立关于V A 的方程组,进而求得各区分布的电压及电阻值.3 埋层及连接层电阻在作埋层扩散时,浓度的分布在几次工艺扩散中变化很复杂,与工艺密切相关,需要用器件及工艺模拟进行精确的参数提取.从TS UPRE M 24的模拟结果可以看到,杂质分布的等浓度线近似是一系列与x 轴平行的直线,仅认为沿纵向方向是非均匀掺杂.图6是TS UPRE M 24软件模拟的埋层杂质纵向分布曲线,其分布为高斯分布N D (y ,t )=Q 0πDt exp -y24Dt (11)上式中Q 0为离子注入剂量,D 为扩散系数,t 是扩散时间.对于已经形成的埋层来说t 为常数,则上式可以写成N D (y )=N D 0exp -y2L 2D(12)上式中L D =4Dt ;N D 0=Q 0ΠπDt .横向埋层电阻可以分为两个部分,如图2所示,其长度分别为L bur1和L bur2.埋层总电阻为两部分的电阻之和.这里只关心沿y 方向电阻率的变化,因此电阻率是y 的函数如图7所示,其微分电导是d G bur1=W L bur11ρ(y )d y(13)图6 N +埋层杂质的高斯分布曲线图Fig.6 Distribution of N +impurity buried layer图7 微分法求埋层电阻示意图Fig.7 The schematic of buried layer resistance for calculus对上式从y =0到y =L j 积分区间内积分G bur1=ρ0WL bur1∫Ljexp -y2L 2Dd y(14)其中ρ0=1ΠquN D 0,L j 为埋层杂质在外延中的扩散距离,则其电阻为R bur1=21π1LD 1ρ0L bur1W erfL jL D-1(15) 根据TS UPRE M 24和ME DICI 的模拟结果,可以看到流过埋层电阻的电流都是平行的,沿x 轴正方向不同位置取3个截面A 0、A 1和A 2,通过这几个截面的电流逐渐减小.取微元W ΔL Δy ,再取电流为线性分布,用平均功率法可以得到微元等效电阻I 2DΔR bur2=∫Lbur2x ΔL I D 2ρ(y )d x W Δy(16)706 6期赵 野等:高压功率VDM OST 的SPICE 直流模型由上式可以得到微分电导并积分ΔG bur2=3WΔL ∫Ljd yρ(y )(17)进而可得到这部分的电阻R bur2=231π1L D 1ρ0Lbur1W erfL jL D-1 (18)所以埋层总电阻R burry =R bur1+R bur2 图8所示为浓N +连接层杂质分布的曲线,从图中可以看到,其杂质分布与埋层杂质分布相似,均为高斯分布.因此可以利用与埋层电阻相似的办法求得此部分电阻的值.不过与埋层电阻不同的是,连接层是经过两次扩散形成的,所以实际上是两个电阻的串连.利用图7所示的微元法,可以求得连接层电阻的阻值R C ONT 3=21π1L D 1ρ0L C ONTW C ONTerfL jL D-1(19)上式中各个参数对应连接层形成时的参数值,L C ONT 和W C ONT 与连接层的版图窗口尺寸相对应.所以总的连接层电阻R C ONT =2R C ONT 3(20)图8 浓N +连接层杂质分布曲线图Fig.8 Distribution of N +contact layer4 等效电路从器件物理结构推导而来的电阻方程,代表了该器件的电学特性.根据电压与电流之间的关系可以求得漂移区的电流分别如下I A =V AR A (V A ,V S )(21)I B =V B -V A R B (V A ,V S )(22) 根据电流连续性定理,流过A 、B 和C 区,以及埋层电阻的电流是一致的.以电流作为中间变量,漂移区电压V DR 受外加漏极电压V DS 的控制,可以把漂移区上的电压看作一个受控电压源,而这个控制电压就是漏极电压.通过计算最终可得到外加漏极电压V DS 和漂移区上的电压V DR 之间对应的数值关系.VDM OST 物理模型的等效电路如图9所示.该等效电路包括3个部分:level3NM OS 晶体管模型,用来模拟VDM OST 的沟道区;一个电压控制电压源E ,模拟在漂移区上的电压降,两者串联起来;最后还有栅源和栅漏电容.因为电容对直流特性影响不是很大,所以采用了定值的栅源和栅漏电容.图9 VDM OST 物理模型的直流等效电路Fig.9 DC equivalent circuit of VDM OST physical m odel 等效电路在SPICE 中的测试电路如图10所示.在沟道宽度W =1μm ,漂移区浓度N d =8E14cm -3,栅氧化层厚度T ox =200nm ,沟长L ch =2μm ,外延厚度L T =30μm 条件下的SPICE 仿真结果和流片实测数据如图11所示.通过对比,在线性区模型仿真结果与实测数据基本吻合,在饱和区仿真结果与实测数据也很接近,在全电压范围内的误差接近5%.因为考虑了漂移区电阻的非线性变化,以及level3模型中电压对迁移率的调制效应,I 2V 模拟曲线也显示出模型的准饱和特征与实际测试结果相吻合.图10 导通特性测试电路Fig.10 On 2region characteristics circuit 在模拟中发现,随着漏压和栅压的增加,器件的准饱和效应越来越明显.这是因为当漏压和栅压足够高时,电压对迁移率的调制效应越明显,沟道中载806 应 用 科 学 学 报23卷 图11 直流I2V特性Fig.11 I2V characteristic of simulation and measure流子的迁移率降低,电流变小;同时,体耗尽层扩展导致漂移区中A区的截面变小,电阻也随着增大.当漏压达到足够高时,沟道区发生夹断.在SPICE模型中电子的饱和速度为一定值,因此电流在饱和区内的变化很小,几乎不变.在实际的工程应用中,器件的线性和准饱和特性很重要,本文提出的模型较准确地模拟了线性及准饱和特性,基本满足工程应用的需要,H VIC的C AD设计中.5 结 论本文在高压六角型VDM OST的物理机制下,建立了数值的三维物理模型,进而提出了基于现有仿真平台的等效电路模型.该模型物理概念清晰,简单准确,即避免了过多工艺参数的引入,又简化了等效电路.将该模型嵌入SPICE进行仿真,得到了全电压范围内连续的I2V特性曲线,与实际测试数据相比较,误差接近5%,已能够满足工程应用的需要.通过对内部节点电压的分析,容易求得内部非线性电容随外加偏压变化的情形,为建立瞬态模型提供参考.但是该模型没有考虑沟道漏端电压随栅压和漏压变化的情形,还有待进一步完善.该器件完整的模型将为高压六角型VDM OST的C AD设计提供简单而有效的手段.参考文献:[1] Sun S C,Plummer J D.M odeling of the on2resistance ofLDM OS,VDM OS,and VM OS power transistors[J].IEEET rans on E lectron Devices,1980,E D227(2):356-367. [2] Hu C,Chi M,Patel V M.Optimum design of powerM OSFET’s[J].IEEE T rans E lectron Devices,1984,E D231(10):1693-1700.[3] Victory J,Miller I,Scanchez J,et al.A new physicalpower M OSFET for improved simulation in power electronicdesign[J].IEEE T rans on E lectron Devices,1996,43(1):83-90.[4] Victory J,Scanchez J J,Demassa T A,et al.A staticphysical VDM OS m odel based on the charge2sheet m odel[J].IEEE T rans on E lectron Devices,1996,43(1):157-164.[5] K im Y S,F ossum J G.Physical DM OST m odeling for high2v oltage IC C AD[J].IEEE T rans on E lectron Devices,1990,37(3):797-803.[6] Chung Y,Burk D E.A physically based DM OS transistorm odel implemented in SPICE for advanced power IC C AD[A].International Symposium on P ower SemiconductorDevices&ICs[C].1995.340-345.[7] K im S D,K im I J,Han M K,et al.An accuration on2resistance m odel for low v oltage VDM OS devices[J].S olid2S tate E lectronics,1995,38(2):345-350.[8] Victory J,Mcandrew C C,Thoma R.A three2dimensional,physically based compact m odel for IC VDM OS transistors[J].Microelectronics Journal,1998,29:451-459.[9] Victory J,Scanchez J,Demassa T,et al.Application ofM OS charge2sheet m odel to nonuniform doping along thechannel[J].S olid2S tate E lctron,1995,38(8):1497-1503.(编辑:曹培华)906 6期赵 野等:高压功率VDM OST的SPICE直流模型。

功率MOS器件单粒子栅穿效应的PSPICE模拟

纵向 DMOS 晶体管的器件结构示于图 1 ,其源 、漏极不在同一平面 ,电流在体内垂直流动 , 具有较高的耐压能力 。

本工作建立的功率 MOS 器件 SEGR 效应的等效电路模型示于图 2 ,将 VDMOSFET 等效 为一个由横向 MOSFET 驱动的纵向 J FET 器件[1 ] ,横向 MOSFET 反映器件的快速开关特性 , 纵向 J F ET 模拟器件的高压大电流特性 ,用一个体二极管 Dbody并联一个 Vbreak来反映 p n - n + 结的单向特性和功率特性 ,器件的电容效应由栅2源电容 C21 、栅电极与沟道之间的氧化层电容 C23和积累层电容 C24来共同模拟 ,电感 L s 表示功率 MOSFET 的源 、漏极的寄生电感 ,控制电 路 E41 、D1 、Vpinch和控制电流源 IDSCHRG使 J EF T 的栅2源电压箝位于阈值电压 Vpinch ,从而使器

图 4 器件 SEGR 阈值 V GS随入射离子 等效 L ET 值的变化曲线

Fig. 4 Measured SEGR responses of vertical power MOSFET’s when exposed to different ions 1 ———L ET = 1115 MeV·cm2/ mg ;2 ———L ET =

164

原子能科学技术 第34卷

横向 MOSFET 模型参数 : V T0 = 311 V , Kp = 2185 ; 纵向 J F ET 模型参数 : R d = 0129 Ω ,βt = 2185 ×102 , V pinch = - 412 V ; 栅电容模型参数 : CIS = 1177 ×10 - 11 F , E0 = 911 MV/ cm , B = 5810 MeV·cm2/ mg 。 图 3 模拟了在等效 L ET 值等于 3711 MeV·cm2/ mg 的入射粒子 (286 MeV ,81Br) 作用下 , 不同源2漏偏置对器件栅穿电压 V GS的影响 ,从图中的模拟结果可以看出 ,器件的栅穿电压 V GS受到漏2源偏置电压 V DS的严重影响 , V DS值增高 ,器件发生 SE GR 的栅阈值电压相应降 低 。表 1 对模拟计算值和文献[ 5 ]中的实验数据进行了比较 ,可以看出 ,二者符合得较好 ,说明 该部分的等效电路模型 、参数提取方法和模拟计算是可靠的 。 图 4 给出了器件在固定漏2源偏置电压 ( V DS = 10 V) 下 ,具有不同等效 L ET 值的入射粒子 对器件栅穿电压 V GS的影响 ,从图中的模拟结果可以看出 ,器件的栅穿电压 V GS随入射离子 L ET 值的不同而发生较大的变化 ,L ET 值增高 ,器件发生 SEGR 的栅阈值电压相应降低 ,表 2 对模拟计算值和文献[ 5 ]中的实验数据进行了比较 ,可以看出 ,二者符合得较好 ,说明该部分的 等效电路模型 、参数提取方法和模拟计算也是可靠的 。

MOS spice参数

2002.5半导体器件4.61第四章MOSFET4.6 MOSFET 模型2002.5半导体器件4.624.6 MOSFET 模型本节内容MOSFET 模型简介MOS1和MOS2模型及模型参数介绍 电容模型(介绍Meyer 电容模型)模型参数提取2002.5半导体器件4.634.6.1 MOSFET 模型简介MOSFET 模型发展至今,已有五十多个模型。

下面简单介绍几个有代表性的模型:Level 1 ——MOS1模型(Shichman-Hodges 模型),该模型是Berkley SPICE 最早的MOST 模型,适用于精度要求不高的长沟道MOST 。

电容模型为Meyer 模型,不考虑电荷贮存效应Level 2 ——MOS2模型,该模型考虑了部分短沟道效应,电容模型为Meyer 模型或Ward-Dutton 模型。

Ward-Dutton 模型考虑了电荷贮存效应。

2002.5半导体器件4.644.6.1 MOSFET 模型简介Level 3 ——MOS3模型,为半经验模型,广泛用于数字电路设计中,适用于短沟道器件,对于沟道长度≥2µm 的器件所得模拟结果很精确。

BSIM 模型——B erkeley S hort-Channel I GFET M odel 。

BSIM 模型是专门为短沟道MOST 而开发的模型。

目前已经发展到BSIM4模型。

Level 4 ——BSIM1模型,适合于L ≈1µm ,t ox ≈15nm 的MOSFET 。

4.6.1 MOSFET 模型简介BSIM1模型考虑了小尺寸MOST 的二阶效应包括 垂直电场对载流子迁移率的影响; 速度饱和效应;DIBL (漏场感应势垒下降)效应; 电荷共享;离子注入器件的杂质非均匀分布; 沟道长度调制效应; 亚阈值导电;参数随几何尺寸的变化基本公式是萨方程的修正4.6.1 MOSFET 模型简介HSPICE Level 28 ——改进的BSIM1模型,适用于模拟电路设计,目前仍有广泛应用。

MOS工艺角SPICE模型参数获取方法[发明专利]

![MOS工艺角SPICE模型参数获取方法[发明专利]](https://img.taocdn.com/s3/m/3b13b606effdc8d376eeaeaad1f34693daef103b.png)

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 202011309907.8(22)申请日 2020.11.20(71)申请人 上海华力微电子有限公司地址 201203 上海市浦东新区自由贸易试验区高斯路568号(72)发明人 陈金明 (74)专利代理机构 上海浦一知识产权代理有限公司 31211代理人 焦天雷(51)Int.Cl.G06F 30/398(2020.01)G06F 30/17(2020.01)(54)发明名称MOS工艺角SPICE模型参数获取方法(57)摘要本发明公开了一种MOS工艺角SPICE模型参数获取方法,包括:根据MOS器件类型将选定工艺角上的参数拷贝到FNSP或SNFP中;将相关工艺参数和电容参数设定为FNSP或SNFP上相应的指定值;将选定工艺角上参数之外的其它参数乘以指定系数,获得FNSP或SNFP上的工艺角参数。

本发明在工艺角参数里面引入模型参数电子通道长度偏差/电子通道宽度偏差的差值长度偏差值/宽度偏差值的概念,在不改变物理尺寸的前提下,修正器件的电学尺寸,从而改变器件的电学特性,实现快速提取FNSP/SNFP的工艺角模型。

权利要求书1页 说明书4页 附图1页CN 112507654 A 2021.03.16C N 112507654A1.一种MOS工艺角SPICE模型参数获取方法,其特征在于,包括以下步骤:S1,根据MOS器件类型将选定工艺角上的参数拷贝到FNSP或SNFP中;S2,将相关工艺参数和电容参数设定为FNSP或SNFP上相应的指定值;S3,将选定工艺角上参数之外的其它参数乘以指定系数,获得FNSP或SNFP上的工艺角参数。

2.如权利要求1所述的MOS工艺角SPICE模型参数获取方法,其特征在于:对于NMOS,将其FF工艺角数参数直接拷贝到FNSP,将相关工艺参数和电容参数设为FNSP上的指定值,将其它参数乘以指定系数,得到FNSP上的工艺角参数。

跨导运算放大器及其Spice电路模型的构建

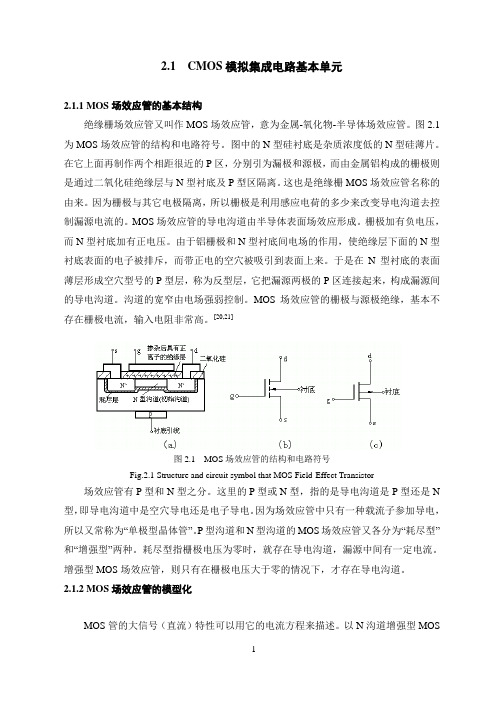

2.1 CMOS模拟集成电路基本单元2.1.1 MOS场效应管的基本结构绝缘栅场效应管又叫作MOS场效应管,意为金属-氧化物-半导体场效应管。

图2.1为MOS场效应管的结构和电路符号。

图中的N型硅衬底是杂质浓度低的N型硅薄片。

在它上面再制作两个相距很近的P区,分别引为漏极和源极,而由金属铝构成的栅极则是通过二氧化硅绝缘层与N型衬底及P型区隔离。

这也是绝缘栅MOS场效应管名称的由来。

因为栅极与其它电极隔离,所以栅极是利用感应电荷的多少来改变导电沟道去控制漏源电流的。

MOS场效应管的导电沟道由半导体表面场效应形成。

栅极加有负电压,而N型衬底加有正电压。

由于铝栅极和N型衬底间电场的作用,使绝缘层下面的N型衬底表面的电子被排斥,而带正电的空穴被吸引到表面上来。

于是在N型衬底的表面薄层形成空穴型号的P型层,称为反型层,它把漏源两极的P区连接起来,构成漏源间的导电沟道。

沟道的宽窄由电场强弱控制。

MOS场效应管的栅极与源极绝缘,基本不存在栅极电流,输入电阻非常高。

[20,21]图2.1MOS场效应管的结构和电路符号Fig.2.1 Structure and circuit symbol that MOS Field-Effect Transistor 场效应管有P型和N型之分。

这里的P型或N型,指的是导电沟道是P型还是N 型,即导电沟道中是空穴导电还是电子导电。

因为场效应管中只有一种载流子参加导电,所以又常称为“单极型晶体管”。

P型沟道和N型沟道的MOS场效应管又各分为“耗尽型”和“增强型”两种。

耗尽型指栅极电压为零时,就存在导电沟道,漏源中间有一定电流。

增强型MOS场效应管,则只有在栅极电压大于零的情况下,才存在导电沟道。

2.1.2 MOS场效应管的模型化MOS管的大信号(直流)特性可以用它的电流方程来描述。

以N沟道增强型MOS管为例,特性曲线和电流方程如图2.2所示。

图2.2 特性曲线和电流方程Fig.2.2 Characteristic property curve and electric current equation如果栅源偏置电压GS V 大于MOS 管的阈值电压T V ,则在P 型衬底的表面由于静电感应会产生大量的电子,形成导电沟道。

VDMOS等效电路的SPICE模型

区构成 J F ET 的栅极 , N - 漂移区 构成 J FET 的 漏 极.如图 2 所示 ,当漏极电压升高或漏极电流变大 时 ,PN 结反偏 , P 体区 对 N - 漂移区的耗尽 扩展影 响了电流通路 ,耗尽层展宽 ,J FE T 电流导通沟道变 窄 ,相当于引起 J FE T 的 Pinchi ng Off 效应. 当 P 体 区之间 的距 离越 来越 小时 , 寄生 J F ET 将对 VD2 MO S 性能产生重要影响. 随着微电子工艺从微米向 亚微米发展 ,VDMO S 单胞越来越密 , P 体区之间的 距离越来越小. 寄生 J F ET 将增加颈区电阻 ,同时也 将引起准饱和效应 ,限制了漏极的最大电流.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 F VSB φ

ε Si 2 F δ φ 2 F V SB φ 4C oxW

MOS器件二阶效应

(4)迁移率修正

在栅电压增加时,表面迁移率率会有所下降, 其经验公式为:

E EXP

ε Ecrit tOX Si μS μ0 ε VGS VTH E traVDS OX

CGB=CGB1+CGB2

CGS=CGS1+CGS2

CGD=CGD1+CGD2

其中不随偏压而变的部分是栅极与源区、漏区的交叠氧化层电容以 及栅与衬底间的交叠氧化层电容(在场氧化层上),即:

CGB2=CGB0L CGS2=CGS0W

CGD2=CGD0W

MOS电容模型

(2)栅电容 随偏压而变的栅电容是栅氧化层电容与空间电荷区电容 相串联的部分。列出了不同工作区栅电容的变化如下: 工作区 截止区 非饱和区 饱和区 CGB1 COXWLeff 0 0 CGS1 0 COXWLeff/2 (2/3)COXWLeff CGD1 0 COXWLeff/2 0

2 LX N DS N A S K 2VBS K1 1 1 S VTH Leff NA

(4)窄沟道效应

VTH K 3 K 3bVBS

W

t OX

'

eff

W0

S

短沟道MOS场效应管BSIM3模型

迁移率

一个好的表面迁移率模型对于MOSFET模型的精度是致关重要的。 一般讲,迁移率与很多工艺参数及偏置条件有关。BSIM3中所提供的

§ MOS场效应晶体管及其SPICE模型

MOS管的结构尺寸缩小到亚微米范围后,多维的物理效应和寄生 效应使得对MOS管的模型描述带来了困难。模型越复杂,模型参 数越多,其模拟的精度越高。但高精度与模拟的效率相矛盾。依 据不同需要,常将MOS模型分成不同级别。SPICE2中提供了几 种MOS场效应管模型,并用变量LEVEL来指定所用的模型。

2 F VSB φ

2 F φ

MOS1模型器件工作特性

(2)饱和区 当VGS>VTH,VDS>VGS-VTH,MOS管工作在饱和区。

电流方程为:

I DS KP W VGS VTH 2 1 λVDS 2 L0 2 LD

(3)两个衬底PN结

两个衬底结中的电流可用类似二极管的公式来模拟。

mj

C jsw0

PS 1 VBS V0

mSW

C BD C j0

AD 1 VBD V0

mj

C jsw0

PD 1 VBD V0

mSW

MOS电容模型

(2)栅电容

栅电容CGB,CGS,CGD包括随偏压变化及不随偏压变化两部分:

式中,µ0表面迁移率;Ecrit为栅-沟道的临界电场强度; Etra是横向电场系数,它表示VDS对栅-沟道电场的影响; EEXP为迁移率下降的临界指数系数。

MOS器件二阶效应

(5)沟道长度调制效应 当VDS增大时,MOS管的漏端沟道被夹断并进入饱和, VDS进一步增大,该夹断点向源区移动,从而使沟道

随着VDS的增加,在漏区这一边的耗尽层宽度会有所增加,这时漏区

和源区的耗尽层宽度WD和WS分别为:

WD X D 2 F VBS VDS φ

上式中,

WS X D 2 F VBS φ

XD

2 Si ε qN SUB

,因此γS修正为:

1 Xj γS γ1 2 L0 2 LD

的有效长度减小,这就是沟道长度调制效应 。 在考虑了沟道长度调制效应后,器件的有效沟道长 度为:

L L0 2LD Λ

式中:

Λ

2 Si ε VDS VDSAT qN

MOS器件二阶效应

(6)载流子有限漂移速度引起的电流饱和 对于同样的几何尺寸比、同样的工艺和偏置,短沟道 器件比起长沟道器件来讲饱和电流要小。 在MOS2模型中,引入了参数νmax表示载流子的最大 漂移速率,于是有:

LEVEL=1 MOS1模型 Shichman-Hodges模型

LEVEL=2 MOS2模型 二维解析模型 LEVEL=3 MOS3模型 半经验短沟道模型

LEVEL=4 MOS4模型 BSIM(Berkeley short-channel IGFET

model)模型

MOS1模型

Xj γS γ1 L0 2 LD

阈值电压提高。

2W 1 1 Xj

可见,当沟道长度L减小时阈值电压降低,而沟道宽度W变窄时

[VTH VT0 γs

2 F VSB 2 F ] φ φ

MOS器件二阶效应

(2)静电反馈效应

νmax

I DSAT WQ CHAN

MOS器件二阶效应

(7)弱反型导电

MOSFET并不是一个理想的开关,实际上当VGS<VTH时在表面处 就有电子浓度,也就是当表面不是强反型时就存在电流。这个电流称 为弱反型电流或次开启电流。SPICE2中定义一个新的阈值电压VON,

它标志着器件从弱反型进入强反型。当VGS<VON时为弱反型,当VGS>

不同工作区的栅电容

串联电阻对MOS器件的影响

漏区和源区的串联电阻会严重地影响MOS管的电学特性,串联电 阻的存在使加在漏源区的有效电压会小于加在外部端口处的电压。 SPICE2等效电路中插入了两个电阻rD和rS,它们的值可在模型语句: “.MODEL ”中给定,也可通过MOSFET中的NRD和NRS来确定 。

2WS 2WD 1 1 γ1 α α 1 1 D S Xj Xj

可见,由于VDS的增加而造成的WD增加,会使阈值电压进一步下降。

[VTH VT0 γs

2 F VSB 2 F ] φ φ

MOS器件二阶效应

(3)窄沟道效应

实际的栅总有一部分要覆盖在场氧化层上(沟道宽度以外),因此场氧 化层下也会引起耗尽电荷。这部分电荷虽然很少,但当沟道宽度W很 窄时,它在整个耗尽电荷中所占的比例将增大。与没有“边缘”效应

时的情况相比较,栅电压要加得较大才能使沟道反型。

这时V TH被修正为:

VTH VT0 γ

(1)短沟和窄沟对阈值电压的影响;(6)漏感应引起位垒下降; (2)横向和纵向的非均匀掺杂; (7)沟道长度调制效应; (3)垂直场引起的载流子迁移率下降(8)衬底电流引起的体效应, (4)体效应; (9)次开启导电问题;

(5)载流子速度饱和效应;

(10)漏/源寄生电阻。

短沟道MOS场效应管BSIM3模型

电流方程为:

I DS K P W L0 2 LD VGS VTH VDS 1 VDS 2 1 λVDS 2

式中: KP-本征跨导参数; λ-沟道长度调制系数;

W-沟道宽度 ; LD-沟道横向扩散长度 ;

L0-版图上几何沟道长度,L0-2 LD=L为有效沟道长度 ; VTH-阈值电压: VTH VT0 γ

MOS3 模型

MOS3模型参数大多与MOS2相同,但其阈值电压、饱和电流、沟 道调制效应和漏源电流表达式等都是半经验公式,并引入了A)和κ(KAPPA)。

下面分别讨论MOS3半经验公式及这三个参数的意义: (1)阈值电压的半经验公式

VTH VFB

8.15 10 22 2 F η φ γFS 2 F VBS FN 2 F VBS φ φ 3 C OX L

(3)沟道宽度对阈值电压的影响;

(4)迁移率随表面电场的变化; (5)沟道夹断引起的沟道长度调制效应;

(6)载流子漂移速度限制而引起的电流饱和效应;

(7)弱反型导电。

MOS器件二阶效应

(1)短沟道对阈值电压的影响

沟道长度L的减少,使衬底耗尽层的体电荷对阈值电压贡献减

少。体电荷的影响是由体效应阈值系数γ体现的,它的变化使V TH 变化。考虑了短沟效应后的体效应系数γS为:

迁移率公式是:

阈值电压

(1)垂直方向非均匀掺杂

VTH VT0 K 1 S VBS S K 2VBS

(2)横向非均匀掺杂

VTH VT0 K 1 S VBS S K 2VBS

(3)短沟道效应

VTH VT0 K1 S VBS

2 LX N DS N A K1 1 1 S Leff NA

FS为短沟道效应的校正因子。

式中,η是模拟静电反馈效应的经验模型参数,

MOS3 模型

(1)阈值电压的半经验公式

在MOS3中采用改进的梯形耗尽层模型,考虑了圆柱 形电场分布的影响,如图所示。图中Wc为圆柱结耗尽

层宽度,Wp为平面结耗尽层宽度 。

L G S Xj Wp Ws Xj1 tox W0 D

Wc

MOS3 模型

(2)表面迁移率调制

表示迁移率和栅电场关系的经验公式为:

S

1 V GSVTH

0

式中经验模型参数θ称为迁移率调制系数 。

MOS3 模型

(3)沟道长度调制减小量的半经验公式 当VDS大于VDSAT时,载流子速度饱和点的位置逐渐移 向源区,造成沟道长度调制效应。沟道长度的减小量ΔL 为:

rD=RshNRD rS=RshNRS

式中,Rsh-漏扩散区和源扩散区薄层电阻 ; NRD—漏扩散区等效的方块数; NRS—源扩散区等效的方块数。

§短沟道MOS场效应管BSIM3模型

BSIM(Berkeley short-channel IGFET model)模型是专门为短沟道