MOSFET隔离型高速驱动电路

隔离mosfet mos管 场效应管模块 替代继电器电路-概述说明以及解释

隔离mosfet mos管场效应管模块替代继电器电路-概述说明以及解释1.引言1.1 概述隔离MOSFET(MOS管)场效应管模块作为一种新型的电子器件,正在逐渐成为替代传统继电器电路的热门选择。

传统的继电器电路由于存在机械结构,在工作过程中容易产生噪声、寿命短、响应时间长等问题,限制了其在现代电子设备中的应用。

而隔离MOSFET场效应管模块因其具有高速响应、可靠性强、功耗低等特点,逐渐受到了工程师和电子爱好者的青睐。

本文将重点介绍隔离MOSFET(MOS管)和继电器电路的基本原理和特点,分析它们在不同应用场景下的工作原理及优缺点。

通过比较两者的特点,旨在探讨隔离MOSFET(MOS管)作为继电器电路的替代品的可行性和推广性。

本文将分为三个部分来进行阐述:引言、正文和结论。

引言部分概述了文章的主要内容和结构,同时阐述了撰写本文的动机和目的。

正文部分将详细介绍MOSFET(MOS管)和继电器电路的基本原理以及它们的工作原理和应用场景。

结论部分将总结MOSFET(MOS管)在替代继电器电路中的优势,并分析其在实际应用中的可行性和推广性。

通过详细的论述和分析,有助于读者全面了解隔离MOSFET(MOS 管)和继电器电路的不同特点,进而评估隔离MOSFET(MOS管)作为继电器电路的替代品的可行性,并为相关领域的工程师和研究人员提供参考和借鉴。

随着科技的不断发展和进步,寻找更加先进、高效、可靠的电子器件,已经成为了当前电子工程领域的一项重要任务。

1.2文章结构文章结构:本文主要分为引言、正文和结论三个部分。

在引言部分,我们将对本文的概述进行介绍,解释MOSFET (MOS管)和继电器电路的基本概念及其作用。

接着将介绍文章的结构和主要内容,提供给读者一个清晰的整体框架。

最后,说明本文的目的,即研究和探讨隔离MOSFET MOS管场效应管模块替代继电器电路的可行性和优势。

正文部分将主要分为两个章节,第一章节将详细介绍MOSFET (MOS 管)的基本原理和特点,包括其结构、工作原理和优势。

常见的MOSFET驱动方式驱动电路的参数计算

常见的MOSFET驱动方式,驱动电路的参数计算在简单的了解MOS管的基本原理以及相关参数后,如何在实际的电路中运用是我们努力的方向。

比如在实际的MOS驱动电路设计中,如何去根据需求搭建电路,计算参数,根据特性完善电路,根据实际需求留余量等等,在这些约束条件下搭建一个相对完善的电路。

参考了一些资料后,就我目前的需求和自身的理解力分享相关的一些笔记和理解。

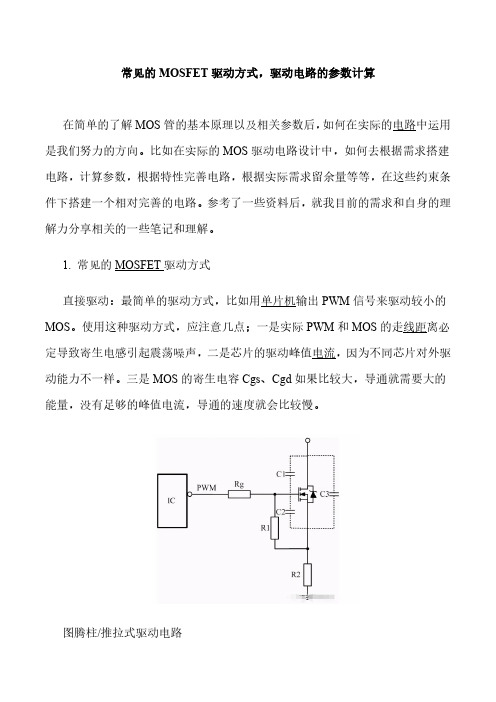

1.常见的MOSFET驱动方式直接驱动:最简单的驱动方式,比如用单片机输出PWM信号来驱动较小的MOS。

使用这种驱动方式,应注意几点;一是实际PWM和MOS的走线距离必定导致寄生电感引起震荡噪声,二是芯片的驱动峰值电流,因为不同芯片对外驱动能力不一样。

三是MOS的寄生电容Cgs、Cgd如果比较大,导通就需要大的能量,没有足够的峰值电流,导通的速度就会比较慢。

图腾柱/推拉式驱动电路由两个三极管构成,上管是NPN型,下管是PNP型三极管,两对管共射联接处为输出端,结构类似于乙类推挽功率放大器。

利用这种拓扑放大驱动信号,增强电流能力。

(驱动IC内部也是集成了类似的结构)隔离式驱动电路为了满足安全隔离也会用变压器驱动。

如图其中R1抑制振荡,C1隔直流通交流同时防止磁芯饱和。

隔离式的驱动电路不太常见,就不做过多的了解。

小结:当然除以上驱动电路之外,还有很多其它形式的驱动电路。

对于各种各样的驱动电路并没有一种是最好的,只能结合具体应用,选择最合适的拓扑。

2.驱动电路的参数计算我的实际工作中碰到最多的驱动电路是以下这种能够控制开关速度的驱动电路,我就以它举例做进一步的分析。

如图,在驱动电阻Rg2上并联一个二极管。

其中D1常用快恢复二极管,使关断时间减小同时减小关断损耗,Rg1可以限制关断电流,R1为mos管栅源极的下拉电阻,给mos管栅极积累的电荷提供泄放回路。

(根据MOSFET栅极高输入阻抗的特性,一点点静电或者干扰都可能导致MOS管误导通,所以R1也起降低输入阻抗作用,一般取值在10k~几十k)Lp为驱动走线的杂散寄生电感,包括驱动IC引脚、MOS引脚、PCB走线的感抗,精确的数值很难确定,通常取几十nH。

详细讲解MOSFET管驱动电路

详细讲解M O S F E T管驱动电路在使用MOS管设计开关电源或者马达驱动电路的时候,大部分人都会考虑MOS的导通电阻,最大电压等,最大电流等,也有很多人仅仅考虑这些因素;这样的电路也许是可以工作的,但并不是优秀的,作为正式的产品设计也是不允许的;下面是我对MOSFET及MOSFET驱动电路基础的一点总结,其中参考了一些资料,非全部原创;包括MOS管的介绍,特性,驱动以及应用电路;1,MOS管种类和结构MOSFET管是FET的一种另一种是JFET,可以被制造成增强型或耗尽型,P沟道或N沟道共4种类型,但实际应用的只有增强型的N沟道MOS管和增强型的P沟道MOS管,所以通常提到NMOS,或者PMOS指的就是这两种;至于为什么不使用耗尽型的MOS管,不建议刨根问底;对于这两种增强型MOS管,比较常用的是NMOS;原因是导通电阻小,且容易制造;所以开关电源和马达驱动的应用中,一般都用NMOS;下面的介绍中,也多以NMOS 为主;MOS管的三个管脚之间有寄生电容存在,这不是我们需要的,而是由于制造工艺限制产生的;寄生电容的存在使得在设计或选择驱动电路的时候要麻烦一些,但没有办法避免,后边再详细介绍;在MOS管原理图上可以看到,漏极和源极之间有一个寄生二极管;这个叫体二极管,在驱动感性负载如马达,这个二极管很重要;顺便说一句,体二极管只在单个的MOS管中存在,在集成电路芯片内部通常是没有的;2,MOS管导通特性导通的意思是作为开关,相当于开关闭合;NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况低端驱动,只要栅极电压达到4V或10V就可以了;PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC时的情况高端驱动;但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS;3,MOS开关管损失不管是NMOS还是PMOS,导通后都有导通电阻存在,这样电流就会在这个电阻上消耗能量,这部分消耗的能量叫做导通损耗;选择导通电阻小的MOS管会减小导通损耗;现在的小功率MOS管导通电阻一般在几十毫欧左右,几毫欧的也有;MOS在导通和截止的时候,一定不是在瞬间完成的;MOS两端的电压有一个下降的过程,流过的电流有一个上升的过程,在这段时间内,MOS管的损失是电压和电流的乘积,叫做开关损失;通常开关损失比导通损失大得多,而且开关频率越快,损失也越大;导通瞬间电压和电流的乘积很大,造成的损失也就很大;缩短开关时间,可以减小每次导通时的损失;降低开关频率,可以减小单位时间内的开关次数;这两种办法都可以减小开关损失;4,MOS管驱动跟双极性晶体管相比,一般认为使MOS管导通不需要电流,只要GS电压高于一定的值,就可以了;这个很容易做到,但是,我们还需要速度;在MOS管的结构中可以看到,在GS,GD之间存在寄生电容,而MOS管的驱动,实际上就是对电容的充放电;对电容的充电需要一个电流,因为对电容充电瞬间可以把电容看成短路,所以瞬间电流会比较大;选择/设计MOS管驱动时第一要注意的是可提供瞬间短路电流的大小;第二注意的是,普遍用于高端驱动的NMOS,导通时需要是栅极电压大于源极电压;而高端驱动的MOS管导通时源极电压与漏极电压VCC相同,所以这时栅极电压要比VCC大4V或10V;如果在同一个系统里,要得到比VCC大的电压,就要专门的升压电路了;很多马达驱动器都集成了电荷泵,要注意的是应该选择合适的外接电容,以得到足够的短路电流去驱动MOS管;上边说的4V或10V是常用的MOS管的导通电压,设计时当然需要有一定的余量;而且电压越高,导通速度越快,导通电阻也越小;现在也有导通电压更小的MOS管用在不同的领域里,但在12V汽车电子系统里,一般4V导通就够用了;MOS管的驱动电路及其损失,可以参考Microchip公司的AN799 Matching MOSFET Drivers to MOSFETs;讲述得很详细,所以不打算多写了;5,MOS管应用电路MOS管最显着的特性是开关特性好,所以被广泛应用在需要电子开关的电路中,常见的如开关电源和马达驱动,也有照明调光;现在的MOS驱动,有几个特别的需求,1,低压应用当使用5V电源,这时候如果使用传统的图腾柱结构,由于三极管的be有左右的压降,导致实际最终加在gate上的电压只有;这时候,我们选用标称gate电压的MOS管就存在一定的风险;同样的问题也发生在使用3V或者其他低压电源的场合;2,宽电压应用输入电压并不是一个固定值,它会随着时间或者其他因素而变动;这个变动导致PWM电路提供给MOS管的驱动电压是不稳定的;为了让MOS管在高gate电压下安全,很多MOS管内置了稳压管强行限制gate电压的幅值;在这种情况下,当提供的驱动电压超过稳压管的电压,就会引起较大的静态功耗;同时,如果简单的用电阻分压的原理降低gate电压,就会出现输入电压比较高的时候,MOS管工作良好,而输入电压降低的时候gate电压不足,引起导通不够彻底,从而增加功耗;3,双电压应用在一些控制电路中,逻辑部分使用典型的5V或者数字电压,而功率部分使用12V甚至更高的电压;两个电压采用共地方式连接;这就提出一个要求,需要使用一个电路,让低压侧能够有效的控制高压侧的MOS管,同时高压侧的MOS管也同样会面对1和2中提到的问题;在这三种情况下,图腾柱结构无法满足输出要求,而很多现成的MOS驱动IC,似乎也没有包含gate电压限制的结构;于是我设计了一个相对通用的电路来满足这三种需求;电路图如下:图1 用于NMOS的驱动电路图2 用于PMOS的驱动电路这里我只针对NMOS驱动电路做一个简单分析:Vl和Vh分别是低端和高端的电源,两个电压可以是相同的,但是Vl不应该超过Vh;Q1和Q2组成了一个反置的图腾柱,用来实现隔离,同时确保两只驱动管Q3和Q4不会同时导通;R2和R3提供了aPWM电压基准,通过改变这个基准,可以让电路工作在PWM信号波形比较陡直的位置;Q3和Q4用来提供驱动电流,由于导通的时候,Q3和Q4相对Vh和GND最低都只有一个Vce的压降,这个压降通常只有左右,大大低于的Vce;R5和R6是反馈电阻,用于对gate电压进行采样,采样后的电压通过Q5对Q1和Q2的基极产生一个强烈的负反馈,从而把gate电压限制在一个有限的数值;这个数值可以通过R5和R6来调节;最后,R1提供了对Q3和Q4的基极电流限制,R4提供了对MOS管的gate电流限制,也就是Q3和Q4的Ice的限制;必要的时候可以在R4上面并联加速电容;这个电路提供了如下的特性:1,用低端电压和PWM驱动高端MOS管;2,用小幅度的PWM信号驱动高gate电压需求的MOS管;3,gate电压的峰值限制4,输入和输出的电流限制5,通过使用合适的电阻,可以达到很低的功耗;6,PWM信号反相;NMOS并不需要这个特性,可以通过前置一个反相器来解决;在设计便携式设备和无线产品时,提高产品性能、延长电池工作时间是设计人员需要面对的两个问题;DC-DC转换器具有效率高、输出电流大、静态电流小等优点,非常适用于为便携式设备供电;目前DC-DC转换器设计技术发展主要趋势有:1高频化技术:随着开关频率的提高,开关变换器的体积也随之减小,功率密度也得到大幅提升,动态响应得到改善;小功率DC-DC转换器的开关频率将上升到兆赫级;2低输出电压技术:随着半导体制造技术的不断发展,微处理器和便携式电子设备的工作电压越来越低,这就要求未来的DC-DC变换器能够提供低输出电压以适应微处理器和便携式电子设备的要求;这些技术的发展对电源芯片电路的设计提出了更高的要求;首先,随着开关频率的不断提高,对于开关元件的性能提出了很高的要求,同时必须具有相应的开关元件驱动电路以保证开关元件在高达兆赫级的开关频率下正常工作;其次,对于电池供电的便携式电子设备来说,电路的工作电压低以锂电池为例,工作电压~,因此,电源芯片的工作电压较低;MOS管具有很低的导通电阻,消耗能量较低,在目前流行的高效DC-DC芯片中多采用MOS管作为功率开关;但是由于MOS管的寄生电容大,一般情况下NMOS开关管的栅极电容高达几十皮法;这对于设计高工作频率DC-DC转换器开关管驱动电路的设计提出了更高的要求;在低电压ULSI设计中有多种CMOS、BiCMOS采用自举升压结构的逻辑电路和作为大容性负载的驱动电路;这些电路能够在低于1V电压供电条件下正常工作,并且能够在负载电容1~2pF的条件下工作频率能够达到几十兆甚至上百兆赫兹;本文正是采用了自举升压电路,设计了一种具有大负载电容驱动能力的,适合于低电压、高开关频率升压型DC-DC转换器的驱动电路;电路基于Samsung AHP615 BiCMOS工艺设计并经过Hspice仿真验证,在供电电压,负载电容为60pF时,工作频率能够达到5MHz以上;自举升压电路自举升压电路的原理图如图1所示;所谓的自举升压原理就是,在输入端IN 输入一个方波信号,利用电容Cboot将A点电压抬升至高于VDD的电平,这样就可以在B端输出一个与输入信号反相,且高电平高于VDD的方波信号;具体工作原理如下;当VIN为高电平时,NMOS管N1导通,PMOS管P1截止,C点电位为低电平;同时N2导通,P2的栅极电位为低电平,则P2导通;这就使得此时A点电位约为VDD,电容Cboot两端电压UC≈VDD;由于N3导通,P4截止,所以B点的电位为低电平;这段时间称为预充电周期;当VIN变为低电平时,NMOS管N1截止,PMOS管P1导通,C点电位为高电平,约为VDD;同时N2、N3截止,P3导通;这使得P2的栅极电位升高,P2截止;此时A 点电位等于C点电位加上电容Cboot两端电压,约为2VDD;而且P4导通,因此B点输出高电平,且高于VDD;这段时间称为自举升压周期;实际上,B点电位与负载电容和电容Cboot的大小有关,可以根据设计需要调整;具体关系将在介绍电路具体设计时详细讨论;在图2中给出了输入端IN电位与A、B两点电位关系的示意图;驱动电路结构图3中给出了驱动电路的电路图;驱动电路采用Totem输出结构设计,上拉驱动管为NMOS管N4、晶体管Q1和PMOS管P5;下拉驱动管为NMOS管N5;图中CL为负载电容,Cpar为B点的寄生电容;虚线框内的电路为自举升压电路;本驱动电路的设计思想是,利用自举升压结构将上拉驱动管N4的栅极B点电位抬升,使得UB>VDD+VTH ,则NMOS管N4工作在线性区,使得VDSN4 大大减小,最终可以实现驱动输出高电平达到VDD;而在输出低电平时,下拉驱动管本身就工作在线性区,可以保证输出低电平位GND;因此无需增加自举电路也能达到设计要求;考虑到此驱动电路应用于升压型DC-DC转换器的开关管驱动,负载电容CL很大,一般能达到几十皮法,还需要进一步增加输出电流能力,因此增加了晶体管Q1作为上拉驱动管;这样在输入端由高电平变为低电平时,Q1导通,由N4、Q1同时提供电流,OUT端电位迅速上升,当OUT端电位上升到VDD-VBE时,Q1截止,N4继续提供电流对负载电容充电,直到OUT端电压达到VDD;在OUT端为高电平期间,A点电位会由于电容Cboot 上的电荷泄漏等原因而下降;这会使得B点电位下降,N4的导通性下降;同时由于同样的原因,OUT端电位也会有所下降,使输出高电平不能保持在VDD;为了防止这种现象的出现,又增加了PMOS管P5作为上拉驱动管,用来补充OUT端CL的泄漏电荷,维持OUT端在整个导通周期内为高电平;驱动电路的传输特性瞬态响应在图4中给出;其中a为上升沿瞬态响应,b为下降沿瞬态响应;从图4中可以看出,驱动电路上升沿明显分为了三个部分,分别对应三个上拉驱动管起主导作用的时期;1阶段为Q1、N4共同作用,输出电压迅速抬升,2阶段为N4起主导作,使输出电平达到VDD,3阶段为P5起主导作用,维持输出高电平为VDD;而且还可以缩短上升时间,下降时间满足工作频率在兆赫兹级以上的要求;需要注意的问题及仿真结果电容Cboot的大小的确定Cboot的最小值可以按照以下方法确定;在预充电周期内,电容Cboot 上的电荷为VDDCboot ;在A点的寄生电容计为CA上的电荷为VDDCA;因此在预充电周期内,A点的总电荷为Q_{A1}=V_{DD}C_{boot}+V_{DD}C_{A} 1B点电位为GND,因此在B点的寄生电容Cpar上的电荷为0;在自举升压周期,为了使OUT端电压达到VDD,B点电位最低为VB=VDD+Vthn;因此在B点的寄生电容Cpar上的电荷为Q_{B}=V_{DD}+V_{thn}Cpar 2忽略MOS管P4源漏两端压降,此时Cboot上的电荷为VthnCboot ,A点寄生电容CA的电荷为VDD+VthnCA;A点的总电荷为QA2=V_{thn}C_{BOOT}+V_{DD}+V_{thn}C_{A} 3同时根据电荷守恒又有Q_{B}=Q_{A}-Q_{A2} 4综合式1~4可得C_{boot}=\frac{V_{DD}+V_{thn}}{v_{DD}-v_{thn}}Cpar+\frac{v_{thn}}{v_{DD}-v_{ thn}}C_{A}=\frac{V_{B}}{v_{DD}-v_{thn}}Cpar+\frac{V_{thn}}{v_{DD}-v_{thn}}C_{ A} 5从式5中可以看出,Cboot随输入电压变小而变大,并且随B点电压VB变大而变大;而B点电压直接影响N4的导通电阻,也就影响驱动电路的上升时间;因此在实际设计时,Cboot的取值要大于式5的计算结果,这样可以提高B点电压,降低N4导通电阻,减小驱动电路的上升时间;P2、P4的尺寸问题将公式5重新整理后得:V_{B}={V_{DD}-V_{thn}\frac{C_{boot}}{Cpar}-V_{thn}\frac{C_{A}}{Cpar} 6 从式6中可以看出在自举升压周期内, A、B两点的寄生电容使得B点电位降低;在实际设计时为了得到合适的B点电位,除了增加Cboot大小外,要尽量减小A、B两点的寄生电容; 在设计时,预充电PMOS管P2的尺寸尽可能的取小,以减小寄生电容CA;而对于B点的寄生电容Cpar来说,主要是上拉驱动管N4的栅极寄生电容,MOS管P4、N3的源漏极寄生电容只占一小部分;我们在前面的分析中忽略了P4的源漏电压,因此设计时就要尽量的加大P4的宽长比,使其在自举升压周期内的源漏电压很小可以忽略;但是P4的尺寸以不能太大,要保证P4的源极寄生电容远远小于上拉驱动管N4的栅极寄生电容;阱电位问题如图3所示,PMOS器件P2、P3、P4的N-well连接到了自举升压节点A上;这样做的目的是,在自举升压周期内,防止他们的源/漏--阱结导通;而且这还可以防止在源/漏--阱正偏时产生由寄生SRC引起的闩锁现象;上拉驱动管N4的阱偏置电位要接到它的源极,最好不要直接接地;这样做的目的是消除衬底偏置效应对N4的影响;Hspice仿真验证结果驱动电路基于Samsung AHP615 BiCMOS工艺设计并经过Hspice仿真验证;在表1中给出了电路在不同工作电压、不同负载条件下的上升时间tr和下降时间tf 的仿真结果;在图5中给了电路工作在输入电压、工作频率为5MHz、负载电容60pF条件下的输出波形;结合表1和图5可以看出,此驱动电路能够在工作电压为,工作频率为5MHz,并且负载电容高达60pF的条件下正常工作;它可以应用于低电压、高工作频率的DC-DC转换器中作为开关管的驱动电路;结论本文采用自举升压电路,设计了一种BiCMOS Totem结构的驱动电路;该电路基于Samsung AHP615 BiCMOS工艺设计,可在电压供电条件下正常工作,而且在负载电容为60pF的条件下,工作频率可达5MHz以上;。

mosfet电压隔离驱动方案

mosfet电压隔离驱动方案MOSFET电压隔离驱动方案随着现代电子技术的快速发展,电路的稳定性和可靠性要求也越来越高。

在一些特殊的应用场景中,如高频电路、高压电路、噪声环境下的电路等,需要对电路进行电压隔离来提高系统的稳定性和安全性。

MOSFET电压隔离驱动方案因其高速、低功耗和可靠性等优势,成为了一种常用的解决方案。

MOSFET(金属氧化物半导体场效应晶体管)是一种常见的半导体器件,具有高速开关和低功耗的特点。

通过控制MOSFET的栅极电压,可以实现对电路的开关控制。

而MOSFET电压隔离驱动方案则是利用MOSFET的特性来实现电路之间的电压隔离。

在MOSFET电压隔离驱动方案中,一般会使用光耦来实现电路间的隔离。

光耦是一种能够将电路间的信号通过光信号进行转换的器件。

它由发光二极管(LED)和光敏二极管(光电晶体管)组成。

当输入信号施加在发光二极管上时,发光二极管会发出光信号,光信号经过隔离区域后,被光敏二极管接收并转换为与输入信号相同的电信号。

通过光耦将输入信号与MOSFET的栅极连接起来,当输入信号施加在光耦上时,光敏二极管会产生相应的电信号,通过MOSFET的栅极电压来控制MOSFET的导通和关断。

由于光耦实现了输入信号和MOSFET之间的电气隔离,可以有效地提高系统的稳定性和安全性。

MOSFET电压隔离驱动方案具有以下几个优势:1. 高速开关:MOSFET具有快速的开关速度,可以实现高频电路的要求。

通过光耦隔离驱动MOSFET,可以实现输入信号的快速响应,提高系统的响应速度。

2. 低功耗:MOSFET的工作电流较小,具有较低的功耗。

通过光耦隔离驱动MOSFET,可以进一步降低功耗,提高系统的能效。

3. 可靠性高:MOSFET具有较高的可靠性,长时间工作不易出现故障。

通过光耦隔离驱动MOSFET,可以避免外部电源的电压干扰和噪声对系统的影响,提高系统的稳定性和可靠性。

4. 成本低:MOSFET电压隔离驱动方案相对于其他电压隔离方案来说,成本较低。

双mos管正激隔离驱动电路

双mos管正激隔离驱动电路双MOS管正激隔离驱动电路是一种常用的隔离型电源拓扑,它采用两个MOSFET作为开关器件,通常用于高效率、高功率密度的应用中。

这种电路的工作原理是通过第一个MOSFET(称为高侧MOSFET)来控制输入电压与输出电压之间的隔离,而第二个MOSFET(称为低侧MOSFET)则用来控制负载的供电。

以下是一个基本的双MOS管正激隔离驱动电路的原理描述:1. 输入侧(高侧):输入电压通过一个整流器(如二极管)后,为高侧MOSFET提供驱动电压。

高侧MOSFET的栅极由一个驱动电路控制,该驱动电路可以产生足够快的开关信号,以控制MOSFET的导通和截止。

2. 隔离变压器:隔离变压器的高压侧连接到高侧MOSFET的源极,低压侧则连接到低侧MOSFET的栅极。

变压器的作用是实现输入与输出之间的电气隔离,同时提升或降低输出电压,以适应不同的负载需求。

3. 输出侧(低侧):低侧MOSFET的源极连接到负载,而栅极则由隔离变压器的次级绕组提供驱动信号。

当高侧MOSFET导通时,隔离变压器的初级绕组与次级绕组之间的磁链增加,从而在次级绕组中产生电动势,驱动低侧MOSFET导通,为负载供电。

当高侧MOSFET截止时,低侧MOSFET也会随之截止,切断负载的供电。

4. 驱动电路:驱动电路通常包括脉冲宽度调制(PWM)控制器,它根据负载需求生成高侧和低侧MOSFET的开关信号。

驱动电路需要提供足够的电流来快速充放电MOSFET的栅极电容,以确保开关动作的快速完成。

5. 钳位电路:为保护MOSFET不受到输入电压或负载电压的过高影响,通常会设计钳位电路,以限制MOSFET的源漏电压。

这种电路的优点包括高效率、低电磁干扰(EMI)、良好的隔离性能等。

然而,设计时需要注意的问题包括MOSFET的选择、驱动电路的设计、变压器的设计、开关频率的选择、EMI的抑制等。

为了确保电路的稳定性和可靠性,还需要考虑电路的温升控制、过流保护、过压保护等保护措施。

mosfet的10种驱动电路图

MOSFET的10种驱动电路图1. PWM芯片直接驱动MOSFET2. 开通和关断速度分开控制的MOSFET驱动电路3. 带图腾柱扩流的MOSFET驱动电路4. 使用TL494,SG3524内部的输出电路采用的单端集电极和射极开路的驱动电路5. 使用光耦隔离的驱动电路(原原理图有误,Q1\Q2位置对调)6. 使用光耦隔离的带负压关断驱动电路:(原原理图有误,Q1\Q2位置对调)7. 采用专用驱动光耦驱动的隔离驱动电路:8. 电动车控制器驱动电路9. P管驱动电路:10. 多管并联驱动电路:下面是赠送的几篇网络励志文章需要的便宜可以好好阅读下,不需要的朋友可以下载后编辑删除!!谢谢!!出路出路,走出去才有路“出路出路,走出去才有路。

”这是我妈常说的一句话,每当我面临困难及有畏难情绪的时候,我妈就用这句话来鼓励我。

一定有很多人想说:“这还在北京混个什么劲儿啊!”但他每天都乐呵呵的,就算把快递送错了也乐呵呵的。

某天,他突然递给我一堆其他公司的快递单跟我说:“我开了家快递公司,你看得上我就用我家的吧。

”我有点惊愕,有一种“哎呦喂,张老板好,今天还能三蹦子顺我吗”的感慨。

之后我却很少见他来,我以为是他孩子出生了休假去了。

再然后,我就只能见到单子见不到他了。

某天,我问起他们公司的快递员,小伙子说老板去上海了,在上海开了家新公司。

我很杞人忧天地问他:“那上海的市场不激烈吗?新快递怎么驻足啊!”小伙子嘿嘿一笑说:“我们老板肯定有办法呗!他都过去好几个月了,据说干得很不错呢!”“那老婆孩子呢?孩子不是刚生还很小吗?”“过去了,一起去上海了!”那个瞬间,我回头看了一眼办公室里坐着的各种愁眉苦脸的同事,并且举起手机黑屏幕照了一下我自己的脸,一股“人生已经如此的艰难,有些事情就不要拆穿”的气息冉冉升起。

并不是说都跳槽出去开公司才厉害,在公司瞪着眼睛看屏幕就是没发展,我是想说,只有勇气才能让自己作出改变。

我们每个人都觉得自己越活越内向,越来越自闭,越长大越孤单,以至于滋生了“换个新环境,我这种性格估计也不会跟其他人相处融洽,所以还是待着忍忍凑合过算了”的思想感情。

电力mosfet驱动电路特点

电力mosfet驱动电路特点电力MOSFET驱动电路是一种用于控制高功率MOSFET开关的电路,具有以下特点:1. 高速开关能力: 电力MOSFET驱动电路可以实现对MOSFET的快速开关,使其能够在毫秒甚至微秒的时间内完成快速开关动作。

这种高速开关能力使得电力MOSFET驱动电路在高频率开关电源、电机驱动等应用中得到广泛应用。

2. 低功耗: 电力MOSFET驱动电路采用了先进的功耗优化设计,能够在保证高性能的同时,尽量减小功耗。

这有助于提高系统的能效,减少能源消耗。

3. 高电压驱动能力: 电力MOSFET驱动电路能够提供足够的电流和电压来驱动MOSFET的栅极,保证其能够迅速切换。

这种高电压驱动能力使得电力MOSFET驱动电路适用于高电压应用场景,如电力电子装置。

4. 低输入电流: 电力MOSFET驱动电路的输入电流较低,可以通过外部逻辑电平或微控制器来控制。

这使得电力MOSFET驱动电路具有灵活性和可编程性,可以方便地集成到各种控制系统中。

5. 具有过温保护和短路保护功能: 电力MOSFET驱动电路通常具有过温保护和短路保护功能,当MOSFET温度过高或输出短路时,能够及时切断电源,以保护MOSFET和整个系统的安全运行。

6. 可靠性高: 电力MOSFET驱动电路采用了先进的保护电路和稳定的控制算法,能够有效地避免MOSFET的过压、过流等问题,提高系统的可靠性和稳定性。

7. 适应性强: 电力MOSFET驱动电路能够适应不同的电力MOSFET 器件,不同的工作条件和负载要求。

同时,电力MOSFET驱动电路还可以根据需求进行定制设计,以满足不同应用场景的需求。

总的来说,电力MOSFET驱动电路具有高速开关能力、低功耗、高电压驱动能力、低输入电流、过温保护和短路保护功能、高可靠性和适应性强等特点。

这些特点使得电力MOSFET驱动电路在各种高功率电子设备和系统中发挥着重要作用,提高了系统的性能和可靠性。

两种常见的MOSFET驱动电路设计

两种常见的MOSFET驱动电路设计常见的MOSFET驱动电路设计有两种:高侧驱动电路和低侧驱动电路。

高侧驱动电路是将MOSFET的源极连接到地,而负载连接到漏极。

这种电路设计的优点是可以在高侧实现PWM调光控制,因为调光信号是接在负载一侧,而不会影响到驱动信号。

高侧驱动电路的实现需要解决负载和电源之间的电位差问题。

一种常见的设计是使用一个电隔离器件,如光耦合器,它可以将输入信号隔离开,并提供一个离地的电位供电MOSFET。

另一种方法是使用一个NPN晶体管来驱动MOSFET,该晶体管的基极通过一个电阻连接到正电源,而发射极连接到MOSFET的源极,并且信号输入到晶体管的基极。

低侧驱动电路是将MOSFET的漏极连接到地,而负载连接到源极。

这种电路设计的优点是相对简单,不需要解决电位差的问题。

低侧驱动电路中最常见的设计时使用一个NPN晶体管将MOSFET的源极与地连接起来。

信号输入到NPN晶体管的基极,晶体管的发射极与MOSFET的源极相连。

当输入信号为高电平时,晶体管导通,MOSFET的源极与地之间产生一个低电平,从而导通MOSFET。

当输入信号为低电平时,晶体管截止,MOSFET被断开。

在设计这两种驱动电路时,需要考虑一些关键参数和特性,以确保MOSFET能够正常工作。

其中一个关键参数是驱动电压的选取。

驱动电压应该足够高以确保MOSFET能够完全导通,同时应该在MOSFET的最大耐压范围内。

另一个关键参数是驱动电流的选取。

驱动电流应该足够大以确保MOSFET能够迅速地从导通到截止的状态切换。

此外,还需要考虑电源的稳定性和电流能力。

为了防止驱动电路的电压波动对MOSFET的工作产生不利影响,应当使用稳定的电源。

此外,驱动电路还应能够提供足够的电流以确保MOSFET迅速地从导通到截止的状态切换。

综上所述,高侧驱动电路和低侧驱动电路是常见的MOSFET驱动电路设计。

通过正确选择驱动电压和驱动电流,并考虑电源稳定性和电流能力,可以确保MOSFET能够正常工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电焊机 Electric Welding Machine

Vol.37 No.5 May 2007

MOSFET 隔离型高速驱动电路

纪圣儒, 朱志明, 周雪珍, 王琳化

(清华大学 机械工程系, 北京 100084)

摘要: 结合以 MOSFET 为主要功率开关器件, 应用于电弧超声焊接的高频脉冲激励系统的研发, 在对

电

子

荷提供低阻的放电回路, 同时晶体管工作于射极跟

元

随方式, 不会出现饱和, 很多隔离型驱动电路也借

器

鉴了这种方式。隔离型驱动主要包括光耦隔离驱动

件

和变压器隔离驱动两种形式。

的

选

2 脉冲变压器隔离驱动

择 与

脉 冲 变 压 器 隔 离 是 MOSFET 和 IGBT 等 全 控

应

型器件驱动电路常用的一种隔离形式, 由于它具有

专题讨论

纪圣儒等: MOSFET 隔离型高速驱动电路

第5期

图 1 用于电弧超声焊接的高频脉冲激励系统 Fig.1 High-fr equency pulse stimulating system applied in ar c excited ultr asonic welding

图 2 MOSFET 的开通和关断过程 Fig.2 Tur n on and tur n off pr ocesses of MOSFET 的开通过程为例, 它可分为如下四个阶段[1]。

间足够短; 关断时, 能为栅极电荷提供低阻放电回

路, 从而提高 MOSFET 的关断速度[2]。

(2)由于栅极驱动电压是相对于 MOSFET 管的

源极而言的, 而在桥式电路中, 同一桥臂的上管和

下管的源极电位是不同的, 即不同 MOSFET 的驱动

信号基准点是不同的。同时, 为了避免功率变换电路

对控制电路产生干扰, 驱动电路必须实现功率变换

根据上述对 MOSFET 开通和关断过程的分析, 在用于电弧超声焊接的高频脉冲激励系统中, 功率

MOSFET 的驱动电路应满足如下要求:

(1)具有足够快的开关ຫໍສະໝຸດ 度, 最大工作频率可达100 kHz。为此, 驱动脉冲应具有足够陡的上升和下降

速度, 即驱动脉冲本身延迟要小。开通时, 能够提供足

够大的瞬时峰值电流, 使得开通延迟和密勒平台时

论

——

隔离驱动型两种。直接驱动包括 TTL 驱 动 、CMOS

驱动和推挽输出驱动等[3]。其中, 推挽输出驱动(又称

焊

为 图 腾 柱 驱 动 )是 直 接 驱 动 中 最 常 用 的 一 种 驱 动 方

机

式, 它采用一对 PNP 和 NPN 晶体管搭建而成, 可以

中

实现开通时输出较大的驱动电流, 关断时为栅极电

MOSFET 开通和关断过程进行分析的基础上, 给出了 MOSFET 隔离型高速驱动电路所必需满足的条件。

详细讨论了最大工作频率可达 100 kHz、实现电气隔离、具有较强驱动能力和抗干扰能力的 MOSFET 驱

动电路的设计与实现过程, 实验结果证明了所设计驱动电路的可行性。所讨论的 MOSFET 驱动电路对

型和 N 型 MOSFET 搭建而成, 两路互补的控制信号

分别控制两个桥臂 MOSFET 的开关状态。当其中一

路控制信号为高电平时, 全桥电路的某一对角开关

管导通, 将某一极性脉冲方波电压施加在隔离变压

器的一次侧, 由于两个二次侧输出绕组的极性相反,

因此得到两路极性相反的驱动信号; 当两路控制信

号均为低电平时(死区时间), 两个 P 型管同时导通,

电路与控制电路的电气隔离。

(3)为 防 止 MOSFET 误 导 通 , 在 MOSFET 关 断

时, 应提供一定的负偏电压, 以提高其抗干扰能力。

(4)为 保 证 MOSFET 的 可 靠 开 通 , 应 使 驱 动 电

专

题

压高于 MOSFET 的开起电压, 通常取 10~15 V。

讨

常见的 MOSFET 驱动电路可分为直接驱动型和

(1)开通延迟阶段(t0~t1)。UGS 从零上升到门限电压 Uth, 而 UDS 和 ID 保持不变。

(2)逐渐开通阶段(t1~t2)。t1 时刻 UGS 达到门限电压 Uth, ID 开始缓慢增加, 至 t2 时刻, ID 达到最大值。在该阶 段, UDS 保持不变。

(3)密勒平台产生阶段(t2~t3)。t2 时刻开始, UDS 开 始下降, 反向传输电容的密勒效应使得 UGS 出现了 一个平台, t3 时刻, UDS 降至 MOSFET 导通压降。

子

in this paper have also referential values for designing driver circuits of other voltage-controlled switches such as IGBT.

元

Key words: MOSFET driver circuit; pulse-transformer; high-speed optocoupler

从事材料加工领域的功率电子设备研究工作。

能够对其寄生电容网络进行快速充/放电, 特别是在 高开关工作频率的应用中。图 2 所示为 MOSFET 在开 通和关断过程中的漏源电压 UDS、漏极电流 ID、栅源 电压 UGS 和栅极充电电荷 Qg 的变化曲线。以 MOSFET

· 6 · Electric Welding M achine

题

JI Sheng-ru, ZHU Zhi-ming, ZHOU Xue-zhen, WANG Lin-hua

讨

论

(Department of Mechanical Engineering, Tsinghua University, Beijing 100084, China)

——

Abstract : Combining with the research and development of high frequency pulse stimulating system applied in arc excited ultrasonic

电

一定变化), 由于脉冲变压器的 复 位 情 况 发 生 了 改

子

变, 从而影响了输出驱动信号的上升沿和下降沿,

元

将无法很好地满足高速驱动的要求, 甚至可能出现

器

件

变压器磁心偏磁现象, 使得驱动输出信号紊乱。因

的

此, 这种采用 RCD 复位的正激变换驱动电路不适

选

用于控制信号频率和占空比变化较大的场合, 但可

隔离变压器一次侧被短路, 两路输出驱动信号均为

· 8 · Electric Welding M achine

用

电路结构简单、不需要提供隔离电源、成本较低, 对

脉冲信号无传输延迟等优点, 能够满足驱动电路电

气隔离、快速性、较强驱动能力的要求, 因此研发过

程中首先考虑采用这种隔离驱动方式, 包括正激变

换和全桥变换两种电路拓扑形式。其中, 正激变换拓

扑单独驱动每个开关管, 而全桥变换拓扑适用于桥

式电路同一桥臂两个互补开关管的驱动。

率为 100 kHz, 因此选用 MOSFET 作为主功率开关

得到广泛应用。

器件, 并采用移相 PWM 控制方式实现零电压开关,

本研究结合以 MOSFET 为主要功率开关器件、 以减小高频开关损耗。

应用于电弧超声焊接的高频脉冲激励系统的研发,

MOSFET 属于电压控制型器件, 其输入阻抗高,

提出了一种工作频率可达 100 kHz 且具有较强负载

所需静态驱动功率很小。然而, 由于各极之间存在着

驱动能力和抗干扰能力的 MOSFET 隔离型驱动电路。 寄生电容, 在其开通和关断过程中, 驱动电路必须

收稿日期: 2007- 03- 07 基金项目: 国家自然科学基金资助项目(50375080) 作者简介: 纪圣儒(1982—), 男, 福建尤溪人, 在读硕士, 主要

焊

welding, in which the MOSFET being used, the turn-on and turn-off processes of MOSFET are presented, and then its requirements of

机

electrical-isolated high-speed driver circuit are introduced.After that, the design and implementation process of MOSFET driver circuit,

中

which meets the requirements including operation frequency up to 100 kHz, electrical-isolated, strong driving capability and anti-

电

disturbance capability, is discussed in detail.Experimental results show the feasibility of the driver circuit.The driver circuits introduced

(4)完全导通阶段(t3~t4)。UGS 继续上升至最终的驱 动电压, UGS 的增 大 使 得 MOSFET 导 通 电 阻 RDS(on) 减小, 但当 UGS 超过 10 V 后, 对 RDS(on)的影响很小。

MOSFET 的关断过程与开通过程正好相反, 也 可 分 为 关 断 延 迟 (t0~t1)、密 勒 平 台 产 生 (t1~t2)、逐 渐 关 断(t2~t3)和完全关断(t3~t4)四个阶段。