单片机第五章1单片机的中断系统

单片机-第五章 单片机中断系统

(1)CPU正在执行一个同级或高优先级的中断服务程序; (2)正在执行的指令尚未执行完; (3)正在执行中断返回指令RETI或者对寄存器IE、IP进 行读/写的指令。 CPU在执行完上述指令之后,要再执行一条指令,才 能响应中断请求。

二、中断响应过程 从中断请求发生直到被响应,准备去执行中断服务程 序,此过程即中断响应过程。中断响应过程一般包括如下几 个阶段: 1、中断采样并置位 中断采样过程:CPU在每个机器周期S5P2期间顺序对 中断源采样、置中断标志。 2、查询标志 在中断采样后的下一个周期的S6按优先级顺序查 询中断标志。

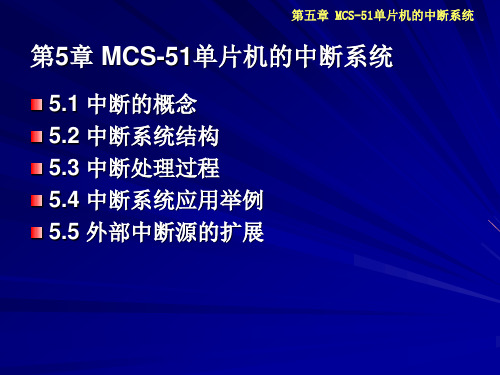

第5章 MCS-51单片机中断系统

5.1.1中断的概念

单片机系统中,CPU和外部设备之间不断进行信息的传 输。通常CPU和外设之间的信息传送方式有以下几种: 程序控制方式 中断方式 直接存储器存取(DMA)方式

1、 程序控制方式 可以分为以下两种方式。 (1)无条件传送方式 外设始终处于就绪状态,CPU不必查询外设的状 态,直接进行信息传输,称为无条件传送方式。 此种信息传送方式只适用于简单的外设。如开 关和数码段显示器等。

三、中断响应的时间

一般来说,中断的响应时间最短为3个机器周期,最长 为8个机器周期。 一般中断请求标志位查询占1个机器周期。而机器周期 又恰好是指令的最后一个机器周期。执行此指令后,CPU 将响应中断,产生硬件长调用指令。 长调用LCALL指令需要2个机器周期。这样,中断响应 时间为3个机器周期。

是不可寻址的

在同级的几个中断源中同时发生请求时, 内部对同级的各中断源的优先级别有一个规 定的查询顺序: 自然优先级

外部中断请求 INT0 最高 定时/计数器 T0 外部中断请求 INT1 定时/计数器 T1 串行口 UART 最低 定时/计数器 T2

MCS-51系列单片机的中断系统

大连理工大学出版社

第5章 中断

当断不断必受其乱

第5章 中断系统

5.1 概述 MCS-51系列单片机的中断系统 5.2 MCS-51系列单片机的中断系统 5.3 中断程序设计方法

第5 章

中断系统

中断控制是单片机最重要的技术之一, 实时控制及人机交互等应用都是通过中 断实现的。 本章主要介绍中断的基本概念、MCS-51 系列单片机单片机的中断机制及其简单 应用。

5.2.2中断控制 5.2.2中断控制

1.中断允许 MCS-51系列单片机中断系统通过中断允许控制 寄存器IE实现开中断和关中断的功能。 (1)IE寄存器 IE寄存器由一个中断允许总控制位和各中断源 的中断允许控制位构成,从而进行两级中断允 许控制。IE寄存器的各位定义如下:

5.2.2中断控制 IE寄存器

5.2.2中断控制 IE寄存器

EX1(IE.2)——外中断1的中断允许控 制位。中断总允许时,EX1=0,禁止外中 断1中断;EX1=1,允许外中断1中断。 ET1(IE.3)——定时器T1的中断允许控 制位。中断总允许时,EX1=0,禁止T1中 断;ET1=1,允许T1中断。

5.2.2中断控制 5.2.2中断控制 IE寄存器

5.2.1中断源和中断标志

当MCS-51系列单片机的外中断源以脉冲方式触 发时,负脉冲有效。CPU在一个机器周期采样到 INT0(或者 INT1 )引脚上为高电平,在接下 来的一个机器周期采样到INT0(或者INT1)引 脚上是低电平,即出现了下降沿的跳变(负脉 冲)时,就认为是外中断0(或者外中断1)的 一个有效的中断请求信号。因为两次检测的间 隔时间为一个机器周期,负脉冲对应的高低电 平持续时间都应至少维持一个机器周期,从而 保证CPU能够检测到电平的跳变。

单片机原理及应用教程(C语言版)-第5章 MCS-51单片机的中断系统

5.2.5 中断允许控制

例5-1 假设允许INT0、INT1、T0、T1中断,试 设置IE的值。 (2)汇编语言程序 按字节操作: MOV IE,#8FH 按位操作: SETB EX0 ;允许外部中断0中断 SETB ET0 ;允许定时器/计数器0中断 SETB EX1 ;允许外部中断1中断 SETB ET1 ;开定时器/计数器1中断 SETB EA ;开总中断控制位

IP (B8H)

D7 —

D6 D5 D4 D3 D2 D1 D0 — PT2 PS PT1 PX1 PT0 PX0

PT2:定时器/计数器T2的中断优先级控制位 PT2设置1则T2为高优先级,PT2设置0则T2为 低优先级。 后面各位均是如此,设置1为高优先级,设置0 为低优先级,不再一一赘述。 PS:串行口的中断优先级控制位。 PT1:定时器/计数器1的中断优先级控制位。 PX1:外部中断1的中断优先级控制位。 PT0:定时器/计数器0的中断优先级控制位。 PX0:外部中断0的中断优先级控制位。

5.2.4 中断请求标志

4.定时器/计数器T2中断请求标志

T2CON D7 D6 D5 (C8H) TF2 EXF2 D4 D3 D2 D1 D0

EXF2:定时器/计数器2的外部触发中断请求标志 位。T2以自动重装或外部捕获方式定时、计数,当 T2EX(P1.1)引脚出现负跳变时,TF2由硬件置1, 向CPU请求中断,CPU响应中断后,EXF2不会被硬 件清0,需要在程序中以软件方式清0。

5.2.3 外中断触发方式

TCON格式如下:

D7 D6 D5 D4 D3 D2 D1 D0

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

IT0=1,外中断0为下降沿触发 CPU在每一个机器周期的S5P2期间对P3.2引 脚采样,若上一个机器周期检测为高电平,紧挨着 的下一个机器周期为低电平,则使IE0置1。 IT1:外中断1触发方式控制位。功能同IT0

第05章 MCS-51单片机的中断与定时(1-4)

2

1

TH0

;P1.0输出“0” ;P1.0输出“1”

5.2 MCS-51单片机的中断系统

五、外中断应用举例

1. 中断初始化程序

设置外中断源的触发方式 设置中断允许寄存器IE 设置中断优先级寄存器IP

2. 中断服务程序

保护现场 中断处理 恢复现场

23/65

5.2 MCS-51单片机的中断系统

【例5-3】 设外部中断0为下降沿触发方 式,高优先级,试编写中断初始化程序

5.2 MCS-51单片机的中断系统

【例5-4】 将单脉冲接到外中断0(INT0)引脚,利 用P1.0作为输出,经反相器接发光二极管。编写程 序,每按动一次按钮,产生一个外中断信号,使发 光二极管的状态发生变化,由亮变暗,或反之

P1.0 单脉冲 发生器 INT0

1

+5V

8031

26/65

5.2 MCS-51单片机的中断系统

串口:0023H

20/65

5.2 MCS-51单片机的中断系统

四、中断请求的撤除

1.定时/计数器中断请求标志TF0/TF1会自动撤除 2.串行口中断请求标志TI/RI要用指令撤除

CLR TI ;清TI标志位 CLR RI ;清RI标志位

3.负脉冲触发的外中断请求标志IE0/IE1会自动撤除 4.低电平触发的外中断请求信号需要外加电路撤除

下次课前请预习5.3节

30/65

5.3 51单片机的定时器/计数器

MCS-51单片机内部有两个16位定时/计数器 T0和T1,简称定时器0和定时器1

在特殊功能寄存器TMOD和TCON的控制下, 它们既可以设定成定时器使用,也可以设定 成计数器使用

定时/计数器有4种工作方式,具有中断功能, 可以完成定时、计数、脉冲输出等任务

第五章 MCS-51的中断系统

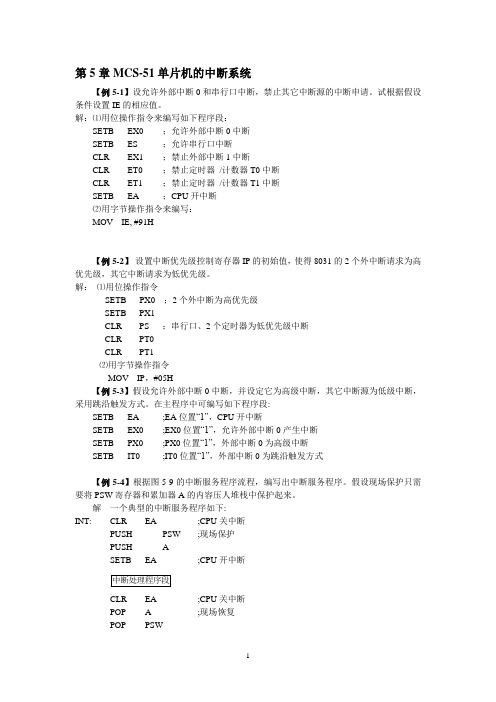

第5章MCS-51单片机的中断系统【例5-1】设允许外部中断0和串行口中断,禁止其它中断源的中断申请。

试根据假设条件设置IE的相应值。

解:⑴用位操作指令来编写如下程序段:SETB EX0 ;允许外部中断0中断SETB ES ;允许串行口中断CLR EX1 ;禁止外部中断1中断CLR ET0 ;禁止定时器/计数器T0中断CLR ET1 ;禁止定时器/计数器T1中断SETB EA ;CPU开中断⑵用字节操作指令来编写:MOV IE, #91H【例5-2】设置中断优先级控制寄存器IP的初始值,使得8031的2个外中断请求为高优先级,其它中断请求为低优先级。

解:⑴用位操作指令SETB PX0;2个外中断为高优先级SETB PX1CLR PS ;串行口、2个定时器为低优先级中断CLR PT0CLR PT1⑵用字节操作指令MOV IP,#05H【例5-3】假设允许外部中断0中断,并设定它为高级中断,其它中断源为低级中断,采用跳沿触发方式。

在主程序中可编写如下程序段:SETB E A ;EA位置“1”,CPU开中断SETB E X0 ;EX0位置“1”,允许外部中断0产生中断SETB P X0 ;PX0位置“1”,外部中断0为高级中断SETB I T0 ;IT0位置“1”,外部中断0为跳沿触发方式【例5-4】根据图5-9的中断服务程序流程,编写出中断服务程序。

假设现场保护只需要将PSW寄存器和累加器A的内容压人堆栈中保护起来。

解一个典型的中断服务程序如下:INT: CLR E A ;CPU关中断PUSH PSW ;现场保护PUSH ASETB E A ;CPU开中断中断处理程序段CLR E A ;CPU关中断POP A ;现场恢复POP PSWSETB E A ; CPU开中断RETI ;中断返回,恢复断点上述程序有几点需要说明的是:⑴本例的现场保护假设仅仅涉及到PSW和A的内容,如果还有其它的需要保护的内容,只需要在相应的位置再加几条PUSH和POP指令即可。

第5章 MCS-51单片机的中断系统

(2)实现实时处理

在实时控制中,现场的参数、信息是不断变化的。 有了中断功能,外界的这些变化量可随时向CPU 发出中断请求,CPU可以马上响应加以处理。

(3)故障处理

单片机运行过程中,出现一些故障时(如掉电、 存储出错、运算溢出等),有了中断功能,单片 机就能自行处理而不必停机。 外界的中断请求是随机的,单片机响应请求后要 转到中断服务程序,与调用子程序相类似,需要 注意对现场进行保护。

ORG 0100H

MAIN: …;

第五章 MCS-51单片机的中断系统

ORG 1000H INT1:PUSH ACC PUSH DPH PUSH DPL PUSH R0 PUSH R1 … POP R1 POP R0 POP DPL POP DPH POP ACC RETI

第五章 MCS-51单片机的中断系统

5.3 中断处理过程

中断响应

中断处理

中断返回

第五章 MCS-51单片机的中断系统

5.3.1 中断响应

1. CPU响应中断的基本条件 (1)有中断源提出中断请求; (2)中断没有被禁止; (3)没有正在响应的同级或更高优先级的中断; (4)当前的指令周期已经结束;(也就是说,中 断申请时,正在执行的这条指令完成后,才会响 应中断请求) (5)若当前指令为RETI或访问IE、IP指令, CPU在执行完当前指令后,要再执行一条指令才 会响应中断请求。

第五章 MCS-51单片机的中断系统

2.中断响应过程 (1)根据响应的中断源的中断优先级,使相应的优 先级状态触发器置1; (2)清除相应的中断请求标志位(串行口中断请求 标志RI和TI除外);

(3)把当前程序计数器PC的内容压入堆栈;

(4)把被响应的中断源所对应的中断服务程序的入 口地址送入PC,从而转入相应的中断服务程序。 CPU响应中断请求后,在中断返回(执行RETI)前, 中断请求必须被清除,即中断标志位=0,否则会再 一次引起中断响应。

第5章 中断系统

例7 如图,试编写程序实现以下功能:系统初始上电时,四 个发光二极管都熄灭,每当按下图中开关时,四个发光二极 管就能反映出与其对应的四个开关状态,开关闭合则对应二 极管亮,开关断开则对应二极管熄灭。

ORG 0000H AJMP MAIN ORG 0003H LJMP INT ORG 0030H MAIN:CLR IT0 SETB EX0 SETB EA SJMP $ ORG 0200H INT:MOV A,#0FFH MOV P1,A MOV A,P1 SWAP A MOV P1,A RETI

第 5章

MCS-51系列单片机 的中断系统

本章介绍的主要内容

★ 中断的基本概念 ★ 中断的系统结构 ★ 中断的响应 ★ 中断的应用编程

5.1 什么是中断

一、中断

中断是指CPU在执行程序的过程中,当某种 特殊状态出现时,CPU暂停现在正在执行的程序, 转向去对引起特殊状态的事件进行处理,处理完毕 后再返回继续执行原来程序的过程。 简单地说,中断就是在运行一段程序的过程中 由于某种原因临时插入了另一段程序的运行。

1. 开中断总控开关EA,置位中断源的中断允许位。 2. 对外部中断INT0、INT1,应选择中断触发方式。 3. 多个中断源中断,应设定中断优先级,预置IP。

例5 若系统需要响应定时/计数器0中断和由下降沿信号引起 的外部中断0中断,且若这两个中断源同时提出中断请求则先 响应内部中断,试编写程序,对相关寄存器进行初始化。

EA 中断 总控 允/ 禁

-

ET2

ES

ET1

EX1

ET0

EX0

不 用

T2 串行口 T1 INT1 T0 INT0 允/ 禁 允/ 禁 允/ 禁 允/ 禁 允/ 禁 允/ 禁

(单片机完整课件PPT)第五章

⑴ 对定时/计数器T0、T1中断,外中断边沿触发方式, CPU响应中断时就用硬件自动清除了相应的中断请求标 志。 ⑵对串行口中断,用户应在串行中断服务程序中用软件清 除TI或RI。

⑶对外中断电平触发方式,需要采取软硬结合的方法消除 后果。

只要 P1.0 端输出一个负脉冲就可以使 D 触发器置 “ 1” ,从而撤消了低电平的中断请求信号。所需 的负脉冲可增加如下两条指令得到: ORL P1,#01H ;P1.0为“1” ANL P1,#0FEH ;P1.0为“0”

T1

PX1 PT0 PX0

/INT1 T0 /INT0

相应位置1为高优先级;置0为低优先级。

优先级结构:

(1)低优先级中断可被高优先级中断所中断,反之不能; (2)任何一种中断(不管是高级还是低级),一旦得到

响应,与它同级的中断源不能再中断它。

(3)同级的中断源同时请求时,遵循辅助优先级顺序。

同级内的优先权 INT0 T0 INT1 T1 串行口 辅助优先级顺序 高

中断类型: (1)按中断源的不同分为: 硬件中断:由硬件产生请求使CPU响应中断。 软件中断:指可以通过相应的中断指令使CPU响应中断。 (2)按是否可屏蔽分为: 可屏蔽中断:指用户可以通过中断控制指令来控制CPU 是否响应中断源的中断请求。 不可屏蔽中断:指CPU不能屏蔽中断源的中断请求,必

ቤተ መጻሕፍቲ ባይዱ

须响应该中断请求。

2.中断申请标志

定时器控制寄存器TCON(88H)

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

ITX:选择 INTx中断触发方式。 ITX=1,选择 INT x 为下降沿触发方式。 ITX=0,选择

INT x 为低电平触发方式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2、 中断源(可由硬件或软件引起):引起中断的事件 MSC-51具有多个中断源,51子系列有5个中断源,2个外部中断,2个定时中断 和1个串行中断。

(A). 外中断:外部信号引起,共2个。 即: 外部中断“0”,中断请求信号由引脚INT0(P3.2)引入; 外部中断“1”,中断请求信号由引脚INT1(P3.3)引入。

(b)低优先级中断请求不能打断高优先级的中断服务;但高优先级中断请求可以打断低优 先级的中断服务,从而实现中断嵌套。

(c)如果1个中断请求已被响应,则同级的其它中断响应将被禁止。

中断优先级:当多个中断源请求中断服务,那么CPU响应这 些中断就有一个先后顺序,称之为中断优先级。

主

应 响

程 序

断

中

低

级

(2) EX0(EXl):外部中断允许控制位(INT0、INT1) EX0(EXl)=0 禁止外中断 EX0(EXl)=l 允许外中断

(3) ET0(ETl):定时/计数中断允许控制位(T0、T1) ET0(ETl)=0 禁止定时(或计数)中断 ET0(ETl)=1 允许定时(或计数)中断

(4) ES:串行中断允许控制位 ES=0 禁止串行中断 ES=1 允许串行中断

有效后,用户软件清零。

SJMP LOOP

b.中断方式时,作为中断请求标志位,为“1”时,自动转向中断

服

务程序,再由硬件自动清零。

(4)TR0、TR1: 下一章讲定时器/计数器时再讲

3. 串行口控制寄存器SCON(其中只有两位与中断有关)寄存器地址为98H

9FH

9EH

9DH

9CH

9BH

9AH

99H

98H

(2)IT0、IT1:外中断请求触发方式控制位。用户软件设置 ITX=0 低电平触发方式 ITX=1 负跳脉冲触发方式

至少2个机器周期 至少1个机器周期

(3)TF0、TF1:定时器溢出中断请求标志位,相应溢出标志位TFX由硬件置“1”。

两种使用方式:a.软件查询时,作为溢出标志位,查询

LOOP:JBC TF0,NEXT

2.定时器控制寄存器TCON 寄存器地址为88H

8FH TCON TF1

8EH 8DH 8CH 8BH 8AH 89H 88H

TR1

TF0

TR0

IE1

IT1

IE0

IT0

(1)IE0、IE1:外部中断请求标志。硬件自动设置 CPU采样到INTX端有效的中断请求后,IEX位由硬件自动置 “1”。在中断响 应期间(要转向中断服务程序时),由硬件自动清零。

中

断

继 续

返

回

程 序

回

应 响 断 中

高

级

中

断

返

程

序

执

行

Hale Waihona Puke RETIRETI主

程

序

•优先级高,则CPU先响应

主

应 响

程 序

断

中

高

级

(平级)中

断

继 续

返

回

程 序

回

应 响 断 中

低

级 (平级) 中

断

返

程

序

执

行

RETI

RETI

主

程

序

优先级低,则CPU不影响高级中断

中断嵌套流程图

•IT0=0 •INT0

•IT0=1 •T0

4. 中断优先级控制寄存器IP 用户软件设置寄存器地址为B8H

0BFH 0BEH 0BDH 0BCH 0BBH 0BAH 0B9H

IP

/

/

/

PS

PT1

PX1

PT0

0B8H PX0

PX0:外部中断0优先级设定位 PXl: 外部中断l优先级设定位 PT0:定时中断0优先级设定位 PTl: 定时中断l优先级设定位 PS : 串行中断优先级设定位

SCON SM0

SM1

SM2

REN

TB8

RB8

TI

RI

(1)TI:串行口发送中断标志位。当CPU将一个数据写入发送缓冲器时,就启动发送 当最后一个数据位发送完后,TI由硬件自动置位,并向CPU发中断申请。进行中 断服务程序时, TI要由软件清0。软件查询时, TI可作为状态位使用。

(2)RI:串行口接收中断标志位。当CPU接收数据时,当接收到最后一个数据位后, RI由硬件自动置位,并向CPU发中断申请。进行中断服务程序时, RI要由软件清0。 软件查询时, RI可作为状态位使用。

(B). 定时器/计数器中断:内部计数器计数溢出,溢出标志位TFX作为单片机接受中断 请求标志。 信号来源:内部(定时)和外部(计数)。

(C). 串行中断:串行数据传送(发送和接收)的需要而设置。

第二节 MCS-51单片机的中断系统

与中断控制有关的控制寄存器有四个:

IE------中断允许控制寄存器, TCON----定时控制寄存器, SCON----串行口控制寄存器。 IP------中断优先级控制寄存器,

•IT1=0 •INT1

•IT1=1

•T1

•TX •RX

•TCON •IE0

结论: • MCS—51通过中断允许控制寄存器对中断的允许实行两级控制。以EA位作为总控

制位,以各中断源的中断允许位作为分控制位。 • MCS—51单片机复位后(1E)=00H,因此中断系统处于禁止状态。 • 单片机在中断响应后不会自动关闭中断。因此在转中断服务程序后,应使用有关指

令禁止中断,即以软件方式关闭中断。

对应位置1,优先级为高;置0,优先级为低; 注意: (一)中断优先级控制原则(参看教材103页)

(二)控制逻辑:

(a)系统复位后,各位均为 0,或如果同级的多个中断请求同时出现,则按CPU查 询次序确定那个中断请求被响应。其查询次序为:外部中断0->定时中断0->外 部中断l->定时中断1->串行中断。

一、中断控制寄存器

通过设置相关寄存器,达到控制中断工作的目的

1. 中断允许控制寄存器IE 用户软件设置 寄存器地址为A8H

0AFH

0AEH 0ADH 0ACH 0ABH 0AAH 0A9H

IE

EA

/

/

ES

ET1

EX1

ET0

0A8H EX0

(1)EA:中断允许总控制位。 EA=0 中断总禁止,禁止所有中断,即不响应任何中断请求。 EA=1 中断总允许,总允许后中断的禁止或允许由各中断源的中断允许 控制位进行设置。

外部中断请求有两种信号形式:低电平触发方式和负跳脉冲触发方式:

低电平触发方式:低电平有效,只要CPU在每机器周期S5P2期间从引入端INTX采 样到低电平,就进入外中断。

负跳脉冲触发方式:负跳信号有效,即CPU在连续两个周期对引入端INTX 采样,如果 前周期为高电平,后一周期为低电平,则为有效的负跳脉冲触发方式的外中断申请。