CMOS集成逻辑门电路

cmos集成电路特点

cmos集成电路特点CMOS集成电路(Complementary Metal-Oxide-Semiconductor Integrated Circuit)是一种常见的集成电路技术,具有许多独特的特点。

在本文中,我们将详细介绍CMOS集成电路的特点,并从不同的角度对其进行扩展描述。

1. 低功耗:CMOS集成电路的一个显著特点是低功耗。

由于CMOS逻辑门内部只有在输入信号变化时才会消耗能量,因此在静态状态下,功耗几乎可以忽略不计。

这使得CMOS集成电路在电池供电和便携设备中得到广泛应用。

2. 抗干扰能力强:CMOS集成电路采用的是一种差动式的工作方式,输入信号的变化通过差分放大器进行放大,从而提高了抗干扰能力。

这使得CMOS集成电路在高噪声环境中具有良好的信号处理能力。

3. 高集成度:CMOS集成电路的制造工艺相对简单,可以实现高度集成。

由于CMOS工艺可以在同一芯片上制造多种功能的电路,因此可以在一个芯片上集成处理器、存储器、输入输出接口等多种功能,大大提高了集成度。

4. 工作电压范围广:CMOS集成电路可以在较低的电压下工作,通常工作电压在1V到5V之间。

这使得CMOS集成电路在低电压供电系统中具有广泛的应用前景。

5. 低噪声:CMOS集成电路由于采用差动放大器的工作方式,其输出信号与输入信号之间的幅度比较大,因此可以减小噪声对输出信号的影响。

这使得CMOS集成电路在信号处理领域中得到广泛应用。

6. 高可靠性:CMOS集成电路由于采用的是金属-氧化物-半导体结构,具有较高的可靠性。

金属层可以提供良好的接触和导电性能,氧化物层可以有效隔离金属层和半导体层,从而提高了电路的可靠性。

7. 高频特性好:CMOS集成电路具有较好的高频特性,可以实现高速的信号处理和传输。

由于CMOS集成电路的输入和输出特性都是电压驱动的,因此可以实现较高的工作频率。

8. 体积小:CMOS集成电路由于采用了微型制造工艺,可以实现高度集成,并且具有较小的体积。

CMOS逻辑电路设计

CMOS逻辑电路设计CMOS(Complementary Metal-Oxide-Semiconductor)逻辑电路是现代集成电路中广泛应用的一种电路结构。

它由N沟道MOS(NMOS)和P沟道MOS(PMOS)互补组成,具有低功耗、高噪声抑制和高速运算等优势。

在本文中,我们将探讨CMOS逻辑电路的设计原理和方法。

一、CMOS逻辑门的基本结构CMOS逻辑门是由一对互补的MOS管组成的。

其中,NMOS管是由N沟道与P+掺杂的互补金属氧化物半导体(CMOS)结构形成,而PMOS管是由P沟道与N+掺杂的CMOS结构形成。

CMOS逻辑电路通过控制这些NMOS管和PMOS管的某些管子通断来实现逻辑运算。

二、CMOS逻辑门的基本原理CMOS逻辑门的基本原理是利用MOS管在开关状态时流过的电流来实现信号的逻辑运算。

当NMOS管的门极接收到高电平信号(逻辑1)时,通常情况下,NMOS管导通,PMOS管截止。

相反,当NMOS 管的门极接收到低电平信号(逻辑0)时,NMOS管截止,PMOS管导通。

通过这种控制逻辑,CMOS逻辑门可以实现与门、或门、非门等基本逻辑运算。

三、CMOS逻辑电路的设计方法在进行CMOS逻辑电路设计时,需要遵循以下步骤:1. 确定逻辑功能:根据所需的逻辑运算,确定需要设计的CMOS逻辑门类型。

2. 绘制逻辑图:根据所需的逻辑功能,用逻辑符号绘制电路的逻辑图。

3. 分析逻辑功能:根据逻辑图,分析逻辑门输入和输出之间的关系,确定每个逻辑门的输入和输出真值表。

4. 选择器件尺寸:根据所需的逻辑门延迟、功耗和面积等要求,选择合适的管子尺寸。

5. 进行布线:根据所选用的管子尺寸,进行电路的布线设计。

6. 进行模拟仿真:使用电路设计软件,进行CMOS逻辑电路的仿真,验证其功能和性能。

7. 进行物理实现:根据设计结果,进行CMOS逻辑电路的物理实现,包括掩膜制作、晶圆制作和封装测试等过程。

四、CMOS逻辑电路的优势与应用CMOS逻辑电路具有以下优势:1. 低功耗:由于CMOS逻辑电路的特殊结构,只有在发生信号变换时才会有较大电流流过。

CMOS逻辑门电路

CMOS逻辑门电路CMOS逻辑门电路是在TTL电路问世之后,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件。

CMOS电路的工作速度可与TTL 相比较,而它的功耗和抗干扰能力则远优于TTL。

此外,几乎所有的超大规模存储器件,以及PLD器件都采用CMOS艺制造,且费用较低。

早期生产的CMOS门电路为4000系列,随后发展为4000B系列。

当前与TTL兼容的CMO器件如74HCT系列等可与TTL器件交换使用。

下面首先讨论CMOS反相器,然后介绍其他CMO逻辑门电路。

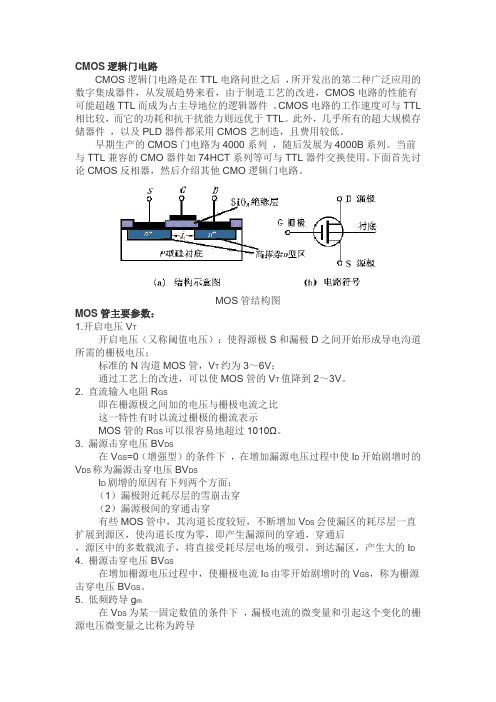

MOS管结构图MOS管主要参数:1.开启电压V T·开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;·标准的N沟道MOS管,V T约为3~6V;·通过工艺上的改进,可以使MOS管的V T值降到2~3V。

2. 直流输入电阻R GS·即在栅源极之间加的电压与栅极电流之比·这一特性有时以流过栅极的栅流表示·MOS管的R GS可以很容易地超过1010Ω。

3. 漏源击穿电压BV DS·在V GS=0(增强型)的条件下,在增加漏源电压过程中使I D开始剧增时的V DS称为漏源击穿电压BV DS·I D剧增的原因有下列两个方面:(1)漏极附近耗尽层的雪崩击穿(2)漏源极间的穿通击穿·有些MOS管中,其沟道长度较短,不断增加V DS会使漏区的耗尽层一直扩展到源区,使沟道长度为零,即产生漏源间的穿通,穿通后,源区中的多数载流子,将直接受耗尽层电场的吸引,到达漏区,产生大的I D 4. 栅源击穿电压BV GS·在增加栅源电压过程中,使栅极电流I G由零开始剧增时的V GS,称为栅源击穿电压BV GS。

5. 低频跨导g m·在V DS为某一固定数值的条件下,漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导·g m反映了栅源电压对漏极电流的控制能力·是表征MOS管放大能力的一个重要参数·一般在十分之几至几mA/V的范围内6. 导通电阻R ON·导通电阻R ON说明了V DS对I D的影响,是漏极特性某一点切线的斜率的倒数·在饱和区,I D几乎不随V DS改变,R ON的数值很大,一般在几十千欧到几百千欧之间·由于在数字电路中,MOS管导通时经常工作在V DS=0的状态下,所以这时的导通电阻R ON可用原点的R ON来近似·对一般的MOS管而言,R ON的数值在几百欧以内7. 极间电容·三个电极之间都存在着极间电容:栅源电容C GS 、栅漏电容C GD和漏源电容CDS·C GS和C GD约为1~3pF·C DS约在0.1~1pF之间8. 低频噪声系数NF·噪声是由管子内部载流子运动的不规则性所引起的·由于它的存在,就使一个放大器即便在没有信号输人时,在输出端也出现不规则的电压或电流变化·噪声性能的大小通常用噪声系数NF来表示,它的单位为分贝(dB)·这个数值越小,代表管子所产生的噪声越小·低频噪声系数是在低频范围内测出的噪声系数·场效应管的噪声系数约为几个分贝,它比双极性三极管的要小一、CMOS反相器由本书模拟部分已知,MOSFET有P沟道和N沟道两种,每种中又有耗尽型和增强型两类。

CMOS门电路

2.1.4 CMOS门电路的电气特性

CD4000 系列门电路的极限参数( VDD=5V) ◆ 输出高电平电压VOH ,VOH(min)= VDD-0.1V

◆ ◆ ◆

◆

输出低电平电压VOL ,VOL(max)= 0.1V 输入高电平电压VIH ,VIH(min)= 70%VDD 输入低电平电压VIL,VIL(max)= 30%VDD 阈值电压VTH=1/2VDD

PMOS

漏极相连 做输出端 NMOS

柵极相连 做输入端

2.1.2 CMOS反相器

2. CMOS反相器的工作原理

(1)当vI=0V时,vGSN=0V,VTN 截 止 , ∣ vGSP∣=VDD , VTP 导 通 , vO≈VDD,门电路输出输出高电平;

VDD

VTP vI VTN vO

( 2 ) 当 vI=VDD 时 , VGSN=VDD , VTN导通,∣VGSP∣=0V,VTP截止 ,vO≈0V,门电路输出低电平。

问题的提出

异或门的逻辑功能:

A B =1 F

输入相同,输出为“0”

输入不同,输出为“1”

F=AB

内部电路是什么样的,如何实现相应的逻辑功能?

门电路有哪些参数?如何正确使用?

本章的教学目标

■ 理解CMOS门电路结构与工作原理 ■ 掌握CMOS门电路外特性,正确使用CMOS门电路

■ 理解TTL门电路结构与工作原理 ■ 掌握TTL门电路外特性,正确使用TTL门电路

(2)由动态尖峰电流产生的瞬时动态功耗

VDD VTP iD vI vO vO

0 iD

t

VTN

0

t

PT CP DVD2D f

(3)总的动态功耗

2 PD PC PT C L C PD)VDD f (

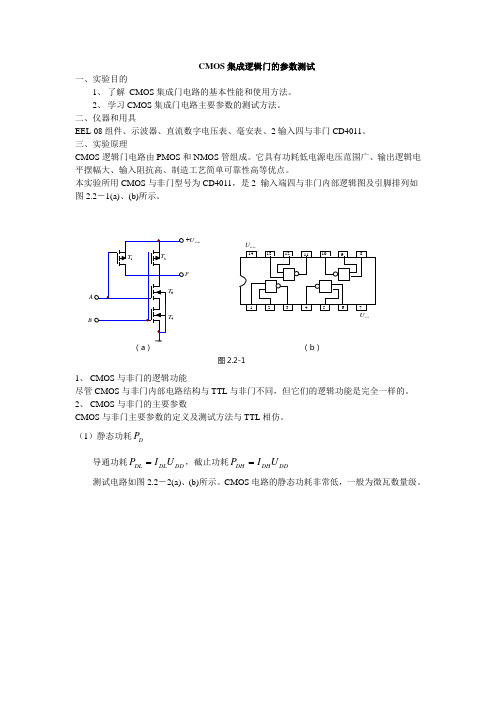

实验二 CMOS集成逻辑门的参数测试

(1) 输出高低电压OH U 和OL U输出端不带任何负载时,当输入端全部接高电平OH U 时,测得的输出电平就是OL U (=)0;当输入端有一个为低电平时,测得的低电平就是OH U (=DD U ) (2) 拉电流和灌电流负载能力图2.2-3所示电路中,输入端接低电平,输出端接拉电流负载L R ,调节L R ,当OL U 上升到0.5V 时所对应的负载电流,即为OL I 。

3、 电压传输特性CMOS 门电路电压传输特性的测试方法类似于TTL 门电路。

图2-4为逐点测量电压传输特性的实验电路。

oHoL(a )(b )图2.2-2(a )(b )图2.2-3ΩK由示波CMOS 与非门CD4011的主要参数规范(DD U =10V )(1) 静态电源电流≤5uA;(2).输出低电平0.1V;(3).输出高电平9.5V ;(4).输出驱动电流OL I >300uA,OH I >300uA;(5).最大允许电压18V ;(6). 最小允许电压3V ;(7).输出延迟时间pdH t =300~150ns,pdL t = 300~150ns ;(8).输入电容5pF5、 CMOS 电路使用注意事项(1)DD U 接电源正极,SS U 接电源负极(通常接地),电源绝对不容反接。

(2)电源电压使用范围+3V ~+18V ,实验中一般要求使用+12V 或+5V 电源。

工作在不同电源电压下的器件,其输出阻抗、工作速度和功耗等参数也会不同,在设计、使用中应引WR K 100图2.2-4起注意。

(3)器件输入信号i U ,要求DD i SS U U U <<范围内。

(3) 闲置输入端一律不准悬空,输入端悬空,不仅会造成逻辑混乱,而且容易损坏器件。

闲置输入端的处理方法:a. 按照逻辑要求,直接接DD U 或SS U .b. 工作速度不高的电路中允许与有用输入端并联使用。

(4) 输出端不允许直接与DD U 或SS U 连接,否则将导致器件损坏。

CMOS集成逻辑门电路特点及使用方法

CMOS集成逻辑门电路特点及使用方法

1.低功耗:CMOS电路在工作时只有短暂的电流流动,且仅在切换过程中会有瞬间的短路电流,因此功耗较低。

2.高集成度:CMOS电路能够实现大规模的集成,由于其结构简单,可以在一个芯片上实现多个逻辑门功能,从而提高整体集成度。

3.抗干扰能力强:CMOS电路采用互补器件,两种类型的晶体管结合在一起,当一种开启时,另一种关闭,因此对干扰信号的抵抗能力强。

4.工作稳定:CMOS电路由于采用了互补结构,不容易产生热失调现象,故工作稳定性较高。

5.可编程性强:CMOS电路通常具有很好的可编程性,可以通过调整电流大小、精密度等参数来实现不同逻辑功能的设计。

1.电路设计:根据需要设计逻辑电路,包括确定所需的逻辑功能、输入输出端口等。

2.电路仿真:使用电路仿真软件对设计的逻辑电路进行仿真,验证其正确性并进行必要的调整。

3.电路布局:根据设计的逻辑电路,进行电路布局设计,确定晶体管和连线的布局,保证电路的正常工作。

4.制作掩膜:根据布局设计制作相应的掩膜,并进行曝光和光刻等加工工艺。

5.生产加工:通过工艺流程,将设计好的电路图案制作到芯片上,完成电路的制造。

6.测试验证:对制作好的CMOS电路进行测试验证,检查其性能和功能是否符合设计要求。

总的来说,CMOS集成逻辑门电路具有低功耗、高集成度、抗干扰能力强、工作稳定等优点,广泛应用于数字电路、微处理器、存储器、通信电路、模拟电路等领域。

在使用CMOS集成电路时,需要进行电路设计、仿真、布局、制作掩膜、生产加工和测试验证等步骤,以确保电路的正常工作和性能达到设计要求。

CMOS技术的不断发展将为电子行业带来更多的创新和发展机遇。

CMOS 集成逻辑门电路特点及使用方法

CMOS 集成逻辑门电路特点及使用方法1.CMOS集成电路特点CMOS集成电路的特点是功耗极低、输出幅度大噪声容限大、扇出能力强。

MOS逻辑门电路主要分为NMOS、PMOS、CMOS三大类,PMOS是MOS逻辑门的早期产品,它不仅工作速度慢且使用负电源,不便与TTL电路连接,CMOS是在NMOS的基础上发展起来,它的各种性能较NMOS都好。

2.集成CMOS电路的特性参数CMOS门电路主要参数的定义同TTL电路,下面主要说明CMOS电路主要参数的特点。

(1)输出高电平U OH 与输出低电平U OLCMOS门电路U OH的理论值为电源电压U DD,U OH(min)=0.9U DD;U OL的理论值为0V,U OL(max)=0.01U DD。

所以CMOS门电路的逻辑摆幅(即高低电平之差)较大,接近电源电压U DD值。

(2)阈值电压U TH从CMOS 非门电压传输特性曲线中看出,输出高低电平的过渡区很陡,阈值电压U TH 约为U DD/2。

(3)抗干扰容限CMOS非门的关门电平U OFF为0.45U DD,开门电平U ON为0.55U DD。

因此,其高、低电平噪声容限均达0.45U DD。

其他CMOS门电路的噪声容限一般也大于0.3U DD,电源电压U DD 越大,其抗干扰能力越强。

(4)传输延迟与功耗CMOS电路的功耗很小,一般小于1 mW/门,但传输延迟较大,一般为几十ns/门,且与电源电压有关,电源电压越高,CMOS电路的传输延迟越小,功耗越大。

前面提到74HC 高速CMOS系列的工作速度已与TTL系列相当。

(5)扇出系数因CMOS电路有极高的输入阻抗,故其扇出系数很大,一般额定的扇出系数可达50。

但必须指出的是,扇出系数是指驱动CMOS电路的个数,若就灌电流负载能力和拉电流负载能力而言,CMOS电路远远低于TTL电路。

以测试过的CD4001为例,其主要特性参数见表11-12。

表3 CD4001四2或非门主要特性参数注:以上参数范围为电源电压选择5V、10V及15V的前提下所得。

CMOS集成门电路

工作原理 在反相器基础上串接 EN = 0 时,VP2 和 VN2 了 PMOS 管 VP2 和 NMOS 导通,呈现低电阻,不影 管 CMOS VN2,它们的栅极分别 响 反相器工作。 受 EN Y =和 A EN 控制。 EN = 1 时,VP2、VN2 均截止,输出端 Y 呈现高 阻态。 因此构成使能端低 电平有效的三态门。

VP1

A Z Y=A VN1

Y

EN

1 0

0 1

截止 导通 VN2

EN

低电平使能的 CMOS 三态输出门

三、CMOS 集成逻辑门使用要点

1. 注意不同系列 CMOS 电路允许的电源电压范围不同, 一般多用 + 5 V。电源电压越高,抗干扰能力也越强。 2. 闲置输入端的处理

不允入电容, 使速度下降,因此工作频率高时不宜这样用。 与门和与非门的闲置输入端可接正电源或高电平; 或门和或非门的闲置输入端可接地或低电平。

[例] 试改正下图电路的错误,使其正常工作。

CMOS 门

悬空 悬空

TTL 门

≥

OD 门

&

EN

(a) 解: CMOS 门

(b) TTL 门

(c) VDD OD 门

(d)

VDD

Ya = AB Yb = A + B

Yc = A

A EN = 1 时 Y d= B EN = 0 时

[例] 试分别采用与非门和或非门实现与门和或门。 解:(1) 用与非门实现与门 因为 Y = AB = AB

回顾旧课:

应用集成门电路时,应注意: (1)由输入电阻确定输入信号

(2)多余输入端的连接

导语:

CMOS集成逻辑门电路是互补金属-氧化物 -半导体场效应管门电路的简称。它的突出优点 是微功耗、高抗干扰能力。在中大规模数字集 成电路中有着广泛的应用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

换会受到电容充放电的影响,使输出波形边沿变得缓

慢,输出电压的变化也会滞后于输入电压的变化。

为减小开关时间,可以用P沟道MOS管来代替电阻RD, 就构成所谓的CMOS开关。

1.2 常用CMOS逻辑门电路

1.CMOS反相器

(1)工作原理。

TN管为工作管,N沟道MOS增强 型场效应管,开启电压UTN 。 TP管为负载管(作漏极负载Rd), P沟道MOS增强型场效应管,开启 电压UTP。 栅极g接在一起,作为输入端 ; 漏极d接在一起,作为输出端 。

CMOS电路较之TTL电路具有以下优点: 功耗低、 静态电流小(约为纳安数量级)、抗干扰能力强、 电源电压范围宽、输入阻抗高、负载能力强等,应 用广泛。

1.1 MOS开关及其等效电路

1.MOS管开关等效电路

电路

输出特性曲线

当输入电压 较小时,有

,

MOS管截止, ,

当 增加,使

,

MOS管工作在可变电阻区。

(2)CMOS反相器电压传输特性和电流传输特性。

2.漏极开路门(OD门) 3.三态(TSL)输出门电路

4.CMOS传输门

又称模拟开关,既可以传输数字信号,也可以传输 模拟信号。

C=0时,传输门关闭,输入和输 出之间呈现出高阻抗状态,不能 进行信号传输。

C=1时, 在整个输入电压范围-5V~+5V内, 至少有一个场效应管导通。场效应 管导通,漏源间的沟道导通电阻 RON小于1kΩ,典型值为80Ω,漏极和源极之间相 当于短路,输出等于输入。

74VHC和74VHCT系列:保持74HC和74HCT系列 的功耗低等优点,并且在工作速度达到74HC和 74HCT系列的两倍。

74LVC和74AUC系列:这种系列是近年来随着便携 设备的发展,要求使用体积小,功耗低、电池耗电 小的半导体器件,因此先后推出了低电压CMOS器 件74LVC系列,及超低压CMOS器件74AUC系列, 并且半导体制造工艺可以使它们的成本更低、速度 更快,同时大多数低电压器件的输入输出电平可以 与5V的CMOS或TTL电平兼容OS管相当于受控制的可变电阻, 且 越大,输出特性曲线越陡峭,RON , (导通电阻)越小。

即MOS管分别工作在截 止区和可变电阻区时, 相当于受 控制的一个 无触点开关 。

2.MOS管开关特性 uI

uIH

O

uO

UDD

O

tpH

tpLH

由于MOS管本身存在电容效应及L 导通电阻,在输入端

加入一个理想脉冲信号时,导通闭合两种状态之间转

即C=1时,传输门打开

1.3 CMOS逻辑门系列

4000系列:早期基本的CMOS集成逻辑门系列,后 来发展为4000B,应用十分广泛。其工作电压宽 (3~18V)、功耗低、抗干扰能力强,但工作速度 较慢,平均传输延迟时间为几十纳秒,最高工作频 率小于5MHz,且与TTL不兼容。

74HC和74HCT系列:74HC系列的其工作电压为 2~6V。与4000B系列相比,其工作速度快,且带负 载能力强。74HCT系列工作电压为4.5V~5.5V,并 可与TTL兼容。

电源UDD须大于两只MOS管的开启 电压的绝对值之和

即UDD > UTN +∣UTP∣

当输入电压 为低电平“0”时, 工作管TN因其UGS小于开启电压 UTN而截止,负载管TP因其UGS小 于开启电压UTP而导通。 工作管TN截止,漏极电流近似为 零,输出电压 为高电平“1”。

当输入电压 为高电平“1”时,工作管TN因其UGS大 于开启电压UTN而导通,负载管TP因其UGS大于开启电 压UTP而截止,输出电压 为低电平“0”。 即电路实现反相器功能,工作管TN和负载管TP总是 工作在互补的开关工作状态,即TN 和TP的工作状态 互补,所以CMOS电路称为互补型MOS电路。

数字电子技术基础

CMOS集成逻辑 门电路

CMOS集成逻辑门电路

1.1 MOS开关及其等效电路 1.2 常用CMOS逻辑门电路 1.3 CMOS逻辑门系列

MOS电路 --由金属氧化物绝缘栅型场效应(MOS)管 构成的单极型集成电路。

主要有三种类型: NMOS门电路、PMOS门电路和CMOS门电路。