vhdl中generic的分频用法

第五讲 VHDL数据对象及属性

第5讲 VHDL数据对象及属性 变量 (variable)

•变量代表电路单元内部的操作,代表暂存的临时数 据。与信号和常量相比,变量仅用于局部的电路描 述,只能用于进程、函数和过程内部。 •注意:对变量的赋值是立即生效的,无需等待进程 结束。新的值可以在下一行代码中立即使用。 •变量的赋值符号“:=”,语法结构:

18

第5讲 VHDL数据对象及属性

如改为信号,则无法实现原功能: …… signal temp : std_logic; …… process(indicator, sig, temp) begin temp<= ‘0’ ; temp<=temp xor (sig(0) and indicator(0)); temp<=temp xor (sig(1) and indicator(1)); temp<=temp xor (sig(2) and indicator(2)); temp<=temp xor (sig(3) and indicator(3)); output <= temp ; 19 end process ;

第5讲 VHDL数据对象及属性 process (a, b, c, d, s0, s1) begin sel<=0; if (s0=‘1’) then sel<=sel+1; end if; if (s1=‘1’) then sel<=sel+2; end if; case sel is when 0=>y<=a; when 1=>y<=b; when 2=>y<=c; when 3=>y<=d; end case; end process; end not_ok;

vhdl中的generic

VHDL语言中generic(类属)类属GENERIC 参量是一种端口界面常数,常以一种说明的形式放在实体或块结构体前的说明部分。

类属为所说明的环境提供了一种静态信息通道,类属与常数不同,常数只能从设计实体的内部得到赋值且不能再改变,而类属的值可以由设计实体外部提供。

因此设计者可以从外面通过类属参量的重新设定而容易地改变一个设计实体或一个元件的内部电路结构和规模。

类属参量以关键词GENERIC 引导一个类属参量表,在表中提供时间参数或总线宽度等静态信息。

类属表说明用于设计实体和其外部环境通信的参数,传递静态的信息。

类属在所定义的环境中的地位与常数十分接近,但却能从环境,如设计实体,外部动态地接受赋值,其行为又有点类似于端口PORT,因此常如以上的实体定义语句那样将类属说明放在其中,且放在端口说明语句的前面。

在一个实体中定义的来自外部赋入类属的值可以在实体内部或与之相应的结构体中读到,对于同一个设计实体,可以通过GENERIC 参数类属的说明,为它创建多个行为不同的逻辑结构,比较常见的情况是利用类属来动态规定一个实体的端口的大小,或设计实体的物理特性,或结构体中的总线宽度,或设计实体中底层中同种元件的例化数量等等。

一般在结构体中,类属的应用与常数是一样的,例如:当用实体例化一个设计实体的器件时,可以用类属表中的参数项定制这个器件,如可以将一个实体的传输延迟,上升和下降延时等参数加到类属参数表中,然后根据这些参数进行定制,这对于系统仿真控制是十分方便的。

其中的常数名是由设计者确定的类属常数名,数据类型通常取INTEGER 或TIME 等类型,设定值即为常数名所代表的数值,但需注意VHDL 综合器仅支持数据类型为整数的类属值。

程序3-2和3-3是两个使用了类属说明的实例描述程序3-2ENTITY mcu1 ISGENERIC (addrwidth : INTEGER := 16);PORT(add_bus : OUT STD_LOGIC_VECTOR(addrwidth-1 DOWNTO 0) );...在这里GENERIC 语句对实体mcu1 作为地址总线的端口add_bus 的数据类型和宽度作了定义即定义add_bus 为一个16 位的标准位矢量定义addrwidth 的数据类型是整数INTEGER 其中常数名addrwidth减 1 即为15 所以这类似于将上例端口表写成PORT (add_bus : OUT STD_LOGIC_VECTOR (15 DOWNTO 0));由程序3-2 可见对于类属值addrwidth 的改变将对结构体中所有相关的总线的定义同时作了改变由此将改变整个设计实体的硬件结构程序3-3 2输入与门的实体描述VHDL实用教程22ENTITY PGAND2 ISGENERIC ( trise : TIME := 1 ns;tfall : TIME := 1 ns ) ;PORT ( a1 : IN STD_LOGIC ;a0 : IN STD_LOGIC ;z0 : OUT STD_LOGIC );END ENTITY PGAND2;这是一个准备作为 2 输入与门的设计实体的实体描述在类属说明中定义参数trise 为上沿宽度tfall为下沿宽度它们分别为1ns 这两个参数用于仿真模块的设计以下的程序3-5 是一个顶层设计文件它在例化语句中调用了程序3-4 读者应注意到在程序3-4 中的类属变量n 并没有如程序3-2 那样明确规定了它的取值n 的具体取值是在程序3-5 中的类属映射语句GENERIC MAP ( )中指定的并在两个不同的类属映射语句中作了不同的赋值程序3-4 和3-5 给出了类属语句的一种典型应用。

基于VHDL数控分频器设计

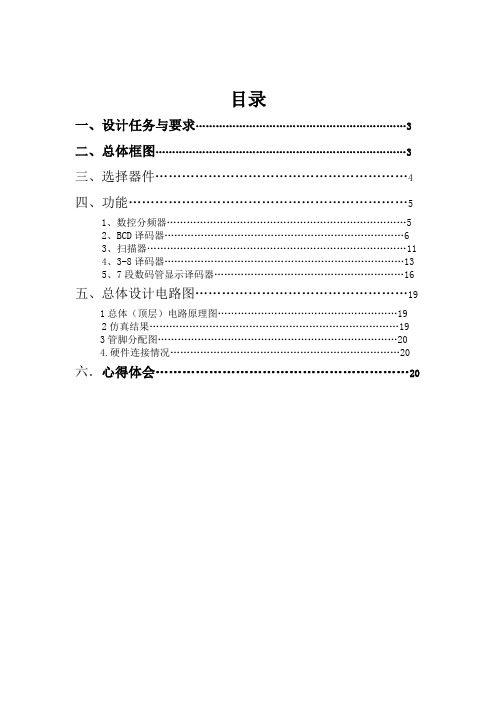

目录一、设计任务与要求 (3)二、总体框图 (3)三、选择器件 (4)四、功能 (5)1、数控分频器 (5)2、BCD译码器 (6)3、扫描器 (11)4、3-8译码器 (13)5、7段数码管显示译码器 (16)五、总体设计电路图 (19)1总体(顶层)电路原理图 (19)2仿真结果 (19)3管脚分配图 (20)4.硬件连接情况 (20)六.心得体会 (20)数控分频器设计一、设计任务与要求数控分频器的功能就是当输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,以实现所需的输出频率。

基本功能:1、实现8位分频器,依据输入的8位2进制数的不同,有不同的分频比。

如输入10010000,即对输入的时钟信号进行144分频,如输入01001000,即对输入的时钟信号进行72 分频。

2、输出的波形应为占空比位50%的方波。

3、有显示功能,显示当前的分频比,即,输入的二进制数的大小。

总体框图设计思路:数控分频器用计数值可并行预置的加法器设计完成,当在输入端给定不同输入数据时将对输入的时钟信号有不同的分频比。

把输入端输入的八位二进制数直接通过BCD译码器转换为十位BCD码表示的十进制数,通过扫描器对3个数码管进行选通扫描,最后7段数码管显示译码器对选中数码管的赋值进行译码,并驱动数码管显示该数据。

模块的功能:1、数控分频器:实现8位分频器,依据输入的8位2进制数的不同,有不同的分频比。

如输入10010000,即对输入的时钟信号进行144分频。

2、BCD译码器:把输入端的8位2进制数转换成10位BCD码表示的十进制数。

3、扫描器:when “000”=>daout<=dout(3 downto 0);when “001”=>daout<=dout(7 downto 4);when “010”=>daout<=dout(3 downto 2)<="00";daout(1 downto 0)<=dout(9 downto 8);when others=>null;4、3-8译码器:当sel=0时,q=11111110;选择个位数码管亮。

VHDL语言各种分频器的设计

硬件描述

使用VHDL,设计师可以描述电路 的结构、行为和功能,而无需关 心具体的物理实现细节。

设计层次

VHDL适用于不同层次的设计,从 门级到系统级,使得设计者可以 专注于设计逻辑而不是物理实现。

VHDL语言基本结构

实体

描述电路的输入和输出端口。

结构体

描述电路的内部逻辑和行为。

库

包含预定义的元件和函数。

end if;

end process;

8分频器设计

end Behavioral;

```

16分频器设计

16分频器:将输入频率降低到原来的 十六分之一。

VHDL代码实现

```vhdl

16分频器设计

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

03

if count = 3 then

4分频器设计

q <= '1';

count <= 0;

4分频器设计

01

else

02

q <= '0';

03

count <= count + 1;

4分频器设计

end if;

end if; end process;

4分频器设计

end Behavioral; ```

配置

指定实体和结构体的关联方式。

VHDL语言数据类型

标量类型

包括整数、实数、布尔等。

记录类型

组合不同数据类型的结构体。

向量类型

如位向量,用于表示位或字节。

数组类型

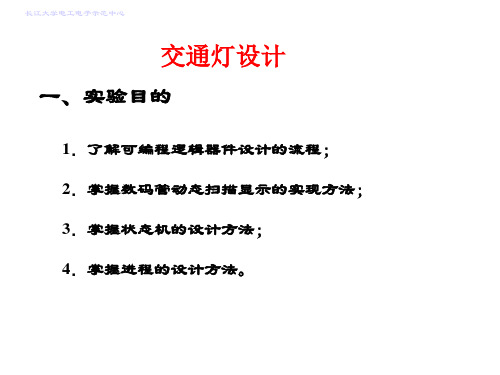

VHDL编程实现交通灯控制(数电实验)解析

•

emergencykey:in std_logic; --紧急开关

•

time_h,time_l:out std_logic_vector(3 downto 0); ; --定时

•

red,green,yellow:out std_logic_vector(3 downto 0) ; --红黄绿灯

•

);

描述状态机的进程

状态机的描述方式: 三进程、二进程、单进程(本实验采用)

一般采用三个进程来描述状态机 描述状态机寄存器的时序进程 描述次态产生逻辑的组合逻辑进程 描述输出组合逻辑进程

状态机寄存器的时序进程

process(reset,clk)

begin

if reset='1' then

current_state<=初始状态;

在进程中利用自定义数据类型定义交通灯的4个状态, 根据东西、南北方向的时间计数器的计数结果利用CASE 语句实现4个状态的转换,在每一个状态中利用内部信号 传递实现对红黄绿灯的显示控制。

FSM设计方法

• 分析控制器设计指标, 建立系统算法模型, 即状态转换图;

• 分析被控对象的时序, 确定控制器的有限 状态机的各个状态及输入、输出条件;

end if;

•

);

• end scandisplay;

• architecture behav of scandisplay is

• end if; •end process;

• signal num_in: std_logic_vector(3 downto 0); • signal counter:integer range 0 to 1; • signal led_chioce:std_logic; • Begin

基于VHDL的串口程序

在quartus里面没找到SCI的LPM部件,又不想自己从头编写,在网上找到了一个verilog的程序,也找到了和这个实现方法相同的VHDL程序。

都是接收到按键按下时候,启动串口发送,发送welcom但是都是发现一个,并延时重新读取按键,然后再重新启动发送。

数据格式是9600 boud rate、8数据位、1启动位、1停止位,每16个bit周期发送一个byte,接收程序,没有中间多位判断部分,考虑接收的有效性和可靠性,对程序进行了修改,改为每11个bit周期发送一个byte,这样也可以兼容接收2个停止位的接收程序,在接收程序中进行了多相判断。

程序和截图如下:--本模块的功能是验证实现和PC机进行基本的串口通信的功能。

需要在PC机上安装一个串口调试工具来验证程序的功能。

--程序实现了一个收发一帧10个bit(即无奇偶校验位)的串口控制器,10个bit是1位起始位,8个数据位,1个结束位。

--串口的波特律由程序中定义的div_par参数决定,更改该参数可以实现相应的波特率。

程序当前设定的div_par 的值--是0x145,对应的波特率是9600。

用一个8倍波特率的时钟将发送或接受每一位bit的周期时间划分为8个时隙以使通--信同步.--程序的基本工作过程是,按动一个按键key1 控制器向PC的串口发送“welcome",--PC机接收后显示验证数据是否正确(串口调试工具设成按ASCII码接受方式).--PC可随时向FPGA发送0-F的十六进制数据,FPGA接受后显示在7段数码管上.library ieee;-- design by jiaolonglanuse myserial isgeneric ( boud_rate:integer := 9600;clk_rate :integer := 50_000_000);port( clk : in std_logic;rstn : in std_logic;rxd : in std_logic; --receive bittxd : out std_logic; --send bit-- txd_buff :in std_logic_vector(7 downto 0); -- buffer write in-- write_data: in std_logic; -- write dataen :out std_logic_vector(7 downto 0);seg_data:out std_logic_vector(7 downto 0);-- rxd_buff :out std_logic_vector(7 downto 0);key_input:in std_logic-- testout: out std_logic-- read_data: in std_logic);end entity myserial;architecture bhv of myserial isSIGNAL div_reg : integer range 0 to 2**16-1;--分频计数器,分频值由波特率决定。

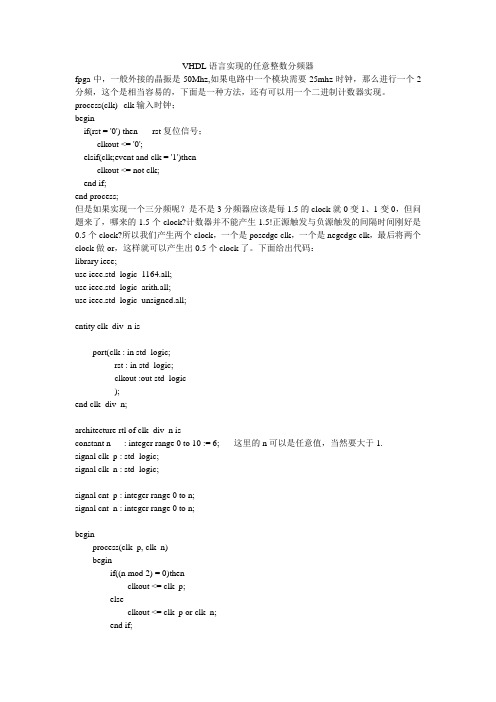

VHDL语言实现的任意整数分频器

VHDL语言实现的任意整数分频器fpga中,一般外接的晶振是50Mhz,如果电路中一个模块需要25mhz时钟,那么进行一个2分频,这个是相当容易的,下面是一种方法,还有可以用一个二进制计数器实现。

process(clk)--clk输入时钟;beginif(rst = '0') then --rst复位信号;clkout <= '0';elsif(clk;event and clk = '1')thenclkout <= not clk;end if;end process;但是如果实现一个三分频呢?是不是3分频器应该是每1.5的clock就0变1、1变0,但问题来了,哪来的1.5个clock?计数器并不能产生1.5!正源触发与负源触发的间隔时间刚好是0.5个clock?所以我们产生两个clock,一个是posedge clk,一个是negedge clk,最后将两个clock做or,这样就可以产生出0.5个clock了。

下面给出代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity clk_div_n isport(clk : in std_logic;rst : in std_logic;clkout :out std_logic);end clk_div_n;architecture rtl of clk_div_n isconstant n : integer range 0 to 10 := 6; --这里的n可以是任意值,当然要大于1.signal clk_p : std_logic;signal clk_n : std_logic;signal cnt_p : integer range 0 to n;signal cnt_n : integer range 0 to n;beginprocess(clk_p, clk_n)beginif((n mod 2) = 0)thenclkout <= clk_p;elseclkout <= clk_p or clk_n;end if;end process;process(clk, rst)beginif(rst = '0') thencnt_p <= 0;elsif(clk'event and clk = '1') thenif(cnt_p = n-1) thencnt_p <= 0;elsecnt_p <= cnt_p + 1;end if;end if;end process;process(clk, rst)beginif(rst = '0') thenclk_p <= '0';elsif(clk'event and clk = '1')thenif (cnt_p < (n/2)) thenclk_p <= '1';elseclk_p <= '0';end if ;end if;end process;process(clk, rst)beginif(rst = '0') thencnt_n <= 0;elsif(clk'event and clk = '0')thenif(cnt_n = n-1) thencnt_n <= 0;elsecnt_n <= cnt_n + 1;end if;end if;end process;process(clk, rst)beginif(rst = '0') thenclk_n <= '0';elsif(clk'event and clk = '0')thenif (cnt_n < (n/2)) thenclk_n <= '1';elseclk_n <= '0';end if ;end if;end process;end rtl;接下来我给出对应的testbench::有兴趣可以用make a simulation in modelsim LIBRARY ieee ;USE ieee.std_logic_1164.all ;USE ieee.std_logic_arith.all ;USE ieee.std_logic_unsigned.all ;ENTITY clk_div_n_tb ISEND clk_div_n_tb;ARCHITECTURE clk_div_tb_arch OF clk_div_n_tb ISSIGNAL clkout : std_logic ;SIGNAL rst : std_logic := '0' ;SIGNAL clk : std_logic := '1' ;COMPONENT clk_div_nPORT (clk : in std_logic ;rst : in std_logic ;clkout : out std_logic);END COMPONENT ;BEGINprocessbeginwait for 50ns;clk <= not clk;end process;rst <= '1' after 200ns;test:clk_div_nPORT MAP (clk => clk,rst => rst,clkout => clkout) ;END clk_div_tb_arch;。

分频器VHDL语言讲解

分频器设计------本源代码属于陈楠个人所有源代码中完成对时钟信号CLK的2分频,4分频,8分频,16分频。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY clkdiv ISPORT(clk : IN STD_LOGIC;clk_div2 : OUT STD_LOGIC;clk_div4 : OUT STD_LOGIC;clk_div8 : OUT STD_LOGIC;clk_div16 : OUT STD_LOGIC);END clk_div;ARCHITECTURE rtl OF clk_div ISSIGNAL count : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk)BEGINIF (clk’event AND clk=’1’) THENIF(count=”1111”) THENCount <= (OTHERS =>’0’);ELSECount <= count +1;END IF ;END IF ;END PROCESS;clk_div2 <= count(0);clk_div4 <= count(1);clk_div8 <= count(2);clk_div16 <= count(3);END rtl;对于分频倍数不是2的整数次幂的情况,我们只需要对源代码中的计数器进行一下计数控制就可以了,如下面源代码描述一个对时钟信号进行6分频的分频器。

ENTITY clkdiv ISPORT(clk : IN STD_LOGIC;clk_div6 : OUT STD_LOGIC);END clk_div;ARCHITECTURE rtl OF clk_div ISSIGNAL count : STD_LOGIC_VECTOR(1 DOWNTO 0);SIGNAL clk_temp : STD_LOGIC;BEGINPROCESS(clk)BEGINIF (clk’event AND clk=’1’) THENIF(count=”10”) THENcount <= (OTHERS =>’0’);clk_temp <=NOT clk_temp;ELSEcount <= count +1;END IF ;END IF ;END PROCESS;clk_div6 <= clk_temp;END rtl;前面两个分频器的例子描述的将时钟信号进行分频,分频后得到的时钟信号的占空比为1:1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

vhdl中generic的分频用法

在VHDL中,generic是一种允许用户在实例化时动态地指定数值

的机制。

它可以用于分频电路的设计,允许用户指定分频器的分频比。

分频器是一个电路,将输入时钟信号分频为一个较低频率的输出

信号。

通常情况下,分频比是一个整数数值。

在VHDL中,可以使用generic将分频比作为参数传递给分频器的实例化。

例如,假设我们要设计一个4分频器,将输入时钟信号分频为输

入时钟的1/4。

我们可以使用一个generic来指定这个分频比。

下面是一个使用generic实现的4分频器的伪代码示例:

```vhdl

entity Divider is

generic(

divide_ratio : positive := 4

);

port (

clk_in : in std_logic;

clk_out : out std_logic

);

end entity Divider;

architecture Behavioral of Divider is

begin

process(clk_in)

variable counter : positive range 0 to divide_ratio-1 := 0;

begin

if rising_edge(clk_in) then

counter := counter + 1;

if counter = divide_ratio-1 then

clk_out <= not clk_out;

counter := 0;

end if;

end if;

end process;

end architecture;

```

在这个例子中,我们定义了一个名为divide_ratio的generic,它的默认值为4。

这个generic确定了分频比。

在实例化时,用户可以选择不同的值来改变分频比。

在架构区,一个进程使用了一个变量counter来计数输入时钟的上升沿。

当counter达到divide_ratio-1时,表示已经达到了所需的分频比,然后将输出时钟信号取反,并重置counter为0。

这是一个简单的4分频器的例子,但是使用generic,可以很轻松地根据需要改变分频比。

例如,如果要设计一个10分频器,只需修改实例化语句中的divide_ratio的值为10即可。

总结起来,VHDL中的generic机制可以灵活地指定分频器的分频比,使得设计更具有通用性。

通过改变generic的值,可以在不修改代码的情况下实现不同分频比的分频器。