vhdl各种实验程序代码

VHDL实验程序

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY dff_1 ISPORT (rst_n:IN STD_LOGIC;clk:IN STD_LOGIC;d:IN STD_LOGIC;q:OUT STD_LOGIC;q_n:OUT STD_LOGIC);END ENTITY dff_1; ARCHITECTURE rtl OF dff_1 IS BEGINPROCESS (rst_n,clk) ISBEGINIF rst_n='0' THENq<='0';q_n<=NOT d;END IF;END PROCESS;END ARCHITECTURE rtl;library ieee;use ieee.std_logic_1164.all;entity d_ff isport(rst_n,clk,d: in std_logic;q,q_n:out std_logic);end entity d_ff;architecture rtl of d_ff isbeginprocess (rst_n,clk) isbeginif rst_n='0' thenq<='0';q_n<='1';elsif clk'event and clk='1' thenq<=d;q_n<=not d;end if;end process;end architecture rtl;library ieee;use ieee.std_logic_1164.all;entity shift_reg8 isgeneric (N:integer:=8);port(rst_n,a,clk: in std_logic;b:out std_logic);end entity shift_reg8 ;architecture rtl of shift_reg8 iscomponent d_ff isport(rst_n,clk,d: in std_logic;q,q_n:out std_logic);end component d_ff;signal s:std_logic_vector(1 to N-1);beging1: for i in 0 to N-1 generateg2: if i=0 generatedffx: d_ff port map ( rst_n,clk,a,s(i+1));end generate;g3: if i=N-1 generatedffx: d_ff port map(rst_n,clk,s(i),b);end generate;g4: if (i/=0) and (i/=N-1) generatedffx: d_ff port map( rst_n,clk,s(i),s(i+1));end generate;end generate;end architecture rtl;library ieee;use ieee.std_logic_1164.all;use work.my_package.all;entity int_bin isport( a:in integer range 0 to 9;b: in std_logic_vector(3 downto 0);c: out std_logic_vector(3 downto 0);d: out integer range 0 to 9);end entity int_bin;architecture rtl of int_bin isbeginc<=int_to_bit (a);bit_to_int(b,d);end architecture rtl;library ieee;use ieee.std_logic_1164.all;package my_package isprocedure bit_to_int( a: in std_logic_vector( 3 downto 0);signal b:out integer range 15 downto 0); function int_to_bit(a: integer range 15 downto 0) return std_logic_vector;end package my_package;package body my_package isprocedure bit_to_int( a: in std_logic_vector( 3 downto 0);signal b:out integer range 15 downto 0) is begincase a iswhen "0000" => b<=0;when "0001" => b<=1;when "0010" => b<=2;when "0011" => b<=3;when "0100" => b<=4;when "0101" => b<=5;when "0110" => b<=6;when "0111" => b<=7;when "1000" => b<=8;when "1001" => b<=9;when "1010" => b<=10;when "1011" => b<=11;when "1100" => b<=12;when "1101" => b<=13;when "1110" => b<=14;when "1111" => b<=15;when others => null;end case;end procedure bit_to_int;function int_to_bit (a: integer range 15 downto 0) return std_logic_vector is variable b: std_logic_vector(3 downto 0);begincase a iswhen 0 => b:="0000";when 1 => b:="0001";when 2 => b:="0010";when 3 => b:="0011";when 4 => b:= "0100";when 5 => b:="0101";when 6 => b:="0110";when 7 => b:="0111";when 8 => b:="1000";when 9 => b:="1001";when 10 => b:="1010" ;when 11 => b:="1011" ;when 12 => b:="1100";when 13 => b:="1101";when 14 => b:="1110";when 15 => b:="1111";when others => null;end case;return b;end function;end package body my_package;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt6 isport( clk: in std_logic;data_o:out std_logic_vector(2 downto 0));end entity cnt6;architecture rtl of cnt6 is--signal cnt:std_logic_vector(2 downto 0):="000"; beginprocess(clk) isvariable cnt:std_logic_vector(2 downto 0):="000";beginif clk'event and clk='1' thenif cnt="101" then--cnt<="000";cnt:="000";else--cnt<=cnt+1;cnt:=cnt+1;end if;end if;data_o<=cnt;end process;--data_o<=cnt;end architecture rtl;library ieee;use ieee.std_logic_1164.all;entity full_adder isport( a:in std_logic;b:in std_logic;c:in std_logic;s:out std_logic;co:out std_logic);end entity full_adder;architecture rtl of full_adder issignal a_n,b_n,c_n:std_logic;signal m1,m2,m4,m7:std_logic;signal m3,m5:std_logic;begina_n<=not a;b_n<=not b;c_n<=not c;m1<=a_n and b_n and c;m2<=a_n and b and c_n;m4<=a and b_n and c_n;m7<=a and b and c;m3<=a_n and b and c;m5<=a and b_n and c;s<=m1 or m2 or m4 or m7;co<= (a and b) or m3 or m5;end architecture rtl;library ieee;use ieee.std_logic_1164.all;entity max_min isport(a,b,c,d: in std_logic_vector(7 downto 0);max,min:out std_logic_vector(7 downto 0)); end entity max_min;--architecture rtl of max_min is-- begin-- process(a,b,c,d) is-- begin-- if a>b then-- if a>c then-- if a>d then-- max<=a;-- else-- max<=d;-- end if;-- else --a<c,c>b-- if c>d then-- max<=c;-- else-- max<=d;-- end if;-- end if;-- else -- a<b-- if b>c then-- if b>d then-- max<=b;-- else-- max<=d;-- end if;-- else --b<c,b>a-- if c>d then-- max<=c;-- else-- max<=d;-- end if;-- end if;-- end if;-- end process;-- end architecture rtl;architecture rtl of max_min isbeginprocess(a,b,c,d) isvariable t1:std_logic_vector(7 downto 0);begint1:=a;if t1<b thent1:=b;end if;if t1<c thent1:=c;end if;if t1<d thent1:=d;end if;end process;process(a,b,c,d) isvariable t2:std_logic_vector(7 downto 0);begint2:=a;if t2>b thent2:=b;end if;if t2>c thent2:=c;end if;if t2>d thent2:=d;end if;min<=t2;end process;end architecture rtl;library ieee;use ieee.std_logic_1164.all;entity relation_op isgeneric(N:integer:=8);port( a:in std_logic_vector(N-1 downto 0);b:in std_logic_vector(N-1 downto 0);c:in std_logic_vector(N-1 downto 0);d:in std_logic_vector(N-1 downto 0);max,min:out std_logic_vector(N-1 downto 0));end entity relation_op;architecture rtl of relation_op isshared variable tmp1,tmp2,tmp3,tmp4:std_logic_vector(N-1 downto 0); --variable tmp2:std_logic_vector(N-1 downto 0);beginprocess(a,b,c,d)isbeginif a<b thentmp1:=b;tmp2:=a;elsetmp1:=a;end if;if c<d thentmp3:=d;tmp4:=c;elsetmp3:=c;tmp4:=d;end if;if tmp1<tmp3 thenmax<=tmp3;elsemax<=tmp1;end if;if tmp2<tmp4 thenmin<=tmp2;elsemin<=tmp4;end if;end process;end architecture rtl;library ieee;use ieee.std_logic_1164.all;entity sum isport( start: in std_logic;dout:out integer range 0 to 4950);end entity sum;architecture rtl of sum isbeginprocess (start) isvariable rt:integer range 0 to 4950:=0;beginrt:=0;for i in 0 to 99 looprt:=rt+i;end loop;if start='1' thendout<=rt;elsedout<=0;end if;end process;end architecture rtl;library ieee;use ieee.std_logic_1164.all;entity mux_8 isport( d0,d1,d2,d3,d4,d5,d6,d7:in std_logic_vector( 7 downto 0);sel: in std_logic_vector( 2 downto 0);data_o:out std_logic_vector( 7 downto 0));end entity mux_8;architecture rtl of mux_8 isbeginprocess(sel,d0,d1,d2,d3,d4,d5,d6,d7) isbegincase sel iswhen "000" =>data_o<=d0;when "001" =>data_o<=d1;when "010" =>data_o<=d2;when "011" =>data_o<=d3;when "100" =>data_o<=d4;when "101" =>data_o<=d5;when "110" =>data_o<=d6;when "111" =>data_o<=d7;when others =>null;end case;end process;end architecture rtl;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt6 isport( clk:in std_logic;rst_n:in std_logic;data_o:out std_logic_vector(2 downto 0)); end entity cnt6;architecture rtl of cnt6 issignal tmp:std_logic_vector(2 downto 0);beginprocess(rst_n,clk) isbeginif rst_n='0' thentmp<="000";elsif clk'event and clk='1' thenif tmp="101" thentmp<="000";elsetmp<=tmp+1;end if;end if;end process;data_o<=tmp;end architecture rtl;--architecture rtl of cnt6 is-- signal tmp:std_logic_vector(2 downto 0);---- begin-- process(rst_n,clk) is-- begin---- if clk'event and clk='1' then-- if rst_n='0' then-- tmp<="000";-- else-- if tmp="101" then-- tmp<="000";-- else-- tmp<=tmp+1;-- end if;-- end if;-- end if;-- end process;-- data_o<=tmp;-- end architecture rtl;library ieee;use ieee.std_logic_1164.all;entity cnt isport( rst_n: in std_logic;clk: in std_logic;data_o:out std_logic_vector(2 downto 0)); end entity cnt;--architecture rtl of cnt is-- signal q0,q1,q2:std_logic;-- begin-- process(rst_n,clk) is-- begin-- if rst_n='0' then-- q0<='0';-- q1<='0';-- q2<='0';-- elsif clk'event and clk='1' then-- q0<=not q0;-- q1<=q0 xor q1;-- q2<=(q0 and q1) xor q2;-- end if;-- end process;-- data_o<=q2&q1&q0;-- end architecture rtl;architecture rtl of cnt issignal q0,q1,q2:std_logic;beginprocess(rst_n,clk) isbeginif rst_n='0' thenq0<='0';elsif clk'event and clk='1' thenq0<=not q0;end if;end process;process(rst_n,q0) isbeginif rst_n='0' thenq1<='0';elsif q0'event and q0='0' thenq1<=not q1;end if;end process;process(rst_n,q1) isbeginif rst_n='0' thenq2<='0';elsif q1'event and q1='0' thenq2<=not q2;end if;end process;data_o<=q2&q1&q0;end architecture rtl;library ieee;use ieee.std_logic_1164.all;entity fre_div isport( rst_n:in std_logic;clk:in std_logic;clk_o:out std_logic);end entity fre_div;architecture rtl of fre_div istype state_t is (s_rst,s0,s1,s2,s3,s4,s5,s6,s7,s8,s9);signal state,next_state:state_t;signal clk_tmp:std_logic;beginprocess(rst_n,clk) isbeginif rst_n='0' thenstate<=s_rst;elsif clk'event and clk='1' thenstate<=next_state;end if;end process;process(state) isbegincase state iswhen s_rst => next_state<=s0;when s0 => next_state<=s1;when s1 => next_state<=s2;when s2 => next_state<=s3;when s3 => next_state<=s4;when s4 => next_state<=s5;when s5 => next_state<=s6;when s6 => next_state<=s7;when s7 => next_state<=s8;when s8 => next_state<=s9;when s9 => next_state<=s0;end case;end process;process(state) isbegincase state iswhen s_rst => clk_tmp<='0';when s0 => clk_tmp<='1';when s1 => clk_tmp<='1';when s2 => clk_tmp<='1';when s3 => clk_tmp<='1';when s4 => clk_tmp<='0';when s5 => clk_tmp<='0';when s6 => clk_tmp<='0';when s7 => clk_tmp<='0';when s8 => clk_tmp<='0';when s9 => clk_tmp<='0';end case;end process;process(clk) isbeginif clk'event and clk='1' thenclk_o<=clk_tmp;end if;end process;end architecture rtl;。

VHDL实验源程序

实验1—— EDA 工具使用与2选1多路选择器VHDL 描述实验2—— D 触发器VHDL 描述实验3—— 半加器VHDL 描述实验4—— 全加器VHDL 描述实验5——方波发生器VHDL 程序(简易函数发生器设计1)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY square ISPORT(clk,reset : IN STD_LOGIC;Q : OUT STD_LOGIC);END square;ARCHITECTURE bhv OF square ISBEGINPROCESS(clk,reset)VARIABLE cnt : INTEGER RANGE 0 TO 63;BEGINIF reset='0' THENq<='0';ELSIF clk'EVENT AND clk='1' THENcnt:=cnt+1;IF cnt<31 THENq<='0';ELSEq<='1';END IF;END IF;END PROCESS;END bhv;实验6 —正弦波发生器VHDL程序(简易函数发生器设计2)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY sin ISPORT(clk,reset:IN STD_LOGIC;q:OUT INTEGER RANGE 0 TO 255);END sin;ARCHITECTURE bhv OF sin ISBEGINPROCESS(clk,reset)VARIABLE tmp:INTEGER RANGE 0 TO 63;BEGINIF reset='0' THENq<=0;ELSIF clk'EVENT AND clk='1' THENIF tmp=63 THENtmp:=0;ELSEtmp:=tmp+1;END IF;CASE tmp ISWHEN 00=>q<=255;WHEN 01=>q<=254;WHEN 02=>q<=252;WHEN 03=>q<=249;WHEN 04=>q<=245;WHEN 05=>q<=239;WHEN 06=>q<=233;WHEN 07=>q<=225;WHEN 08=>q<=217;WHEN 09=>q<=207;WHEN 10=>q<=197;WHEN 11=>q<=186;WHEN 13=>q<=162; WHEN 14=>q<=150; WHEN 15=>q<=137; WHEN 16=>q<=124; WHEN 17=>q<=112; WHEN 18=>q<=99; WHEN 19=>q<=87; WHEN 20=>q<=75; WHEN 21=>q<=64; WHEN 22=>q<=53; WHEN 23=>q<=43; WHEN 24=>q<=34; WHEN 25=>q<=26; WHEN 26=>q<=19; WHEN 27=>q<=13; WHEN 28=>q<=8; WHEN 29=>q<=4; WHEN 30=>q<=1; WHEN 31=>q<=0; WHEN 32=>q<=0; WHEN 33=>q<=1; WHEN 34=>q<=4; WHEN 35=>q<=8; WHEN 36=>q<=13; WHEN 37=>q<=19; WHEN 38=>q<=26; WHEN 39=>q<=34; WHEN 40=>q<=43; WHEN 41=>q<=53; WHEN 42=>q<=64; WHEN 43=>q<=75; WHEN 44=>q<=87; WHEN 45=>q<=99; WHEN 46=>q<=112; WHEN 47=>q<=124; WHEN 48=>q<=137; WHEN 49=>q<=150;WHEN 51=>q<=174;WHEN 52=>q<=186;WHEN 53=>q<=197;WHEN 54=>q<=207;WHEN 55=>q<=217;WHEN 56=>q<=225;WHEN 57=>q<=233;WHEN 58=>q<=239;WHEN 59=>q<=245;WHEN 60=>q<=249;WHEN 61=>q<=252;WHEN 62=>q<=254;WHEN 63=>q<=255;WHEN OTHERS=>NULL;END CASE;END IF;END PROCESS;END bhv;实验7------- 加减法计数器VHDL程序加减法计数器:本例程为加减法计数器,主要实现的加减法计数的功能。

vhdl语言100例程序

vhdl语言100例程序以下是100个关于VHDL语言的程序示例:1. 用VHDL编写一个计数器模块2. 用VHDL编写一个SR-Latch模块3. 用VHDL编写一个JK-Flip Flop模块4. 用VHDL编写一个D-Flip Flop模块5. 用VHDL编写一个T-Flip Flop模块6. 用VHDL编写一个复位计数器模块7. 用VHDL编写一个移位寄存器模块8. 用VHDL编写一个状态机模块9. 用VHDL编写一个MUX模块10. 用VHDL编写一个DeMUX模块11. 用VHDL编写一个加法器模块12. 用VHDL编写一个减法器模块13. 用VHDL编写一个乘法器模块14. 用VHDL编写一个除法器模块15. 用VHDL编写一个比较器模块16. 用VHDL编写一个位逻辑模块17. 用VHDL编写一个字逻辑模块18. 用VHDL编写一个数据选择器模块19. 用VHDL编写一个FIFO队列模块20. 用VHDL编写一个LIFO栈模块21. 用VHDL编写一个流水线模块22. 用VHDL编写一个中断控制器模块23. 用VHDL编写一个时钟分频器模块24. 用VHDL编写一个IO控制器模块25. 用VHDL编写一个SPI通信控制器模块26. 用VHDL编写一个I2C通信控制器模块27. 用VHDL编写一个UART通信控制器模块28. 用VHDL编写一个哈希函数模块29. 用VHDL编写一个随机数产生器模块30. 用VHDL编写一个CRC校验器模块31. 用VHDL编写一个AES加密算法模块32. 用VHDL编写一个DES加密算法模块33. 用VHDL编写一个SHA加密算法模块34. 用VHDL编写一个MD5加密算法模块35. 用VHDL编写一个RSA加密算法模块36. 用VHDL编写一个卷积滤波器模块37. 用VHDL编写一个峰值检测器模块38. 用VHDL编写一个平滑滤波器模块39. 用VHDL编写一个中值滤波器模块40. 用VHDL编写一个微处理器模块41. 用VHDL编写一个信号发生器模块42. 用VHDL编写一个信号采集器模块43. 用VHDL编写一个频率计算器模块44. 用VHDL编写一个相位计算器模块45. 用VHDL编写一个时序分析器模块46. 用VHDL编写一个正弦波产生器模块47. 用VHDL编写一个余弦波产生器模块48. 用VHDL编写一个数字滤波器模块49. 用VHDL编写一个数字信号处理器模块50. 用VHDL编写一个数字识别模块51. 用VHDL编写一个自动售货机模块52. 用VHDL编写一个二进制加法器模块53. 用VHDL编写一个二进制减法器模块54. 用VHDL编写一个二进制乘法器模块55. 用VHDL编写一个二进制除法器模块56. 用VHDL编写一个自然对数模块57. 用VHDL编写一个指数函数模块58. 用VHDL编写一个三角函数模块59. 用VHDL编写一个高斯滤波器模块60. 用VHDL编写一个激光传感器模块61. 用VHDL编写一个超声波传感器模块62. 用VHDL编写一个光电传感器模块63. 用VHDL编写一个温度传感器模块64. 用VHDL编写一个气压传感器模块65. 用VHDL编写一个陀螺仪模块67. 用VHDL编写一个电流传感器模块68. 用VHDL编写一个电容传感器模块69. 用VHDL编写一个磁场传感器模块70. 用VHDL编写一个通信电缆模块71. 用VHDL编写一个电源控制器模块72. 用VHDL编写一个电机控制器模块73. 用VHDL编写一个汽车控制器模块74. 用VHDL编写一个飞机控制器模块75. 用VHDL编写一个摄像头模块76. 用VHDL编写一个音频控制器模块77. 用VHDL编写一个扬声器控制器模块78. 用VHDL编写一个拨号器模块79. 用VHDL编写一个振动控制器模块80. 用VHDL编写一个压力控制器模块81. 用VHDL编写一个过滤器模块82. 用VHDL编写一个微波发射模块84. 用VHDL编写一个智能电表模块85. 用VHDL编写一个闹钟模块86. 用VHDL编写一个计时器模块87. 用VHDL编写一个时间戳模块88. 用VHDL编写一个脉冲宽度模块89. 用VHDL编写一个电路仿真模块90. 用VHDL编写一个电路控制模块91. 用VHDL编写一个电路测试模块92. 用VHDL编写一个电路优化模块93. 用VHDL编写一个电路布局模块94. 用VHDL编写一个电路验证模块95. 用VHDL编写一个数字信号发生器模块96. 用VHDL编写一个数字信号反演器模块97. 用VHDL编写一个数字信号滤波器模块98. 用VHDL编写一个数字信号加速器模块99. 用VHDL编写一个数字信号降噪器模块100. 用VHDL编写一个数字信号解调器模块VHDL语言是一种硬件描述语言,它用于描述数字电路和系统。

VHDL实验代码示例

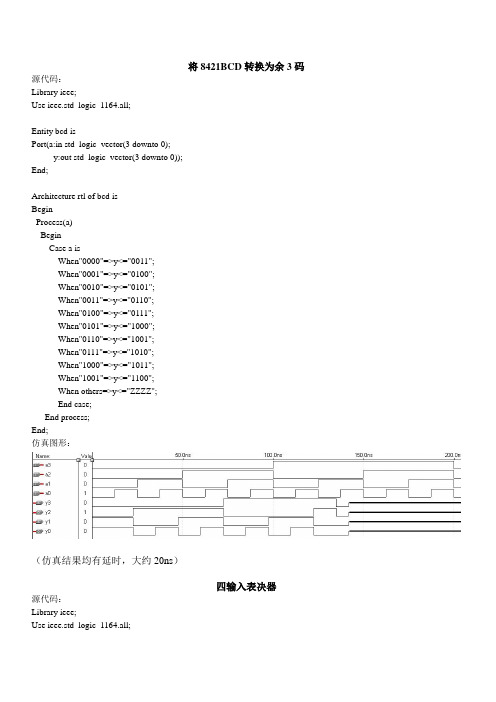

将8421BCD转换为余3码源代码:Library ieee;Use ieee.std_logic_1164.all;Entity bcd isPort(a:in std_logic_vector(3 downto 0);y:out std_logic_vector(3 downto 0));End;Architecture rtl of bcd isBeginProcess(a)BeginCase a isWhen"0000"=>y<="0011";When"0001"=>y<="0100";When"0010"=>y<="0101";When"0011"=>y<="0110";When"0100"=>y<="0111";When"0101"=>y<="1000";When"0110"=>y<="1001";When"0111"=>y<="1010";When"1000"=>y<="1011";When"1001"=>y<="1100";When others=>y<="ZZZZ";End case;End process;End;仿真图形:(仿真结果均有延时,大约20ns)四输入表决器源代码:Library ieee;Use ieee.std_logic_1164.all;Entity bjq isPort(i:in std_logic_vector(3 downto 0);f:out std_logic);End;Architecture nm2 of bjq isBeginProcess(i)Begincase i isWhen"0000"=>f<='0';When"0001"=>f<='0';When"0010"=>f<='0';When"0011"=>f<='0';When"0100"=>f<='0';When"0101"=>f<='0';When"0110"=>f<='0';When"0111"=>f<='1';When"1000"=>f<='0';When"1001"=>f<='0';When"1010"=>f<='0';When"1011"=>f<='1';When"1100"=>f<='0';When"1101"=>f<='1';When"1110"=>f<='1';When"1111"=>f<='1';When others=>f<='Z';End case;End process;End;仿真图形:2位二进制相乘电路源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity multi isport(A,B:in std_logic_vector(1 downto 0);F:out std_logic_vector(3 downto 0));end;architecture bhv of multi isbeginprocess(A,B)beginif(A="01" and B="01" )thenF<="0001";elsif(A="01" and B="10")thenF<="0010";elsif(A="01" and B="11")thenF<="0011";elsif(A="10" and B="01")thenF<="0010";elsif(A="10" and B="10")thenF<="0100";elsif(A="10" and B="11")thenF<="0110";elsif(A="11" and B="01")thenF<="0011";elsif(A="11" and B="10")thenF<="0110";elsif(A="11" and B="11")thenF<="1001";elseF<="0000";end if;end process;end;仿真图形:一位二进制全减器源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity subtracter isport(A,B,Ci:in std_logic;F,Co:out std_logic);end;architecture bhv of subtracter isbeginprocess(A,B,Ci)beginif(A='0' and B='0' and Ci='0')thenF<='0';Co<='0';elsif(A='0' and B='0' and Ci='1')thenF<='1';Co<='1';elsif(A='0' and B='1' and Ci='0')thenF<='1';Co<='1';elsif(A='0' and B='1' and Ci='1')thenF<='0';Co<='1';elsif(A='1' and B='0' and Ci='0')thenF<='1';Co<='0';elsif(A='1' and B='0' and Ci='1')thenF<='0';Co<='0';elsif(A='1' and B='1' and Ci='0')thenF<='0';Co<='0';elseF<='1';Co<='1';end if;end process;end;仿真图形:开关控制电路源代码:Library ieee;Use ieee.std_logic_1164.all;Entity switch_control isPort(a,b,c:in std_logic;y:out std_logic);End;Architecture nm5 of switch_control isBeginProcess(a,b,c);V ariable comb:std_logic_vector(2 downto 0);BeginComb:=a&b&c;Case comb isWhen"000"=>y<='0';When"001"=>y<='1';When"011"=>y<='0';When"010"=>y<='1';When"110"=>y<='0';When"111"=>y<='1';When"101"=>y<='0';When"100"=>y<='1';When others=>y<='X';End case;End process;End;仿真图形:4-16译码器library ieee;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY decode4-16 ISPORT(a,b,c,d:IN STD_LOGIC;q:BUFFER STD_LOGIC_VECTOR(15 DOWNTO 0)); END decode4-16 ;architecture behave of decode4-16 issignal indata:std_logic_vector(2 downto 0);beginindata<=c&b&a;process(indata)begincase indata iswhen “0000”=>y<=”1111111111111110”;when “0001”=>y<=”1111111111111101”;when “0010”=>y<=”1111111111111011”;w hen “0011”=>y<=”1111111111110111”;when “0100”=>y<=”1111111111101111”;when “0101”=>y<=”1111111111011111”;when “0110”=>y<=”1111111110111111”;when “0111”=>y<=”1111111101111111”;when “1000”=>y<=”1111111011111111”;when “1001”=>y<=”1111110111111111”;when “1010”=>y<=”1111101111111111”;when “1011”=>y<=”1111011111111111”;when “1100”=>y<=”1110111111111111”;when “1101”=>y<=”1101111111111111”;when “1110”=>y<=”1011111111111111”;when “1111”=>y<=”0111111111111111”;when others=>y<=”xxxxxxxxxxxxxxxx”;end case;end process;end behave;4-16译码器library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity test isPort(a:in std_logic;b:in std_logic;c:in std_logic;d:in std_logic;Y:buffer std_logic_vector(15 downto 0);r0:out std_logic;r1:out std_logic;r2:out std_logic;r3:out std_logic);end test;architecture Behavioral of test issignal DIN:std_logic_vector(3 downto 0);beginDIN<=a&b&c&d;process(DIN)begincase DIN iswhen"0000"=>Y<="1111111111111110";when"0001"=>Y<="1111111111111101";when"0010"=>Y<="1111111111111011";when"0011"=>Y<="1111111111110111";when"0100"=>Y<="1111111111101111";when"0101"=>Y<="1111111111011111";when"0110"=>Y<="1111111110111111";when"0111"=>Y<="1111111101111111";when"1000"=>Y<="1111111011111111";when"1001"=>Y<="1111110111111111";when"1010"=>Y<="1111101111111111";when"1011"=>Y<="1111011111111111";when"1100"=>Y<="1110111111111111";when"1101"=>Y<="1101111111111111";when"1110"=>Y<="1011111111111111";when"1111"=>Y<="0111111111111111";when others=>Y<="0000000000000000";end case;end process;r0<=not(Y(5) and Y(7) and Y(13) and Y(15));r1<=not(Y(6) and Y(7) and Y(9) and Y(11) and Y(13) and Y(14));r2<=not(Y(10) and Y(11) and Y(14));r3<=not(Y(15) and Y(15));end Behavioral;NET "d" LOC="p94";NET "c" LOC="p95";NET "b" LOC="p96";NET "a" LOC="p97";NET "r0" LOC="p58";NET "r1" LOC="p59";NET "r2" LOC="p60";NET "r3" LOC="p61";1.设计60进计数器:1)设计思想:两个同步计数器,一个实现个位计数,一个实现十位计数,当个位计数到9时,十位的计数器加一,并个位计数器清零,继续自加,如此循环,直到十位到5,即计数到59,一端口输出高电平,十位和个位计数器清零,如此循环。

VHDL实验报告与代码毕业设计(论文)

实验一. 分频器设计一.实验目的1.熟悉QUARTUSII 软件的使用2.熟悉PLD设计流程3. 学习分频器的设计二.实验内容设计一个最大分频为225的分频器,将50MHz时钟作为输入三.实验框图四.管脚设定CLOCK_50 PIN_N2LEDR[0] PIN_AE23五.实验代码LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_UNSIGNED.all;ENTITY clk1 ISPORT(clk:IN STD_LOGIC;DIGIT:OUT STD_LOGIC);END clk1;ARCHITECTURE clk1 OF clk1 ISBEGINCOUNT: PROCESS(clk)V ARIABLE temp:STD_LOGIC_VECTOR(25 DOWNTO 0);BEGINIF(clk'EVENT AND clk = '1')THENtemp := temp+1;IF(temp(25)='1') THENtemp:=(OTHERS=>'0');END IF;END IF;DIGIT <= temp(24);END PROCESS count;END clk1;六.心得体会通过这次实验,我初步掌握了QUARTUSII 软件的使用,为今后的实验打下基础。

实验二. VHDL描述风格比较一.实验目的1.深入体会VHDL三种描述风格的区别2. 学习3输入表决器,异或门的实现3.设计一个5输入表决器。

二.实验内容以3输入表决器,异或门,通用寄存器等代码为例,深入体会VHDL描述风格。

1.学习已给的3输入表决器代码,完成3输入表决器的三种描述方式的验证比较。

在QUARTUS II中对程序进行编译,下载,验证。

使用拔码开关SW0,SW1,SW2作为三个输入,输出在LEDR0表示,亮表示‘1’,不亮表示‘0’2.学习已给的异或门代码,完成异或门的三种描述方式的验证比较。

vhdl各种实验程序代码

1.三与门library ieee;use ieee.std_logic_1164.all;entity yumen isport(a,b,c : in std_logic;f : out std_logic);end yumen;architecture and3_1 of yumen isbeginf<=a and b and c;end architecture and3_1;2.三八译码器library ieee;use ieee.std_logic_1164.all;entity jg isport(a,b,c,g1,g2a,g2b:in std_logic;y:out std_logic_vector(7 downto 0));end entity jg;architecture rt1 of jg issignal indata:std_logic_vector(2 downto 0); beginindata<=c&b&a;process(indata,g1,g2a,g2b)isbeginif(g1='1' and g2a='0' and g2b='0')then case indata iswhen"000"=>y<="11111110"; when"001"=>y<="11111101"; when"010"=>y<="11111011"; when"011"=>y<="11110111"; when"100"=>y<="11101111"; when"101"=>y<="11011111"; when"110"=>y<="10111111"; when"111"=>y<="01111111";when others=>y<="xxxxxxxx";end case;elsey<="11111111";end if;end process;end rt1; 3.同步复位/置位、下降沿触发的d触发器ibrary ieee;use ieee.std_logic_1164.all;entity adff isport(clk,d,r,s:in std_logic;q:out std_logic);end adff;architecture rtl of adff issignal q_temp,qb_temp:std_logic;beginprocess(clk,r,s)beginif(clk'event and clk='0')thenif(r='0' and s='1')thenq_temp<='1';if(r='1' and s='0')thenq_temp<='0';elseq_temp<=d;end if;end if;end if;end process;q<=q_temp;end rtl;4.异步复位/置位、上升沿触发的d发器ibrary ieee;use ieee.std_logic_1164.all;entity adff isport(clk,d,r,s:in std_logic;q:out std_logic);end adff;architecture rtl of adff issignal q_temp,qb_temp:std_logic;beginprocess(clk,r,s)beginif(r='0' and s='1')thenq_temp<='1';elsif(r='1' and s='0')thenq_temp<='0';elsif(clk'event and clk='1')thenq_temp<=d;end if;end process;q<=q_temp;end rtl;5.四分频器ibrary ieee;use ieee.std_logic_1164.all;entity one isport( clk1:in std_logic;clk4:out std_logic);end one;architecture one1 of one issignal data1:integer range 0 to 10;signal q1:std_logic;beginprocess(clk1)beginif rising_edge(clk1) thenif(data1=1) thendata1<=0;q1<=not q1;elsedata1<=data1+1;end if;end if;clk4<=q1;end process;end architecture one1;6.四选一library ieee;use ieee.std_logic_1164.all;entity mux4 isport(input:in std_logic_vector(3 downto 0); a,b:in std_logic;y : out std_logic);end mux4 ;architecture rtl of mux4 issignal sel:std_logic_vector(1 downto 0); beginsel<=b & a;process (input,sel)beginif (sel="00") theny <= input(0);elsif (sel="01") theny <= input(1);elsif (sel="10") theny <= input(2);elsey <= input(3);end if;end process;end rtl; 7.五分频器use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity fenpin5 isport (rst,clkin :in std_logic;clkout:out std_logic);end fenpin5;architecture rtl of fenpin5 issignal count1,count2: std_logic_vector(7 downto 0);signal tmp,tmp1,tmp2: std_logic;begintmp<=tmp1 and tmp2;clkout<=tmp xor tmp1;process(clkin,rst)beginif rst ='1'thencount1 <= "00000000";tmp1<= '0';elsif clkin'event and clkin='1' thenif count1 = "00000100" thencount1 <= "00000000";elsecount1 <= count1 + 1;if count1 < "00000010" thentmp1<= '0';elsetmp1<= '1';end if;end if;end if;end process;end rtl;8.moore状态机library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity moore isport (rst,clk,x:in std_logic; op:out std_logic);end moore;architecture a of moore is type state is (s0,s1,s2,s3); signal st: state;beginstate_comp: process(rst,clk) beginif rst='1' thenst <= s0;elsif rising_edge(clk) then case st iswhen s0 =>if x = '0' thenst <= s0;elsest <= s1;end if;op <= '1';when s1 =>if x = '0' thenst <= s3;elsest <= s2;end if;op <= '1';when s2=>if x = '0' thenst <= s2;elsest <= s3;end if;op <= '1';when s3=>if x = '0' thenst <= s3;elsest <= s0;end if;op <= '0';end case;end if; 9.mealy状态机library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity mealy isport (rst,clk,x:in std_logic; op:out std_logic);end mealy;architecture a of mealy istype state is (s0,s1,s2,s3); signal st : state;beginstate_comp: process(rst,clk) beginif rst='1' thenst <= s0;elsif rising_edge(clk) then case st iswhen s0 =>if x = '0' thenst <= s0; op <= '0';elsest <= s1; op <= '1';end if;when s1 =>if x = '0' thenst <= s3; op <= '1';elsest <= s2; op <= '1';end if;when s2 =>if x = '0' thenst <= s2; op <= '0';elsest <= s3; op <= '1';end if;when s3 =>if x = '0' thenst <= s3; op <= '0';elsest <= s0; op <= '0';end if;end case;end if;end process state_comp;end a10.全加器library ieee;use ieee.std_logic_1164.all;entity full_adder isport (a,b,cin:in std_logic;s,co:out std_logic);end full_adder;architecture full1 of full_adder issignal tmp1,tmp2,tmp3:std_logic;begintmp1 <= a xor b;tmp2 <= a and b;tmp3 <= tmp1 and cin;s <= tmp1 xor cin;co <= tmp2 or tmp3;end full1;11.同步12进制计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity count12en isport (clk,clr, en :in std_logic;qa,qb,qc,qd:out std_logic);end count12en;architecture rtl of count12en issignal count_4:std_logic_vector(3 downto 0); beginqa<=count_4(0);qb<=count_4(1);qc<=count_4(2);qd<=count_4(3);process (clr,clk)beginif(clr='1') thencount_4<="0000";elsif (clk'event and clk ='1') thenif(en='1') thenif (count_4="1011") thencount_4<="0000";elsecount_4<=count_4+'1';end if;end if;end if;end process;end rtl; 12.优先编码器library ieee;use ieee.std_logic_1164.all;entity priority_encoder isport(input:in std_logic_vector(7 downto 0); y : out std_logic_vector(2 downto 0));end priority_encoder;architecture rtl of priority_encoder is beginp1: process (input)beginif ( input(0) ='0') theny <= "111";elsif (input(1) ='0') theny <= "110";elsif (input(2) ='0') theny <= "101";elsif (input(3) ='0') theny <= "100";elsif (input(4) ='0') theny <= "011";elsif (input(5) ='0') theny <= "010";elsif (input(6) ='0') theny <= "001";elsey <= "000";end if;end process p1;end rtl;。

vhdl编程实例

vhdl编程实例VHDL编程实例- 设计与实现一个4位的全加器在本篇文章中,我们将一步一步地回答如何设计和实现一个4位的全加器。

VHDL编程语言将是我们用于描述和模拟这个电路的工具。

第一步:理解全加器的原理在编写代码之前,我们首先需要理解全加器的原理。

全加器是一种用于对两个二进制数字进行相加的电路。

它接收三个输入信号:两个位的输入(A 和B)以及一个进位输入(C_in)。

全加器的输出结果为一个位的和(S)和一个进位输出(C_out)。

我们可以使用如下的真值表来描述全加器的输出结果:输入信号输出结果A B C_in S C_out0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1了解了全加器的工作原理后,我们可以开始编写代码了。

第二步:编写全加器的VHDL代码我们将使用VHDL语言来描述和模拟全加器。

下面是一个简单的4位全加器的VHDL代码实现:vhdlEntity声明entity full_adder isport (A, B : in std_logic_vector(3 downto 0);C_in : in std_logic;S : out std_logic_vector(3 downto 0);C_out : out std_logic);end full_adder;Architecture声明architecture Behavioral of full_adder isbeginprocess(A, B, C_in)variable carry : std_logic;begincarry := C_in;for i in 0 to 3 loopS(i) <= A(i) xor B(i) xor carry;carry := (A(i) and B(i)) or (carry and (A(i) xor B(i)));end loop;C_out <= carry;end process;end Behavioral;在此代码中,我们首先声明了一个实体(entity)和一个架构(architecture)。

数字逻辑实验程序VHDL

实验一:半加器--底层的异或门library IEEE;use IEEE.std_logic_1164.all;entity xor_gate isport( a1,a2 : in std_logic;xor_out : out std_logic); end entity;architecture behav1 of xor_gate is beginxor_out <=a1 xor a2;end behav1;--底层的与门library IEEE;use IEEE.std_logic_1164.all;entity and_gate isport( a1,a2 : in std_logic;and_out : out std_logic); end entity;architecture behav1 of and_gate is beginand_out <=a1 and a2;end behav1;--顶层的设计实体library IEEE;use IEEE.std_logic_1164.all;entity half_adder isport( ai,bi : in std_logic;so,co : out std_logic); end entity;architecture struct2 of half_adder is component xor_gateport( a1,a2 : in std_logic;xor_out : out std_logic); end component;component and_gateport( a1,a2 : in std_logic;and_out : out std_logic); end component;beging1: xor_gate port map(a1=> ai, a2=> bi, xor_out=> so);--对异或门的例化g2: and_gate port map(a1=> ai, a2=> bi, and_out=> co);--对与门的例化end struct2;实验二:加法器--底层的异或门library IEEE;use IEEE.std_logic_1164.all;entity xor_gate isport( a1,a2 : in std_logic;xor_out : out std_logic);end entity;architecture behav1 of xor_gate isbeginxor_out <=a1 xor a2;end behav1;--底层的与门library IEEE;use IEEE.std_logic_1164.all;entity and_gate isport( a1,a2 : in std_logic;and_out : out std_logic);end entity;architecture behav1 of and_gate isbeginand_out <=a1 and a2;end behav1;--顶层的设计实体library IEEE;use IEEE.std_logic_1164.all;entity half_adder isport( ai,bi : in std_logic;so,co : out std_logic);end entity;architecture struct2 of half_adder iscomponent xor_gateport( a1,a2 : in std_logic;xor_out : out std_logic);end component;component and_gateport( a1,a2 : in std_logic;and_out : out std_logic);end component;beging1: xor_gate port map(a1=> ai, a2=> bi, xor_out=> so);--对异或门的例化g2: and_gate port map(a1=> ai, a2=> bi, and_out=> co);--对与门的例化end struct2;实验三:--底层的异或门library IEEE;use IEEE.std_logic_1164.all;entity xor_gate isport( a1,a2 : in std_logic;xor_out : out std_logic);end entity;architecture behav1 of xor_gate isbeginxor_out <=a1 xor a2;end behav1;--底层的与门library IEEE;use IEEE.std_logic_1164.all;entity and_gate isport( a1,a2 : in std_logic;and_out : out std_logic);end entity;architecture behav1 of and_gate isbeginand_out <=a1 and a2;end behav1;--顶层的设计实体library IEEE;use IEEE.std_logic_1164.all;entity half_adder isport( ai,bi : in std_logic;so,co : out std_logic);end entity;architecture struct2 of half_adder iscomponent xor_gateport( a1,a2 : in std_logic;xor_out : out std_logic);end component;component and_gateport( a1,a2 : in std_logic;and_out : out std_logic);end component;beging1: xor_gate port map(a1=> ai, a2=> bi, xor_out=> so);--对异或门的例化g2: and_gate port map(a1=> ai, a2=> bi, and_out=> co);--对与门的例化end struct2;实验四:自动售饮料机library ieee;use ieee.std_logic_1164.all;entity drinker isport(clk,rst:in std_logic;--clk时钟信号,rst复位x:in std_logic_vector(1 downto 0);--两个输入c:out std_logic_vector(1 downto 0)--两个输出);end drinker;architecture behave of drinker istype states is (s0,s1,s2);--自定义类型signal state:states;beginprocess (clk,rst)beginif rst='1' then state<=s0;--异步复位成初始状态s0c<="00";--初始输出为00elsif (clk' event and clk ='1') then --时钟上升沿case state iswhen s0=>--当状态为s0时if x="01" then --如果输入为01state<=s1;c<="00";--输出为00elsifx="10" then state<=s2;c<="00";elsestate<=s0; c<="00";--当输入为00或是约束的状态则保持原来的状态不变end if;when s1=>--当状态为s1时if x="01" thenstate<=s2;c<="00";elsifx="10" then --输入为10state<=s0;c<="10";--输出为10,状态变为s0elsestate<=s1; c<="00";--当输入为00或是约束的状态则保持原来的状态不变end if;when s2=>if x="01" thenstate<=s0;c<="10";elsifx="10" thenstate<=s0;c<="11";elsestate<=s2; c<="00";--当输入为00或是约束的状态则保持原来的状态不变end if;end case;end if;end process;end behave;。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.三与门library ieee;use ieee.std_logic_1164.all;entity yumen isport(a,b,c : in std_logic;f : out std_logic);end yumen;architecture and3_1 of yumen isbeginf<=a and b and c;end architecture and3_1;2.三八译码器library ieee;use ieee.std_logic_1164.all;entity jg isport(a,b,c,g1,g2a,g2b:in std_logic;y:out std_logic_vector(7 downto 0));end entity jg;architecture rt1 of jg issignal indata:std_logic_vector(2 downto 0); beginindata<=c&b&a;process(indata,g1,g2a,g2b)isbeginif(g1='1' and g2a='0' and g2b='0')then case indata iswhen"000"=>y<="11111110"; when"001"=>y<="11111101"; when"010"=>y<="11111011"; when"011"=>y<="11110111"; when"100"=>y<="11101111"; when"101"=>y<="11011111"; when"110"=>y<="10111111"; when"111"=>y<="01111111";when others=>y<="xxxxxxxx";end case;elsey<="11111111";end if;end process;end rt1; 3.同步复位/置位、下降沿触发的d触发器ibrary ieee;use ieee.std_logic_1164.all;entity adff isport(clk,d,r,s:in std_logic;q:out std_logic);end adff;architecture rtl of adff issignal q_temp,qb_temp:std_logic;beginprocess(clk,r,s)beginif(clk'event and clk='0')thenif(r='0' and s='1')thenq_temp<='1';if(r='1' and s='0')thenq_temp<='0';elseq_temp<=d;end if;end if;end if;end process;q<=q_temp;end rtl;4.异步复位/置位、上升沿触发的d发器ibrary ieee;use ieee.std_logic_1164.all;entity adff isport(clk,d,r,s:in std_logic;q:out std_logic);end adff;architecture rtl of adff issignal q_temp,qb_temp:std_logic;beginprocess(clk,r,s)beginif(r='0' and s='1')thenq_temp<='1';elsif(r='1' and s='0')thenq_temp<='0';elsif(clk'event and clk='1')thenq_temp<=d;end if;end process;q<=q_temp;end rtl;5.四分频器ibrary ieee;use ieee.std_logic_1164.all;entity one isport( clk1:in std_logic;clk4:out std_logic);end one;architecture one1 of one issignal data1:integer range 0 to 10;signal q1:std_logic;beginprocess(clk1)beginif rising_edge(clk1) thenif(data1=1) thendata1<=0;q1<=not q1;elsedata1<=data1+1;end if;end if;clk4<=q1;end process;end architecture one1;6.四选一library ieee;use ieee.std_logic_1164.all;entity mux4 isport(input:in std_logic_vector(3 downto 0); a,b:in std_logic;y : out std_logic);end mux4 ;architecture rtl of mux4 issignal sel:std_logic_vector(1 downto 0); beginsel<=b & a;process (input,sel)beginif (sel="00") theny <= input(0);elsif (sel="01") theny <= input(1);elsif (sel="10") theny <= input(2);elsey <= input(3);end if;end process;end rtl; 7.五分频器use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity fenpin5 isport (rst,clkin :in std_logic;clkout:out std_logic);end fenpin5;architecture rtl of fenpin5 issignal count1,count2: std_logic_vector(7 downto 0);signal tmp,tmp1,tmp2: std_logic;begintmp<=tmp1 and tmp2;clkout<=tmp xor tmp1;process(clkin,rst)beginif rst ='1'thencount1 <= "00000000";tmp1<= '0';elsif clkin'event and clkin='1' thenif count1 = "00000100" thencount1 <= "00000000";elsecount1 <= count1 + 1;if count1 < "00000010" thentmp1<= '0';elsetmp1<= '1';end if;end if;end if;end process;end rtl;8.moore状态机library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity moore isport (rst,clk,x:in std_logic; op:out std_logic);end moore;architecture a of moore is type state is (s0,s1,s2,s3); signal st: state;beginstate_comp: process(rst,clk) beginif rst='1' thenst <= s0;elsif rising_edge(clk) then case st iswhen s0 =>if x = '0' thenst <= s0;elsest <= s1;end if;op <= '1';when s1 =>if x = '0' thenst <= s3;elsest <= s2;end if;op <= '1';when s2=>if x = '0' thenst <= s2;elsest <= s3;end if;op <= '1';when s3=>if x = '0' thenst <= s3;elsest <= s0;end if;op <= '0';end case;end if; 9.mealy状态机library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity mealy isport (rst,clk,x:in std_logic; op:out std_logic);end mealy;architecture a of mealy istype state is (s0,s1,s2,s3); signal st : state;beginstate_comp: process(rst,clk) beginif rst='1' thenst <= s0;elsif rising_edge(clk) then case st iswhen s0 =>if x = '0' thenst <= s0; op <= '0';elsest <= s1; op <= '1';end if;when s1 =>if x = '0' thenst <= s3; op <= '1';elsest <= s2; op <= '1';end if;when s2 =>if x = '0' thenst <= s2; op <= '0';elsest <= s3; op <= '1';end if;when s3 =>if x = '0' thenst <= s3; op <= '0';elsest <= s0; op <= '0';end if;end case;end if;end process state_comp;end a10.全加器library ieee;use ieee.std_logic_1164.all;entity full_adder isport (a,b,cin:in std_logic;s,co:out std_logic);end full_adder;architecture full1 of full_adder issignal tmp1,tmp2,tmp3:std_logic;begintmp1 <= a xor b;tmp2 <= a and b;tmp3 <= tmp1 and cin;s <= tmp1 xor cin;co <= tmp2 or tmp3;end full1;11.同步12进制计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity count12en isport (clk,clr, en :in std_logic;qa,qb,qc,qd:out std_logic);end count12en;architecture rtl of count12en issignal count_4:std_logic_vector(3 downto 0); beginqa<=count_4(0);qb<=count_4(1);qc<=count_4(2);qd<=count_4(3);process (clr,clk)beginif(clr='1') thencount_4<="0000";elsif (clk'event and clk ='1') thenif(en='1') thenif (count_4="1011") thencount_4<="0000";elsecount_4<=count_4+'1';end if;end if;end if;end process;end rtl; 12.优先编码器library ieee;use ieee.std_logic_1164.all;entity priority_encoder isport(input:in std_logic_vector(7 downto 0); y : out std_logic_vector(2 downto 0));end priority_encoder;architecture rtl of priority_encoder is beginp1: process (input)beginif ( input(0) ='0') theny <= "111";elsif (input(1) ='0') theny <= "110";elsif (input(2) ='0') theny <= "101";elsif (input(3) ='0') theny <= "100";elsif (input(4) ='0') theny <= "011";elsif (input(5) ='0') theny <= "010";elsif (input(6) ='0') theny <= "001";elsey <= "000";end if;end process p1;end rtl;。