vhdl基本语法 ifdef

8.VHDL基本语句和函数

4)

格式

IF

条件1 THEN 条件1 顺序语句1 顺序语句1; 条件2 ELSIF 条件2 THEN 顺序语句2 顺序语句2; …… 条件n ELSIF 条件n THEN 顺序语句n; 顺序语句n; ELSE 顺序语句n+1; 顺序语句n+1; IF; END IF;

注意

这类语句可以实现不同类型电路的描述。 这类语句可以实现不同类型电路的描述。 其任一分支顺序语句的执行条件是以上各分支 条件相与, 条件相与,即语句中顺序语句的执行条件具有 向上相与的功能。 向上相与的功能。

注意ቤተ መጻሕፍቲ ባይዱ

•条件句中的选择值必须在表达式的取值范围内; 条件句中的选择值必须在表达式的取值范围内; 条件句中的选择值必须在表达式的取值范围内 •CASE语句中每一条件句的选择只能出现一次,相同 CASE语句中每一条件句的选择只能出现一次 CASE语句中每一条件句的选择只能出现一次, 选择值的条件语句不能重复出现; 选择值的条件语句不能重复出现; •所有表达式的值都必须穷举,不能穷举的值用 所有表达式的值都必须穷举, 所有表达式的值都必须穷举 OTHERS表示 表示。 OTHERS表示。

Library ieee; use ieee.std_logic_1164.all; entity test_06 is port( d: in std_logic; x: out std_logic); end test_06; architecture test_06 of test_06 is signal a: std_logic_vector(3 downto 0); signal b: std_logic_vector(2 downto 0); begin process begin a<="1010"; b<="111"; if(a>b) then x<=d; else x<='0'; end if; end process; end test_06;

VHDL基本语句

例

ARCHITECTURE example OF mux4 IS BEGIN PROCESS (sel) 注 BEGIN ●CASE中的选择值必须在表达式的取值范围内; CASE sel IS WHEN 0=> q <= d0 ; ●CASE语句是无序的,所有表达式值都是并行 WHEN 1=> q <= d1 ; 处理;而IF语句是有序的,最起始、最优先 WHEN 2=> q<= d3 ; WHEN 3=> q<= d4 ; 的先处理; WHEN others => NULL; ●可以有很多分支,但OTHERS分支只能有一个, END CASE; 且只能位于最后;用来使所有选择值能涵盖表 END PROCESS; END example; 达式的所有取值,以免插入不必要的锁存器

3、用于多选控制的IF语句:

格式 IF 条件1 THEN

<顺序处理语句1>;

ELSIF 条件2 THEN <顺序处理语句2>; : ELSIF 条件n-1 THEN <顺序处理语句n-1>; ELSE <顺序处理语句n>; END IF;

P1: PROCESS (clk) BEGIN

IF (clk‘ event and clk=‗1‘ ) THEN

顺序语句

赋值语句

VHDL设计实体内的数据传递以及对端口界面外部数据的读写 都必须通过赋值语句的运行来实现。 功能是将一个值或表达式的运算结果传递给某一数据对象。 赋值语句有两种: 信号赋值语句和变量赋值语句 区别

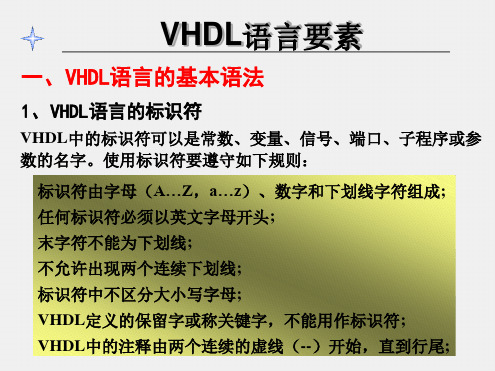

VHDL语言的基本语法

B:二进制基数符号,表示二进制数位0或1。 二进制基数符号,表示二进制数位0 O:八进制基数符号。 八进制基数符号。 X:十六进制基数符号(0~F) 。 十六进制基数符号(0~ (0 例如: 1_1101_1110 1_1101_1110” 例如:B“1_1101_1110 --二进制数数组,位矢数组长度是9 --二进制数数组,位矢数组长度是9 二进制数数组 AD0 X“AD0” AD --十六进制数数组,位矢数组长度是12 --十六进制数数组,位矢数组长度是12 十六进制数数组

4、下标名及下标段名 下标名用于指示数组型变量或信号的某一 下标名用于指示数组型变量或信号的某一 元素, 元素,如:a(2) , b(n) 下标段名则用于指示数组型变量或信号的 下标段名则用于指示数组型变量或信号的 某一段元素,其语句格式如下: 某一段元素,其语句格式如下:

数组类型信号名或变量名(表达式 表达式2]); 数组类型信号名或变量名 表达式1 [TO/DOWNTO 表达式 ; 表达式

信号的使用和定义范围是实体、结构体和程序包 信号的使用和定义范围是实体、结构体和程序包.

在程序中: 在程序中 (1) 信号值的代入采用“<=”代入符,而且信号 信号值的代入采用“ ”代入符, 代入时可以附加延时。 代入时可以附加延时。 (2) 变量赋值时用“:=”,不可附加延时。 变量赋值时用“ ” 不可附加延时。 (3) 信号的初始赋值符号仍是“:=”。 信号的初始赋值符号仍是“ ” 例: X<=Y AFTER 10 ns; ; --X,Y都是信号,且Y的值经过 都是信号, 的值经过10ns延 , 都是信号 的值经过 延 时以后才被代入X。 时以后才被代入 。

(1) 赋值语句右方的表达式必须是一个与目标变量有相同 数据类型的数值。 数据类型的数值。 (2) 变量不能用于硬件连线和存储元件。 变量不能用于硬件连线和存储元件。 (3) 变量的适用范围仅限于定义了变量的进程或子程序中。 变量的适用范围仅限于定义了变量的进程或子程序中。 (4) 若将变量用于进程之外,必须将该值赋给一个相同的 若将变量用于进程之外, 类型的信号,即进程之间传递数据靠的是信号。 类型的信号,即进程之间传递数据靠的是信号。

VHDL语言的基本语法解析

2、变量( Variable )

变量是一个局部变量,它只能在进程语句、函数语句和过程 语句结构中使用,用作局部数据存储。变量常用在实现某种算 法的赋值语句中。

一般格式:

VARIABLE 变量名:数据类型 约束条件:= 表达式;

例: VARIABLE x, y: INTEGER;

--定义x,y为整数变量

SIGNAL Y ,Z :BIT;

Y<=A(M) ;

--M是不可计算型下标表示

Z<=B(3) ;

--3是可计算型下标表示

C (0 TO 3)<=A (4 TO 7) ; -以段的方式进行赋值

C (4 TO 7)<=A (0 TO 3) ; -以段的方式进行赋值

二、VHDL语言的数据对象

1、常数( Constant )

常量的使用范围取决于它被定义的位置 :

(1)程序包中定义的常量具有最大的全局化特性,可以用在调 用此程序包的所有设计实体中;

(2)设计实体中定义的常量,其有效范围为这个实体定义的所 有的结构体;

(3)设计实体中某一结构体中定义的常量只能用于此结构体;

(4)结构体中某一单元定义的常量,如一个进程中,这个常量 只能用在这一进程中。

5,678,0,156E2(=15600) , 45_234_287(=45234287)

(2) 实数文字: 实数文字也都是十进制的数,但必 须带有小数点,如: 188.993, 88_670_551.453_909(=88670551.453909) ,

1.0,44.99E-2(=0.4499) ,1.335,0.0

?16#F.01#E+2ቤተ መጻሕፍቲ ባይዱ--( 十六进制数表示,等于 3841.00)

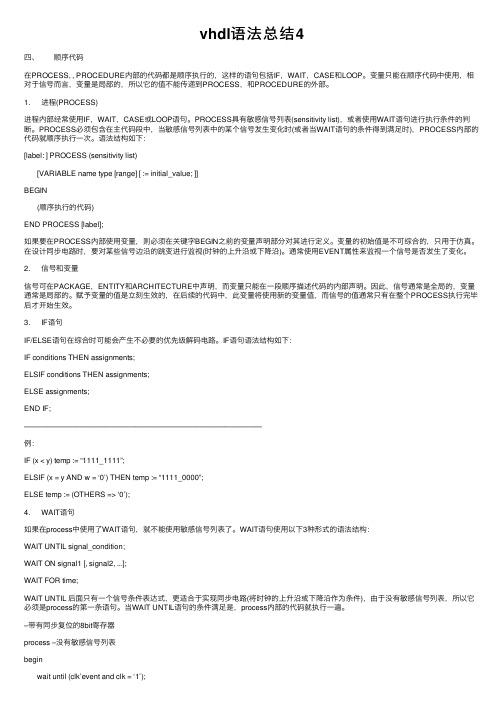

vhdl语法总结4

vhdl语法总结4四、顺序代码在PROCESS, , PROCEDURE内部的代码都是顺序执⾏的,这样的语句包括IF,WAIT,CASE和LOOP。

变量只能在顺序代码中使⽤,相对于信号⽽⾔,变量是局部的,所以它的值不能传递到PROCESS,和PROCEDURE的外部。

1. 进程(PROCESS)进程内部经常使⽤IF,WAIT,CASE或LOOP语句。

PROCESS具有敏感信号列表(sensitivity list),或者使⽤WAIT语句进⾏执⾏条件的判断。

PROCESS必须包含在主代码段中,当敏感信号列表中的某个信号发⽣变化时(或者当WAIT语句的条件得到满⾜时),PROCESS内部的代码就顺序执⾏⼀次。

语法结构如下:[label: ] PROCESS (sensitivity list)[VARIABLE name type [range] [ := initial_value; ]]BEGIN(顺序执⾏的代码)END PROCESS [label];如果要在PROCESS内部使⽤变量,则必须在关键字BEGIN之前的变量声明部分对其进⾏定义。

变量的初始值是不可综合的,只⽤于仿真。

在设计同步电路时,要对某些信号边沿的跳变进⾏监视(时钟的上升沿或下降沿)。

通常使⽤EVENT属性来监视⼀个信号是否发⽣了变化。

2. 信号和变量信号可在PACKAGE,ENTITY和ARCHITECTURE中声明,⽽变量只能在⼀段顺序描述代码的内部声明。

因此,信号通常是全局的,变量通常是局部的。

赋予变量的值是⽴刻⽣效的,在后续的代码中,此变量将使⽤新的变量值,⽽信号的值通常只有在整个PROCESS执⾏完毕后才开始⽣效。

3. IF语句IF/ELSE语句在综合时可能会产⽣不必要的优先级解码电路。

IF语句语法结构如下:IF conditions THEN assignments;ELSIF conditions THEN assignments;ELSE assignments;END IF;————————————————————————————————例:IF (x < y) temp := “1111_1111”;ELSIF (x = y AND w = ‘0’) THEN temp := “1111_0000”;ELSE temp := (OTHERS => ‘0’);4. WAIT语句如果在process中使⽤了WAIT语句,就不能使⽤敏感信号列表了。

vhdl if else语句

vhdl if else语句

VHDL

(VeryHigh-SpeedIntegratedCircuitHardwareDescriptionLanguag e)是一种硬件描述语言,它可以用来描述数字电路的行为。

if-else 语句是VHDL中常用的条件语句。

它用于根据一个条件是否成立来执

行不同的操作,语法如下:

if condition_1 then

--执行操作1

elsif condition_2 then

--执行操作2

else

--执行操作3

end if;

其中,condition_1是一个布尔表达式,如果它的值为TRUE,就执行第一个操作;如果值为FALSE,则继续判断condition_2,如果

它的值为TRUE,则执行第二个操作;如果condition_2的值也为FALSE,则执行第三个操作。

在VHDL中,if-else语句也可以嵌套使用,以实现更复杂的条

件判断。

在使用if-else语句时,需要注意以下几点:

1. 条件表达式必须是布尔型的,即只能取TRUE或FALSE两个值。

2. 在每个条件分支中,必须有且仅有一个操作被执行。

3. else语句是可选的,如果没有else语句,则当所有条件都

不成立时,不会执行任何操作。

4. 在VHDL中,if-else语句可以与选择语句(case语句)结合使用,以实现更灵活的条件判断。

总之,if-else语句是VHDL中常用的条件语句,用于根据一个条件是否成立来执行不同的操作。

要使用if-else语句,需要熟悉它的语法和注意事项。

第10章VHDL基本语句

END LOOP L2; ...

11

11

10.1.4 LOOP语句

(2) FOR_LOOP语句,语法格式如下: [LOOP标号:] FOR 循环变量 IN 循环次数范围 顺序语句

LOOP

END LOOP [LOOP标号];

SIGNAL tmp :STD_LOGIC ;

BEGIN

奇校验就是看2进制数旳1旳个数为奇数

PROCESS(a)

就在校验位填0 偶数就填1 使1旳个数

BEGIN

变成奇数个. 偶校验相反 把1旳个数变

tmp <='0';

成偶数.

FOR n IN 0 TO 7 LOOP 然后传送数据,接受后在做相应旳奇偶

FOR后旳”循环变量”是一种临时变量,属LOOP语句旳局 部变量,不必事先定义. 这个变量只能作为赋值源,不能被赋值,它 由LOOP语句自动定义. 使用时应该注意,在LOOP语句范围内不 要再使用其他与此循环变量同名旳标识符.

“循环次数范围”要求LOOP语句中旳顺序语句被执行次数. 循环变量从范围初值开始,每执行完一次顺序增1,直至最大值.

第 10 章 VHDL基本语句

1

1

10.1 顺序语句

VHDL有6种基本顺序语句:赋值语句、流程控制语句、等待 语句、子程序调用语句、返回语句、空操作语句.

10.1.1 赋值语句

信号赋值语句

10.1.2 IF语句

10.1.3 CASE语句

变量赋值语句

多条件选择

值体现式旳 4种形式

单个一般数值,如6。

数值选择范围,如(2 TO 4)。

第03章 VHDL语法基础

VARIABLE tmp:STD_LOGIC

16

第3章 VHDL语法基础

BEGIN

tmp:=„0‟;

FOR i IN 0 TO 7 LOOP tmp:= tmp XOR a(i);

END LOOP;

y <= tmp; END PROCESS;

END rtl;

17

第3章 VHDL语法基础

3、WHILE-LOOP语句

13

第3章 VHDL语法基础

三、LOOP语句

LOOP语句就是循环语句,它可以使包含的一组顺序语句 被循环执行,其执行的次数受迭代算法控制。在VHDL中常用 来描述迭代电路的行为。 1、单个LOOP语句 单个LOOP语句的书写格式如下: [标号:] LOOP 顺序语句

END LOOP[标号];

14

第3章 VHDL语法基础

这种循环语句需引入其他控制语句(如EXIT)后才能确定, 否则为无限循环。其中的标号是可选的。 例如:

loop1:LOOP

WAIT UNTIL clk=„1‟; q <= d AFTER 2 ns;

END LOOP loop1;

2、FOR-LOOP语句 [标号:] FOR 循环变量 IN 离散范围 LOOP 顺序处理语句

LIBRARY IEEE; USE IEEE. STD_LOGIC_1164.ALL; ENTITY dff IS PORT(clk,d:IN STD_LOGIC;

q:OUT STD_LOGIC);

END dff;

ARCHITECTURE rtl OF dff IS BEGIN PROCESS (clk) BEGIN IF (clk‟EVENT AND clk=‟1‟) THEN q <= d; END IF; END PROCESS; END rtl; 3

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统。

它是由美国国防部(DOD)于20

世纪80年代初期的VHSIC(Very High Speed Integrated Circuits)项目中开发的。

VHDL的基本语法包括一些常用的关键字和结构,其

中ifdef是其中之一。

ifdef是VHDL中的一个条件编译指令,用于根据给定的条件来判断是否包含某段代码。

在VHDL中,ifdef语句的基本语法如下:

```vhdl

`ifdef condition

-- code to be included if condition is true

`else

-- code to be included if condition is false

`endif

```

在上面的代码中,condition是一个条件表达式,可以是一个参数、宏定义或者其他已经定义过的条件。

如果condition为真,则会编译

`ifdef和`endif之间的代码;如果condition为假,则会编译`else和

`endif之间的代码。

使用ifdef可以让我们根据不同的条件来控制代码的编译和包含,这在

一些复杂的项目中非常有用。

下面是使用ifdef的一个简单示例:

```vhdl

`ifdef DEBUG

report "Debug mode is enabled";

`else

report "Debug mode is disabled";

`endif

```

在上面的代码中,如果DEBUG宏被定义了,那么report语句"Debug mode is enabled"将被编译进去;否则将编译进去"Debug mode is disabled"。

除了`ifdef语句外,VHDL还提供了一些其他的条件编译指令,如

`ifndef(如果给定条件为假则编译)、`elsif(如果前面的条件为假则

继续判断下一个条件)、`elsif和`endif。

VHDL中的`ifdef语句能够帮助我们根据条件来控制代码的包含和编译,从而使代码更具有灵活性和可维护性。

当我们需要根据不同的条件来

进行调试、测试或者生产部署时,ifdef可以提供一种简洁而有效的方式来处理这些情况。

在VHDL中合理地使用ifdef语句可以提高代码

的可读性和可维护性,是VHDL程序设计中的一个重要技巧。