脉冲信号发生器设计

一种短脉冲宽度的CW信号发生器的设计

ms ,滤波 器 也不用 修改 ,只须修 改单 片机程 序 ,将 信 号 的方波 数适 当增 加 ,使模拟 开 关导通 时带 通

图 4模拟开关与隔离级

3实验结果与结论

实验 结 果 表 明 本 电路 可产 生上 升 及 下 降沿 非 以频率 准确 度较 高 ,脉 宽 与发射 周期 也 比较准

以采用 较普 通 的模拟 开关 。

器 的输 出只有约 04ms . 有信 号 , 余 时间输 出均 为 其

m s

1 0 2

图 1发 射 信 号 波 形 示 意 图

图 2 信 号 产生 电路 框 图

O00 u . 0s

1 00u . s 0

2 .u 00O s

30 .us 00

单 片机采 用 A 8 C 0 1 T 9 2 5 ,其 内部有 2 B 可编 K 程 Fah存储 器 ( ls 可擦 写 1 0 0 0次 ) ,不 需外部 扩展 程序 存储 器 , 积 比 A 8 C 1 体 T 9 5 小很 多 , 用十 分方 使

便。

图 3 带 通滤 波 器

信号 和 信号 D 分别从 A 8 C 0 1的端 口 T 9 25 P . P . 输 出,P .、P . 12和 13 1 2 1 3均有 内部 上拉 电阻 , 输 出 时不 需外接 上拉 电 阻。电路 较 简单 , 不再 给 出 。 带 通 有 源 滤 波 器 采 用 无 限 增 益 多 环 反 馈 型 二 阶 带通 有源 滤波 器 。如 图 3所 示 。

在 本 文 中 , 取 冠 =足 =R =6 k , OQ

=

c =4 0 F, R = 8 4 7p 2 10Q,按 照上 面 的 公 式计

算 ,带 宽 B 约 为 1 k ,中心频 率为 1 1 Hz W 0 Hz 0 。 k

单片机 低频脉冲信号发生器 设计报告

低频脉冲信号发生器“低频脉冲信号发生器”功能:在P1.0引脚输出低频脉冲信号,脉冲信号的频率可以通过键盘设定,输出的脉冲频率在6位数码管显示。

在程序执行过程中,读取键盘设置,根据设置改变输出频率,根据脉冲频率计算定时周期,使用定时器产生定时中断,在中断服务程序中对P1.0取反(cpl P1.0),产生脉冲。

编写数码管显示程序,完成频率显示。

MCS-51单片机内部有2个定时/计数器,当工作在定时器模式时,可以对时钟的12分频计数,实现准确定时。

利用定时器的周期中断,就可以实现在P1.0上产生脉冲波。

单片机实验开发系统上提供了键盘,在程序执行过程中,读取键盘状态,根据状态值改变定时器的定时周期,就可以实现改变输出频率。

单片机实验开发系统上数码管显示采用8155的PB、PC口控制的动态扫描方式,共6位数码管。

编写一个通用的数码管显示驱动程序,在每一次定时器中断中显示一位数码,6个定时器中断周期完成扫描,只要保证扫描周期<20ms,就可以稳定显示。

程序中各功能模块如下所示:程序清单如下:ORG 0000HMOV R1,#50HAJMP MAINORG 000BHAJMP TC0S ;转到T/C0的中断TC0SMAIN: MOV TMOD,#00H ;置T/C0为方式0,定时MOV TH0,#0E0HMOV TL0,#18HSETB ET0 ;T/C0允许中断SETB EA ;CPU开中断SETB TR0 ;启动T/C0定时HERE: SJMP HERE ;等待中断ORG 0150HTC0S: MOV TH0,#0E0HMOV TL0,#18HCPL P1.0 ;输出方波START: MOV DPTR,#0FF20HMOV A,#03HMOVX @DPTR,A ;设定状态字MOV 70H,#00HKEY1: ACALL KS1 ;跳至KS1,扫描是否有键闭合JNZ LK1 ;有键闭合跳至LK1N1: ACALL DIRAJMP KEY1 ;转到KEY1,继续扫描是否有闭合键LK1: ACALL DIRACALL DIRACALL KS1 ;转到KS1,扫描闭合键是否为波动JNZ LK2 ;键不是波动,跳至LK2判断键号ACALL DIRAJMP KEY1LK2: MOV R2,#0FEH ;列扫描码送到R2MOV R4,#00H ;R4是列数的计数单元LK4: MOV DPTR,#0FF21HMOV A,R2MOVX @DPTR,A ;列扫描码送到PA口INC DPTRINC DPTRMOVX A,@DPTR ;读PC口JB ACC.0,LONE ;第零行为高电平,转到第一行MOV A,#00H ;第零行为低电平,行首健号送到AAJMP LKP ;转到LKP,计算键号LONE: JB ACC.1,LTWOMOV A,#08HAJMP LKPLTWO: JB ACC.2,LTHRMOV A,#10HAJMP LKPLTHR: JB ACC.3,LFORMOV A,#18HSJMP LKPLFOR: JB ACC.4,NEXTMOV 70H,#19H ;“19号键”为确认键AJMP KEY2 ;转到KEY2,将输入值给TL0&TH0赋值LKP: ADD A,R4 ;行首键号+列号=键号MOV @R1,AINC R1MOV 70H,A ;将键号送入70H单元PUSH ACC ;键号压入堆栈LK3: ACALL DIRACALL KS1 ;进行第二次扫描JNZ LK3 ;有键闭合,返回LK3POP ACCAJMP KEY1NEXT: INC R4 ;第一行没有键闭合,进行第二列的扫描MOV A,R2 ;列扫描码送到A中JNB ACC.7,KND ;全部列扫描完成,跳到KND进行下一轮扫描RL A ;列扫描码向后移一位MOV R2,A ;列扫描码送回R2AJMP LK4KND: AJMP KEY1KS1: MOV DPTR,#0FF21H ;PA口地址0FF21HMOV A,#00HMOVX @DPTR,AINC DPTR ;转到PC口,地址0FF23HINC DPTRMOVX A,@DPTR ;读键入状态CPL A ;键入状态取反ANL A,#0FH ;屏蔽键入状态高四位RETDIR: MOV R0,#70H ;键值放入R0MOV A,@R0ANL A,#0FH ;屏蔽键值高四位MOV 30H,AMOV A,@R0SW AP AANL A,#0FH ;屏蔽键值高四位MOV 31H,AMOV R0,#30HMOV R3,#01HDO1: MOV A,R3MOV DPTR,#0FF21HMOVX @DPTR,AINC DPTRMOV A,@R0ADD A,#0DH ;计算偏移量MOVC A,@A+PC ;查表得出相应的键值DIR1: MOVX @DPTR,AACALL DL1MOV A,R3RL AJB ACC.2,LD1MOV R3,AINC R0AJMP DO1LD1: RETDSEH: DB 0C0H,0F9H,0A4H,0B0H,99H,92H,82H,0F8HDB 80H,90H,88H,83H,0C6H,0A1H,086H,08EH,0FFH,0C0HDL1: MOV R7,#2DL: MOV R6,#0FFHDL6: DJNZ R6,DL6DJNZ R7,DLRETKEY2: MOV B,50H ;将输入值给B,A,并合并存在A中MOV A,51HSW AP AANL A,BMOV TL0,A ;低位赋给TL0MOV 40H,A ;保存以备后用MOV B,52HMOV A,53HSW AP AANL A,BMOV TH0,A ;高位赋给TH0MOV 41H,AEND改进方案:本程序为了方便输入的是计时初值而非频率,可以尝试使用频率,然后编写一个多位除法的程序。

555脉冲发生器电路图大全(六款555脉冲发生器电路设计原理图详解)

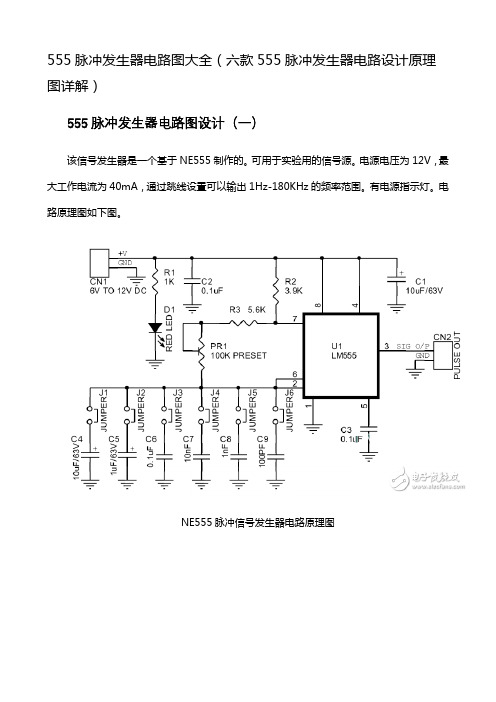

555脉冲发生器电路图大全(六款555脉冲发生器电路设计原理图详解)555脉冲发生器电路图设计(一)该信号发生器是一个基于NE555制作的。

可用于实验用的信号源。

电源电压为12V,最大工作电流为40mA,通过跳线设置可以输出1Hz-180KHz的频率范围。

有电源指示灯。

电路原理图如下图。

NE555脉冲信号发生器电路原理图信号发生器跳线帽设置频率元件清单PCB图555脉冲发生器电路图设计(二)时钟脉冲发生器555组成的多谐振荡器可以用作各种时钟脉冲发生器,如图所示,其中(1)为脉冲频率可调的矩形脉冲发生器,改变电容C可获得超长时间的低频脉冲,调节电位器RP可得到任意频率的脉冲如秒脉冲,1KHz,10KHz等标准脉冲。

由于电容C的充放电回路时间常数不相等,所以图(1)所示电路的输出波形为矩形脉冲,矩形脉冲的占空比随频率的变化而变化。

图(2)所示电路为占空比可调的时钟脉冲发生器,接入两只二极管D1,D2后,电容C 的充放电回路分开。

放电回路为D2,R,内部三极管T及电容C,放电时间T1约等于0.7RC。

充电回路为R’,D1,C,充电时间为T2约等于0.7R’C。

输出脉冲的频率f=1.43/[(R+R’)C]调节电位器RP可以改变输出脉冲的占空比,但频率不变。

如果使R=R’则可获得对称方波。

(1)矩形脉冲发生器(2)占空比可调的脉冲发生器555脉冲发生器电路图设计(三)闸门脉冲发生器(555)电路图555脉冲发生器电路图设计(四)PWM(脉冲宽度调制)是电子技术领域中一项重要的技术,在许多设备中都有PWM的应用,比如电机控制、照明控制等场合。

在没有单片机的场合,如果需要应用PWM,可以使用NE555芯片生成所需的PWM信号。

脉宽调制的占空比:PWM信号保持在高电平的时间百分比被称为占空比。

占空比脉宽调制的频率:PWM信号的频率决定PWM完成一个周期的速度。

如果LED关闭半秒,然后打开LED半秒,那么看起来LED是闪烁的。

单片机控制低频脉冲信号发生器的设计

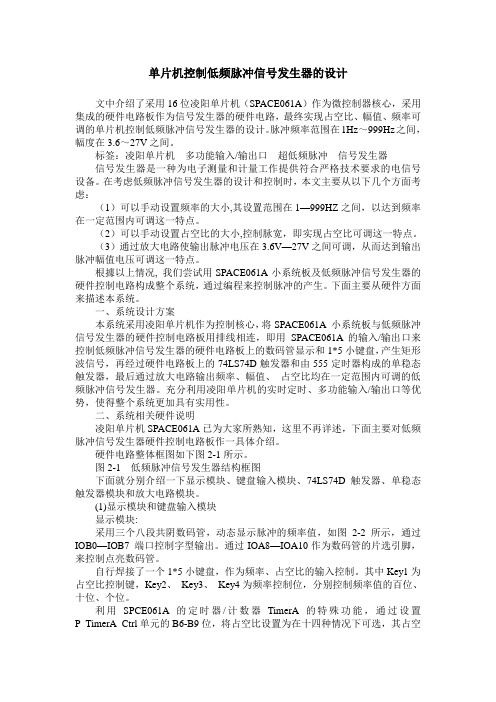

单片机控制低频脉冲信号发生器的设计文中介绍了采用16位凌阳单片机(SPACE061A)作为微控制器核心,采用集成的硬件电路板作为信号发生器的硬件电路,最终实现占空比、幅值、频率可调的单片机控制低频脉冲信号发生器的设计。

脉冲频率范围在1Hz~999Hz之间,幅度在3.6~27V之间。

标签:凌阳单片机多功能输入/输出口超低频脉冲信号发生器信号发生器是一种为电子测量和计量工作提供符合严格技术要求的电信号设备。

在考虑低频脉冲信号发生器的设计和控制时,本文主要从以下几个方面考虑:(1)可以手动设置频率的大小,其设置范围在1—999HZ之间,以达到频率在一定范围内可调这一特点。

(2)可以手动设置占空比的大小,控制脉宽,即实现占空比可调这一特点。

(3)通过放大电路使输出脉冲电压在3.6V—27V之间可调,从而达到输出脉冲幅值电压可调这一特点。

根據以上情况, 我们尝试用SPACE061A小系统板及低频脉冲信号发生器的硬件控制电路构成整个系统,通过编程来控制脉冲的产生。

下面主要从硬件方面来描述本系统。

一、系统设计方案本系统采用凌阳单片机作为控制核心,将SPACE061A 小系统板与低频脉冲信号发生器的硬件控制电路板用排线相连,即用SPACE061A 的输入/输出口来控制低频脉冲信号发生器的硬件电路板上的数码管显示和1*5小键盘,产生矩形波信号,再经过硬件电路板上的74LS74D触发器和由555定时器构成的单稳态触发器,最后通过放大电路输出频率、幅值、占空比均在一定范围内可调的低频脉冲信号发生器。

充分利用凌阳单片机的实时定时、多功能输入/输出口等优势,使得整个系统更加具有实用性。

二、系统相关硬件说明凌阳单片机SPACE061A已为大家所熟知,这里不再详述,下面主要对低频脉冲信号发生器硬件控制电路板作一具体介绍。

硬件电路整体框图如下图2-1所示。

图2-1低频脉冲信号发生器结构框图下面就分别介绍一下显示模块、键盘输入模块、74LS74D触发器、单稳态触发器模块和放大电路模块。

数控脉冲宽度调制信号发生器课程设计报告1

摘要:本设计采用EDA技术,通过FPGA芯片实现了数控脉冲宽度调制信号发生器的设计,本文采用Verilog 硬件描述语言来说明电路,完成对电路的功能仿真。

通过D触发器及两个可加载8位计数器lcnt8.v实现本设计。

与传统的设计方式相比,本设计由于采用了FPGA芯片来实现,它将大量的电路功能集成到一个芯片中,并且可以由用户自行设计逻辑功能,提高了系统的集成度和可靠性。

关键词:EDA技术、FPGA芯片、硬件描述语言、信号发生器Abstract:This design uses the EDA technology, through the FPGA chip to realize numerical control pulse width modulation signal generator design, the use of Verilog hardware description language to describe the circuit circuit, complete function simulation. Through the D trigger and two can be loaded in 8bit counter lcnt8.v to achieve the design. Compared with traditional design methods, the design adopts FPGA chip to achieve, it will be a large number of circuit functions are integrated into one chip, and can be designed by the user logic function, improve the system integration degree and reliability.Keywords:EDA technology, FPGA chips, hardware description language,Signal generator前言目录前言 (1)1 EDA技术发展及VHDL 简介 (2)1.1 EDA技术的介绍 (2)1.2 EDA技术的发展 (2)1.3 EDA技术的发展趋势 (3)1.4 VHDL简介 (3)2 总体方案设计 (4)2.1设计内容 (4)2.2设计方案比较 (4)2.3方案论证 (5)2.4方案选择 (6)3 特殊器件的介绍 (7)3.1 CPLD器件介绍 (7)3.2 FPGA器件介绍 (7)3.3 EP1K30TC144器件介绍 (8)4 单元模块设计 (9)4.1 供电电路 (9)4.2 PS配置电路 (10)4.3有源晶振电路 (11)4.4 八位计数器输入电路 (11)4.5 D触发器电路 (12)5 最小系统原理图 (13)6 软件实现 (14)6.1软件设计 (14)6.2思考题扩展 (16)7 系统仿真及调试 (20)7.1仿真 (20)7.2 调试 (21)8 总结 (23)9 参考文献 (24)前言随着电子技术的发展,人们的生活水平和质量不断提高,生活设备的智能化程度也越来越高,这些都离不开电子产品的进步。

uwb超宽带脉冲信号发生器设计内容和要求

uwb超宽带脉冲信号发生器设计内容和要求

“uwb超宽带脉冲信号发生器设计内容和要求”这个短语涉及到UWB (超宽带)脉冲信号发生器的设计和相关要求。

UWB是一种无线通信技术,使用极短的脉冲信号来传输数据,通常在纳秒级别。

这种技术被广泛应用于近距离高速数据传输和定位系统等领域。

设计UWB超宽带脉冲信号发生器的主要内容和要求包括:

1.确定信号的参数:根据应用需求,确定脉冲信号的参数,如脉冲宽度、脉

冲幅度、频率范围等。

这些参数将影响信号的传输特性和覆盖范围。

2.选择合适的波形:UWB脉冲信号有多种波形,如高斯脉冲、矩形脉冲等。

根据实际需求选择合适的波形,以满足系统的性能要求。

3.设计脉冲生成电路:为实现所需的脉冲信号,需要设计相应的脉冲生成电

路。

这包括脉冲产生单元、脉冲调制单元等,以确保信号的稳定性和准确性。

4.考虑系统的集成度:在设计过程中,需要考虑信号发生器的尺寸、功耗和

成本等因素,以满足实际应用的需求。

5.验证和测试:完成设计后,需要对信号发生器进行验证和测试,以确保其

性能符合预期要求。

这包括信号质量、覆盖范围、传输速率等方面的测试。

总结:UWB超宽带脉冲信号发生器设计内容和要求是指设计和制造一种能够生成UWB超宽带脉冲信号的设备,并满足相关的参数、性能和成本要求。

这种设备广泛应用于通信、雷达、定位等领域,对于实现高速、短距离无线通信具有重要意义。

用AT89S52设计具有定量脉冲输出功能的脉冲信号发生器

脉 冲信 号 发 生器 是 一种 常用 的 电子 仪器 ,通 常 这种

S10

仪器只 能输 出连续 脉冲 或单脉 冲 。本 文介 绍 的脉冲信 号发 生器不 但能输 出连 续脉 冲 ,而 且 能够 根据 设定输 出规 定数

De gn by A si T8 52 Qu tt tv 9S an ia i e Pul se and Cont nuous Pul i se ut O put of Pul se

Gen a or / u J a x e X i n u er t /  ̄ i n u , u J a h i

A B C D — — L B T I — — C 4 D 51 1 L E A BC D CD 51 4 1 L E

5 0 z、 1 K z、 2 K 0 H H Hz

ABC DL T

CD 5 4 11 L E a b C o d e f

维普资讯

4 6

徐涛学 徐泞慧:用A8S2 T95设计具有定量脉冲输出功能的脉冲信号发生器

第 1 8期

用AT 9 5 设计具有 定量脉冲输 出功 能 的 8S 2 脉冲信 号发 生器

徐 涛学 徐涛慧。

1 内蒙古 民族 大学 内蒙 古通 辽 08 4 2 内蒙 古移 动 公司通 辽 分公 司 内蒙古通 辽 2 03 08 0 2 00

Ab t a h u e f c m u e — h p d s g p l e e e a o , a u n i a i e p l e s r ct T e s o o p t r c i e i n u s g n r t r q a t t t v u s ,

电子课程设计_1HZ脉冲信号发生器

电子设计报告姓名:李均波学号:0810*******班级:09级电信2班指导教师:杨继民课程名称:一赫兹方波发生器提交日期:2011 年 6月30 日目录1 555定时器的结构2 工作原理3 多谐振荡器(1)电路组成(2) 工作原理4 方波(1)方波的产生(2)一赫兹方波(3) 实验电路图555定时器的结构和工作原理多谐振荡器1.555定时器构成的多谐振荡器电路及工作波形2. . 描述矩形脉冲特性的指标3. 工作原理由于接通电源前,电容器两端电压uC=0,电源刚接通时UB=1,UA=0,因而Q=1,Q=0,经输出缓冲级后uO 为高电平,放电管V 处于截止。

电源电压通过R1、R2对C 充电其暂态过程为:由于比较器A 、B 的存在,电容C 不可能充至UDD 。

过程如下:当时,UB 、UA 均为低电平, RS 触发器状态不变;但当 时,UA=1,UB=0,RS 触发器状态变为Q=0, Q=1,输出uO 为低电平,放电管V 导通,这段时间我们称为第一暂稳态期。

放电管V 导通时,电容C 通过电阻R2和放电管放电,电路进入第二暂稳态期,放电过程为由于比较器A 、B 的存在,电容器不可能放电至0。

当电容放电,时,UA=UB=0,RS 触发器处于维持状态, 输出也不变;但当C 继续放电, 时,UB=1,UA=0, 这时Q=1, Q=0,输出uO 为高电平,放电管截止,UDD 再次对电容充电。

如此反复,可输出矩形波形。

⎪⎪⎩⎪⎪⎨⎧+==∞=+C R R U u u DDCC ))(0)0(21(充τ⎪⎪⎪⎩⎪⎪⎪⎨⎧+==∞=+C R R u U u C DD C)0)(32)0(21(放τDD C DD U u U 3231<≤D D CU u 31≤DD C DD U u U 3231<≤D D C U u 32≥4.方波的产生方波是高电平于低电平持续时间相等的矩形波所以当T1=T2时既充电时间于放电时间相等时多谢振荡器输出地就是方波5.一赫兹方波当输出一赫兹方波时周期为一秒频率为一赫兹既:T1=0.5s,T2=0.5秒6.电路图如下所示:其中R1=54.9ΩK。

四位全加器设计

一. 设计原理。

1.全加器与脉冲信号发生器电路图U1、U2 和 U3A 组成一位全加器, 个加数”由 U1A 的 1、2 “2 脚输入, “进位”有 U8A 的 5 脚输入, “全加和”由 U2C 的 8 脚输出到 D 触发器 U4A 的数据输出端 D,进位输出到 U8A 的 数据输入端。

和 U3C 组成的基本 RS 触发器和单刀双掷无 U3B 锁按键 KP 一起组成脉冲发生器,每按一次 KP 在 U3C 的管脚 8 形成的一个正位脉冲给所有 D 触发器提供 CP 脉冲 2 累加器 A 电路图由双 D 触发器 U4 和 U5 组成的“移位寄存器 A”保存累加器 的一个加数 3.累加器 B 电路图由双 D 触发器 U6 和 U7 组成的“移位寄存器 B”保存累加器 的另一个加数,D 触发器 U8A 保存进位位 C4.累加器电路图按下 KR 键可使所有 D 触发器复位为全 0,复位后可通过KA3-KA0 键分别设置加数 A 的各个位,通过 KB3-KB0 键分别 设置另一个加数 B 的各个位, 通过 KC 设置来自低位的进位 C。

按 KP 键 4 次产生 4 各 CP 脉冲完成累加, 结果在寄存器 A 中, 向高位的进位在 C 中,寄存器 B 全为 0.二、制作调试过程 1、 步骤 (1) 打印: 3 个电路图分别打印在 3 张要求大小的硫酸 将 纸上 (2) 裁板:裁切 3 张比电路图大小大一点的铜板 (3) 压图: 用过热机将电路图压在铜板上, 冷却后撕去硫 酸纸,检查电路是否完整 (4) 腐蚀:将铜板放在三氯化铁腐蚀液中腐蚀 (5) 钻孔:用钻孔机钻孔 (6) 焊接:用电烙铁将每个元器件焊接在正确的位置上 2、 准备工作 用万能表检查有没有短路、断路情况。

三、 测试。

(1) 全加器与脉冲信号发生器的测试 A0,B0,C 接逻辑开关,VCC 接电源,GND 解地,S,CO,CP 分 别接发光二极管。

基于FPGA的脉冲信号发生器的设计

摘要:r O绍了一种基于 FG P A的脉冲 信号发生器的设计方法与电路。该仪器可以产生周期在 1 s m 秒到 1 0 之 O s

间的方波信号 , 并且信号的占空 比可 以以千分之一周 期 的步进 进行调 节 , 出模式 可 以分成 连续模式 和单 次手动 触 输

sr e ecr u t.Co a e i h i u t c n t c e y c mmo e ie , h e u s e e ao a a u e u h a s o o e t , t th i i u t c s mp rd w t t ec r i o sr td b o h c s u n d vc s t en w p le g n r tr sf t r ss c s l s c mp n n s h e e

aet omo e ee tbefro tu uss ig lrp s up ta d rp t iep leo tu ,w ih c n b e ya t o— p s in s i h r w d sslca l o up t l e ,sn ua u eo tu n e eiv us up t hc a estb p l t w oio wt . t c

tenlO sadl. adte u yl o te u eC eajs df ml 10 yl t 9 9 10 yl s pe y11 0cce. h r w e O n s , t cc fh l a b dut o / 00cc 9/ 0 0cc ep db / O yl T ee n n hd y e ps n e r eo et

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

脉冲信号发生器摘要:本实验是采用fpga方式基于Alter Cyclone2 EP2C5T144C8的简易脉冲信号发生器,可以实现输出一路周期1us到10ms,脉冲宽度:0.1us到周期-0.1us,时间分辨率为0.1us的脉冲信号,并且还能输出一路正弦信号(与脉冲信号同时输出)。

输出模式可分为连续触发和单次手动可预置数(0~9)触发,具有周期、脉宽、触发数等显示功能。

采用fpga计数实现的电路简化了电路结构并提高了射击精度,降低了电路功耗和资源成本。

关键词:FPGA;脉冲信号发生器;矩形脉冲;正弦信号;1 方案设计与比较脉冲信号产生方案:方案一、采用专用DDS芯片的技术方案:目前已有多种专用DDS集成芯片可用,采用专用芯片可大大简化系统硬件制作难度,部数字信号抖动小,输出信号指标高;但专用芯片控制方式比较固定,最大的缺点是进行脉宽控制,测量困难,无法进行外同步,不满足设计要求。

方案二、单片机法。

利用单片机实现矩形脉冲,可以较方案以更简化外围硬件,节约成本,并且也可以实现灵活控制、能产生任意波形的信号发生器。

但是单片机的部时钟一般是小于25Mhz,速度上无法满足设计要求,通过单片机产生脉冲至少需要三条指令,所需时间大于所要求的精度要求,故不可取。

方案二:FPGA法。

利用了可编程逻辑器件的灵活性且资源丰富的特点,通过Quartus 软件的设计编写,实现脉冲信号的产生及数控,并下载到试验箱中,这种方案电路简单、响应速度快、精度高、稳定性好故采用此种方案。

2 理论分析与计算脉冲信号产生原理:输入量周期和脉宽,结合时钟频率,转换成两个计数器的容量,用来对周期和高电平的计时,输出即可产生脉冲信号。

脉冲信号的精度保证:时间分辨率0.1us,周期精度:+0.1%+0.05us,宽度精度:+0.1%+0.05us,为满足精度要求,所以所选时钟频率至少1/0.05us=20MHZ,由于试验箱上大于10MHZ只有50MHZ,故选时钟信号50MHZ,此时精度1/50MHZ=0.02us<0.05us,满足精度要求。

正弦信号产生原理:正弦信号的产生由DDS原理实现,频率由频率控制字M和时钟周期Fc决定,M=Fout*2^N/Fc,Fout=1/T,N即为相位累加器的位数,化简锝M=2^N/(5*T),即说明可以通过输入量周期控制正弦的频率,与脉冲达到同周期。

3程序设计3.1 系统框图如图3-1所示。

图3-1 系统框图按键输入模块:通过不同的按键切换周期和脉宽、高低位输入数据。

(vhdl语言见附录1)图3-2 按键输入模块显示模块:采用查询ROM表的方法,二进制数值通过一个ROM表显示为十进制数值,在数码管上显示。

(Vhdl及rom表见附录2)图3-3 显示模块高低电平计数模块:计数器接时钟脉冲50MHZ,即每次计数0.02us,5次计数为0.1us,即为实验要求的时间精度0.1us,通过置入周期和脉宽放大5倍(周期和脉宽均以0.1us为单位)便可产生高低脉冲信号。

(Mk模块vhdl见附录三)图3-4 脉冲信号产生模块正弦信号产生模块:由DDS原理产生,频率控制字M=Fout*2^N/Fc,Fout=1/T,N即为相位累加器的位数,化简得M=2^N/(5*T),再通过相位累加器查找正弦ROM表,便可产生正弦信号,正弦信号的周期即为T,与脉冲信号同周期。

(reg29、dm1、正弦rom见附录四)图3-5正弦信号产生模块整体电路连接:(见附录五)4 作品测试4.1 测试仪器TDS1002型60MHZ1 0GS/s双通道数字存储示波器,系统试验箱。

4.2 测试方案控制时钟:50MHz按键操作:Key1:十分位、百位计数使能;Key2:个位、千位计数使能;key3:十位、万位计数使能;key4:高三位低三位切换;key5:脉宽、周期切换;key6:脉宽周期输入脉冲;Key7:猝发脉冲计数按键;key8:系统清零键;key3与key2同时按下切换至单猝发方式;key3、2、1同时按下但猝发脉冲发射。

测试方法:按键输入脉宽和周期,经过示波器观察测量正弦和脉冲周期以及脉宽,记录数据制4.3表格,切换猝发方式后继续用示波器进行单猝发计数测试。

4.3 测试结果输入周期输入脉宽显示脉宽脉宽误差显示周期周期误差上升时间正弦周期幅度猝发模式状态下输入数据N,示波器显示输出N个脉冲和正弦信号;波形图见附录6 4.4 结果分析系统在输出脉冲脉宽、周期和正弦波以及猝发脉冲等指标达到题目的基本和发挥部分要求,各项指标测量精度高,整体性能达到题目发挥部分要求。

5 总结本系统以fpga作为系统的核心控制器件,以系统试验箱为平台,具有1us-10ms的方波脉冲发生和正弦脉冲发生功能,同时具有1-9固定数量脉冲单猝发功能,具有精度较高速度快的特点,所有指标均达到或部分超过赛题要求。

附录附件1:按键输入模块library ieee;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;entity xianshi isport(cp,change,clr,hl,aj1,aj2,aj3:in std_logic;zq,mk:out std_logic_vector(16 downto 0));end xianshi;architecture one of xianshi issignal m:std_logic_vector(16 downto 0);signal n:std_logic_vector(16 downto 0);beginprocess(cp,change,clr,hl,aj1,aj2,aj3)beginif clr='1'thenm<="00000000000000000"; n<="00000000000000000";elsif cp'event and cp='1' thenif change='0'and hl='0'thenif aj1='1'then m<=m+1;end if;if aj2='1'then m<=m+10;end if;if aj3='1'then m<=m+100;end if;end if;if change='0'and hl='1'thenif aj1='1'then m<=m+1000;end if;if aj2='1'then m<=m+10000;end if;if aj3='1'then m<=m+100000;end if;end if;if change='1'and hl='0'thenif aj1='1'then n<=n+1;end if;if aj2='1'then n<=n+10;end if;if aj3='1'then n<=n+100;end if;end if;if change='1'and hl='1'thenif aj1='1'then n<=n+1000;end if;if aj2='1'then n<=n+10000;end if;if aj3='1'then n<=n+100000;end if;end if;end if;zq<=m;mk<=n;end process;end one;附件2:library ieee;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;entity chg isport(change:in std_logic;zq,mk:in std_logic_vector(16 downto 0);xs:out std_logic_vector(16 downto 0));end chg;architecture one of chg isbeginprocess(change)beginif change='0'thenxs<=zq;elsexs<=mk;end if;end process;end one;library ieee;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;entity hhll isport(hl:in std_logic;h:in std_logic_vector(16 downto 0);l:in std_logic_vector(9 downto 0);xxss:out std_logic_vector(9 downto 0)); end hhll;architecture one of hhll isbeginprocess(hl)beginif hl='0'thenxxss<=l;elsexxss<=h(9 downto 0);end if;end process;end one;显示rom表附件3:mklibrary ieee;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;entity mk isport(clk:in std_logic;t,k:std_logic_vector(19 downto 0); f:out std_logic);end mk;architecture one of mk issignal m:std_logic_vector(19 downto 0); beginprocess(clk,t,m)beginif clk'event and clk='1'thenm<=m+1;if m>=t thenm<="00000000000000000001";f<='0'; elsif m<=k thenf<='1';else f<='0';end if;end if;end process;end one;附件4:Reg29library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity reg29 isport(d:in std_logic_vector(31 downto 0);clk:in std_logic;q:out std_logic_vector(31 downto 0));end reg29;architecture one of reg29 isbeginprocess(clk,d)beginif clk'event and clk='1' thenq<=d;end if;end process;end one;dm1library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity dm1 isport(q:in std_logic_vector(9 downto 0);si:in std_logic_vector(16 downto 0);f:out std_logic_vector(9 downto 0));end dm1;architecture one of dm1 isbeginprocess(si,q)beginif si="00000000000000000" then f<="0000000000"; else f<=q;end if;end process;end one;正弦rom附件五:。